常用IC芯片管脚的定义中引文翻译

CPU针脚定义

23. REQ[4:0]# •

這些訊號由CPU接到NB(北橋),當總線擁有者開始一個新 的交易時,由它來定義交易的命令。

23. RESET# •

I

Reset(重置訊號)

當Reset為High時CPU內部被重置到一個已知的狀態並且開 始從位址0FFFFFFF0H讀取重置後的第一個指令。CPU內部 的TLB(位址轉換參考暫存器)、BTB(分歧位址暫存器) 以及SDC(區段位址轉換快取記憶體)當重置發生時內部資 料全部都變成無效。 I Response Status(響應狀態)

7.) FERR# (浮點運算錯誤): 此PIN為一輸出訊號,當CPU內部浮點運算器發生一個Non-Masked Floating Point Error (不遮蔽的浮點運算錯誤) 時,FERR#會被CPU驅 動為LOW。 FERR#的功能與Intel387 Math Coprocessor ( 術學輔助處理器 ) 的 ERROR#訊號相同,為與DOS應用程式相容且提供DOS系統報告浮點 運算錯誤相同的模式。 動作說明 : 一 . Type : output 二 . Normal Voltage Status : High (1.5 V ) 三 . High Min Level : 0.8 V 四 . High Man Level : 1.2 V

當CPU的溫度傳感器偵測到CPU的溫度超過它設定的最高度 溫度時,這個訊號將會變Low,相應的CPU的溫度控制電路 就會動作。 I Power Good(電源OK)

22. PWRGOOD •

這個訊號通常由ICH(南橋)發給CPU,來告訴CPU電源已 OK,若這個訊號沒有供到CPU,CPU將不能動作。 I/O Command Request(命令請求)

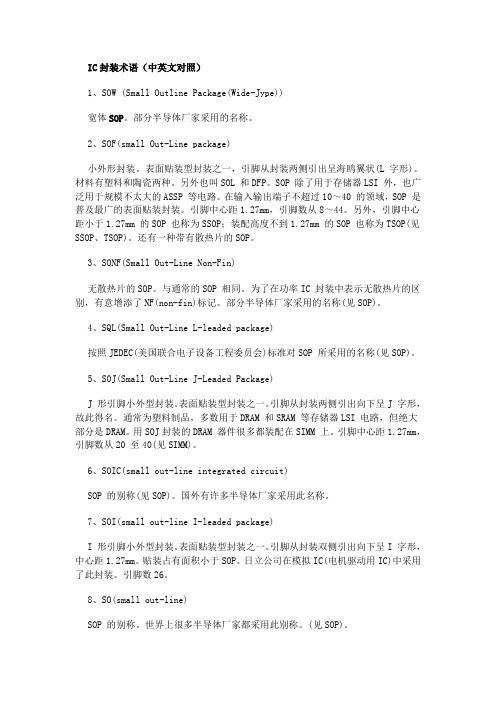

IC封装术语(中英文对照)

IC封装术语(中英文对照)1、SOW (Small Outline Package(Wide-Jype))宽体SOP。

部分半导体厂家采用的名称。

2、SOF(small Out-Line package)小外形封装。

表面贴装型封装之一,引脚从封装两侧引出呈海鸥翼状(L 字形)。

材料有塑料和陶瓷两种。

另外也叫SOL 和DFP。

SOP 除了用于存储器LSI 外,也广泛用于规模不太大的ASSP 等电路。

在输入输出端子不超过10~40 的领域,SOP 是普及最广的表面贴装封装。

引脚中心距1.27mm,引脚数从8~44。

另外,引脚中心距小于1.27mm 的SOP 也称为SSOP;装配高度不到1.27mm 的SOP 也称为TSOP(见SSOP、TSOP)。

还有一种带有散热片的SOP。

3、SONF(Small Out-Line Non-Fin)无散热片的SOP。

与通常的SOP 相同。

为了在功率IC 封装中表示无散热片的区别,有意增添了NF(non-fin)标记。

部分半导体厂家采用的名称(见SOP)。

4、SQL(Small Out-Line L-leaded package)按照JEDEC(美国联合电子设备工程委员会)标准对SOP 所采用的名称(见SOP)。

5、SOJ(Small Out-Line J-Leaded Package)J 形引脚小外型封装。

表面贴装型封装之一。

引脚从封装两侧引出向下呈J 字形,故此得名。

通常为塑料制品,多数用于DRAM 和SRAM 等存储器LSI 电路,但绝大部分是DRAM。

用SOJ封装的DRAM 器件很多都装配在SIMM 上。

引脚中心距1.27mm,引脚数从20 至40(见SIMM)。

6、SOIC(small out-line integrated circuit)SOP 的别称(见SOP)。

国外有许多半导体厂家采用此名称。

7、SOI(small out-line I-leaded package)I 形引脚小外型封装。

芯片引脚定义翻译

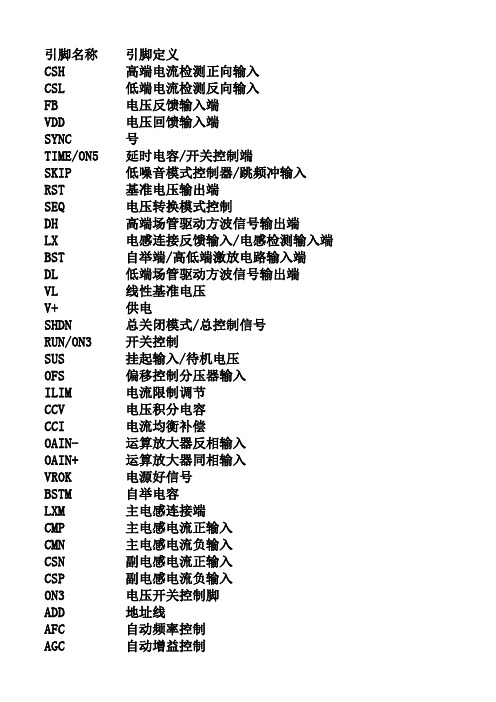

引脚名称引脚定义CSH 高端电流检测正向输入CSL 低端电流检测反向输入FB 电压反馈输入端VDD 电压回馈输入端SYNC同步电压频率选择/频率设置/同步信号TIME/ON5延时电容/开关控制端SKIP 低噪音模式控制器/跳频冲输入RST 基准电压输出端SEQ 电压转换模式控制DH 高端场管驱动方波信号输出端LX 电感连接反馈输入/电感检测输入端BST 自举端/高低端激放电路输入端DL 低端场管驱动方波信号输出端VL 线性基准电压V+供电SHDN 总关闭模式/总控制信号RUN/ON3开关控制SUS 挂起输入/待机电压OFS 偏移控制分压器输入ILIM 电流限制调节CCV 电压积分电容CCI 电流均衡补偿OAIN-运算放大器反相输入OAIN+运算放大器同相输入VROK 电源好信号BSTM 自举电容LXM 主电感连接端CMP 主电感电流正输入CMN 主电感电流负输入CSN 副电感电流正输入CSP 副电感电流负输入ON3电压开关控制脚ADD 地址线AFC自动频率控制AGC 自动增益控制AVCC音频供电BACKLIGHT背光灯开启BAT_VOLT电压检测Boost-En升压启动BUZZER振铃CS FLASH字库片选CS ROM版本片选CSRAM暂存片选DATA数据线LCD_CS显示屏片选LCD-EN显示屏启动MIC-本机话筒负极MIC+本机话筒正极ON_OFF开机触发POWER ON开机启动Reset复位VBATT电池电压TIME频率设置TON导通时间选择S0挂起模式DLM低端管驱动EC嵌入式控制器THRMTRIP温度控制VRON开机电源电压控制信号VSB待机VCCP总线供电EMI电磁抗干扰电路MOSFET方波切割组件PWM脉宽调制定义说明用于逻辑控制电路。

IC脚位及术语英汉对照

SRVM / FODAC/ TRDAC / SLPWM / SPDPWM / LDON / SSPDO

偏置/聚焦/循跡/滑行/主軸/ 發光二極管控制開關/ 驅動開啟控制信號輸出

RF-SDEN/ RF-SDA /RF-SCK:串行數據使能﹑ 雙向﹑時鐘控制信號輸入

BYTE : word/byte selection input 字/位選擇輸入

RY/BY: ready/busy output 閑/忙輸出

WP: write protect 寫入保護

FWR : flash write enable input 閃存寫入使能信號1

LRCK: left/right clock 左右聲道時鐘7

LNBC: LBN control output bits

SDA: Serial control colk (I2C)

SCL: Serial control data (I2C)

Nimd/ NimdA/ NimdB: parallel data input bits

EMU : Emulation mode select 仿效模式選擇

NIMclk : clock of parallel/serial data input 時鐘的parallel

NIMerr : error of parallel/serial data input 無效的parallel

NIMvld : valid of parallel/serial data input 有效的parallel

AAFOC /AAFIC 彩色信號外接濾波器輸入輸出

AAFIY/AAFOY亮度信號外接濾波器輸入輸出

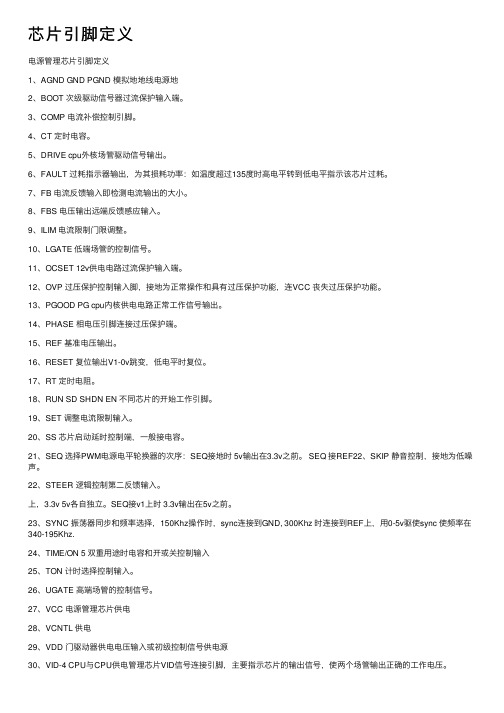

芯片引脚定义

芯⽚引脚定义电源管理芯⽚引脚定义1、AGND GND PGND 模拟地地线电源地2、BOOT 次级驱动信号器过流保护输⼊端。

3、COMP 电流补偿控制引脚。

4、CT 定时电容。

5、DRIVE cpu外核场管驱动信号输出。

6、FAULT 过耗指⽰器输出,为其损耗功率:如温度超过135度时⾼电平转到低电平指⽰该芯⽚过耗。

7、FB 电流反馈输⼊即检测电流输出的⼤⼩。

8、FBS 电压输出远端反馈感应输⼊。

9、ILIM 电流限制门限调整。

10、LGATE 低端场管的控制信号。

11、OCSET 12v供电电路过流保护输⼊端。

12、OVP 过压保护控制输⼊脚,接地为正常操作和具有过压保护功能,连VCC 丧失过压保护功能。

13、PGOOD PG cpu内核供电电路正常⼯作信号输出。

14、PHASE 相电压引脚连接过压保护端。

15、REF 基准电压输出。

16、RESET 复位输出V1-0v跳变,低电平时复位。

17、RT 定时电阻。

18、RUN SD SHDN EN 不同芯⽚的开始⼯作引脚。

19、SET 调整电流限制输⼊。

20、SS 芯⽚启动延时控制端,⼀般接电容。

21、SEQ 选择PWM电源电平轮换器的次序:SEQ接地时 5v输出在3.3v之前。

SEQ 接REF22、SKIP 静⾳控制,接地为低噪声。

22、STEER 逻辑控制第⼆反馈输⼊。

上,3.3v 5v各⾃独⽴。

SEQ接v1上时 3.3v输出在5v之前。

23、SYNC 振荡器同步和频率选择,150Khz操作时,sync连接到GND, 300Khz 时连接到REF上,⽤0-5v驱使sync 使频率在340-195Khz.24、TIME/ON 5 双重⽤途时电容和开或关控制输⼊25、TON 计时选择控制输⼊。

26、UGATE ⾼端场管的控制信号。

27、VCC 电源管理芯⽚供电28、VCNTL 供电29、VDD 门驱动器供电电压输⼊或初级控制信号供电源30、VID-4 CPU与CPU供电管理芯⽚VID信号连接引脚,主要指⽰芯⽚的输出信号,使两个场管输出正确的⼯作电压。

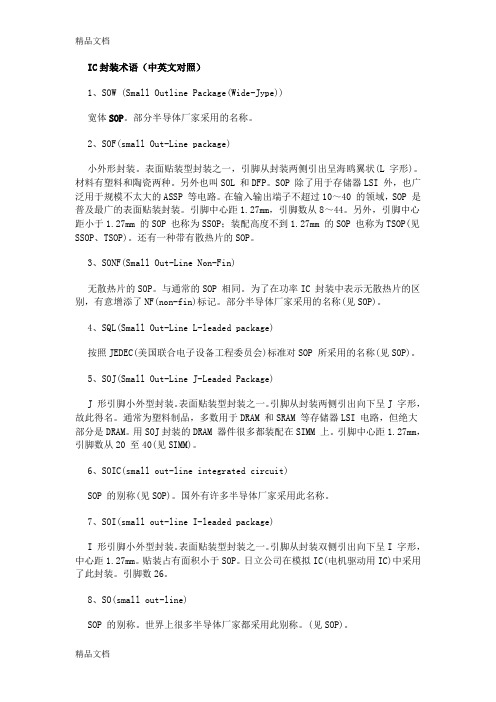

(整理)IC封装术语中英文对照.

IC封装术语(中英文对照)1、SOW (Small Outline Package(Wide-Jype))宽体SOP。

部分半导体厂家采用的名称。

2、SOF(small Out-Line package)小外形封装。

表面贴装型封装之一,引脚从封装两侧引出呈海鸥翼状(L 字形)。

材料有塑料和陶瓷两种。

另外也叫SOL 和DFP。

SOP 除了用于存储器LSI 外,也广泛用于规模不太大的ASSP 等电路。

在输入输出端子不超过10~40 的领域,SOP 是普及最广的表面贴装封装。

引脚中心距1.27mm,引脚数从8~44。

另外,引脚中心距小于1.27mm 的SOP 也称为SSOP;装配高度不到1.27mm 的SOP 也称为TSOP(见SSOP、TSOP)。

还有一种带有散热片的SOP。

3、SONF(Small Out-Line Non-Fin)无散热片的SOP。

与通常的SOP 相同。

为了在功率IC 封装中表示无散热片的区别,有意增添了NF(non-fin)标记。

部分半导体厂家采用的名称(见SOP)。

4、SQL(Small Out-Line L-leaded package)按照JEDEC(美国联合电子设备工程委员会)标准对SOP 所采用的名称(见SOP)。

5、SOJ(Small Out-Line J-Leaded Package)J 形引脚小外型封装。

表面贴装型封装之一。

引脚从封装两侧引出向下呈J 字形,故此得名。

通常为塑料制品,多数用于DRAM 和SRAM 等存储器LSI 电路,但绝大部分是DRAM。

用SOJ封装的DRAM 器件很多都装配在SIMM 上。

引脚中心距1.27mm,引脚数从20 至40(见SIMM)。

6、SOIC(small out-line integrated circuit)SOP 的别称(见SOP)。

国外有许多半导体厂家采用此名称。

7、SOI(small out-line I-leaded package)I 形引脚小外型封装。

常用IC芯片管脚的定义中引文翻译

使能信号。

VA: analog power 模拟电源输入; LVDS:Low voltage differential signal低电平微分信号。

电源开关输入。

定时程序信号输入signal).11 .WE:写入启动信号;RST: reset 复位信号;CLK 时钟控制信号;CKE 时钟控制信号。

12. Vcc:电源信号;CS 片选信号;SCLK:串行时钟输入;RF:信号输出;FCOM:公共信号端。

:晶振信号输出;XTALI:晶振信号输入。

OPOLS:VCO 信号输出。

:ASCO 时钟、数据输出;RXD:ASCO^据输入或输出。

: 同步脉冲输入 ; RCT: 振荡器时间常数电路 ;DC: 占空比控制。

:5V 基准电压;VFB:误差放大器倒相输入;COMP 误差放大器输出。

1、2、 3、 4、 5、 常用 IC 芯片管脚的定义中引文翻译VOL — Voltage Output Low 低电平输出电压; VIH (Voltage Input High )高 电平输入电压。

CLKO(Clock Out put)时钟输出;Vss 数字地。

DP:USB 端 D+言号。

VD —数字电源;Vssp:I/O 驱动缓冲数字地。

DM: USB 端 D-信号。

CE:Chip enable input 片使能输出; OE :Output enable input 输出使能输入。

WP:Write protect 写入保护; FWR Flash write enable input闪存写入6、 7、 FB :Output voltage feedback输出电压返回输入; SW:Power switch input8、 SHON:Shutdown control input 关闭信号输入 ;COMP:comp voltage. 9、 TS:Temperature-sense input温度感应信号输入 RC:Timer-program input10. SNS:Current-sense input电流感应信号输入;CE:使能信号(enable:软启动控制外接电容;Vc:功放电路电源(驱动电路电源);OUT 驱动输出。

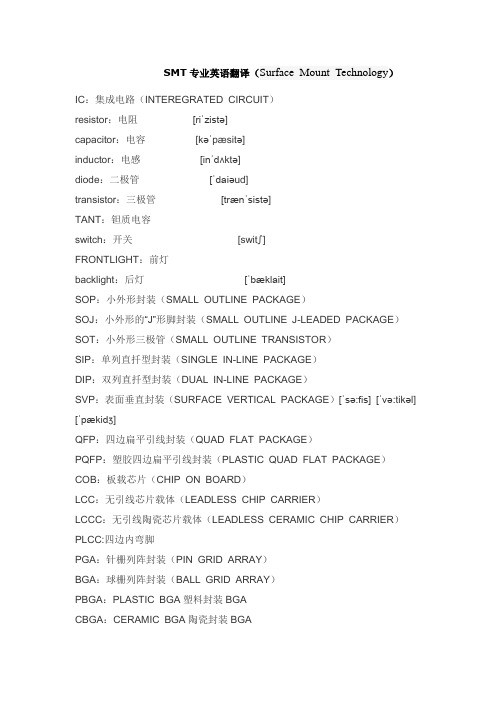

SMT专业英语翻译

SMT专业英语翻译(Surface Mount Technology)IC:集成电路(INTEREGRATED CIRCUIT)resistor:电阻[riˈzistə]capacitor:电容[kəˈpæsitə]inductor:电感[inˈdʌktə]diode:二极管[ˈdaiəud]transistor:三极管[trænˈsistə]TANT:钽质电容switch:开关[switʃ]FRONTLIGHT:前灯backlight:后灯[ˈbæklait]SOP:小外形封装(SMALL OUTLINE PACKAGE)SOJ:小外形的“J”形脚封装(SMALL OUTLINE J-LEADED PACKAGE)SOT:小外形三极管(SMALL OUTLINE TRANSISTOR)SIP:单列直扦型封装(SINGLE IN-LINE PACKAGE)DIP:双列直扦型封装(DUAL IN-LINE PACKAGE)SVP:表面垂直封装(SURFACE VERTICAL PACKAGE)[ˈsə:fis] [ˈvə:tikəl] [ˈpækidʒ]QFP:四边扁平引线封装(QUAD FLAT PACKAGE)PQFP:塑胶四边扁平引线封装(PLASTIC QUAD FLAT PACKAGE)COB:板载芯片(CHIP ON BOARD)LCC:无引线芯片载体(LEADLESS CHIP CARRIER)LCCC:无引线陶瓷芯片载体(LEADLESS CERAMIC CHIP CARRIER)PLCC:四边内弯脚PGA:针栅列阵封装(PIN GRID ARRAY)BGA:球栅列阵封装(BALL GRID ARRAY)PBGA:PLASTIC BGA塑料封装BGACBGA:CERAMIC BGA陶瓷封装BGACCGA:CERAMIC COLUMN BGA陶瓷柱状封装BGATBGA:TAPE BGA 载带状封装BGACSP:CHIP SCALE PACKAGE或ΜBGATAB:金手指I.C SOCKET:集成电路插座POTRNTIOMETER:电位器ELEC:电解电容LED:发光二极管chip component:片状元件[tʃip] [kəmˈpəunənt]薄膜开关:membrane switch [ˈmembrein] [switʃ]insulation resistance:绝缘电阻[ˈɪnsjuˈleiʃən] [riˈzistəns] control :控制[kənˈtrəul]production: 产品[prəˈdʌkʃən]changeover: 转换[ˈtʃeindʒˈəuvə]program : 程序[ˈprəuɡræm]Device check: 驱动检查[diˈvais] [tʃek]Mode: 模式[məud]operation 操作[ˈɔpəˈreiʃən]board skip data 基板跳掉数据[bɔ:d] [skip] [ˈdeitə]nozzle skip : 吸嘴跳掉[ˈnɔzl] [skip]setup : 安装panel loader : 基板载入器[ˈpænəl] [ˈləudə]position :位置[pəˈziʃən]nozzle check : 吸嘴检查[ˈnɔzl] [tʃek]part supdty 零件废弃[pɑ:t]part reiection : 零件检测[pɑ:t]chgscheduled panels 优化基板[ˈʃedju:ld] [ˈpænəl]scheduled panels : 完成基板[ˈʃedju:ld] [ˈpænəl]clear comple led pamelscompleted panels 完成基板[ˈpænəl] [ˈpænəl]tabe mode: device change 驱动选择stage:spare (completion) stage productionoperation mode 操作模式[ˈɔpəˈreiʃən] [məud] schedcle 计划[ˈʃedju:ld]completed 结束[kəmˈpli:t] Recovery mode 恢复模式[riˈkʌvəri] [məud]Recovery tims 恢复时间Board( skip marks 根据基板标识点跳跃Loader 载入器[ˈləudə]Nozzle data 吸嘴数据[ˈnɔzl] [ˈdeitə] Production info 产品信息[prəˈdʌkʃən] [ˈinfəu]Change pallet 转换装置(应该是指吸嘴转换装置)[ˈtʃeindʒˈəuvə][ˈpælit]Finish current panel 结束当前基板[ˈfiniʃ] [ˈkʌrənt] [ˈpænəl]Finish panel and unload 结束基板并搬出[ˈfiniʃ] [ˈpænəl] [ˈʌnˈləud]。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

常用IC芯片管脚的定义中引文翻译

1、VOL—Voltage Output Low 低电平输出电压;VIH(V oltage Input High)高电平输入电压。

2、CLKO(Clock Output) 时钟输出;Vss 数字地。

DP:USB端D+信号。

3、VDD—数字电源;Vssp:I/O驱动缓冲数字地。

DM:USB端D-信号。

4、CE:Chip enable input 片使能输出;OE:Output enable input 输出使能输入。

5、WP:Write protect 写入保护;FWR:Flash write enable input闪存写入使能信号。

6、V A: analog power 模拟电源输入;LVDS:Low voltage differential signal低电平微分信号。

7、FB:Output voltage feedback 输出电压返回输入;SW:Power switch input 电源开关输入。

8、SHON:Shutdown control input 关闭信号输入;COMP:comp voltage.

9、TS:Temperature-sense input温度感应信号输入RC:Timer-program input定时程序信号输入

10. SNS:Current-sense input 电流感应信号输入;CE:使能信号(enable signal).

11 .WE:写入启动信号;RST: reset 复位信号;CLK:时钟控制信号;CKE:时钟控制信号。

12. Vcc:电源信号;CS:片选信号;SCLK:串行时钟输入;RF: 信号输出;FCOM:公共信号端。

13.XTALO:晶振信号输出;XTALI:晶振信号输入。

OPOLS:VCOM 信号输出。

14.TXD:ASCO 时钟、数据输出;RXD:ASCO 数据输入或输出。

15.SYNC:同步脉冲输入; RCT: 振荡器时间常数电路;DC: 占空比控制。

16.VREF:5V基准电压;VFB: 误差放大器倒相输入;COMP:误差放大器输出。

17.SS:软启动控制外接电容;Vc:功放电路电源(驱动电路电源);OUT:驱动输出。

18.PGND:功放电路地线;SGND: 小信号电路地线。

ISEN:电流检测。

19.DIS:关闭控制。

不使用时此脚接小信号地线端,不能悬空。

20.DC-LIM: 占空比限制。

接基准电源脚时,驱动脉冲占空比被限制在50%。

如果此脚悬空

或是接地时,驱动脉冲占空比不被限制。

21.ST-BY:待机控制,通过电阻接第二脚。

如不使用待机控制,将此脚接基准电压脚或悬空。