数字逻辑设计习题第4章

数字逻辑-习题以及习题答案

AD

F的卡诺图

ACD

G的卡诺图

根据F和G的卡诺图,得到:F G

湖南理工学院计算机与信息工程系通信教研室 陈进制作

第3章习题 3.4 在数字电路中,晶体三极管一般工作在什么状态?

答:在数字电路中,晶体三极管一般工作在饱和导通状态 或者截止状态。

湖南理工学院计算机与信息工程系通信教研室 陈进制作

第3章习题

111110

1100110

⊕ ⊕⊕⊕ ⊕

10 000 1

⊕ ⊕⊕⊕ ⊕⊕

10 101 01

⑵ (1100110)2 = 64+32+4+2 = (102)10 = (0001 0000 0010)8421码

(1100110)2 =( 101?0101 )格雷码

湖南理工学院计算机与信息工程系通信教研室 陈进制作

第2章习题

2.2 用逻辑代数的公理、定理和规则证明下列表达式:

⑴ AB AC AB AC

⑵ AB AB AB AB 1

⑶ AABC ABC ABC ABC

证⑴:AB AC

AB AC

A B A C

AA AC BA BC

证⑶:AABC

A A B C

AB AC

第1章习题 1.3 数字逻辑电路可分为哪两种类型?主要区别是什么?

答:数字逻辑电路可分为组合逻辑电路、时序逻辑电路两 种类型。 主要区别:组合逻辑电路无记忆功能, 时序逻辑电路有记忆功能。

湖南理工学院计算机与信息工程系通信教研室 陈进制作

第1章习题 1.6 将下列二进制数转换成十进制数、八进制数和十六进制数。

第2章习题 2.8 ⑴ ②求出最简或-与表达式。

两次取反法

圈0,求F 最简与或式。

数字逻辑设计习题参考答案(第4章)

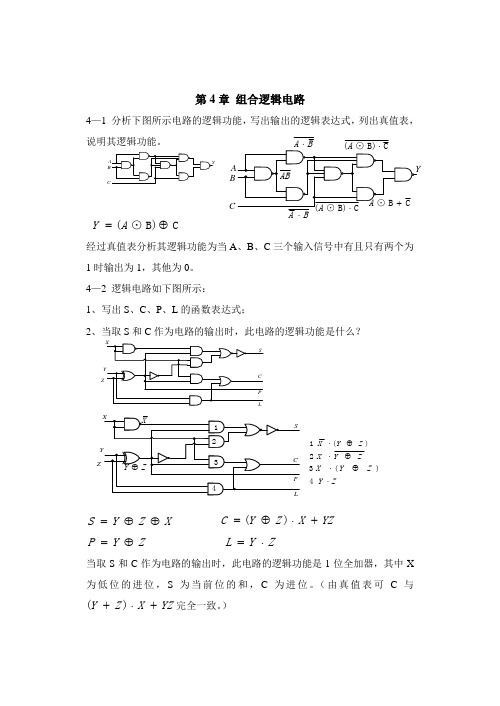

第4章 组合逻辑电路4—1 分析下图所示电路的逻辑功能,写出输出的逻辑表达式,列出真值表,说明其逻辑功能。

C B)⊙(⊕=A Y经过真值表分析其逻辑功能为当A 、B 、C 三个输入信号中有且只有两个为1时输出为1,其他为0。

4—2 逻辑电路如下图所示: 1、写出S 、C 、P 、L 的函数表达式;2、当取S 和C 作为电路的输出时,此电路的逻辑功能是什么?X Z Y S ⊕⊕= YZ X Z Y C +⋅⊕=)(Z Y P ⊕= Z Y L ⋅=当取S 和C 作为电路的输出时,此电路的逻辑功能是1位全加器,其中X 为低位的进位,S 为当前位的和,C 为进位。

(由真值表可C 与YZ X Z Y +⋅+)(完全一致。

)ZB CBA ⋅CB)⊙(⋅A Z)(Z Y X ⊕⋅ZY X ⊕⋅)(Z Y X ⊕⋅ZY ⋅12344—3 下图是由三个全加器构成的电路,试写出其输出1F ,2F ,3F ,4F 的表达式。

Z Y X F ⊕⊕=1 Z Y X F ⋅⊕=)(2Z XY Z XY F +⋅=3 XYZ F =44—4 下图是由3线/8线译码器74LS138和与非门构成的电路,试写出1P 和2P 的表达式,列出真值表,说明其逻辑功能。

ABC C B A m m m m Y Y P +⋅⋅=+=⋅=⋅=70707016543216543212m m m m m m Y Y Y Y Y Y P +++++=⋅⋅+⋅⋅=C B C A B A ++=P1的逻辑功能为当三个输入信号完全一致时输出为1。

P2的逻辑功能为当上输入信号不完全一致时输出为1。

4—5使用74LS138 译码器及少量门电路对三台设备状态进行监控,由不同指示灯进行指示。

当设备正常工作时,指示灯绿灯亮;当有一台设备出故障时,指示灯红灯亮;当有两台设备出故障时,指示灯黄灯亮;当有三台设备出故障时,指示灯红灯和黄灯都亮。

1234解:设输入变量A 、B 、C 分别对应三台设备的状态,0表示故障,1表示正常;输出变量X 、Y 、Z 表示绿、黄、红三个灯的亮灭,0表示灭,1表示亮,根据题意可得真值表如下:设ABC 分别连入74LS138的A 2A 1A 0 由真值表得 42104210Y Y Y Y m m m m Y ⋅⋅⋅=+++=6530Y Y Y Y Z ⋅⋅⋅=4—6 下图3.6是由八选一数据选择器构成的电路,试写出当1G 0G 为各种不同的取值时的输出Y 的表达式。

数字逻辑(欧阳星明)第四章

第四章

组合逻辑电路

4.3.2 设计举例 例1 设计一个三变量“多数表决电路”。

解 分析:“多数表决电路”是按照少数服从多数的原则 对某项决议进行表决,确定是否通过。 令 逻辑变量A、B、C --- 分别代表参加表决的3个成员, 并约定逻辑变量取值为0表示反对,取值为1表示赞成; 逻辑函数 F --- 表示表决结果。F取值为0表示决议被否定, F取值为1表示决议通过。 按照少数服从多数的原则可知,函数和变量的关系是:当3 个变量 A、B、C中有 2 个或 2个以上取值为 1 时,函数F 的值为 1, 其他情况下函数F的值为0。

2

第四章

组合逻辑电路

4. 1 基 本 概 念

一.定义 组合逻辑电路:若逻辑电路在任何时刻产生的稳定输出 值仅仅取决于该时刻各输入值的组合,而与过去的输入值无 关,则称为组合逻辑电路。 二.结 构 组合逻辑电路的结构框图如下图所示。

输 X1 入X 2 信 号 Xn

组合 逻辑电路

信 号 Fm

F1 输 F2 出

第四章

组合逻辑电路

第

四

章

组

合

逻

辑

电

路

1

第四章

组合逻辑电路

数字系统中的逻辑电路按其结构可分为组合逻辑电路和 时序逻辑电路两大类型。 组合逻辑电路既可完成各种复杂的逻辑功能,又是时序 逻辑电路的组成部分,应用十分广泛。 本章知识要点: 组合逻辑电路分析和设计的基本方法; 组合逻辑电路设计中几个常见的实际问题及其处理; 组合逻辑电路中的竞争与险象问题。

图中, X1,X2 , … , Xn 是电路的 n 个输入信号, F1,F2,… , Fm 是电路的m个输出信号。输出信号是输入信号的函数。

数字逻辑-第四章习题-759

4-1 试分析图题4-1中各电路的逻辑功能。

图题4 - 1

4-2 试分析图题4-2中各电路的逻辑功能。

图题4 - 2

4-3 分析图题4-3所示逻辑电路,写出其简化的逻辑表达 式,并用与非门改进设计。

图题4 - 3

4-4 分析图题4-4所示逻辑电路,写出其简化的逻辑表 达式。

图题4 - 4

4-5 分析图题4-5所示逻辑电路的逻辑功能,写出函数 的逻辑表达式,并用最简线路实现它。

4-16 举重比赛有3个裁判,一个是主裁判A,2个是辅 裁判B和C,杠铃完全举上的裁决由每个裁判按一下自己 面前的按钮来决定。只有2个基本点以上裁判(其中必须 有主裁判)判明成功时,表示成功的灯才亮。试设计此逻 辑电路。

4-17 试用与非门设计一个无反变量输入的最简三级 线路,以实现下列函数。

(1)F(A ,B,C)= Σ m(3,5,6) (2)F(A ,B,C,D)= Σm(1,4,5,8,12)+

Σd(3,6,9,15) (3)F(A ,B,C,D)= Σ m(0,6,10,11,14) (4)F(A ,B,C)= AB + AC + AB 4-18 试用8选1多路选择器组成64选1多路选择器。 4-19 试用中规模集成4位二进制比较器组成18位二 进制数字比较器。 4-20 试用中规模集成4位二进制比较器组成20位二 进制数字比较器。

4-10 设二进制补码[x]补= x0. x1 x2 x3 x4 ,分别写出下 列要求的判断条件:

(1)(1/2≤ x)或(x < - 1/2) (2)(1/4≤ x <1/2)或(- 1/2≤ x < - 1/4) (3)(1/8≤ x <1/4)或(- 1/4≤ x < - 1/8) (4)(0≤ x <1/8)或(- 1/8≤ x <0) 4-11 设输入ABCD是按余3码编码的二进制数码,其相 应的十进制数路如图题4-6 所示,其中A和B为输入变量 ,F为输出函数。试说明当S3 、S2 、S1 、S0 作为控制信 号时,F 与A、B 的逻辑关系。

数字逻辑电路与系统设计蒋立平主编习题解答

第4章习题及解答用门电路设计一个4线—2线二进制优先编码器。

编码器输入为3210A A A A ,3A 优先级最高,0A 优先级最低,输入信号低电平有效。

输出为10Y Y ,反码输出。

电路要求加一G 输出端,以指示最低优先级信号0A 输入有效。

题 解:根据题意,可列出真值表,求表达式,画出电路图。

其真值表、表达式和电路图如图题解所示。

由真值表可知3210G A A A A =。

(a)0 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 0 1 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 10000000000000000000000000010100011111010110000103A 2A 1A 0A 1Y 0Y G真值表≥1&1Y 3A 2A 1&&1A 0Y &1GA 00 01 11 100010001111000000001101113A 2A 1A 0A 03231Y A A A A =+00 01 11 1000000011110001000011103A 2A 1A 0A 132Y A A =(b) 求输出表达式(c) 编码器电路图图 题解4.1试用3线—8线译码器74138扩展为5线—32线译码器。

译码器74138逻辑符号如图(a )所示。

题 解:5线—32线译码器电路如图题解所示。

&&&&11EN01234567BIN/OCTENY 0&G 1G 2AG 2B42101234567BIN/OCTEN&G 1G 2A G 2B42101234567BIN/OCT EN&G 1G 2A G 2B42101234567BIN/OCT EN&G 1G 2A G 2B421A 0A 1A 2A 3A 4Y 7Y 8Y 15Y 16Y 23Y 24Y 31图 题解4.3写出图所示电路输出1F 和2F 的最简逻辑表达式。

第四章1 《数字逻辑》(第二版)习题答案

第四章1.分析图1所示的组合逻辑电路,说明电路功能,并画出其简化逻辑电路图。

图1 组合逻辑电路解答○1根据给定逻辑电路图写出输出函数表达式CA B CBA B CAA B CF⋅+⋅+⋅=○2用代数法简化输出函数表达式CBA ABC CBA ABC C)B(A ABCCABCBABCAABCF+ =+ ++ =+ +=⋅+⋅+⋅=○3由简化后的输出函数表达式可知,当ABC取值相同时,即为000或111时,输出函数F的值为1,否则F的值为0。

故该电路为“一致性电路”。

○4实现该电路功能的简化电路如图2所示。

图24.设计一个组合电路,该电路输入端接收两个2位二进制数A=A2A1,B=B2B1。

当A>B时,输出Z=1,否则Z=0。

解答○1根据比较两数大小的法则,可写出输出函数表达式为○2根据所得输出函数表达式,可画出逻辑电路图如图6所示。

图66.假定X=AB代表一个2位二进制数,试设计满足如下要求 (2) Y=X3(Y也用二进制数表示。

)○1假定AB表示一个两位二进制数,设计一个两位二进制数立方器。

由题意可知,电路输入、输出均为二进制数,输出二进制数的值是输入二进制数AB的立方。

由于两位二进制数能表示的最大十进制数为3,3的立方等于27,表示十进制数27需要5位二进制数,所以该电路应有5个输出。

假定用TWXYZ表示输出的5位二进制数,根据电路输入、输出取值关系可列出真值表如表4所示。

由真值表可写出电路的输出函数表达式为T=AB,====BWAB,ZA,Y0,X根据所得输出函数表达式,可画出用与非门实现给定功能的逻辑电路图如图9所示。

图98.设计一个“四舍五入”电路。

该电路输入为1位十进制数的8421码,当其值大于或等于5时,输出F 的值为1,否则F 的值为0。

解答○1 根据题意,可列出真值表如表5所示。

表5○2 由真值表可写出输出函数表达式为 F(A,B,C,D)=∑m(5~9)+∑d(10~15)经化简变换后,可得到最简与非表达式为○3逻辑电路图如图11所示。

数字逻辑课后答案 第四章

第四章 习题答案1.设计4个寄存器堆。

解:2. 设计具有4个寄存器的队列。

解:3.设计具有4个寄存器的堆栈解:可用具有左移、右移的移位寄存器构成堆栈。

寄存器组输入数据输出数据4.SRAM 、DRAM 的区别解:DRAM 表示动态随机存取存储器,其基本存储单元是一个晶体管和一个电容器,是一种以电荷形式进行存储的半导体存储器,充满电荷的电容器代表逻辑“1”,“空”的电容器代表逻辑“0”。

数据存储在电容器中,电容存储的电荷一般是会慢慢泄漏的,因此内存需要不时地刷新。

电容需要电流进行充电,而电流充电的过程也是需要一定时间的,一般是0.2-0.18微秒(由于内存工作环境所限制,不可能无限制的提高电流的强度),在这个充电的过程中内存是不能被访问的。

DRAM 拥有更高的密度,常常用于PC 中的主存储器。

SRAM 是静态的,存储单元由4个晶体管和两个电阻器构成,只要供电它就会保持一个值,没有刷新周期,因此SRAM 比DRAM 要快。

SRAM 常常用于高速缓冲存储器,因为它有更高的速率;5. 为什么DRAM 采用行选通和列选通解:DRAM 存储器读/写周期时,在行选通信号RAS 有效下输入行地址,在列选通信号CAS 有效下输入列地址。

如果是读周期,此位组内容被读出;如果是写周期,将总线上数据写入此位组。

由于DRAM 需要不断刷新,最常用的是“只有行地址有效”的方法,按照这种方法,刷新时,是在RAS 有效下输入刷新地址,存储体的列地址无效,一次选中存储体中的一行进行刷新。

每当一个行地址信号RAS 有效选中某一行时,该行的所有存储体单元进行刷新。

6. 用ROM 实现二进制码到余3码转换 解: 真值表如下:8421码 余三码B B BG G G栈顶SR 1SR 2SR 3输入数据输出数据压入弹出3232BG0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 10 0 110 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1 11 1 0 0最小项表达式为: G=G=G=G=阵列图为:7. 用ROM 实现8位二进制码到8421码转换10103∑)9,8,7,6,5(2∑)9,4,3,2,1(1∑)8,7,4,3,0(0∑)8,6,4,2,0(G 3G 2G 1G 0B 3B 2B 1B B 0解:输入为8位二进制数,输出为3位BCD码,12位二进制数,所以,所需8ROM的容量为:2*12=30728.ROM、EPROM和EEPROM的区别解:ROM 指的是“只读存储器”,即Read-Only Memory。

第04章 组合逻辑电路习题解

4.7写出下图所示电路的逻辑函数表达式,其中以S3,S2, 写出下图所示电路的逻辑函数表达式,其中以 , , 写出下图所示电路的逻辑函数表达式 S1,S0作为控制信号,A,B作为输入数据,列表说明输出 作为控制信号, , 作为输入数据 列表说明输出Y 作为输入数据, , 作为控制信号 的作用下与A, 的关系 的关系. 在S3–S0的作用下与 ,B的关系. 的作用下与

4.12试画出用 线-8线译码器 试画出用3线 线译码器 线译码器74LSl38和门电路产生如下多输 试画出用 和门电路产生如下多输 出逻辑函数的逻辑图. 出逻辑函数的逻辑图.

Y1 = AC Y2 = AB C + AB C + BC Y3 = B C + AB C

C B A 1

A0 A1 A2 S1 & S2 S3 EN

1,由波形图得到真值表 ,

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 F 0 0 1 1 0 0 1 0 1 1 1 1 1 1 1 0

能对输入信号设置优先级并总是对优先级最高的一 个输入信号进行编码的编码器称作优先编码器. 个输入信号进行编码的编码器称作优先编码器. 变量处打" 表示该变量不管取什么值对输出没有 变量处打"X"表示该变量不管取什么值对输出没有 影响, 影响,在写出函数与或式中表示这是一个并项后消 去的因子. 去的因子.

【电子科技大学】2015下数字逻辑设计(作业题)Chapter 4 Exercise Solutions(对应老教材第3章题号)

Chapter 4【以下为老版教材(John F. Wakerly著)的题号】3.1 The Stub Series Terminated low Voltage logic (SSTV) family, used for SDRAM modules, defines a LOW signal to be in the range 0.0~0.7V, and a HIGH signal to be in the range 1.7~2.5V. Under a positive-logic convention, indicate the logic value associated with each of the following signal levels:(a) 0.0V (b) 0.7V (c) 1.7V (d) -0.6V(e) 1.6V (f) -2.0V (g) 2.5V (h) 3.3V(a) 0 (b) 0 (c) 1 (d) undefined(e) undefined (f) undefined (g) 1 (h) undefined3.2 Repeat exercise 3.1 using a negative-logic convention.(a) 1 (b) 1 (c) 0 (d) undefined(e) undefined (f) undefined (g) 0 (h) undefined3.5 True or false: For a given set of input values, a NAND gate produces the opposite output as a NOR gate.When the two inputs are different, it will be ture.3.9 For a given silicon area, which is likely to be faster, a CMOS NAND gate or a CMOS NOR?CMOS NAND will be faster than CMOS NOR.3.11 The circuit in Figure 3-1 is a type of CMOS AND-OR-INVERT gate. Try to wirte its logic expression and draw its logic diagram using the method Mr. yuan told you with AND and OR gates and inverters.Figure 3-1A B C D Z 0 X 0 0 1 X 0 0 0 1 -- -- -- -- 0∵ A • B = 0 且 (C + D) = 0 即 A • B + (C + D) = 0 ∴ Logic expression: Z = ( A • B + C + D )’Logic diagram:3.16 Which has fewer transistors, a CMOS inverting gate or a noninverting gate?CMOS inverting gate has fewer transistors.3.21 How much high-state DC noise margin is available in an inverter whose transfer characteristic under worst-case conditions is shown in Figure 3-2? How much low-state DC noise margin is available? Assume 1.5V and 3.5V thresholds for LOW and HIGH. (Hints : The thresholds voltage means a input voltage. That is to say: V ILmax =1.5V ,V IHmin =3.5V )Figure 3-2从图中可以看出,在输入为0~1.5V 的有效低态范围内,输出的高态范围为4.75~5V ,即V OHmin =4.75V ,在输入为3.5V~5V 的有效高态范围内,输出的低态范围为0~0.25V ,即V OLmax =0.25V 。

数字逻辑第四章答案

1 第4章 作业答案1、某工厂有三个车间,每个车间各需1kW 电力。

这三个车间有两台发电机组供电,一台是1kW ,另一台是2kW 。

三个车间经常不同时工作,有时共有1个车间工作,有时两个或三个车间同时工作。

为了节省能源又能保证电力供应,请设计一个逻辑电路,能自动完成供电分配任务。

(所需要的门电路输入引脚个数和类型无限制要求,但是尽量用与非门和异或门实现)。

解:设A 、B 、C 分别为三个车间工作时的电力需求情况,1为工作,需要用电,0为不工作不需要电力供应;输出为两个F 1、F 2,F 1=1表示需要1Kw 的发电机供电,F 2=1表示需要2Kw 的发电机供电,根据题意列阵真值根据真值表得F 1和F 2的逻辑函数为:电路图为:2、分析下面逻辑电路图的功能。

解:根据电路图写出布尔表达式为:BC A BC A F +=∙=根据真值表可知,当A 为1或B 、C 同时为1时,输出F=1;此电路可看作一个表决电路,A 为主裁判,B 、C 为副裁判,规则为:当主裁判通过或两个副裁判同时通过时,最终表决结果F 为通过。

3、使用74138和与非门(输入引脚数目无限制)实现函数BC A F +=解:将函数扩展成为最小项表达式:也可以如下操作:4、使用74151和逻辑门实现下列逻辑函数。

(1)∑=)7,3,1,0(),,(m C B A F解:7766554433221100D m D m D m D m D m D m D m D m Y +++++++=令输入D 0、D 1、D 3、D 7为1,D 2、D 4、D 5、D 6为0,可得:(2)∑=)14,11,9,5,4,3,1(),,,(m D C B A F (可参考课本P89 例解:ABC D A B B D F ++++++=设ABC 为输入地址,则有:D 2输入1,D 3、D 6输入0,D 0、D 1、D 4、D 5输入变量D ,D 7输入D。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第4章 组合逻辑电路

4—1 分析下图所示电路的逻辑功能,写出输出的逻辑表达式,列出真值表,说明其逻辑功能。

4—2 逻辑电路如下图所示: 1、写出S 、C 、P 、L 的函数表达式;

2、当取S 和C 作为电路的输出时,此电路的逻辑功能是什么?

4—3 下图是由三个全加器构成的电路,试写出其输出1F ,2F ,3F ,4F 的表达式。

123

B C

Z

P和4—4 下图是由3线/8线译码器74LS138和与非门构成的电路,试写出

1

P的表达式,列出真值表,说明其逻辑功能。

2 Array

4—5使用74LS138 译码器及少量门电路对三台设备状态进行监控,由不同指示灯进行指示。

当设备正常工作时,指示灯绿灯亮;当有一台设备出故障时,指示灯红灯亮;当有两台设备出故障时,指示灯黄灯亮;当有三台设备

出故障时,指示灯红灯和黄灯都亮。

4—6 下图4.6是由八选一数据选择器构成的电路,试写出当1G 0G 为各种不同的取值时的输出Y 的表达式。

4—7仿照全加器设计一个全减器,被减数为A ,减数为B ,低位来的借位为C ,差为D ,向上借一位为J 。

要求:1.写出真值表,写出D 与J 的表达式;2.用译码器74LS138和必要的基本门电路实现此电路;3.用双四选一数据选择器实现。

G A

4—8 设计一组合逻辑电路,输入为四位二进制码3B 2B 1B 0B ,当

3B 2B 1B 0B 是BCD8421码时输出1=Y ;否则0=Y 。

列出真值表,写出

与或非表达式,用集电极开路门实现。

4—9 设计一个多功能组合数字电路,实现下表所示逻辑功能。

表中1C 0C 为功能选择输入信号;A ,B 为输入变量;F 为输出。

1.列出真值表,写出F 的表达式; 2.用八选一数据选择器和门电路实现。

4—10分析图4.10(a)所示电路:

1.写出L,Q,G的表达式,列出真值表,说明它完成什么逻辑功能。

2.用图4.10(a)所示电路与集成四位数码比较器(如图4.10(b)所示)构成一个五位数码比较器。

图4.10(a)

图4.10(b)。