Cadence学习笔记4PCB板设计

Cadence PCB设计教程

一、用Design Entry CIS(Capture)设计原理图1、创建工程:file-->new-->project ;输入工程名称,指定工程放置路径;2、设置操作环境Options-->Preferencses:颜色:colors/Print格子:Grid Display杂项:Miscellaneous.........常取默认值3、配置设计图纸:设定模板:Options-->Design Template:(应用于新图)设定当前图纸Options-->Schematic Page Properities4、创建元件及元件库File-->New Library -->选择要添加到的工程Design -->New Part.(或者在Library处右击选择New Part)(1)Homogeneous:复合封装元件中(多个元件图组成时)每个元件图都一样(default适用于标准逻辑)(2)Heterogeneous:复合封装元件(多个元件图组成时)中使用不一样的元件图(较适用于大元件)一个封装下多个元件图,以View ext part(previous part)切换视图元器件封装:(1)place -->line 画线,用来画封装外形;(2)place-->pin 放置管脚;放单个或多个;不同类型的管脚选择的type不同;5、绘制原理图(1)放置电器Place-->part ;可以从设计缓存中,活着元件库,软件自带元件库,中选择;选择Add Library 增加元件库;电源和地(power gnd)从右边工具栏中选择;(2)连接线路wirebus:与wire之间必须以支线连接,并以网标(net alias)对应(wire:D0,D1....D7;bus:D[0..7])数据总线和数据总线的引出线必须定义net alias(3)Schematic new page (可以多张图:单层次电路图间,以相同名称的“电路端口连接器”off-page connector连接多层次式电路图:以方块图(层次块Hierarchical Block...)来代替实际电路的电路图,以相同名称Port的配对内层电路,内层电路之间可以多张,同单层连接(4)PCB层预处理编辑元件属性在导入PCB之前,必须正确填写元件的封装(PCB Footprint)参数整体赋值(框住多个元件,然后Edit Properties),出现如图所示的property editer;编辑pcb footPrint(与allegro pcb中的元器件的封装名称相一致);part Perference是网表导入allegro pcb后的元器件名称;还能进行其他属性编辑;还可添加其他需要的属性;(6)分类属性编辑Edit Properties-->New ColumnClass:IC(IC,IO,Discrete三类,在PCB中分类放置)放置定义房间(Room)Edit Properties-->New ColumnRoom添加文本和图像添加文本、位图(Place...)6、原理图绘制的后续处理(切换到项目管理器窗口,选中*.DSN文件,然后进行后处理————DRC检查、生成网表及元器件清单)(1)设计规则检查(Tools-->Design Rules Check...)Design Rules Checkscope(范围):entire(全部)/selection(所选)Mode(模式):occurences(事件:在同一绘图页内同一实体出现多次的实体电路)instance(实体:绘图页内的元件符号)Action(动作):check design rules/delete DRCReport(报告):Create DRC markers for warn(在错误之处放置警告标记)Check hierarchical port connection(层次式端口连接)Check off-page connector connection(平坦式端口连接)Report identical part referenves(检查重复的元件序号)Report invalid package (检查无效的封装)Report hierarchical ports and off-page connector(列出port和off-page 连接)Check unconnected netCheck SDT compatibleReport all net names(2)元件自动编号(Tools -->Annotate)scope(范围):Update entire design/selectionAction:Incremental reference update 增长的自动编号unconfitional reference updatereset part reference to "?" 将编号重置为“?”;Add/delete Intersheet Reference(在分页图纸的端口的序号加上/删除图纸的编号)Reset reference numbers to begin at 1 each page原理图每个页重置编号从1开始(3)自动更新器件或网络的属性(Tools-->Update Properties...)7、生成网表在原理图检查无误后Tools-->Create NetLists生成网表;二、Cadence PCB editor绘制PCB板步骤:焊盘设计,零件封装→创建电路板,机械结构尺寸层叠结构预定义→导入网表→设定电器规则线宽线距→布局布线→布线后调整零件编号,丝印,DRC检查→设计输出gerber文件Drill文件图纸1、Cadence SPB15.7 Pad Designer画电子元器件的焊盘;(1)File-->New创建文件Through为通孔类热焊盘;Single为表贴类热焊盘中间层:固定的或者任意的单位:英制mils;公制mm;根据情况选择;Decimal Places 精度;钻孔类型,钻孔直径,偏移坐标(2)层的定义:BEGIN Layer(Top)层:REGULAR-PAD <THERMAL-PAD =ANTI-PAD END LAYER(同BEGIN,常用copy begin layer, then paste it)TOP SOLDERMASK:只定义REGULAR-PAD ,大于(Begin layer层regular-pad,约为1.1~1.2倍)BOTTOM SOLDERMASK(同Top soldermask,常用Top soldermask, then paste it)PASTEMASK _TOP(同BEGIN,常用copy begin layer, then paste it)设置高度,宽度,偏移坐标原点的x,y值;(3)A:规则的焊盘可以在Geometry中选择圆形,正方形,长方形,椭圆形等;B:不规则焊盘需要导入设计好的图形;图形通过Allegro PCB Editer设计;File -->new -->shape symbol;设计好begin层和soldermask_top层的图形后设置放置路径setup--user preference editer 选择Design_pathsCadence PCB editor零件封装手工建立元件(主要包含四项:PIN;Geometry:SilkScreen/Assembly;Areas:Boundary/Height;RefDes:SilkScreen/Display)注意:元件应放置在坐标中心位置,即(0,0)(1)、File →n ew→package symbol(2)、设定绘图区域:Setup →Drawing size →Drawing parameter...设置栅格点:setup →Grids;(3)、添加pin:选择padstack ,放置。

CADENCEPCB设计中文教程

CADENCEPCB设计中文教程CADENCE是一种著名的电子设计自动化(EDA)工具,广泛应用于PCB (Printed Circuit Board,印刷电路板)设计。

CADENCE PCB设计软件在工业界具有广泛的应用,设计工程师可以使用CADENCE软件来设计和制造高品质的电路板。

本教程将向您介绍CADENCE PCB设计的基本概念和步骤。

一、CADENCEPCB设计的基本概念1.原理图设计:首先,在CADENCE工具中,您需要绘制电路的原理图。

原理图是电路的图形表示,包含电路中所有元件(如电阻、电容、晶体管等)的符号和连接线,以及它们之间的连接关系。

您可以使用CADENCE工具库中提供的元件符号来绘制原理图。

2.元件库管理:CADENCE提供了一个元件库管理工具,您可以在其中创建和管理自定义的元件库。

通过元件库管理,您可以将常用的元件符号保存在库中,以便在不同的电路设计中重复使用。

3.PCB布局设计:在完成原理图设计后,您需要将电路中的元件布局在PCB上。

PCB是一个具有金属层、绝缘层和焊盘的印刷电路板。

CADENCE提供了一个布局工具,您可以在其中将各个元件放置在PCB上,并绘制它们之间的连接线。

4.线路连接:在CADENCE中,您可以使用布线工具将电路中的元件之间连接起来。

通过布线工具,您可以选择不同的线宽和线间距,并确保线路之间没有短路和断路。

布线完成后,您可以使用CADENCE的自动布线功能来优化线路布线,并提高电路性能。

5.电气规则检查:在完成PCB布局和布线后,您需要进行电气规则检查。

电气规则检查可以帮助您查找布局中的错误,如未连接的元件、未连接的引脚、引脚冲突等。

CADENCE提供了一些强大的电气规则检查工具,可帮助您轻松检查电路的正确性。

6. 制造文件生成:最后,在完成PCB设计后,您需要生成制造文件。

制造文件包括Gerber文件、钻孔文件和BOM(Bill of Materials,物料清单)等。

Cadence自学笔记笔记

Cadence⾃学笔记笔记Cadence SPB15.7 快速⼊门视频教程⽬录Capture CIS 原理图及元件库部分第1-15讲第1讲课程介绍,学习⽅法,了解CADENCE软件Cadence下⼏个程序说明Design Entry CIS 系统级原理图设计Design Entry HDL 芯⽚设计Layout plus orcad ⾃带的pcb板布局布线⼯具,功能不是很强⼤,不推荐使⽤Pcb Editor Pcb librarian Cadence带的PCB布局布线封装设计PCB Router pcb⾃动布线Pcb SI SigXplorer Pcb电路板信号完整性仿真OrCAD Capture CIS 对元件管理更⽅便相对于OrCAD CaptureI 放⼤O 缩⼩页⾯属性设置options Design Templateoptions Schematic Page Propertie s第2讲创建⼯程,创建元件库原理图元件库,某元件分成⼏个部分,各部分间浏览ctrl+N ctrl+B元件创建完后修改footprint封装,options Package Properties第3讲分裂元件的制作⽅法1、homogeneous 和heterogeneous 区别homogeneous,芯⽚包含⼏个完全相同的部分选择该模式,画好第⼀个part后,后⾯的part会⾃动⽣成,因为完全⼀样。

但是引脚编号留空了,要⾃⼰再设置引脚编号。

heterogeneous芯⽚包含⼏个功能部分,可按照功能部分分成⼏个部分。

ctrl+N ctrl+B切换分裂元件的各个部分原理图画完之后,要对各元件⾃动编号,在项⽬管理窗⼝选择项⽬,点击tools annotate,在Action下⾯选择相应的动作。

2、创建homogeneous类型元件3、创建heterogeneous类型元件第4讲正确使⽤heterogeneous类型的元件1、可能出现的错误Cannot perform annotation of heterogeneous part J?A(Value RCA_Octal_stack ) part has not been uniquely group(using a common User Property with differing Values) or the device designation has not been chosen2、出现错误的原因分裂元件分成⼏个part,并且⽤了多⽚这样的分裂元件。

cadence-PCB-画图(傻瓜教程快速入门)

cadence画PCB板傻瓜教程(转帖)复制于某网站,谢谢。

拿出来分享吧,希望对初学者能有帮助,可以很快了解Cadence的使用,谢谢共享者。

一.原理图1.建立工程与其他绘图软件一样,OrCAD以Project来管理各种设计文件。

点击开始菜单,然后依次是所有程序—打开cadence软件—》一般选用Design Entry CIS,点击Ok进入Capture CIS。

接下来是File-—New——Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。

2.绘制原理图新建工程后打开的是默认的原理图文件SCHEMATIC1 PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似.点击上侧工具栏的Project manager(文件夹树图标)或者是在操作界面的右边都能看到进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等.1) 修改原理图纸张大小:双击SCHEMATIC1文件夹,右键点击PAGE1,选择Schematic1 Page Properties,在Page Size中可以选择单位、大小等;2)添加原理图库:File--New--Library,可以看到在Library文件夹中多了一个library1.olb的原理图库文件,右键单击该文件,选择Save,改名存盘;(注意:在自己话原理图库或者封装库的时候,在添加引脚的时候,最好是画之前设定好栅格等参数,要不然很可能出现你画的封装,很可能在原理图里面布线的时候通不过,没法对齐,连不上线!)3) 添加新元件:常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。

右键单击刚才新建的olb库文件,选New Part,或是New Part From Spreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。

Cadence学习笔记4PCB板设计

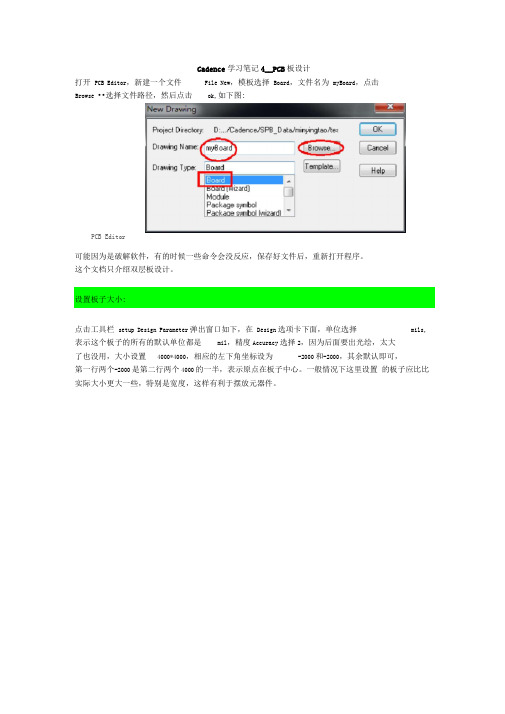

Cadence 学习笔记4__PCB 板设计打开 PCB Editor ,新建一个文件File New ,模板选择 Board ,文件名为 myBoard ,点击 PCB Editor可能因为是破解软件,有的时候一些命令会没反应,保存好文件后,重新打开程序。

这个文档只介绍双层板设计。

设置板子大小:点击工具栏 setup Design Parameter 弹出窗口如下,在 Design 选项卡下面,单位选择 mils ,表示这个板子的所有的默认单位都是 mil ,精度Accuracy 选择2,因为后面要出光绘,太大了也没用,大小设置4000*4000,相应的左下角坐标设为-2000和-2000,其余默认即可,第一行两个-2000是第二行两个4000的一半,表示原点在板子中心。

一般情况下这里设置 的板子应比比实际大小更大一些,特别是宽度,这样有利于摆放元器件。

Browse ••选择文件路径,然后点击ok ,如下图:〕D 『曲电T jQrMLMrrjiParaTiEtiTi dewiphcn pecim Ifie T sn上二号1 t-iiD_gh a pup •中 ireu tlplcns sie^v L. C. D_. aid Oll^. [he 厲店1 由匕 d-emng 阳畝 ii liw LI 丹i Uh 补■・ Miv a Indi 祸 4 v A, M 匚 or 口怙L Fir 匚山*,冯 $UVL ,「I O Utw Unit; k Milrriuivit cr 匚爭* tjmmg 传 ai 辜 A' A3..A4. or QthmrIf png 口fE *百Uh 辜或E 黄 i$ dics eti th$ 甸十才 miimatiMl 卩 h 旳目臍I he cCnV-s hr the SZE.亡r t -e C wg Exterts sectcriOK Cincd -p <接着设置栅格点大小,点击工具栏 setup Grids ,勾选“ GridsOn'显示栅格点,在非电气属性区域Non-Etch 设置为25mil ,表示布局 <摆放元件)时的最小栅格点为 25mil ,在电气属性区域All Etch 及下面的TOP 和BOTTOM 设为5mil ,表示布线时的最小栅格点为5mil ,在 All Etch 这里的 Spaceing x 和y 可以设置所有层的电气属性栅格点,在下面的TOP 和BOTTOM 可以单独设置各个层,这里默认的是两层,如果还有更多的层,都会在这里显示。

CADENCEPCB设计布局与布线

CADENCEPCB设计布局与布线CADENCEPCB设计工具是电子工程师在进行PCB电路板设计时经常使用的软件。

其强大的功能使得设计师可以进行布局和布线,确保电路板的性能和可靠性。

下面将详细介绍CADENCEPCB设计的布局和布线过程。

首先是布局过程。

布局是指在PCB上放置电子元器件和确定它们之间的物理布置。

布局的目标是优化电路板的性能、减小电磁干扰并提供良好的散热。

以下是CADENCEPCB设计中的布局步骤:1.确定布局约束:首先,设计师需要根据电路的要求和特定的应用环境,确定布局的约束条件,如电源分配、信号完整性、热管理等。

这些约束条件将指导接下来的布局和布线过程。

2.放置电子元器件:根据电路图和设计要求,将电子元器件在PCB上进行合理的放置。

重要的因素包括元器件之间的物理距离,信号和电源线的长度和走向,以及避免冲突和干扰的布局。

3.优化布局:在放置元器件之后,设计师需要优化布局,以确保信号完整性。

这包括优化电源和地平面的布置,减小信号线的长度和交叉,并提供良好的散热条件等。

4.电源和地平面设计:在布局过程中,需要合理设计电源和地平面,以提供足够的电源稳定性和地电流供应。

这需要将电源和地线走线得当,并采用合适的电容和电感等元件进行滤波和终端处理。

接下来是布线过程。

布线是指设计师将电子元器件之间的连线进行优化和优化,以确保信号的完整性、最小化电磁干扰并满足设计约束条件。

以下是CADENCEPCB设计中的布线步骤:1.设计路由规则:在进行布线之前,设计师需要制定一个路由规则,包括最小线宽和线间距、阻抗控制、信号类型和电源线与地线的关系等。

这些规则将指导后续的布线过程。

2.自动布线:CADENCEPCB设计工具提供了自动布线工具,可以根据预先设定的规则和优化目标,自动生成布线方案。

设计师可以根据需要进行调整和优化。

3.手动布线:对于一些复杂的板线、高速信号或特殊需求,手动布线是必要的。

对于这些情况,设计师需要手动布线,根据设计约束和优化目标,确定线路的走向和走线方式,并避免冲突和干扰。

Cadence PCB拼板

拼板设计介绍孙海峰鉴于贵公司多使用拼板方式加工PCB板,我向您介绍一下两种拼板设计方法:第一种方法:Sub-Drawing方式使用subdrawing方式将PCB的布局、布线以及铜皮设置都Export成对应的subdrawing文件,然后在新的PCB中导入这些文件,可以实现拼板设计。

一、从已有PCB导出布局布线铜皮等数据;1、准备好已经完成的PCB,如下图:2、导出PCB走线/网络/过孔:执行File/Export/Sub-drawing命令,在Find栏,选择Clines、Vias,然后框选整个PCB,在控制窗口输入x 0 0,Enter,这可以将PCB走线保存为*.clp文件;3、导出PCB上的Symbol和Pin:执行File/Export/Sub-drawing命令,在Find栏,选择Symbols、Pins,然后框选整个PCB,在控制窗口输入x 0 0,Enter,这可以将PCB上零件布局保存为*.clp文件;4、导出PCB上的铜皮设置:执行File/Export/Sub-drawing命令,在Find栏,选择Shapes,然后框选整个PCB,在控制窗口输入x 0 0,Enter,这可以将PCB上铜皮设置保存为*.clp文件;二、创建新的PCB,导入以上各层对应Sub-drawing,即可重建该PCB,但没有Outline(没有导出outline的数据),以便后期做拼板新的outline外框。

——注意导入Sub-drawing时候,必须先设置好新的PCB叠层,要和之前的PCB 叠层设置一致方可!(包括叠层名称和正负片的选择)——注意导入布局等时,要做好Options中的选择,如下图。

注意坐标的设置,则可以放置许多相同的PCB进去,最后再画出外框OUTLINE 即可。

第二种方法:Design Partition的方式Design Partition需要与L Option配合使用,需要升级现在的Allegro L,而对于现在贵公司的产品,不需要升级,因此,经过我们工程师善良,不建议使用该方法。

pcb课程设计cadence

pcb课程设计cadence一、教学目标本课程旨在通过Cadence软件的使用,让学生掌握PCB(印刷电路板)设计的基本原理和方法,培养学生的实际操作能力和创新思维。

知识目标:使学生了解PCB设计的基本概念、流程和规范,熟悉Cadence软件的操作界面和功能模块。

技能目标:培养学生运用Cadence软件进行PCB设计的能力,包括原理图绘制、元件封装、线路布局、布线规则设置、DRC(设计规则检查)和Gerber文件输出等。

情感态度价值观目标:激发学生对PCB设计兴趣,培养学生的创新意识、团队协作能力和工程项目实践能力。

二、教学内容本课程的教学内容主要包括PCB设计的基本概念、Cadence软件操作、实际案例分析等。

1.PCB设计基本概念:介绍PCB的基本组成、设计流程、设计规范等。

2.Cadence软件操作:讲解Cadence软件的安装与启动、操作界面认识、原理图绘制、元件封装、线路布局、布线规则设置、DRC检查和Gerber 文件输出等。

3.实际案例分析:分析具体PCB设计案例,让学生动手实践,提高设计能力。

三、教学方法本课程采用讲授法、案例分析法、实验法等多种教学方法,以激发学生的学习兴趣和主动性。

1.讲授法:讲解PCB设计的基本概念、原理和Cadence软件操作方法。

2.案例分析法:分析实际案例,引导学生运用所学知识解决实际问题。

3.实验法:让学生动手实践,完成PCB设计案例,提高实际操作能力。

四、教学资源本课程的教学资源包括教材、Cadence软件、多媒体教学资料、实验设备等。

1.教材:选用权威、实用的PCB设计教材,为学生提供理论知识支持。

2.Cadence软件:为学生提供正版Cadence软件,便于学生动手实践。

3.多媒体教学资料:制作精美的PPT课件,辅助讲解和展示案例。

4.实验设备:配备必要的实验设备,如计算机、示波器等,保障实验教学的顺利进行。

五、教学评估本课程的评估方式包括平时表现、作业、考试和实践项目,以全面客观地评价学生的学习成果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Cadence学习笔记4__PCB板设计打开PCB Editor,新建一个文件File→New,模板选择Board,文件名为myBoard,点击Browse…选择文件路径,然后点击ok,如下图:可能因为是破解软件,有的时候一些命令会没反应,保存好文件后,重新打开程序。

这个文档只介绍双层板设计。

设置板子大小:点击工具栏setup→Design Parameter弹出窗口如下,在Design选项卡下面,单位选择mils,表示这个板子的所有的默认单位都是mil,精度Accuracy选择2,因为后面要出光绘,太大了也没用,大小设置4000*4000,相应的左下角坐标设为-2000和-2000,其余默认即可,第一行两个-2000是第二行两个4000的一半,表示原点在板子中心。

一般情况下这里设置的板子应比比实际大小更大一些,特别是宽度,这样有利于摆放元器件。

接着设置栅格点大小,点击工具栏setup Grids,勾选“Grids On”显示栅格点,在非电气属性区域Non-Etch设置为25mil,表示布局<摆放元件)时的最小栅格点为25mil,在电气属性区域All Etch及下面的TOP和BOTTOM设为5mil,表示布线时的最小栅格点为5mil,在All Etch这里的Spaceing x和y可以设置所有层的电气属性栅格点,在下面的TOP和BOTTOM可以单独设置各个层,这里默认的是两层,如果还有更多的层,都会在这里显示。

设置板框:板框大小就是做出来的板子的实际大小,根据实际情况确定。

点击Add→line或左侧工具栏的划线图标,在右侧工具栏选择Options,然后选择类Board Geometry和子类Outline,其余默认,如下图。

其右上角有三个很小的图标,可以点击右上角的图标将其展开,否则鼠标移开后会自动收缩,展开后也可以点击将其收缩。

如果不小心点击关掉了这个小窗口,可以在上方工具栏View→Windows勾选Options,同样的Visibility 和Find都可以这么操作。

如果Options、Visibility和Find窗口都是点击了展开,那么可以点击将其中一个置于最前。

用输入坐标的方式确定板框大小,大小为2760*2160,在下方命令行输入x 1380 1080回车,确定了第一个点坐标;然后输入ix -2760回车,向左移动2760mil;输入iy -1080回车,向下移动1080mil;输入ix 2760回车,向右移动2760mil;输入iy 1080回车,向上移动1080mil。

最后鼠标右击Done结束,可以看见白色的边框线。

导角:就是将矩形边框的四个直角变成圆弧,免得割伤手,工具栏Manufacture→Dimension/Draft→Filet,在右侧工具栏设置大小,一般的100mil即可,这里写100mil,然后点击矩形边框一个直角的相邻两边,如下图,直角变成圆弧了。

同样的设置其余角,设置好后右击Done结束。

如果想改变导角大小,激活命令后直接输入新的导角大小,然后点击各个角的相邻边即可。

注意,Z-copy命令产生的板边框不能设置导角,必须是line的方式画的边框才行。

允许布线区:点击上方工具栏Setup→Areas→Route Keepin,在右侧工具栏options中选择类Route Keepin和子类All,Type为无填充Unfilled,其余默认,如果All最左边的小方块是黑色的,表示这个没有显示,点击这个黑色的小框变成和All左边一样的黄色,表示可以显示了。

允许布线区一般在板框内100mil,即长和宽都小200mil,距板边太近会在生产时被夹具夹断走线。

输入坐标即可,这里的大小为2560*1960,默认颜色为黄色。

也可以用一种快速放置的方式,在放好板边框后,点击上侧工具栏Edit→Z-copy,options 选择类Route Keepin和子类All,下面的Size选择Contract,表示新的边框在原来边框内部,Expand表示在外部,Offset表示偏移多少,设为100,单位是在设置板子大小时设置的mil,如下图。

然后点击刚才设置的板子边框的任意一点,就出现了黄色的允许布线区,右击Done结束。

快速创建:这里介绍快速创建板框和允许布线区,点击上侧工具栏Setup→Outlines→Board Outline弹出下面窗口,如果还没有创建就会默认选择Create,Board Edge Clearance表示板框和允许布线区的间距,下面如果选择Draw Rectangle,就可以在板子中用鼠标点击或输入坐标创建,输入的坐标是矩形的两个对角的坐标,最后点击ok结束。

如果选择的不是Draw Rectangle而是Place Rectangle,就会显示下图右的样子,分别输入板框的宽度和高度,用鼠标点击或在命令行输入矩形左下角的坐标即可。

如果选择的是Draw Polygon,表示可以画出由直线和直角构成的任意形状,直接鼠标点击或输入坐标即可,如下图。

如果已经创建了这个东西,下次打开这个窗口的时候,会默认选择Edit,然后在下面输入板框和允许布线区的间距再点击ok即可。

如果此时选择Create,会提示删除当前的板框和允许布线区,因为一个板子只能有一个。

同样的,可以选择Move移动或Delete删除。

允许摆放区:点击上方工具栏Setup→Areas→Package Keepin,在右侧工具栏options中选择类Package Keepin和子类All,Type为无填充Unfilled,Shape grid选择Current grid,其余默认。

同样的,在允许布线区内100mil,即长和宽都小200mil,距离太近会在生产时被夹具夹断走线。

输入坐标即可,这里的大小为2360*1760,默认颜色为紫色。

设置好后如下图:同样可以用一种快速放置的方式,在放好板边框后<也可以用允许布线区,那么应该是偏移100),点击上侧工具栏Edit→Z-copy,options选择类Package Keepin和子类All,下面的Size选择Contract,表示新的边框在原来边框内部,Expand表示在外部,Offset表示偏移多少,设为200,单位是在设置板子大小时设置的mil,如下图。

然后点击刚才设置的板子边框的任意一点,就出现了紫色的允许摆放区,右击Done结束。

放置安装孔:可以直接放置机械孔,点击上方工具栏Place→Manually,先在Advanced Settings选项卡下面勾选Library,表示在自带库和指定路径中搜索元件,指定的路径就是做封装时在工具栏Setup→User preferences→Paths→Library的padpath和psmpath添加的路径。

如果勾选AutoHide表示放置元件时自动隐藏这个窗口,放置完成后又显示,如下图左,然后回到Placement List选项卡,如下图右,选择Mechanical symbols,下面会显示可用的机械零件,也就是机械孔,勾选一个放置即可,现在选择MTG156,右下方出现预览,直接放置到板子中即可,也可以通过输入坐标的方式放置,也就是勾选这个之后,在下方命令栏输入坐标回车,如x 0 0。

注意每次勾选只能放置一次,下次放置还要勾选。

记得放完后要点击ok 关闭窗口,如果点击Cancel就取消了刚才的放置。

也可以自己做一个机械孔,先做一个带有Flash的通孔类焊盘,命名为installhole.pad,添加好路径,在做一个封装installHole.dra,以机械零件的方式加入该焊盘,在封装中加入Place_Bound_Top和Ref,Ref在Assembly层的元件中心输入*即可,封装如下图所示。

然后在PCB设计中点击上方工具栏Place Manually,先在Advanced Settings选项卡下面勾选Library,再在Placement List选项卡选择Package symbols,如下图,勾选INSTALLHOLE,右下方出现预览,鼠标移到PCB板中会看到一个机械孔,点击鼠标放置或输入坐标放置都可以,注意每次勾选只能放置一次,下次放置还要勾选,放置完成之后点击ok结束放置。

安装孔和与元件一样,要在允许摆放区内。

这里顺便介绍一下Move命令,点击Edit→Move或点击上侧工具栏图标,可以在右侧Find中勾选要选中的类型,然后选中元件、边框、线等移动,此时可以直接点击放置,也可以输入坐标放置。

导入网表:打开PCB板后,点击File→Import→Logic,弹出下面的窗口,在Cadence选项卡选择Design entry HDL,Always和Import changes only,下面的Import directory选择原理图目录下的allegro目录,然后点击Import Cadence按钮,显示下面的进度条,最后弹出一个报告,报告的最后会说明有没有错误,如果有警告,如下图,一定要解决,仔细看前面的内容可以知道具体错误。

解决了错误之后,可以成功导入网表,并显示下面的提示信息打开上方工具栏Place→Manually,看到显示所有未摆放的元件,勾选任意一个可以看到右下角显示预览,如果没有显示,可能是封装错误,或封装路径没有添加<在PCB Editor里面点击工具栏Setup→User Preferences→Path→Library→padpath和psmpath添加封装所在路径,不支持子目录搜索,一个完整的封装应该包括焊盘文件*.pad,数据文件*.psm,Device 文件*.txt,封装文件*.dra)摆放元件的4种方式:A.手动一个个摆放:点击工具栏Place→Manually,弹出上图的窗口,可以在Advanced Settings选项卡下面勾选AutoHide,表示放置时隐藏窗口,放置完成后又显示,删除PCB 中的某个原件后,这里又显示该元件,因为这里都是没有摆放的元件。

B.原理图交互式摆放:打开原理图组件OrCAD Capture CIS,点击上侧工具栏Options→Preference,打开选项卡Miscellaneous,勾选Enable Intertool Communication,表示打开原理图组件和PCB组件的数据传递工具,这样就可以将原理图组件中的一些元件属性或原理图属性传递到PCB组件中,传递的途径是网表的导出与导入。

下面还有个Allow component move with connectiviy changes,也可以勾选上,画线时方便。

接着在PCB Editor中点击Place→Manually激活摆放元件命令,在原理图中选一个元件右击选择最后一项PCB Editor Select,将鼠标移动到PCB Editor中,鼠标上会悬挂该元件摆放即可C.原理图整页摆放:在OrCAD Capture CIS项目树目录里选一个原理图页,如第一页miniSystem_page1,点击工具栏Edit→Browse→Parts弹出下面的窗口,选择默认的即可,点击ok然后在弹出的窗口中按住Shift用鼠标点击选择所有的元件,点击工具栏Edit→Properties,弹出下面的窗口,点击New新建一个属性,输入属性名和属性值如下,点击ok后在窗口右侧显示一个PAGE属性,所有的元件都有这个属性而且属性值都为1,点击ok即可<要删除该属性就选中该列点击Remove),其它各页都这样设置,Name都为PAGE,Value不同,设为页面编号即可。