Altera公司FPGA的配置

FPGA 协议实现配置-ALTERA

2011年5月Altera 公司订阅版权© 2011 Altera 公司。

保留所有权利。

ALTERA 、ARRIA 、CYCLONE 、HARDCOPY 、MAX 、MEGACORE 、NIOS 、QUARTUS 以及STRATIX 均在美国专利和商标事务所进行了注册,是Altera 公司在美国和其他国家的商标。

所有其他商标或者服务标记的所有权属于其各自持有人,/common/legal.html 对此进行了解释。

Altera 保证当前规范下的半导体产品性能与Altera 标准质保一致,但是保留对产品和服务在没有事先通知时的升级变更权利。

除非与Altera 公司的书面条款完全一致,否则Altera 不承担由此处所述信息、产品或者服务导致的责任。

Altera 建议客户在决定购买产品或者服务,以及确信任何公开信息之前,阅读Altera 最新版的器件规范说明。

101 Innovation DriveSan Jose, CA 95134反馈FPGA 协议实现配置Altera 新的器件配置模式——协议实现配置(CvP),通过结合PCI Express ®来配置Altera 28-nm Arria ® V、Cyclone ® V 和Stratix ® V FPGA 的内核架构。

CvP 能够降低产品成本,减小电路板面积,同时简化了软件应用模型,具备可靠的现场系统更新功能。

此外,嵌入式自治PCIe IP 内核有助于确保设计满足PCIe 上电时序要求,FPGA 内核架构配置时间对其没有影响,保证了各种基于PCIe 计算机平台上广泛的互操作性。

引言PCIe 技术替代了PCI 成为处理器和被监控设备之间的标准控制平面接口。

自从2005年推出以来,FPGA 设计人员在FPGA 和处理器之间已经广泛使用了PCIe 接口。

现在的FPGA 包括嵌入式PCIe 内核,它用作端点或者根端口。

Altera_FPGA_配置模式

FPGA配置模式时间:2011-09-12 23:15:16 来源:作者:FPGA有多种配置模式:并行主模式为一片FPGA加一片EPROM的方式;主从模式可以支持一片PROM编程多片FPGA;串行模式可以采用串行PROM编程FPGA;外设模式可以将FPGA作为微处理器的外设,由微处理器对其编程。

如何实现快速的时序收敛、降低功耗和成本、优化时钟管理并降低FPGA与PCB并行设计的复杂性等问题,一直是采用FPGA的系统设计工程师需要考虑的关键问题。

如今,随着FPGA向更高密度、更大容量、更低功耗和集成更多IP的方向发展,系统设计工程师在从这些优异性能获益的同时,不得不面对由于FPGA前所未有的性能和能力水平而带来的新的设计挑战。

在很多项目设计中采用Altera 公司基于SRAM架构Cyclone系列器件。

Cyclone器件与其他FPGA器件一样是基于门阵列方式为用户提供可编程资源的,其内部逻辑结构的形成是由配置数据决定的。

这些配置数据可通过多种模式加载到FPGA内部的SRAM中,由于SRAM的易失性,每次上电时,都必须对FPGA进行重新配置。

1 Cyclone FPGA 配置模式Cyclone系列FPGA器件配置方案主要有三种,包括使用低成本配置芯片的主动串行(AS)配置、被动串行(PS)配置以及基于JTAG配置,实际应用时可以使用其中的一种方案配置Cyclone系列FPGA器件,来实现用户编程所要实现的功能。

Cyclone系列FPGA器件是用SRAM单元配置数据的。

由于SRAM掉电后容易丢失数据,配置数据必须即时地下载到上电的Cyclone器件中。

不同的配置模式可采用不同的专用配置芯片或数据源这三种配置模式是由Cyclone器件的模式选择引脚MSEL1和MSEL0的高低电平来决定的,如果你的实际应用只要求单一的配置模式,可以把模式选择引脚连接到VCC端或接地端在切换引脚的过程中,器件的运行状态不会被影响。

alterafpga配置

alterafpga配置配置是连接FPGA软件设计到硬件功能实现的桥梁,配置电路部分有误,配置文件无法下载到配置器件中,对FPGA编程,则再好的设计都是浮云。

上电后,配置数据保存在配置RAM中,将配置数据载入配置RAM即是对FPGA编程。

配置方式有很多种,主要区别为FPGA所处的地位和打入数据的方式不同,其基本时序基本相同。

基本时序波形如下:配置过程主要由nCONFIG、nSTATUS、CONF_DONE以及可选的INIT_DONE四个状态信号控制。

一个器件完整的配置过程包括上电复位、配置、初始化三个阶段。

正常上电后,nCONFIG管脚被拉低,器件复位,此时配置RAM的所有内容被清空,所有I/O处于高阻态,其余三个状态信号亦均被拉低,复位结束后,FPGA释放nCONFIG管脚,使其被外部上拉电阻拉高,FPGA在nCONFIG检测到由低到高的跳变沿,配置开始,同时FPGA 采样MSEL的信号状态,决定接受何种配置模式。

随后,FPGA释放nSTATUS管脚,外不上拉电阻将其拉高,FPGA在nSTATUS管脚检测到由低到高的跳变沿,表示FPGA开始接受数据。

配置数据由DATA管脚打入,配置时钟经DCLK管脚送入(被动方式下,主动方式DCLK 由FPGA提供),配置数据在上升沿锁存至FPGA中,配置数据全部打入到FPGA后,FPGA释放CONF_DONE管脚,使其由外部上拉电阻拉高,说明配置结束,进入初始化过程。

INIT_DONE是一个可选的指示初始化完成的信号(Device-Pin&Options-general),INIT_DONE在nCONFIG信号为低或配置的初期时为高电平,而当使能INIT_DONE的比特位(在配置数据的第一帧中)被配置进FPGA后,INIT_DONE信号变低,因此INIT_DONE信号由高到低的跳变表示FPGA配置真正开始,开始接收配置数据,如果INIT_DONE一直保持为高,说明FPGA没有接收到正确配置数据的文件头。

第三章 Altera的 CPLDFPGA

Altera的CPLD/FPGA器件系列 Altera的CPLD/FPGA器件 Altera的CPLD/FPGA的配臵

Altera是著名的PLD器件生产厂 商,Altera的PLD器件具有高性能、 高集成度和高性价比的优点,并且 Altera提供了全面的开发工具和丰 富的IP核、宏功能库等,因此 Altera的产品得到了广泛应用。

… 1 6个扩展乘积项

共享扩展项

去P IA

MAX7000器件的宏单元可以单独地配臵成 时序逻辑或组合逻辑工作方式。每个宏单元 由逻辑阵列、乘积项选择矩阵和可编程寄存 器等三个功能块组成。 MAX7000器件的宏单元中的逻辑阵列用来 实现组合逻辑,它为每个宏单元提供五个乘 积项。乘积项选择矩阵把这些乘积项分配到 “或”门和“异或”门作为基本逻辑输入,以 实现组合逻辑功能;或者把这些乘积项作为 宏单元中寄存器的辅助输入来实现清除、预 臵、时钟和时钟使能等控制功能。

APEX系列

APEX20K系列器件是第一个具有多核结构,支持可编程单芯片系统( SOPC)的PLD器件系列 。这种多核结构集成了乘积项、查找表和嵌入式存储器块( EAB)。乘积项结构适用于实现复 杂组合逻辑;使用查找表逻辑能实现增强型寄存器功能;查找表结构能有效实现数据通道、增 强型寄存器、数学运算及数字信号处理器等设计;嵌入式系统块( ESB)能实现多种存储功能 ,包括FIFO、双端口RAM及内容可寻址存储器(CAM)。 APEX20K系列器件的配臵通常是在系统上电时,通过存储一个 Altera串行PROM中的配臵数据 或者由系统控制器提供的配臵数据来完成。Altera提供ISP串行数据配臵芯片,如EPC1、EPC2 、EPC16;APEX20K具有优化的接口,允许微处理器串行或并行,同步或异步对其进行配臵,微 处理器将APEX20K作为存储器对待,重新配臵也很容易。APEX20K器件被配臵后,可以通过重新 复位器件、加载新数据的方法实现在线可配臵。 APEX20KE器件属于超级APEX20K器件,它支持先进的I/O标准和内容可寻址存储器(CAM), 并具有更多的全局时钟数、增强的“时钟锁定”时钟电路等附加特性。APEX20KE在APEX20K器 件基础上扩展到150万门。 APEXII器件结构与APEX20K器件结构一样,它集成了高速差分I/O,支持使用True-LVDS接口 。在True-LVDS接口中的并串转换、串并转换和CDS电路支持LVDS、LVPECL、HyperTransport和 PCML I/O标准。在一般用户I/O的Flexible-LVDS引脚提供附加的差分支持,增加了整个器件的 带宽,这种电路再加上增强型IOE及对大量I/O标准的支持,使得APEXII器件能满足高速接口的 需要。APEXII其间还具有其他的高性能特征,如双向双端口RAM、CAM、普通的PLL和大量的全 局时钟。

FPGA具体型号及参数

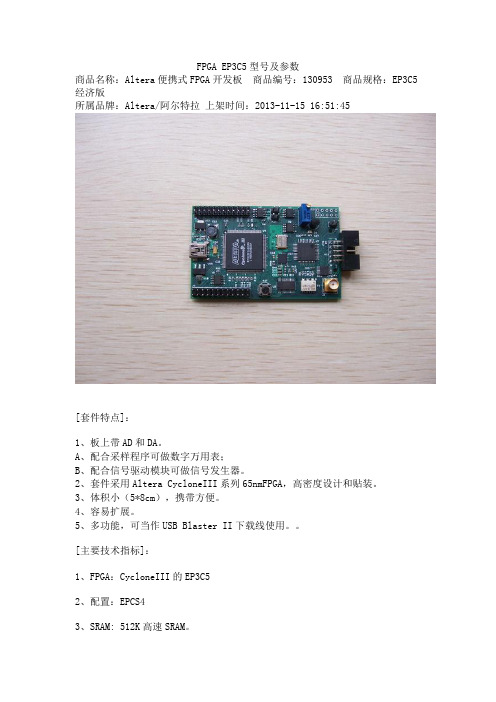

FPGA EP3C5型号及参数

商品名称:Altera便携式FPGA开发板商品编号:130953 商品规格:EP3C5经济版

所属品牌:Altera/阿尔特拉上架时间:2013-11-15 16:51:45

[套件特点]:

1、板上带AD和DA。

A、配合采样程序可做数字万用表;

B、配合信号驱动模块可做信号发生器。

2、套件采用Altera CycloneIII系列65nmFPGA,高密度设计和贴装。

3、体积小(5*8cm),携带方便。

4、容易扩展。

5、多功能,可当作USB Blaster II下载线使用。

[主要技术指标]:

1、FPGA:CycloneIII的EP3C5

2、配置:EPCS4

3、SRAM: 512K高速SRAM。

4、常用电压型DA :1 路10Bit,1.25 MHz maximum update rate

5、AD :1 路10Bit,1.25 MSPS

6、1个LED指示

7、1个复位按钮

8、24M有源晶振

9、2个24针扩展座,支持20个扩展IO,4个CLK输入。

10、四层板,通过全板EMC/EMI和SI仿真。

11、高速电流型DA:可选1 路14Bit 165MSPS(完全版才有此项)。

Altera FPGA配置及升级

Altera FPGA配置方式及升级方式(针对cyclone II器件)1、配置cyclone II FPGA对于altera fpga,主要配置方式为AS,PS,JTAG三种配置方式。

这几种配置方式在于电路上对器件配置方式引脚选择不同:如图1.1所示:图1.1注意1:对于快速AS模式,只支持配置芯片EPCS16,EPCS64;2:对于JTAG配置模式,只应用JTAG,该引脚连接到地;2、配置器件(图2.1):图2.13、FPGA配置方式具体分体3.1AS(Active Serial)配置:3.1.1原理AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持Cyclone系列。

使用Altera串行配置器件来完成。

Cyclone器件处于主动地位,配置器件处于从属地位。

AS配置器件采用四引脚接口处理:DCLK、DATA、ASDI、nCS;配置数据通过DATA0引脚送入FPGA。

配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

3.1.2电路连接方式(图3.1)图3.13.1.3配置时序(图3.2)图3.2在配置完成后到初始化完成所需要299个时钟周期(100M)3.1.4配置文件.pof .jic .rbf3.2PS(Passive Serial)配置方式3.2.1配置原理主动串行配置方式可以通过altera配置器件,一个下载电缆,或者通过一个主控制器,诸如MAX II器件、MCU等来配置FPGA。

配置数据通过DATA0在每个DCLK的上升沿送入器件。

FPGA配置方式选择引脚配置如图3.3所示图3.33.2.2电路连接:配置器件配置(图3.4)图3.4MAX II配置,图3.5图3.5MCU配置,图3.6图图3.63.2.3配置时序图3.73.2.4配置文件格式.rbf .hex .ttf3.3JTAG配置方式3.3.1原理对于cyclone II器件来说,JTAG配置方式优先于其他器件配置方式。

Altera公司FPGA的配置

10

(4)PCB电路板上的10针连接插头

PCB板上的10针插头连接到FPGA器件的编程 或配置引脚上,ByteBlaster下载电缆的10针插座 连接到PCB板上的10针插头,ByteBlaster电缆通 过10针插头获得电源并下载数据到FPGA器件上。

编辑ppt

11

2. ByteBlasterMV并行下载电缆

编辑ppt

4

(2)电缆插头与插座

ByteBlaster与PC机并口相连的是25针插头,与FPGA 应用电路PCB电路板相连的是10针插座。编程数据从PC机 并口通过ByteBlaster电缆下载到电路板。连接示意图如 图6.1所示。

注意:利用 ByteBlaster下载电缆配置/编程3.3V器 件(如FLEX10KA、MAX7000A器件)时,要将电缆的VCC脚 连到5.0V电源,而器件的VCC脚连到3.3V电源。FLEX10KA 和 MAX7000A器件能够耐压到 5.0V,因此,ByteBlaster 电缆的5.0 V输出不会对 3.3 V器件造成损害,但5.0V电 源中应连接上拉电阻。

编辑ppt

15

(3)电缆插头与插座

ByteBlasterMV的25针插头,与ByteBlaster 下载电缆的区别仅是第15脚不同,ByteBlaster 连到GND,而ByteBlasterMV连到VCC。

ByteBlasterMV的10针插座与ByteBlaster电 缆的10针插座完缆

针对FPGA器件不同的内部结构,Altera公司 提供了不同的器件配置方式。Altera FPGA的配 置可通过编程器、JATG接口在线编程及Altera在 线配置等方式进行。

Altera器件编程下载电缆的有: ByteBlaster并行下载电缆,ByteBlasterMV并行 下载电缆,MasterBlaster串行/USB通信电缆, BitBlaster串口下载电缆。

第1章 FPGA开发简介-Altera FPGA系统设计实用教程(第2版)-李莉-清华大学出版社

下载电缆

ByteBlaster II

USB-Blaster

Ethernet Blaster

(1)完全符合设计人员的设计思路,从功能描述开 始,到物理实现的完成。

(2)设计更加灵活。 (3)设计易于移植和更改。 (4)易于进行大规模、复杂电路的设计实现。 (5)设计周期缩短。

1.4.2 典型FPGA开发流程

电路功能设计

设计输入

编译 综合

功能仿真

FPGA适配(布局布线)

时序仿真

配置

硬件环境要求高,软件投资大,通用性强,不面向具体 公司的PLD器件。

PLD制造厂商开发的专用软件工具则具有硬件环境要求 低,软件投资小的特点,并且很多PLD厂商的开发工具 是免费提供的,因此其市场占有率非常大;缺点是只针 对本公司的PLD器件,有一定的局限性。

1.4 基于FPGA的开发流程

1.4.1 FPGA设计方法概论 FPGA的设计方法属于自上而下的设计方法

第1章 FPGA开发简介

1.1 可编程逻辑器件概述 1.2 FPGA芯片 1.3 FPGA开发工具 1.4 基于FPGA的开发流程

1.1 可编程逻辑器件概述

可编程逻辑器件(Programmable Logic Device,简

称PLD)

可编程逻辑器件

PLD

低密度 PLD

高密度 PLD

PROM

PLA

PAL

GAL

EPLD CPLD FPGA

70年代初

70年代末 80年代初

80年代中期

80年代中期 及以后

图1-1 PLD器件的发展流程

低密度PLD的基本结构参考图

输入项 乘积项

或项

输

输

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

•

针对FPGA器件不同的内部结构,Altera公司

提供了不同的器件配置方式。Altera FPGA的配

置可通过编程器、JATG接口在线编程及Altera在

线配置等方式进行。

•

Altera器件编程下载电缆的有:

ByteBlaster并行下载电缆,ByteBlasterMV并行

MAX9000(包括MAX9000A)、MAX7000S和MAX7000A

进行编程。ByteBlaster为FPGA提供了一种快速而

廉价的配置方法,设计人员的设计可以直接通过

ByteBlaster下载电缆下载到芯片中去。

(1)下载模式

ByteBlaster并行下载电缆提供两种下载模式: • ①Passive serial mode(PS,被动串行模式)

1. PS(被动串行)模式

•

在PS(被动串行)模式下,MasterBlaster

下载电缆和ByteBlasterMV下载电缆可以对单个

与多个APEXⅡ、APEX20K、Mercury、ACEX1K、

FLEX10K或 FLEX6000系列器件进行配置。在PS模

式,配置数据从数据源通过MasterBlaster下载

电缆和ByteBlasterMV下载电缆串行地传送到器

件,配置数据由数据源提供的时钟同步。

(1)PS模式单个器件的配置电路设计

•

PS模式可以完成对单个APEXⅡ、 NhomakorabeaPEX20K、

Mercury、ACEX1K、FLEX10K或 FLEX6000系列器件

的配置,配置电路如图6.2所示。

•

图中:除 APEX20KE、APEX20KC系列器件外,

APEXⅡ、APEX20K、Mercury、ACEX1K、FLEX10K

或 FLEX6000系列器件的编程或配置。

(1)JTAG模式单个器件的配置电路设计

•

JTAG模式可以完成对单个APEXⅡ、APEX20K、

Mercury、ACEX1K、FLEX10K或 FLEX6000系列器件

的配置,配置电路如图6.4所示。

以忽略。nCONFIG、MSELO、MSEL1引脚端应采用

支持非JTAG配置模式的方式连接,如果仅仅使用

JTAG配置模式,则nCONFIG引脚端应连接到VCC,

MSELO和MSELI引脚端应连接到地。

MasterBlaster电缆驱动器的参考电压VIO应与器

用于配置FLEX10K、FLEX8000和FLEX600O系列 器件。 • ②JTAG模式

采用工业标准的JTAG边界扫描测试电路(符 合IEEE 1149.1-1990标准)用于配置FLEX10K、 MAX9000、MAX7000S和 MAX7000A系列器件进行编 程。

(2)电缆插头与插座

• ByteBlaster与PC机并口相连的是25针插头,与FPGA 应用电路PCB电路板相连的是10针插座。编程数据从PC机 并口通过ByteBlaster电缆下载到电路板。连接示意图如 图6.1所示。

害,但5.0V电源中应连接上拉电阻。

•

ByteBlaster与PC机并口相连的是25针插头,在PS模

式下和在JTAG模式下的引脚信号名称是不同的,如表6.1

所示。

图6.1 ByteBlaster与PC并口连接示意图

•

ByteBlaster与FPGA应用电路PCB电路板相连

的是10针插座,在PS模式下和在JTAG模式下的引

插头,与PCB电路板相连的是10针插座。数据从PC机并行

口通过ByteBlasterMV电缆下载到电路板中。

•

注意:为了利用 ByteBlasterMV下载电缆配置1.5V

APEXⅡ、1.8V APEX20KE、2.5V APEX20K、Excalibur、

Mercury、ACEXIK和FLEX10KE器件,3.3V电源中应该连接

•

ByteBlasterMV并行下载电缆具有与PC机25

针标准并行口相连的接口,工作电压VCC支持

3.3V或5.0V,允许 PC机用户从MAX+PLUS或

QuartusⅡ开发软件中下载数据,通过PC机标准

并行口在线编程 MAX9000、MAX7000S、MAX7000A、

MAX7000B和MAX3000A系列器件;可配置 APEXⅡ、

间加入一根并行口连接电缆。

(4)PCB电路板上的10针连接插头

•

PCB板上的10针插头连接到FPGA器件的编程

或配置引脚上,ByteBlaster下载电缆的10针插

座连接到PCB板上的10针插头,ByteBlaster电缆

通过10针插头获得电源并下载数据到FPGA器件上。

2. ByteBlasterMV并行下载电缆

上拉电阻,电缆的VCC脚连到3.3V电源,而器件的VCCINT 引脚端连到相应的2.5V、1.8V或1.5V电源。对于PS配置, 器件的VCCIO引脚端必须连到2.5V或3.3V电源。对于APEX Ⅱ、Mercury、ACEX1K、APEX20K和 FLEX10KE系列器件的 JTAG在线配置,或MAX7000A和MAX3000A系列器件的JTAG在

• ⑤在QuartusⅡ软件的编程器中选择 Start按钮 开始编程或配置器件。ByteBlasterMV电缆 从 .sof 、 .pof文件中下载数据到目标器件。

主系统通用 10针标准 配置/下载接口

PIN1

目标板10针标准 配置接口

OTP配置器件插座

6.2使用ByteBlasterMV的两种配置模式

•

注意:利用 ByteBlaster下载电缆配置/编程3.3V

器件(如FLEX10KA、MAX7000A器件)时,要将电缆的VCC

脚连到5.0V电源,而器件的VCC脚连到3.3V电源。

FLEX10KA和 MAX7000A器件能够耐压到 5.0V,因此,

ByteBlaster电缆的5.0 V输出不会对 3.3 V器件造成损

下载电缆,MasterBlaster串行/USB通信电缆,

BitBlaster串口下载电缆。

1、ByteBlaster并行下载电缆

•

ByteBlaster并行下载电缆是一种连接到PC机

25针标准口(LPT口)的硬件接口产品。

ByteBlaster并行下载电缆可以对FLEX10K、

FLEX8000和 FLEX6000进行配置,也可以对

器件的VCCIO匹配。ByteBlasterMV电缆插座上的 引脚端6不连接。

图6.2 PS模式单个器件的配置电路

•

在图6.3电路中,在器件链中将每个器件的

nCEO引脚端连接到下一个器件的nCE引脚端,所

有其它配置引脚端应分别连接在一起,器件链中

的第一个器件的nCE引脚端连接到地,最后一个

器件的nCEO引脚端悬空。在PS模式中,由于所有

APEX20K(包括APEX20K、APEX20KE和APEX20KC)、

ACEX1K、Mercury、FLEX10K(包括 FLEX10KA

和FLEX10KE)、FLEX8000 和FLEX6000系列器件

及Excalibur嵌入式微处理器。

•

工作电压VCC支持3.3 V或5.0V。使用与

ByteBlaster并行口和BitBlaster串口下载电

上拉电阻应该连接到 MasterBlaster(VIO脚)

或ByteBlasterMV的电源。对于APEX20KE、

APEX20KC器件使用10 kΩ电阻上拉nCONFIG到 VCCINT。MasterBlaster和 ByteBlasterMV电缆的 电源电压VCC为3.3V或5.0V。插座上的引脚端6为 MasterBlaster电缆提供的VIO基准电压,VIO应与

•

ByteBlasterMV的10针插座与ByteBlaster电

缆的10针插座完全相同。

•

PCB电路板上的10针连接插头与采用

ByteBlaster下载电缆的方式完全相同。

(4)软件编程和配置步骤

•

使用 ByteBlasterMV电缆和 QuartusⅡ编

程器,对一个或多个器件进行编程或配置的步

骤如下:

① 对项目进行编译

QuartusⅡ编译器对 APEX Ⅱ、APEX20K、 Mercury和 Excalibur系列器件的配置自动产 生 .sof文件,为了对EPC配置芯片进行编程, 就要用到 .pof文件或JAM STAPL格式文件。

• ②连接 ByteBlasterMV电缆到 PC机的并行 口,将10针插座插到包含目标器件的电路板中, 电路板必须为 ByteBlasterMV电缆提供电源。 对于Windows NT操作系统,在使用 ByteBlasterMV电缆前必须安装驱动器。

具有标准的 JTAG接口,用于编程或配置 APEXⅡ、APEX20K、Mercury、ACEX1K、 Excalibur、FLEX10K、MAX9000、MAX7000S、 MAX7000A、MAX7000B和 MAX3000A系列器件。

(2)连接

•

ByteBlasterMV下载电缆与PC机并行口相连的是25针

的CONF-DONE引脚端连接在一起,器件链中的所

有器件初始化时同时进入用户模式。另外,由于

所有的nSTATUS引脚端连接在一起,如果任何一

个器件检测到错误,则整个器件链中断配置。

图6.3 PS模式多个器件的配置电路

2. JTAG摸式

•

在JTAG模式下,MasterBlaster通信电缆和

ByteBlasterMV下载电缆可以完成单个和多个

线编程,电缆的VCC引脚端则必须连接3.3V电源。器件的 VCCIO引脚端既可连到2.5V,也可连到3.3V电源上。