利用D触发器构成计数器

基于d触发器的3位格雷码计数器

基于触发器的3位格雷码计数器概述1. 本文将介绍基于d触发器的3位格雷码计数器的设计和工作原理。

2. 格雷码是一种二进制数的编码方式,相邻的两个数只有一位二进制位不同。

格雷码计数器是一种特殊的计数器,其计数规律符合格雷码的排列方式。

3. 我们将通过使用d触发器和逻辑门来设计一个3位格雷码计数器,并且详细分析其工作原理和电路结构。

d触发器1. d触发器是数字电路中常用的一种触发器,它采用时钟信号来控制数据输入,从而实现数据的存储和传递。

2. d触发器有一个数据输入端d和一个时钟输入端clk,当时钟信号发生上升沿时,d触发器会将d端的输入数据存储并输出。

3位格雷码计数器的设计1. 我们将使用三个d触发器和逻辑门来设计3位格雷码计数器。

假设三个d触发器的输入端分别为a、b和c,输出端分别为Qa、Qb和Qc。

2. 我们首先设计逻辑电路,根据格雷码的规律,确定d触发器的输入信号和逻辑门的连接方式。

3. 根据逻辑电路设计的结果,将三个d触发器和逻辑门连接起来,形成3位格雷码计数器的电路。

工作原理1. 当计数器处于初始状态时,三个d触发器的输出信号分别为000,表示计数器的初始值为0。

2. 当时钟信号发生上升沿时,逻辑门会根据当前状态来确定下一个状态的输入信号。

3. 经过逻辑门的处理,下一个状态的输入信号被送入对应的d触发器,从而使得计数器的值按照格雷码的规律递增。

总结1. 通过本文的介绍,我们了解了基于d触发器的3位格雷码计数器的设计方法和工作原理。

2. 格雷码计数器在数字逻辑电路中有着广泛的应用,其高效、稳定的特点使得它在实际工程中得到了广泛的应用。

3. 我们希望本文对读者对于数字电路设计和格雷码计数器有所启发,并对相关领域的学习和实践有所帮助。

为了进一步深入理解和学习基于d触发器的3位格雷码计数器,我们可以继续探讨一些具体的细节和应用。

逻辑门的应用1. 在3位格雷码计数器中,逻辑门起着至关重要的作用。

它们用于根据当前状态确定下一个状态的输入信号。

数字电路实验报告-用D触发器设计三位二进制加法计数器

电学实验报告模板实验原理1.触发器的触发方式(1)电平触发方式电平触发方式的特点是:CP = 1时,输出与输入之间通道“透明”,输入信号的任何变化都能引起输出状态的变化。

当CP = 0时,输入信号被封锁,输出不受输入影响,保持不变。

(2)边沿触发方式边沿触发方式的特点是:仅在时钟CP信号的上升沿或下降沿才对输入信号响应。

触发器的次态仅取决于时钟CP信号的上升沿或下降沿到达时输入端的逻辑状态,而在这以前或以后,输入信号的变化对触发器输出端状态没有影响。

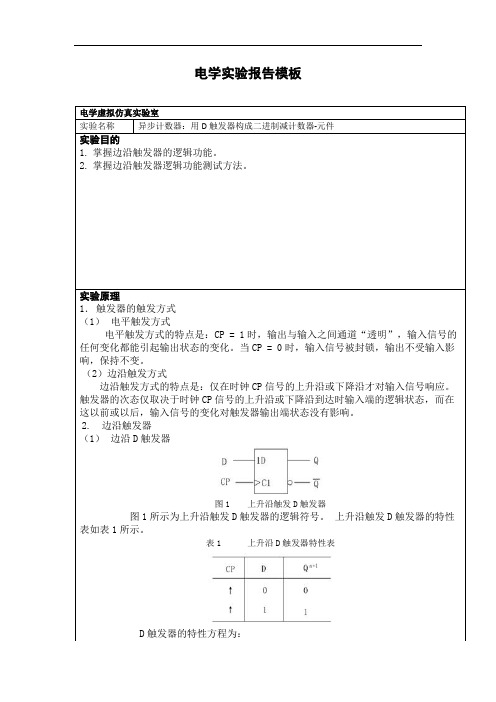

2. 边沿触发器(1)边沿D触发器图1 上升沿触发D触发器图1所示为上升沿触发D触发器的逻辑符号。

上升沿触发D触发器的特性表如表1所示。

表1 上升沿D触发器特性表D触发器的特性方程为:Q^(n+1) = D1.同步触发器的异步置位复位端电平触发器和边沿触发器都在CP时钟信号的控制下工作,这种工作方式称之为“同步”。

也把这类触发器称为同步触发器,以区别于基本RS触发器。

在小规模集成电路芯片中,触发器既能同步工作,又兼有基本RS触发器的功能。

例如。

图2所示的触发器。

这是上升沿触发D触发器,其中,SD(-)和RD(-)是异步置位复位端。

只图2 带有异步置位复位端的D触发器要在SD(-)或RD(-)加入低电平,立即将触发器置“1”或置“0”,而不受时钟信号CP和输入信号D的控制。

只有当SD(-)或RD(-)均处于高电平时,触发器才正常执行上升沿触发D触发器的同步工作功能。

实验仪器实验内容及步骤1.测试双D触发器74LS74的逻辑功能(1)74LS74引脚图图3 74LS74引脚图图3所示为集成电路芯片74LS74的引脚图。

芯片包含两个带有异步置位复位端的上升沿D触发器。

(1)测试74LS74的逻辑功能图4 测试74LS74的逻辑功能实验电路按照图4连接电路。

D触发器的Q和Q(-)(芯片5和6号引脚)各接一个发光二极管用以观察触发器的输出逻辑电平。

按照上面测试74LS112的逻辑功能同样的方法和步骤,测试74LS74的逻辑功能,将实验数据记录在表2。

数字电子技术基础第四章习题及参考答案

数字电子技术基础第四章习题及参考答案第四章习题1.分析图4-1中所示的同步时序逻辑电路,要求:(1)写出驱动方程、输出方程、状态方程;(2)画出状态转换图,并说出电路功能。

CPY图4-12.由D触发器组成的时序逻辑电路如图4-2所示,在图中所示的CP脉冲及D作用下,画出Q0、Q1的波形。

设触发器的初始状态为Q0=0,Q1=0。

D图4-23.试分析图4-3所示同步时序逻辑电路,要求:写出驱动方程、状态方程,列出状态真值表,画出状态图。

CP图4-34.一同步时序逻辑电路如图4-4所示,设各触发器的起始状态均为0态。

(1)作出电路的状态转换表;(2)画出电路的状态图;(3)画出CP作用下Q0、Q1、Q2的波形图;(4)说明电路的逻辑功能。

图4-45.试画出如图4-5所示电路在CP波形作用下的输出波形Q1及Q0,并说明它的功能(假设初态Q0Q1=00)。

CPQ1Q0CP图4-56.分析如图4-6所示同步时序逻辑电路的功能,写出分析过程。

Y图4-67.分析图4-7所示电路的逻辑功能。

(1)写出驱动方程、状态方程;(2)作出状态转移表、状态转移图;(3)指出电路的逻辑功能,并说明能否自启动;(4)画出在时钟作用下的各触发器输出波形。

CP图4-78.时序逻辑电路分析。

电路如图4-8所示:(1)列出方程式、状态表;(2)画出状态图、时序图。

并说明电路的功能。

1C图4-89.试分析图4-9下面时序逻辑电路:(1)写出该电路的驱动方程,状态方程和输出方程;(2)画出Q1Q0的状态转换图;(3)根据状态图分析其功能;1B图4-910.分析如图4-10所示同步时序逻辑电路,具体要求:写出它的激励方程组、状态方程组和输出方程,画出状态图并描述功能。

1Z图4-1011.已知某同步时序逻辑电路如图4-11所示,试:(1)分析电路的状态转移图,并要求给出详细分析过程。

(2)电路逻辑功能是什么,能否自启动?(3)若计数脉冲f CP频率等于700Hz,从Q2端输出时的脉冲频率是多少?CP图4-1112.分析图4-12所示同步时序逻辑电路,写出它的激励方程组、状态方程组,并画出状态转换图。

实验五 计数器及其应用

实验五计数器及其应用一、实验目的1.熟悉由集成触发器构成的计数器电路及其工作原理。

2.熟练掌握常用中规模集成电路计数器及其应用方法。

二、实验原理所谓计数,就是统计脉冲的个数,计数器就是实现“计数”操作的时序逻辑电路。

计数器的应用十分广泛,不仅用来计数,也可用作分频、定时等。

计数器种类繁多。

根据计数体制的不同,计数器可分成二进制(即2n进制)计数器和非二进制计数器两大类。

在非二进制计数器中,最常用的是十进制计数器,其它的一般称为任意进制计数器。

根据计数器的增减趋势不同,计数器可分为加法计数器——随着计数脉冲的输入而递增计数的;减法计数器——随着计数脉冲的输入而递减的,可逆计数器——既可递增、也可递减的。

根据计数脉冲引人方式不同,计数器又可分为同步计数器——计数脉冲直接加到所有触发器的时钟脉冲(CP)输入端;异步计数器——计数脉冲不是直接加到所有触发器的时钟脉冲(CP)输入端。

1.异步二进制加法计数器异步二进制加法计数器是比较简单的。

图32 (a)是由4个JK(选用74LS112集成片)触发器构成的4位二进制(十六进制)异步加法计数器,图32 (b)和(c)分别为其状态图和波形图。

对于所得状态图和波形图可以这样理解:触发器FFo(最低位)在每个计数沿(CP)的下降沿(1 → 0)翻转,触发器FF1的 CP 端接 FF0的 Q0端 .因而当 FF0(Q0)由1→0时,FF1翻转。

类似地,当 FF l(Q l)由1→0时,FF2翻转,FF2(Q2)由1→0时,FF3翻转。

(a)逻辑图(b)状态图(c)波形图图32 4位二进制(十六进制)异步加法计数器4位二进制异步加法计数器从起始态0000到1111共十六个状态,因此,它是十六进制加法计数器,也称模16加法计数器 (模M = 16)。

从波形图可看到,Q0的周期是CP周期的二倍;Q l是Q0的二倍,CP的四倍;Q2是Q1的二倍,Q0的四倍,CP的八倍;Q3是Q2的二倍,Q l的四倍,Q0的八倍,CP 的十六倍。

d触发器计数器原理

D触发器是一种基于数据输入(D)的触发器,它的输出状态会在时钟上升沿时发生改变。

D触发器有两个稳定的输出状态,通常表示为Q和Q'。

当输入的数据发生变化时,Q 和Q'的状态也会随之改变。

基于D触发器的计数器原理如下:

1. 首先,我们需要确定所需的计数器位数。

例如,如果要实现一个4位二进制计数器,就需要4个D触发器。

2. 然后,将这四个D触发器按照串行的方式连接起来,形成一个二进制计数器。

触发器的输入端分别连接到上一位的输出端和反相输出端,输出端连接到下一位的输入端。

3. 接着,设置一个时钟信号,用来控制计数器的计数速度。

时钟信号的频率决定了计数器的计数速度,可以通过调整时钟信号的频率来改变计数器的计数速度。

4. 然后,设置一个复位信号,用来将计数器的值清零。

当复位信号为高电平时,所有D 触发器的输出都被强制为低电平,从而将计数器的值清零。

5. 最后,根据需要,可以设置一个计数方向信号,用来控制计数器的计数方向。

当计数方向信号为高电平时,计数器按照正常的二进制计数方式进行计数;当计数方向信号为低电平时,计数器按照逆向的二进制计数方式进行计数。

通过上述步骤,就可以使用D触发器实现一个二进制计数器。

如果要实现其他进制的计数器,可以采用类似的方法,只需要相应地增加或减少D触发器的数量即可。

级《数字逻辑电路》实验指导书

课程名称:数字逻辑电路实验指导书课时:8学时集成电路芯片一、简介数字电路实验中所用到的集成芯片都是双列直插式的,其引脚排列规则如图1-1所示。

识别方法是:正对集成电路型号<如74LS20)或看标记<左边的缺口或小圆点标记),从左下角开始按逆时针方向以1,2,3,…依次排列到最后一脚<在左上角)。

在标准形TTL集成电路中,电源端V一般排在左上CC,7脚为端,接地端GND一般排在右下端。

如74LS20为14脚芯片,14脚为VCCGND。

若集成芯片引脚上的功能标号为NC,则表示该引脚为空脚,与内部电路不连接。

二、TTL集成电路使用规则1、接插集成块时,要认清定位标记,不得插反。

2、电源电压使用范围为+4.5V~+5.5V之间,实验中要求使用Vcc=+5V。

电源极性绝对不允许接错。

3、闲置输入端处理方法(1> 悬空,相当于正逻辑“1”,对于一般小规模集成电路的数据输入端,实验时允许悬空处理。

但易受外界干扰,导致电路的逻辑功能不正常。

因此,对于接有长线的输入端,中规模以上的集成电路和使用集成电路较多的复杂电路,所有控制输入端必须按逻辑要求接入电路,不允许悬空。

<也可以串入一只1~10KΩ的固定电阻)或接至某一 (2> 直接接电源电压VCC固定电压(+2.4≤V≤4.5V>的电源上,或与输入端为接地的多余与非门的输出端相接。

(3> 若前级驱动能力允许,可以与使用的输入端并联。

4、输入端通过电阻接地,电阻值的大小将直接影响电路所处的状态。

当R ≤680Ω时,输入端相当于逻辑“0”;当R≥4.7 KΩ时,输入端相当于逻辑“1”。

对于不同系列的器件,要求的阻值不同。

5、输出端不允许并联使用<集电极开路门(OC>和三态输出门电路(3S>除外)。

否则不仅会使电路逻辑功能混乱,并会导致器件损坏。

6、输出端不允许直接接地或直接接+5V电源,否则将损坏器件,有时为,一般取R 了使后级电路获得较高的输出电平,允许输出端通过电阻R接至Vcc=3~5.1 KΩ。

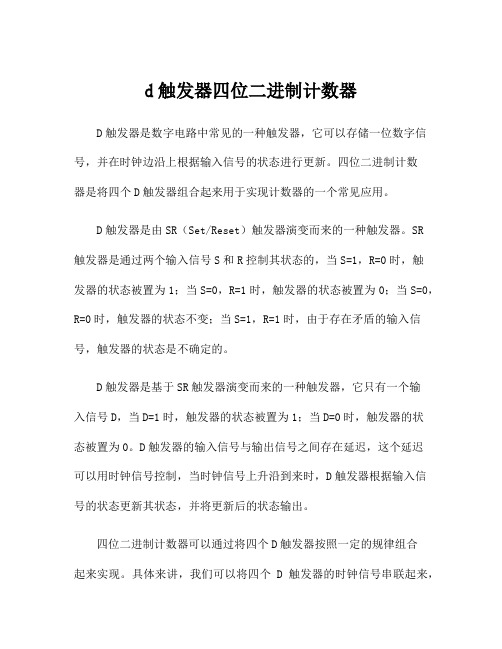

d触发器四位二进制计数器

d触发器四位二进制计数器D触发器是数字电路中常见的一种触发器,它可以存储一位数字信号,并在时钟边沿上根据输入信号的状态进行更新。

四位二进制计数器是将四个D触发器组合起来用于实现计数器的一个常见应用。

D触发器是由SR(Set/Reset)触发器演变而来的一种触发器。

SR触发器是通过两个输入信号S和R控制其状态的,当S=1,R=0时,触发器的状态被置为1;当S=0,R=1时,触发器的状态被置为0;当S=0,R=0时,触发器的状态不变;当S=1,R=1时,由于存在矛盾的输入信号,触发器的状态是不确定的。

D触发器是基于SR触发器演变而来的一种触发器,它只有一个输入信号D,当D=1时,触发器的状态被置为1;当D=0时,触发器的状态被置为0。

D触发器的输入信号与输出信号之间存在延迟,这个延迟可以用时钟信号控制,当时钟信号上升沿到来时,D触发器根据输入信号的状态更新其状态,并将更新后的状态输出。

四位二进制计数器可以通过将四个D触发器按照一定的规律组合起来实现。

具体来讲,我们可以将四个D触发器的时钟信号串联起来,这样它们就共享一个时钟信号,在时钟信号上升沿到来时,它们会同时更新。

然后,我们将第一个D触发器的D输入接到高电平信号上,这个D触发器的输出信号就是计数器的最低位,每个时钟周期它会更新一次。

接着,我们将第二个D触发器的D输入接到第一个D触发器的输出信号上,这个D触发器的输出信号就是计数器的第二位,以此类推,每个D触发器的D输入接到前一个D触发器的输出信号上,最后一个D触发器的输出信号就是计数器的最高位。

四个D触发器的状态共有16种可能,每当时钟信号上升沿到来时,计数器的状态会加1,当计数器的状态达到16时,它会从0重新开始计数。

这个计数器可以用于很多应用场景,比如频率除法、时序控制等。

值得注意的是,四位二进制计数器的实现不是唯一的,可以通过不同的组合方式实现。

这个时候需要注意的是,不同的实现方式可能会导致电路的性能、功耗甚至正确性存在差异,需要根据具体的应用场景选择合适的实现方式。

d触发器的原理简述和应用

d触发器的原理简述和应用1. d触发器的原理简述d触发器是数字电路中常用的触发器类型之一,它是一种单稳态触发器,可以在时钟信号的上升或下降沿触发的情况下,根据数据输入信号的状态来改变输出的状态。

1.1 d触发器的基本结构d触发器由两个输入端(数据输入端d和时钟输入端clk)和两个输出端(输出端q和反相输出端q’)组成。

其基本结构如下:_________| |--|d |--| |--| q |----| |--| clk |--| |--| q' |--|_________|1.2 d触发器的工作原理当时钟信号clk变化时,根据d端的输入信号确定q端和q’端的输出状态。

具体的状态转换规则如下:•当时钟信号clk的边沿(上升沿或下降沿)到来时,若d端输入为低电平(0),则q端输出为低电平(0),q’端输出为高电平(1)。

•当时钟信号clk的边沿到来时,若d端输入为高电平(1),则q端输出为高电平(1),q’端输出为低电平(0)。

2. d触发器的应用d触发器由于其特性和性能优势,在数字电路设计中得到广泛应用。

以下是d 触发器常见的应用场景:2.1 同步时序电路d触发器可以用于同步时序电路中,实现数据的暂存和延时功能。

通过将数据输入信号与时钟信号相接,当时钟信号到来时,输入信号的状态被暂存到d触发器中,随后输出到后续电路中。

这种设计方式可以有效解决时序电路中的数据竞争和冲突问题,提高电路的稳定性和可靠性。

2.2 计数器d触发器还可以组成计数器电路。

通过将多个d触发器串联连接,并将上一个触发器的输出连接到下一个触发器的时钟输入端,就可以实现一个多位二进制计数器。

在计数器电路中,每个触发器的输出与时钟信号相连,当时钟信号边沿到来时,触发器按照一定的规律进行状态转换,从而实现计数功能。

2.3 状态机d触发器还可以用于实现状态机。

状态机是一种非常常见的逻辑电路,可以按照预定的状态序列完成特定的功能。

通过适当地设置和连接多个d触发器,可以实现复杂的状态转换,从而实现更高级的功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字电路实验设计:

D触发器组成的4位异步二进制加法计数器一、选用芯片74LS74,管脚图如下:

说明:74LS74是上升沿触发的双D触发器,D触发器的特性方程为 "'' -——、设计方案:

用触发器组成计数器。

触发器具有0和1两种状态,因此用一个触发器就可以表示一位二进制数。

如果把n个触发器串起来,就可以表示n位二进制数。

对于十进制计数器,它的10个数码要求有10个状态,要用4位二进制数来构成。

下图是由D触发器组成的4位异步二进制加法计数器。

三、实验台:

四、布线:

1、将芯片(1)的引脚4、10连到一起,

2、将芯片(2)的引脚4、10连到一起,

3、将芯片(1)的引脚10和芯片(2)的引脚10连到一起,

4、将芯片(1)的引脚10连到+5V;

5、将芯片(1)的引脚1、13连到一起,

6、将芯片(2)的引脚1、13 连到一起,

7、将芯片(1)的引脚13 和芯片(2)的引脚13 连到一起,

i>

8、将芯片(1)的引脚13 连到+5V;

9、将芯片(1)的引脚3 接到时钟信号CP

10、将芯片(1)的引脚2、6 接到一起,再将引脚2 接到引脚11

11、将芯片(1)的引脚8、12 接到一起,再将芯片(1)的引脚8 接到芯片(2)的引脚3

12、将芯片(2)的引脚2、6 接到一起,再将引脚6 接到引脚11

13、将芯片(1)的引脚5、9分别接到Q o、Q i,再将芯片(2)的引脚5、9分别接到

Q2 、Q3

14、分别将两芯片的14脚接电源+5V,分别将两芯片的7脚接地0V。

五、验证:

接通电源on,默认输出原始状态0000

每输入一个CP 信号(单击CP),的状态就会相应的变化,变化规律为0000 (原始状态)、1000、0100 、1100、0010、1010、0110、1110、0001 、1001 、0101 、1101 、

0011 、1011 、0111 、1111。