6第六章 基本输入输出口

电气控制与PLC控制基础理论-第六章

输入

输出

SB1 X1 SB2 X2

红灯L1

Y0

绿灯L2,L3,L4,L5 Y1

黄灯L6,L7,L8,L9 Y2

表6-2 天塔之光控制系统输入/输出端口分配表

天塔之光控制系统设计

2、基于三菱FX2N系列PLC天塔之光控制系统设计 (2)PLC外部接线图设计 PLC外部接线图设计如图6-10所示。

➢ 要考虑电源的输出功率和极性问题。

编制PLC程序并进行模拟调试

编制PLC程序时要注意以下问题: (1)以输出线圈为核心设计梯形图,并画出该线圈的得电条件、失电条件和自锁条件。 (2)如果不能直接使用输入条件逻辑组合成输出线圈的得电和失电条件,则需要使用辅助继电器 建立输出线圈的得电和失电条件。 (3)如果输出线圈的得电和失电条件中需要定时或计数条件时,要注意定时器或计数器得电和失 电条件。 (4)如果输出线圈的得电和失电条件中需要功能指令的执行结果作为条件时,使用功能指令梯级 建立输出线圈的得电和失电条件。 (5)画出各个输出线圈之间的互锁条件。 (6)画保护条件。 根据以上要求绘制好梯形图后,将程序下载到PLC中,通过观察其输出端发光二极管的变化进行模 拟调试,并根据要求进行修改,直到满足系统要求。

图6-16 PLC外部接线图 图6-17 DC24V直流电源接线图

十字交通灯控制系统设计

2、基于三菱FX2N系列PLC十字交通灯控制系统设计 (4)PLC强电电路图 PLC强电电路图如图6-18所示。

图6-18 PLC强电电路图

十字交通灯控制系统设计

2、基于三菱FX2N系列PLC十字交通灯控制系统设计 (5)PLC梯形图设计 PLC梯形图设计如图6-19所示。 (6)指令程序的传输 使用GX Developer(或FXGP/WIN-C)编程软件绘 制图6-19所示的PLC梯形图,并进行转换和PLC程序传 输。也可使用FX-20P型手持式编程器进行程序传输, 方法不再赘述。

模拟量输入输出

8253/ 8254

脉冲 频率

拟

信 号

MPU

ADC/DAC

V/I

模拟量转换与I/O通道

1. 模数转换--ADC 数模转换--DAC Analog to Digital Converter/ Digital to Analog Converter 2. 模入与模出通道的组成: 输入通道: (高精度测量,1%~0.05%,可分时采样,同步采样)

信号调理

检测/控制 传感器 变送器 执行机构

A/D D/A

数字量

输入调理

显示器

微 机 主 机

I/O接口

V/I变换

I/O接口 I/O接口

DI

电平变换 功放驱动

传感器

执行机构

DO

频率、其他 I/O接口 变换 信号处理

过 程 对 象 ︵ 被 控 对 象 ︶

传感、执行

模拟量I/O接口

模拟量的概念(信号连续量):DC-V(mv)/mA(V)典型: 过程控制、各类监控/自动化系统 转换输入输出:实验P22输入:V/F计数器------输出:计 数器F/V(LM331);PWM调宽(时间) T/C F/V V/F 模

;???

多路转换器Multiplexer(MUX)

用途(作用):信号复用 机械(干簧继电器、水银R等):导通电阻小,断开高阻隔离, 百万次,400HZ 电子模拟开关:晶体管、场效应管、IC导通电阻大(几十 (百)欧姆),断开高阻不独立,隔离?(信号限制--共模电压) 高速 Analog Multiplexer----N-1,1-N 分时使用1端器件 典型MUX芯片 单向/双向 CD4051B 8-1 双向,带INH端(=0使能); LF13508(NSC)/DG508 8-1; LF13509 差分输入四选一 AD7501/3八选一单向(7501EN=0/7302EN=1);CD7502双四选一 逻辑关系简单:通道选择信号需外加锁存;电平匹配问题 CMOS+5时TTL兼容;+15V时HTL

计算机原理 第六章输入输出系统

1

2

3

为保证总线所传输的信息的有效性,总线 信息应具有单一性:在同一时刻至多只能有一 个部件向总线发送信息,但可以有多个部件同 时接收总线信息。

1. 总线电路: 输出挂在总线上的部件需通过“总线电路” 向总线发送信息。

总线电路由三态输出器件(TSL器件)承担。 input TSL control output

1. ISA总线:用于IBM PC/XT 微机系统,(8086),一共62根信号线, 其中20根地址线,8根数据线,4个读写信号,6个中断请求线,3 路DMA请求,还包括时钟、电源线和地等,总线带宽 8.33 MB/s。

2.EISA总线 (80386), 数据线扩展到了32位,带宽达到了33.3MB/s。 3. PCI总线:(Peripheral component interconnection)(外围部 件互连) 总线频率为33 MHZ→66MHZ→133MHZ, 可以直接连接高速外部 设备。 同步时序总线,对地址信号和数据信号分时复用, 64根线,采用集中式的总线仲裁方式。 4.AGP总线(加速图形接口总线) AGP总线把主存和显存连接起来,不再走PCI总线。 5.USB总线(通用串行总线)主要用于连接低速输入输出设备。 带宽为1.5MB/s。

3. 控制总线CB(Control Bus) 控制总线用来传送各类控制/状态信号。

包括I/O读写命令,MEMR/W存储器读写命令,应答信号,总线请求与 总线使用信号,复位信号,时钟信号等。

4. 电源线

许多总线标准中都包含了电源线的定义,主要有+5V逻辑电源;GND逻 辑电源地;-5V辅助电源;±12V辅助电源。

2.计数器查询方式

在计数器查询方式中,总线上的任一设备申请使用总线时,通过 BR线发出总线请求。

第六章输入输出接口基础(CPU与外设之间的数据传输)

§6.1 接口的基本概念

3、什么是微机接口技术?

处理微机系统与外设间联系的技术 注意其软硬结合的特点 根据应用系统的需要,使用和构造相应的接 口电路,编制配套的接口程序,支持和连接 有关的设备

§6.1 接口的基本概念

4、接口的功能

⑴对I/O端口进行寻址,对送来的片选信号进行 识别;

(2)根据读/写信号决定当前进行的是输入操作还 是输出操作,对输入输出数据进行缓冲和锁存 输出接口有锁存环节;输入接口有缓冲环节 实际的电路常见: 输出锁存缓冲环节、输入锁存缓冲环节

对接口内部寄存器的寻址。

P279

§6.2 CPU与外设之间数据的传送方式

CPU与外设之间传输数据的控制方式通常有 三种: 程序方式:

• 无条件传送方式和有条件传送方式

中断方式 DMA方式

§6.2 CPU与外设之间数据的传送方式

一、程序方式 指用输入/输出指令,来控制信息传输

的方式,是一种软件控制方式,根据程序控 制的方法不同,又可以分为无条件传送方式 和条件传送方式。

输入数据寄存器:保存外设给CPU的数据 输出数据寄存器:保存CPU给外设的数据

⑵ 状态寄存器

保存外设或接口电路的状态

⑶ 控制寄存器

保存CPU给外设或接口电路的命令

§6.1 接口的基本概念

接口电路的外部特性 主要体现在引脚上,分成两侧信号 面向CPU一侧的信号:

用于与CPU连接 主要是数据、地址和控制信号

程序不易阅读(不易分 清访存和访问外设)

00000

I/O 部分

§6.1 接口的基本概念

独立编址方式

FFFFF

优点:

I/O端口的地址空间独立

内存 空间

控制和地址译码电路相对简单 FFFF I/O

报关员考试第六章进出口货物报关单填制

第六章进出口货物报关单填制删减:“六章章节概括”P330“进出口货物报关单是报关员代表报关单位向海关办理货物进口境手续的主要单证。

按照《中华人民共和国海关进出口货物申报管理规定》(以下简称《货物申报管理规定》)和《报关单填制规范》的要求,完整、准确、有效地填制进出口货物报关单是报关员执业所必备的基本技能。

本章主要介绍纸质进出口货物报关单各个栏目填制的基本要求及应注意的事项。

”改为“进出口货物报关单是报关员代表报关单位向海关办理货物进口境手续的主要单证。

本章主要介绍纸质进出口货物报关单各个栏目填制的基本要求及应注意的事项。

”第一节进出口货物报关单概述三、进出口货物报关单各联的用途P332(三)进出口货物报关单加工贸易核销联“进出口货物报关单海关核销联是指接受申报的海关对已实际申报进口或出口的货物所签发的证明文件,是海关办理加工贸易合同核销、结案手续的重要凭证。

加工贸易的货物进出口后,申报人应向海关领取进出口货物报关单海关核销联,并凭以向主管海关办理加工贸易合同核销手续。

该联在报关时与海关作业联一并提供。

”改为“进出口货物报关单海关核销联是指接受申报的海关对已实际申报进口或出口的货物所签发的证明文件,是海关办理加工贸易合同核销、结案手续的重要凭证。

该联在报关时与海关作业联一并提供。

加工贸易的货物进出口后,并凭以向主管海关办理加工贸易合同核销手续。

”(四)出口货物报关单出口退税证明联“出口货物报关单出口退税证明联是海关对已实际申报出口并以装运离境的货物所签发的证明文件,是国家税务部门办理出口货物退税手续的凭证之一。

对可办理出口退税的货物,出口货物发货人或其代理人应当在载运货物的运输工具实际离境,海关办理结关手续后,向海关申领出口货物报关单出口退税证明联,有关出口货物发货人凭以向国家税务管理部门申请办理出口货物退税手续。

对不属于退税范围的货物,海关均不予签发该联。

出口退税报关单证明联因遗失,损毁申请补签,出口货物的发货人、受委托的报关企业应当自原出口退税报关单签发日起1年内向海关书面申请,随附主管其出口退税的地(市)国家税务局签发的‘关于申请出具(补办报关单)证明’及有关证明材料,经海关审核同意后,可予以补签,并在出口退税专用报关单上注明“补签”字样。

操作系统第6章

45

第六章

输入输出系统

(3) 驱动程序与I/O设备所采用的I/O控制方式紧密相关,

常用的I/O控制方式是中断驱动和DMA方式。 (4) 由于驱动程序与硬件紧密相关,因而其中的一部分 必须用汇编语言书写。目前有很多驱动程序的基本部分已经 固化在ROM中。

2. 通道类型

1) 字节多路通道(Byte Multiplexor Channel) 这是一种按字节交叉方式工作的通道。它通常都含有许 多非分配型子通道,其数量可从几十到数百个,每一个子通 道连接一台I/O设备,并控制该设备的I/O操作。这些子通道

按时间片轮转方式共享主通道。

28

第六章

输入输出系统

数组选择通道虽有很高的传输速率,但它却每次只允许 一个设备传输数据。数组多路通道是将数组选择通道传输速 率高和字节多路通道能使各子通道(设备)分时并行操作的优 点相结合而形成的一种新通道。

31

第六章

输入输出系统

3. “瓶颈”问题

由于通道价格昂贵,致使机器中所设置的通道数量势必 较少,这往往又使它成了I/O的瓶颈,进而造成整个系统吞 吐量的下降。

令中的抽象要求转换为与设备相关的低层操作序列。

(2) 检查用户I/O请求的合法性,了解I/O设备的工作状态, 传递与I/O设备操作有关的参数,设置设备的工作方式。 (3) 发出I/O命令,如果设备空闲,便立即启动I/O设备, 完成指定的I/O操作;如果设备忙碌,则将请求者的请求块挂 在设备队列上等待。 (4) 及时响应由设备控制器发来的中断请求,并根据其中 断类型,调用相应的中断处理程序进行处理。

44

第六章

输入输出系统

2. 设备驱动程序的特点

设备驱动程序属于低级的系统例程,它与一般的应用程 序及系统程序之间有下述明显差异:

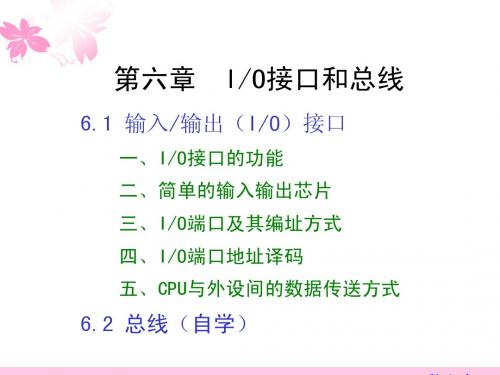

第六章 IO接口和总线

1、缓冲器 74LS244

单路基本组成:

真值表 A

B

G#

0

A

1

B

1

0 G

1

0

高阻

0

状态

1A1 1A2

/1G 1A1 2Y4 1A2 2Y3 1A3 2Y2 1A4 2Y1 GND

1 2 3 4 5 6 7 8 9 10

1Y1 1Y2 1Y3 1Y4 2Y1 2Y2 2Y3 2Y4

244

20 19 18 17 16 15 14 13 12 11

需要输入设备送入信息,输出设备送出结果,这些输 入输出设备被称为外设。

通信:计算机(CPU)与外设间的数据、状态和控制

命令的交换过程统称为通信。

2、CPU与外设直接通信存在的问题 速度不匹配(CPU快,外设慢) 信号电平不匹配 (CPU使用TTL电平,外设多为机电设备) 信号格式不匹配 (CPU总线上为并行数字量,而外设有串行模拟量等) 时序不匹配 解决方案: 用I/O接口:把外设连接到CPU总线上的一组逻辑电 路的总称。用于协调外设与主机之间的信息交换。

2、译码的常用方法

线选法

利用一根地址线,产生指定的端口地址的选择信号。

A7

PORT1

当A7=1,选中PORT1,地址可为80H 当A6=1,选中PORT2,地址可为40H 当A5=1,选中PORT3,地址可为20H

A6

PORT2

对于PORT1,地址为81H,82H,83H

等仍可选中。

A5

PORT3

无条件输出电路例子 例:假设该端口号为

0# D0

80H,要想让0、2、4、

6号灯亮,如何编写

D1

1D 2D

操作系统题目第6章

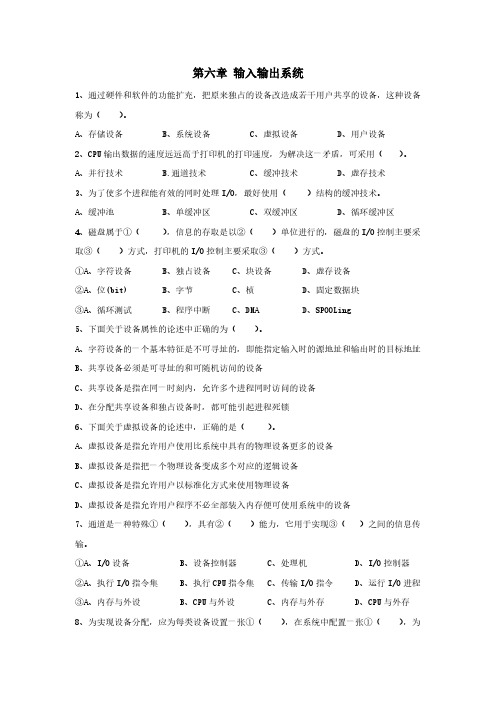

第六章输入输出系统1、通过硬件和软件的功能扩充,把原来独占的设备改造成若干用户共享的设备,这种设备称为()。

A、存储设备B、系统设备C、虚拟设备D、用户设备2、CPU输出数据的速度远远高于打印机的打印速度,为解决这一矛盾,可采用()。

A、并行技术 B.通道技术C、缓冲技术D、虚存技术3、为了使多个进程能有效的同时处理I/O,最好使用()结构的缓冲技术。

A、缓冲池B、单缓冲区C、双缓冲区D、循环缓冲区4、磁盘属于①(),信息的存取是以②()单位进行的,磁盘的I/O控制主要采取③()方式,打印机的I/O控制主要采取③()方式。

①A、字符设备 B、独占设备 C、块设备D、虚存设备②A、位(bit) B、字节C、桢D、固定数据块③A、循环测试 B、程序中断 C、DMA D、SPOOLing5、下面关于设备属性的论述中正确的为()。

A、字符设备的一个基本特征是不可寻址的,即能指定输入时的源地址和输出时的目标地址B、共享设备必须是可寻址的和可随机访问的设备C、共享设备是指在同一时刻内,允许多个进程同时访问的设备D、在分配共享设备和独占设备时,都可能引起进程死锁6、下面关于虚拟设备的论述中,正确的是()。

A、虚拟设备是指允许用户使用比系统中具有的物理设备更多的设备B、虚拟设备是指把一个物理设备变成多个对应的逻辑设备C、虚拟设备是指允许用户以标准化方式来使用物理设备D、虚拟设备是指允许用户程序不必全部装入内存便可使用系统中的设备7、通道是一种特殊①(),具有②()能力,它用于实现③()之间的信息传输。

①A、I/O设备B、设备控制器C、处理机D、I/O控制器②A、执行I/O指令集 B、执行CPU指令集C、传输I/O指令D、运行I/O进程③A、内存与外设B、CPU与外设C、内存与外存D、CPU与外存8、为实现设备分配,应为每类设备设置一张①(),在系统中配置一张①(),为实现设备的独立性,系统中应设置一张②()。

①A、设备控制表B、控制器控制表C、系统设备表D、设备分配表②A、设备开关表B、I/O请求表C、系统设备表D、逻辑设备表9、下面不适合于磁盘调度算法的是()。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DDRA=1导 通,此时为 输出口

引脚 PTAx pin

内 部 数 据 总 线

写 PTA($0000)

PTAPUE=1, 三极管导通, 上拉有效

DDRA=0导 通,此时为 输入口

4

6.1 并行I/O口

2)C口 PTC6~PTC0 • 只有并行I/O口的功能 • 在寄存器定义上和A口相同 • 数据方向寄存器 –DDRC --$0006 • 数据寄存器 --PTC --$0002 • 上拉电阻允许寄存器 –PTCPUE --$000E

5

6.1 并行I/O口

• 3)D口 PTD6~PTD0 • • • •

在寄存器定义上和A口相同

数据方向寄存器 –DDRD --$0007 数据寄存器 --PTD --$0003 上拉电阻允许寄存器 –PTDPUE --$000F

6

6.1 并行I/O口

• 6.1.3 B口、E口

• (1)数据方向寄存器 –DDRB --$0006 • 该寄存器的一位:0---输入;1—输出

MOTOROLA QY4 MCU

LCD

PTB PTC

28

DB9针座

• • • • • • • • • 1.A/D转换状态和控制寄存器(Analogto-Digital Status and Control Register—ADSCR) ADSCR主要功能是:选取要转换的通道、决定 转换结束数据获取的方式、设置是连续转换还 是一次转换。 A/D转换状态和控制寄存器(ADCSCR): 地址:$003C 位7:COCO—Conversions Complete(转换完成) 读位,1—转换完成;0—转换未完成

26

• 1—选择内部总线时钟;0—选择外部时钟(CGMXCLK)

6.5.3 A/D转换编程举例

• 1)A/D初始化 • LDA #%00110000 ;使用内部总线时钟,2分频(内部总

线频率=2.4576MHz) • STA $003E ;送入寄存器ADCLK

• 2)启动A/D

• LDA #%00000000 ;0通道,转换结束不产生中断,一次 A/D转换 • STA $003C ;并启动0通道转换

• • • • (1)键的识别 查询法、定时扫描法、中断法 (2)抖动问题 软件方法:延迟等待抖动的消失

12

6.3 键盘与键盘中断口

行线接 输出口

+5V 5K×4

PTA0 行线 m1

PTA1 PTA2 PTA3

m2 m3 m4 列线 n1 图 5-3 n2 n3 n4

PTA0~3定义为输出 PTA4~7定义为输入

PTA4 PTA6 PTA6 PTA7

4×4 键盘结构

列线接 输入口

13

6.3 键盘与键盘中断口

• 6.3.2 MC68HC908QY4单片机的键盘中断模块

• (1)KBI寄存器 • 键盘状态和控制寄存器 INTKBSCR 地址:$001A

• • • • • • • •

位7-4:未用。读出均为0,没有具体含义。 位3:只读位:KEYF—Keyboard Flag Bit(键盘标志位) 1—键盘中断已产生;0—未产生键盘中断 位2:只写位:ACKK—Keyboard Acknowledge Bit(键盘中断应答) 位1:IMASKK—Keyboard Interrupt Mask Bit(键盘中断屏蔽位) 位0:MODEK—Keyboard Triggering Sensitivity Bit 定义键盘中断引脚触发方式 0—下降延及低电平触发;1—仅下降延触发

14

• 说明:位3只读,位2只写;位1、位0可读写。复位时全为0。

6.3 键盘与键盘中断口

• • • • 键盘中断允许寄存器INTKBIER 地址:$001B 位7—位0 : KBIE7—KBIE0 若KBIEx=1,表示相应引脚KBIEx pin(也就 是引脚PTAx pin)被定义为中断引入引脚

• 数据寄存器

--PTB --$0001

• 输出时,0—输出低电平;1—输出高电平 • 输入时,0—外部输入低电平;1—外部输入高电平

注意:B口被定义成输入时,没有内部上拉 电阻

7

6.1 并行I/O口

读 DDRB($0005) 写 DDRB($0005)

内 部 数 据 总 线

复位 写 PTB($0001)

22

6.5.2 A/D转换模块的寄存器

当位6(AIEN)=1时,即转换结束产生 中断,COCO是可读写位,应该写COCO=0。 • 位6:AIEN—ADC Interrupt Enable Bit • (AD转换中断允许标志位) • 位5:ADCO—ADC Continuous • Conversion Bit(连续转换控制位) • 位4~位0:ADCH4~ADCH0—ADC Channel • Select Bits(通道选择) • ADCH4~ADCH0=00000-00111:AD0pin~AD7 pin

18

6.4 键盘中断编程举例

•

• • •

•

• •

•

•

LDA #%00001111 ;定义A口7-4为输入,3-0为输出 STA DDRA LDA #%11110000 ;定义A口7-4有上拉电阻 STA PTAPUE BSET 1,INTKBSCR ;屏蔽键盘中断(IMASK=1) LDA #%11110000 ;允许KBIE7-4 pin中断进入 STA INTKBIER BSET 2,INTKBSCR ;清除键盘中断请求(ACKK=1) BCLR 1,INTKBSCR ;开放键盘中断(IMASKK=0)

23

6.5.2 A/D转换模块的寄存器

• 2.A/D 转 换 数 据 寄 存 器 ( Analog-toDigital Data Register—ADR) • ADR存放A/D转换的8位结果,每次A./D 转换结束更新该寄存器。 • 编程从该寄存器读取A/D转换结果。 • 该寄存器地址为:$003D,为只读寄存 器,复位时为$00。

B 口数据方向寄存器 DDRBx 位 B 口数据寄存器 PTBx 位 引脚 PTBx pin

读 PTB($0001) 图 5-2 B 口的一个引脚内部逻辑电路框图

8

6.1 并行I/O口

• (2)E口 PTE1、PTE0 类比B口

• 数据方向寄存器 –DDRE • 数据寄存器 --PTE --$000C --$0008

• 3)获A/D转换结果

• • BRCLR 7,$003C,* ;COCO位=0则等待COCO位=1 LDA $003D ;转换结束,转换结果送入A中

27

vcc

LED vcc 开关

VCC

other

MAX232

PTE

PTA7 PTA6 PTA6 PTA4 PTA3 PTA2 PTA1 PTA0 PTC0 PTC1 PTC2 PTC3 PTC4

15

6.3 键盘与键盘中断口

• (2)与KBI相关问题

• 1)键盘中断矢量地址:$FFE0~$FFE1 • 2)键盘中断初始化顺序: • 设置键盘状态和控制寄存器 (INTKBSCR) • 设置中断允许寄存器(INTKBIER)

16

6.3 键盘与键盘中断口

• 3)为避免键盘误中断,建议初始化时 注意顺序

电阻: • 0—没有内部上拉电阻

• 1—有内部上拉电阻

3

6.1 并行I/O口

读 DDRA($0004) 写 DDRA($0004) 复位 A 口数据方向寄存器 DDRAx 位 A 口数据寄存器 PTAx 位 VDD PTAPUEx 内部上拉电阻 读 PTA($0000) 图 5-1 A 口的一个引脚内部逻辑电路框图

25ቤተ መጻሕፍቲ ባይዱ

6.5.2 A/D转换模块的寄存器

• • • • • • • • • • 设ADC时钟输入时钟源频率为f入, 由ADIV2~ADIV0定义的分频系数为n 则ADC时钟频率=f入/n ADIV2~ADIV0=000 n=1 =001 n=2 =010 n=4 =011 n=8 =1xx n=16 位4:ADICLK—ADC Input Clock Select Bit (ADC输入时钟源选择位)

• • • • • • 数据方向寄存器 –DDRA--$0004 该寄存器的一位:0---输入;1—输出 数据寄存器 --PTA --$0000 输出时,0—输出低电平;1—输出高电平 输入时,0—外部输入低电平; 1—外部输入高电平

2

6.1 并行I/O口

• 上拉电阻允许寄存器 –PTAPUE --$000D • 引脚定义为输入时,可定义为有无内部上拉

19

• 6.5.1 概述 • MC68HC908单片机的B口的8根引脚与8路A/D转 换模块的引脚复用 即PTB7/AD7~PTB0/AD0 • B口引脚作为A/D转换引脚时,叫作AD7 pin ~ AD0 pin。 • 它们是8位A/D转换,正常A/D转换要求提供 1MHz的ADC时钟频率,一次一路A/D转换时间一 般为16到17个ADC时钟周期,所以一般A/D转换 时间为16~17μS。

1) 定义A口的数据方向(7~4为输入,3~0为输 出) 2) IMASK=1(屏蔽键盘中断)、 3) 设置KBIEx=1(定义中断引脚)、 4) 写ACKK=1(清除键盘中断请求)、 5) 令IMASK=0(开放键盘中断)

17

6.4 键盘中断编程举例

• • • • • • (1)键盘初始化子程序 (2)扫描法读取键值子程序 (3)键盘中断子程序 (4)键值转化为定义值子程序 (5)延时子程序 (6)主程序

• • • • • • • • • NOP SEI LDHX #$023f TXS LDA #%00001111 ;定义A口7-4为输入,3-0为输出 STA DDRA LDA #%11110000 ;定义A口7-4有上拉电阻 STA PTAPUE …