基于Multisim的数字时钟设计.(精选)

基于Multisim的数字时钟仿真设计

数字时钟仿真设计山东大学(威海)机电与信息工程学院09级通信工程姓名:XXX学号:XXXXXXXXX目录目录 (1)序言 (2)设计思路 (2)设计原理 (2)一、秒脉冲产生电路 (2)二、计数器电路 (3)1. 六十进制计数电路 (3)2. 二十四/十二进制计数电路 (3)三、校时、校分电路 (4)四、报时电路 (5)五、总电路 (6)实现的功能 (6)感想 (6)参考文献: (7)序言数字时钟是用数字集成电路构成的、用数码显示的一种现代计时器,与传统机械表相比,它具有走时准确、显示直观、无机械传动装置等特点,因而广泛应用于车站、码头、机场、商店等公共场所。

在控制系统中,数字时钟也常用来做定时控制的时钟源。

设计思路数字时钟由振荡器、分频器、计数器、译码显示、报时等电路组成。

其中,振荡器和分频器组成标准秒信号发生器,直接决定计时系统的精度。

由不同进制的计数器、译码器和显示器组成计时系统。

将标准秒信号送入采用六十进制的“秒计数器”,每累计60s就发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。

“分计数器”也采用六十进制计数器,每累计60min,发出一个“时脉冲”信号,该信号将被送到“时计数器”。

“时计数器”采用二十四或十二进制计时器,可实现对一天24小时或12小时的累计。

译码显示电路将“时”、“分”、“秒”计数器的输出状态通过六位七段译码显示器显示出来,可进行整点报时,计时出现误差时,可以用校时电路校时、校分。

数字时钟的原理框图如图1所示。

图1.原理框图设计原理根据仿真电路的设计要求,该电路应满足一下功能:1.具有时、分、秒的十进制数字显示的计时器。

2.具有手动校时、校分的功能。

3.通过开关能实现小时的十二进制和二十四进制转换。

4.具有整点报时的功能,应该是每个整点完成相应点数的报时。

以及闹钟功能。

一、秒脉冲产生电路秒脉冲产生电路在此例中的主要功能有两个:一是产生标准脉冲信号,二是可提供整点报时所需要的频率信号。

MULTISIM数字电子技术电子时钟设计实验报告

MULTISIM数字电子技术电子时钟设计实验报告数字时钟一、实验目的学习综合数字电子电路的设计、实现和调试方法。

二、实验内容(1)设计一个24小时制的数字时钟。

(2)要求:计时、显示精度到秒;有校时功能。

采用中小规模集成电路设计。

(3)发挥:增加闹钟功能。

三、设计方案首先构成一个555定时器和分频器产生震荡周期唯一秒的标准“秒”脉冲信号,由74LS160D采用清零法分别组成六十进制的秒计数器、六十进制得分计数器、二十四进制的是计数器。

使用555定时器的输出作为秒计数器的CP脉冲,把秒计数器的进位输出作为分计数器的CP脉冲,分计数器的进位输出作为是计数器的CP脉冲。

使用SEVEN_SEG_COM_K_GREEN数码管作为显示器,74LS48为驱动器。

校时电路采用开关控制时、分、秒计数器的时钟信号为校时脉冲以完成校时。

四、性能指标精度稳定性五、电路框图整时计数器秒计数器分计数器点(24进制) (60进制) (60进制) 报时校时电路秒信号发生器六、电路原理图6.1 六十进制分秒电路 VCC12VVCCU1CLK2U12~CLR1~LOAD9GND8ENT106ENPRCO7155404DQD611CQC512GNDBQB413AQA3 14DCD_HEXVCC74LS160D12VU2CLK2VCC~CLR1~LOAD9U1328ENT10ENPRCO71512GND11DQD61110 CQC5129BQB413AQA314GNDDCD_HEX74LS160DU8AU7A297400N 32317400N60进制分秒电路该图使用的是整体置数,可靠性高。

首先将两片74LS160D接成百进制的计数器。

然后将电路的59状态译码产生LD=1信号,同时接到两片74LS160D上,在下一个计数脉冲到达时,将0000同时置入两片74LS160D中,从而得到60进制的计数器。

进位信号可以直接由门U9A引出。

6.2 二十四进制时电路35U5VCCCLK2~CLR1VCC12VU16~LOAD9ENT10ENPRCO23715GND22DQD21611CQC20512BQB4133AQA314GNDDCD_HEXVCC74LS160D12VU6CLK2~CLRVCC1~LOAD9U172ENT10ENPRCO71527DQDGND26611CQC25512BQB24413AQA314 GNDDCD_HEX74LS160DU11A7400N24进制时电路24进制计数器使用整体置零法接成的。

基于Multisim的数字电子时钟设计报告

大学大数据与信息工程学院基于Multisim的数字电子时钟设计报告学院:大数据与信息工程学院专业:电子科学与技术班级:151学号:1500890151学生:宋磊指导教师:郭祥2017年7月20日目录一、设计目的与要求 (1)1.1设计目的 (1)1.2设计要求 (1)二、基本元器件的选择与原理 (1)2.1 555定时器 (1)2.2 74LS390D计数器 (2)2.2.1 分、秒位实现六十进制 (3)2.2.2 小时位实现二十四进制 (3)2.2.3 星期位实现七进制 (4)2.3 显示器 (5)2.4 其他元器件 (6)三、虚拟实验平台与仿真 (6)3.1 手动校准功能的实现 (6)3.2 整点报时功能的实现 (6)3.3 设计从设计从220V交流~6V直流 (7)3.4 数字电子时钟功能的实现 (7)附录设计总结与心得体会 (9)一、设计目的与要求1.1设计目的用中、小规模集成电路设计日、时、分、秒的电子钟。

1.2设计要求1)用555定时器产生1Hz秒信号;2)秒、分为00~59六十进制;3)时为00~23二十四进制;4)星期为1~7七进制;5)日、时、分可手动校准;6)具有整点报时功能;7)设计从220V交流~6V直流。

二、基本元器件的选择与原理2.1 555定时器单稳态触发器和施密特触发器主要用于脉冲的整形,多谐振荡器则用于产生脉冲信号。

而利用555集成定时器,可以方便地构成施密特触发器、单稳态触发器和多谐振荡器,并且带负载能力较强。

此次数字电子钟的计数脉冲则由多谐振荡器提供。

脉冲频率取决于555定时器电路。

在Multisim13下构建多谐振荡器,如图2.1:图2.1振荡频率:f=1.43/[(R9+2R10)C1]振荡周期:T=1/f2.2 74LS390D计数器计数器——用于统计输入脉冲CP个数的电路。

本次设计统一采用74LS390D计数芯片,74LS390D是一种双四位十进制计数器。

基于Multisim的数字电子时钟设计报告

贵州大学大数据与信息工程学院基于Multisim的数字电子时钟设计报告学院:大数据与信息工程学院专业:电子科学与技术班级:151学号:**********学生姓名:***指导教师:***2017年7月20日目录一、设计目的与要求 (1)1.1设计目的 (1)1.2设计要求 (1)二、基本元器件的选择与原理 (1)2.1 555定时器 (1)2.2 74LS390D计数器 (2)2.2.1 分、秒位实现六十进制 (3)2.2.2 小时位实现二十四进制 (3)2.2.3 星期位实现七进制 (4)2.3 显示器 (5)2.4 其他元器件 (6)三、虚拟实验平台与仿真 (6)3.1 手动校准功能的实现 (6)3.2 整点报时功能的实现 (6)3.3 设计从设计从220V交流~6V直流 (7)3.4 数字电子时钟功能的实现 (7)附录设计总结与心得体会 (9)一、设计目的与要求1.1设计目的用中、小规模集成电路设计日、时、分、秒的电子钟。

1.2设计要求1)用555定时器产生1Hz秒信号;2)秒、分为00~59六十进制;3)时为00~23二十四进制;4)星期为1~7七进制;5)日、时、分可手动校准;6)具有整点报时功能;7)设计从220V交流~6V直流。

二、基本元器件的选择与原理2.1 555定时器单稳态触发器和施密特触发器主要用于脉冲的整形,多谐振荡器则用于产生脉冲信号。

而利用555集成定时器,可以方便地构成施密特触发器、单稳态触发器和多谐振荡器,并且带负载能力较强。

此次数字电子钟的计数脉冲则由多谐振荡器提供。

脉冲频率取决于555定时器电路。

在Multisim13下构建多谐振荡器,如图2.1:图2.1振荡频率: f=1.43/[(R9+2R10)C1]振荡周期: T=1/f2.2 74LS390D计数器计数器——用于统计输入脉冲CP个数的电路。

本次设计统一采用74LS390D计数芯片,74LS390D是一种双四位十进制计数器。

数字时钟仿真设计

基于multisim 10.0的数字时钟仿真设计一、设计目的1、综合运用数字电路的知识,掌握数字时钟的设计方法。

2、掌握计数器、译码器、分频器的设计原理和设计方法。

3、掌握运用仿真软件multisim 10.0设计综合数字电路的方法。

二、设计意义数字时钟是用数字集成电路构成的、用数码显示的一种现代计时器,与传统机械表相比,它具有走时准确、校时方便、显示直观、无机械传动装置等特点,因而广泛应用于车站、码头、机场、商店等公共场所。

在控制系统中,数字时钟也常用来做定时控制的时钟源。

三、设计要求1、设计一个具有时、分、秒的十进制数字显示的计时器。

2、具有手动校时、校分的功能。

3、通过开关能实现小时的十二进制和二十四进制转换。

4、具有整点报时的功能。

5、用74系列集成电路设计实现6、电路实现的各功能部分用子电路表示。

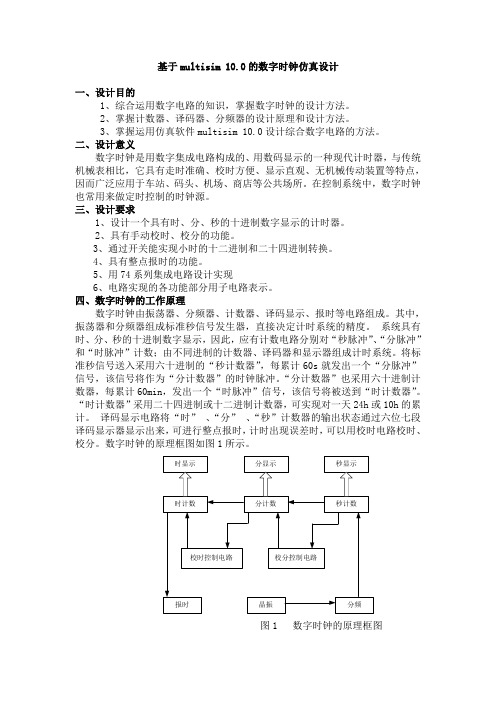

四、数字时钟的工作原理数字时钟由振荡器、分频器、计数器、译码显示、报时等电路组成。

其中,振荡器和分频器组成标准秒信号发生器,直接决定计时系统的精度。

系统具有时、分、秒的十进制数字显示,因此,应有计数电路分别对“秒脉冲”、“分脉冲”和“时脉冲”计数;由不同进制的计数器、译码器和显示器组成计时系统。

将标准秒信号送入采用六十进制的“秒计数器”,每累计60s就发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。

“分计数器”也采用六十进制计数器,每累计60min,发出一个“时脉冲”信号,该信号将被送到“时计数器”。

“时计数器”采用二十四进制或十二进制计数器,可实现对一天24h或10h的累计。

译码显示电路将“时”、“分”、“秒”计数器的输出状态通过六位七段译码显示器显示出来,可进行整点报时,计时出现误差时,可以用校时电路校时、校分。

数字时钟的原理框图如图1所示。

图1 数字时钟的原理框图五、单元电路设计单元电路分为小时计时模块、分钟和秒计时模块、整点译码电路、时钟产生电路、校时电路等。

待单元电路设计完成后,将各单元电路进行封装连接得到总体电路,进行总体电路的仿真、调试,最终完成数字时钟的设计。

基于Multisim的数字时钟设计资料整理

目录第1章引言 (3)1.设计思路 (6)2.主要内容 (7)第2章数字时钟模块设计 (7)2.1数字时钟秒脉冲信号的设计 (7)2.1.1秒时钟信号发生器的设计 (7)2.2器件分析 (8)2.2.174LS160分析 (8)2.3计数器设计 (10)2.3.1六十进制计数器 (10)2.3.2二十四进制计数器 (11)2.4计时电路设计 (12)2.4.1秒计时电路的设计 (12)2..4.2时计时电路的设计 (12)2.5数字时钟电路设计 (13)2.6校时电路 (15)2.7整点报时 (17)2.8闹钟电路 (17)第3章仿真调试 (22)3.1时钟显示 (23)3.1.1时钟显示完整的00:00:00 (23)3.1.2时钟完整显示01:00:00 (24)3.1.3时钟完整显示23:59:59 (24)3.1.4仿真开关校准“秒”电路 (25)3.1.6仿真开关校准“时”电路 (26)第4章结论 (20)第5章利用Multisim10.0仿真软件设计体会 (27)参考文献 (28)基于Multisim的数字时钟设计摘要:时间对于人们来说总是那么的宝贵,工作的忙碌性和繁杂性容易使人们忘记当前的时间。

于是,20世纪末,,电子技术有了飞快地发展,不仅在通信技术上用数字信号替代模拟信号,,,数字时钟相比模拟钟能给人一种一目了然的感觉,它不仅可以同时显示时、分和秒,并且可以完成准确的校正。

数字时钟具有走时精确,校准方便设计和使用简单的特点。

对于Multisim软件进行数字时钟的设计和仿真。

首先在Multisim创建好数字时钟的总电路图。

然后用该软件中的仿真功能进行仿真。

一个数字时钟需要振荡器,计数器,译码器和显示器电路精确时间“小时”“分”“秒”与数字显示,并需要校正电路,使其准确的工作,也可有定时和计时功能。

数字钟及扩大其应用,有着非常现实的意义。

在本文中,multisim10.0的基础上设计的数字钟,由数字集成电路,数码组成。

基于Multisim 14仿真设计的多功能数字电子钟

电子产品世界基于Multisim 14仿真设计的多功能数字电子钟Multifunctional digital electronic clock based on simulation design of Multisim 14金子涵,任致远,史旭东,王胜铎 (黑龙江工程学院,哈尔滨150050)摘 要:数字电子钟是一种利用数字电子技术实现计时的钟表。

本文介绍了在Multisim 14仿真软件上设计的满足要求的可调闹钟功能数字钟,对其设计原理、整体框图和各单元电路做了详细说明。

利用Multisim软件具有花费少、效率高、周期短,功能强等优势,可对数字电子钟电路进行分层设计。

将整机框图拆分成多个单元电路,再将各单元电路连线成整机电路,结构清晰,便于理解每个单元电路功能,使整机电路功能一目了然。

关键词:数字电子钟;Multisim 14;可调闹钟;反馈置数法;分层设计0 引言Multisim 14是美国NI公司研发的一款以Windows 为操作平台的EDA工具软件[1],可以对模拟、数字电路进行仿真与设计,具有丰富仿真分析能力,所以在电子技术领域以Multisim仿真软件为平台进行电路设计非常普遍。

数字电子钟是一种以数字电路技术实现计时的现代计数器,与传统机械式时钟相比,具有更高的准确性和直观性,且无机械装置,使用寿命更长,因此得到了广泛使用。

从原理上讲,数字电子钟是一种典型数字电路,包括组合逻辑电路和时序电路[2],所以,本文借助Multisim 14软件仿真数字电路便捷高效的优势,进行模块化电路设计,使得设计花费少、效率高、周期短。

1 设计任务1.1 基本功能1)应用模拟振荡电路实现正弦波时钟信号发生,并作为数字钟的时钟信号。

2)实现数字时钟计时功能,时间以24 min为1个周期。

3)用数码管显示分钟、秒。

1.2 扩展功能1)具有校时功能,可以对分钟和秒单独校时。

2)计时过程具有闹钟功能,到达指定时间(时间可选定)蜂鸣。

基于Multisim的数字时钟的设计及仿真

基于Multisim的数字时钟的设计及仿真摘要随着电子设计自动化(EDA)技术的发展,开创了利用“虚拟仪器”、“虚拟器件”在计算机上进行电子电路设计和实验的新方法。

Multisim就是一种能够运用这种新方法的软件,因它直观、便捷的特点使其在电子设计中具有广泛的应用。

可以在Multisim软件中进行模拟仿真,避免了实际操作的繁杂和不便,同时节约了实验器材,有助于边学边用,从而学以致用。

而数字时钟具有走时精确、校时方便、设计和使用简单的特点,能实现定时和报时功能,得到了广泛使用。

通过这个数字时钟的仿真,帮助认识其软件作用,深入分析其原理,帮助了解数字时钟工作原理。

对于Multisim软件进行数字时钟的设计和仿真。

我们首先在Multisim软件中创建好数字时钟的总电路图。

然后用该软件中的仿真功能进行仿真。

正确仿真的数字时钟应具有“秒”、“分”、“时”的十进制数字显示,能够随时校正分钟和小时,当时钟到整点时能够进行整点报时,还能够进行定时设置。

关键词:EDA,Multisim,模拟仿真,数字时钟Simulation Discussion of Digital Clock Based on MultisimAuthor: Huang ShengTutor: Si Xiao--pingAbstractAlong with the development of Electronic Design Automation(EDA),a new way of the electronic circuit design and experiments is created by using virtual instruments and components on computers.Multisim is a software to be able to use this way, because of its intuitive and convenient features of its electronic design with a wide range of applications. Multisim software can be carried out in the simulation, the actual operation to avoid the inconvenience of the complicated and, at the same time to save the experimental equipment, help to learn, and thus apply what they have learned. And go figure, when the clock has precision, school and convenient design and easy to use features, to achieve timing and time functions, have been widely used. Through this figure the simulation clock to help recognize the role of its software, in-depth analysis of its principles, to help understand the working principle of the digital clock.For design and simulation with Multisim software in the digital clock. We first created Multisim software digital clock circuit diagram of the total. And then use the software's simulation features in the simulation. Correct simulation of the digital clock should have "seconds", "sub", "when" the decimal figures, can be corrected at any time minutes and hours, when the bell when the whole point to carry out the whole time, but also can be set from time to time.Key word: EDA,Multisim,Simulation,Digital Clock目录1绪论 (1)1.1 课题背景及目的 (1)1.2 国内外研究状况 (2)1.3 论文的构成及研究内容 (2)2设计方案 (4)3 Multisim 10软件介绍 (6)3.1 Multisim 10软件简介 (6)3.2 Multisim 10软件功能 (6)3.3 Multisim 10软件发展 (6)3.4 Multisim 10软件分析工具 (7)3.5 Multisim 10仿真的基本步骤 (7)3.6 Multisim 10意义 (8)4数字时钟设计及仿真分析 (9)4.1 数字时钟设计概况 (9)4.2 数字时钟设计 (9)4.2.1 小时计时电路 (9)4.2.2 分钟计时电路 (11)4.2.3 校时选择电路 (12)4.2.4 整点译码电路 (13)4.2.5 定时比较电路 (14)4.2.6 脉冲产生和分频电路 (15)4.2.7 整点报时电路 (16)4.3 总体电路设计和仿真分析 (17)4.3.1 总体电路设计 (17)4.3.2 仿真分析 (17)结论 (19)致谢 (20)参考文献 (21)1绪论1.1课题背景及目的EDA就是(Electronic Design Automation,电子设计自动化)的缩写技术已经在电子设计领域得到广泛应用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

东北大学课程设计报告课程设计名称:数字电子技术课程设计专题题目:指导教师:学生姓名:学号:专业:计算机科学与技术班级:设计日期: 2017 年7 月 3 日~ 2017 年7 月7日目录摘要 (3)Abstract (3)第1章概述 (4)1.1设计思路 (4)1.2主要内容 (4)第2章课程设计任务及要求 (5)2.1 设计任务 (5)2.2 设计要求 (5)第3章系统设计 (6)3.1 方案论证 (6)3.2 系统设计 (6)3.2.1 结构框图及说明 (6)3.2.2 系统原理图及工作原理 (7)3.3单元电路设计 (8)3.3.1数字时钟秒脉冲信号的设计 (8)3.3.2器件分析 (8)3.3.3 计数器设计 (9)3.3.4 计时电路设计 (11)3.3.5 数字时钟电路设计 (12)3.3.6 校时电路 (12)3.3.7 整点报时 (13)3.3.8 闹钟电路 (14)第4章仿真调试 (16)4.1时钟显示 (17)4.1.1 时钟显示完整的00:00:00 (17)4.1.2 时钟完整显示01:00:00 (17)4.1.3 时钟完整显示23:59:59 (18)4.1.4 仿真开关校准“秒”电路 (18)4.1.5 仿真开关校准“分”电路 (19)4.1.6 仿真开关校准“时”电路 (19)4.2 整点报时 (20)4.2.1 07:59:50—07:59:59报时 (20)4.3 闹钟电路 (21)4.3.1 7:59:00闹钟设定 (21)第5章结论 (22)第6章利用Multisim14.0仿真软件设计体会 (23)参考文献 (23)第7章收获、体会和建议 (24)摘要时间对于人们来说总是那么的宝贵,工作的忙碌性和繁杂性容易使人们忘记当前的时间。

于是,20世纪末,,电子技术有了飞快地发展,不仅在通信技术上用数字信号替代模拟信号,数字时钟相比模拟钟能给人一种一目了然的感觉,它不仅可以同时显示时、分和秒,并且可以完成准确的校正。

数字时钟具有走时精确,校准方便设计和使用简单的特点。

对于Multisim软件进行数字时钟的设计和仿真。

首先在Multisim创建好数字时钟的总电路图。

然后用该软件中的仿真功能进行仿真。

一个数字时钟需要振荡器,计数器,译码器和显示器电路精确时间“小时”“分”“秒”与数字显示,并需要校正电路,使其准确的工作,也可有定时和计时功能。

数字钟及扩大其应用,有着非常现实的意义。

在本文中,multisim14.0的基础上设计的数字钟,由数字集成电路,数码组成。

关键词:数字钟,振荡器,计数器译码,显示,仿真AbstractThe time for people to always so precious,A busy and complex nature of the work is easy to make people forget the current time。

So, At the end of the twentieth Century,Electronic technology has been rapid development。

Not only in communication technology with digital signal instead of analog signal,but also in our daily life,Digital clock compared to analog clock can give people a feeling of stick out a mile,It not only can display hours, minutes and seconds,And it can accomplish accurate correction.Digital clock is accurate, convenient and simple in design with calibration.For design and simulation with Multisim software in digital clock .We first created Multisim software digital clock circuit diagram of the total.And then use the software’s simulation features in the simulation .a d igital clock to the oscillator,a counter,decoder and display circuit accurately time "hours" "minutes"" seconds" with digital display, and the need for correction circuit ma ke its accurate work, also can have from time to time and timekeeping function. Digital clock and the expansio n of its application, has very realistic significance. In this paper, the Multisim14.0 based on the design of the di gital clock, is composed of a digital integrated circuit, digital display.Key words: digital clock ,oscillators ,counter , decoding display , simulation第1章概述数字钟是一种用数字电路技术实现时、分、秒计时的装置,钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能。

诸如定时自动报警、按时自动打铃、时间程序自动控制、定时广播。

而且与传统的机械钟相比,它具有走时准确、显示直观、无机械传动、无需人的经常调整等优点。

数字钟的设计涉及到模拟电子与数字电子技术,其中绝大部分是数字部分、逻辑门电路、数字逻辑表达式、计算真值表与逻辑函数间的关系、编码器、译码器显示等基本原理。

现在主要用各种芯片实现其功能,更加方便和准确。

Multisim14.0作为一种高效的设计与仿真平台。

其强大的虚拟仪器库和软件仿真功能,为电路设计提供了先进的设计理念和方法。

本课题要求设计一个数字电子时钟的控制电路。

该电路用于反映电路的时间显示,时钟共有六个显示屏。

当电路启动时,以启动时间为初始时间,按正常时间进行计时和报时操作。

当需要对时间进行调试的时候需要对时分秒三个部分都进行必要的调时工作。

当时间显示为整时(即整点)时需要进行响铃提示操作。

1.1 设计思路经过以上所述的设计内容及要求的分析,可以将电路分为以下几部分:1.由秒时钟信号发生器、计时电路和校时电路构成电路。

2.首先由开关控制电路,进而对时间进行调时调分调秒操作,开关电路包括:非门,异或门,与非门,电阻,直流稳压电源。

分别控制输出的接通与断开以便达到控制各芯片工作的目的。

3.其次将开关电路输出的信号输入到74LS160芯片分别控制显示时分秒的逐步递增。

4.通过级联将74LS160芯片扩展为24进制和十进制的计数器,秒和分之间,分和时之间的进制为60进制。

5.计时电路中采用两个60进制计数器分别完成秒计时和分计时;24进制计数器完成时计时;采用译码器将计数器的输出译码后送七段数码管显示。

6.校时电路采用开关控制时、分、秒计数器的时钟信号为校时脉冲以完成校时7.系统应具有整点报时功能,因此,应有译码电路将整点时间识别出来,同时应有报时电路。

8.系统应有定时功能,因此,应有定时输入电路和时间比较电路。

9.系统应具有闹钟功能。

10. 理论部分用Multisim14软件进行仿真,并且达到设计要求。

1.2主要内容熟悉Multisim14.0仿真软件的应用;设计一个具有显示、校时、整点报时和定时功能的数字时钟,.能独立完成整个系统的设计;用Multisim14.0仿真实现数字时钟的功能第2章课程设计任务及要求2.1 设计任务设计一个数字时钟电路,实现显示时间、调整时间、整点报时、闹铃提醒等功能。

2.2 设计要求设计数字时钟需要有六个显示屏来显示时间,根据课程设计中提出的需求,设计出的时钟电路应当满足如下要求:1.启动时钟后,时钟可以进行正常的时间按秒增加;2.时钟可以正常显示信息;3.时钟的进制正常,即秒与分之间,分与时之间均为六十进制,当表示小时的部分为24时全体清零;4.时钟具备整点报时功能,即当显示时间为整点时应当有响铃提示。

5.时钟具备闹铃功能,当时间达到预设时间时应当有响铃提示。

第3章系统设计3.1 方案论证根据课程设计中提到的设计要求,结合本学期课程内容及所学,本方案设计了一个“数字电子时钟控制电路”。

考虑到“数字电子时钟控制电路”作为数字电子技术课程的基础实践,遂对该设计进行分析后考虑选取片选如下:四位十进制计数器74LS160,二输入与非门74LS00,二输入正与门74LS08,二输入正或门74LS32,非门74LS04,四输入与或门74LS20,74LS85以及电阻、开关、蜂鸣器等。

该设计方案主要通过74LS160以及该片选的级联构成所需要的进制计数器并通过各型逻辑门芯片向其他位产生进位信号,构成数字时钟的基本功能,通过74LS85进行比较完成闹铃设定功能。

数字时钟电路主要由时、分、秒三部分组成,秒时钟电路主要由秒脉冲信号发生器、计数器、译码器、数码管组成,秒计数周期60s。

同样分时钟电路由计数器、译码器、数码管组成,计数周期为60m,与秒时钟电路不同的是脉冲信号由秒时钟电路提供。

时时钟电路采用同样的设计,计数周期为24h。

3.2 系统设计根据课程设计题目要求,对该电路控制系统进行一系列设计,现说明如下。

3.2.1 结构框图及说明图3.2.1 数字电子钟框图说明:数字电子钟实际上是一个对标准频率(1HZ)进行计数的计数电路。

由于计数的起始时间不可能与标准时间(例如北京时间)一致,故需要在电路上加上一个校时电路,同时标准的1HZ时间信号必须做到准确稳定,通常使用555定时器产生脉冲,从而得出数字电子钟的功能结构框图如图3.2.1所示。

3.2.2 系统原理图及工作原理图3.2.2.1 数字电子钟执行原理流程图根据各单元电路的设计,将555定时器构成的多谐振荡器、校对电路、六十进制秒、分计数器及二十四进制时计数器、开关控制电路、译码及显示电路、整点报时电路和比较器构成的闹钟电路进行整合调试得到所设计的数字电子钟控制电路的总原理图。