微机原理与接口技术-第三章-课后答案

微机原理与接口技术 张颖超 叶彦斐 第3章 习题答案

MULCL

MOVCX, AX

MOVAL, CL

MOVAH, 0

MULCX

13.假设DX:AX中存放一个双字的数据:

NEG DX

NEG AX

SBB DX,0

请问:

(1)上述程序段完成什么功能?

(2)设执行前,DX=0001H,AX=FFFFH,上述程序段执行后,DX、AX的值是什么?

(1)清累加器AX;

(2)清进位标志位

(3)将累加器内容乘以2(不考虑溢出)

(4)将累加器内容除以2(不考虑余数)

答:

(1) a.XORAX, AX

b.SUBAX, AX

c.ANDAX,0

d.MOVAX,0

(2) a.SUBAX, AX

b.ANDAX, AX

c.ORAX, AX

d.XORAX, AX

(7)检查BX中的第2、6、10和12位是否同时为0。

答:

(1) ANDDL, 0FCH;1111 1100B

(2)ORSI, 0E000H;1110 0000 0000 0000B

(3)ANDAX, 0FFF0H;1111 1111 1111 0000B

ORAX, 0380H; 0000 0011 1000 0000B

(1) IN AL, PORT; AL=

(2) IN AL, 40H;AX=

(3) OUTDX,AL; (DX)=

(4) OUT DX, AX; (DX)=

答:

(1)AL=22H

(2) IN AX, 40H; AX=226EH

(3) OUTDX,AL; (DX)=6EH

(4) OUT DX, AX; (DX)=226EH

微型计算机原理和接口技术第三章课后答案

微型计算机原理和接口技术第三章课后答案本文回答了微型计算机原理和接口技术第三章的课后题目,涵盖了数字逻辑电路、组合逻辑电路、时序逻辑电路和存储器等内容。

1. 数字逻辑电路1.1. 逻辑电路和数字逻辑电路的基本概念逻辑电路是由逻辑门(与门、或门、非门等)和触发器等基本逻辑元件组合而成的电路。

数字逻辑电路是逻辑电路在数字系统中的应用,主要用于实现数字信号的逻辑运算和信号的转换等功能。

1.2. 数字逻辑门电路的组合和简化数字逻辑电路中常见的逻辑门有与门(AND)、或门(OR)、非门(NOT)等。

这些逻辑门可以通过组合和简化来构造更复杂的逻辑电路,例如与非门(NAND)、或非门(NOR)等。

1.3. 数字逻辑电路的时序特性数字逻辑电路的时序特性主要包括延迟时间、上升时间和下降时间等。

延迟时间表示信号经过电路的传播所需的时间,上升时间和下降时间表示信号从一个逻辑状态到另一个逻辑状态所需的时间。

2. 组合逻辑电路2.1. 组合逻辑电路的定义和特点组合逻辑电路是由多个逻辑门组合而成的电路,输入信号直接决定输出信号,不涉及时钟信号和状态存储。

2.2. 组合逻辑电路的设计方法组合逻辑电路的设计方法主要有真值表法、卡诺图法和特征方程法。

真值表法通过列出输入输出的真值表来进行设计,卡诺图法通过画出卡诺图进行化简,特征方程法通过建立逻辑方程进行设计。

2.3. 组合逻辑电路的应用组合逻辑电路广泛应用于数字系统中,包括逻辑运算、数据选择、数据的编码和解码等功能。

3. 时序逻辑电路3.1. 时序逻辑电路的定义和特点时序逻辑电路是由触发器和组合逻辑电路组合而成的电路,通过时钟信号来控制触发器的状态转换。

时序逻辑电路具有状态存储的功能,可以实现存储和记忆功能。

3.2. 触发器和时序逻辑电路的设计方法触发器是时序逻辑电路的基本组件,常见的触发器包括SR 触发器、D触发器和JK触发器等。

时序逻辑电路的设计方法主要是通过状态转换图、状态转移表和重建方程等方法进行设计。

微机原理与接口技术第三章试题及答案

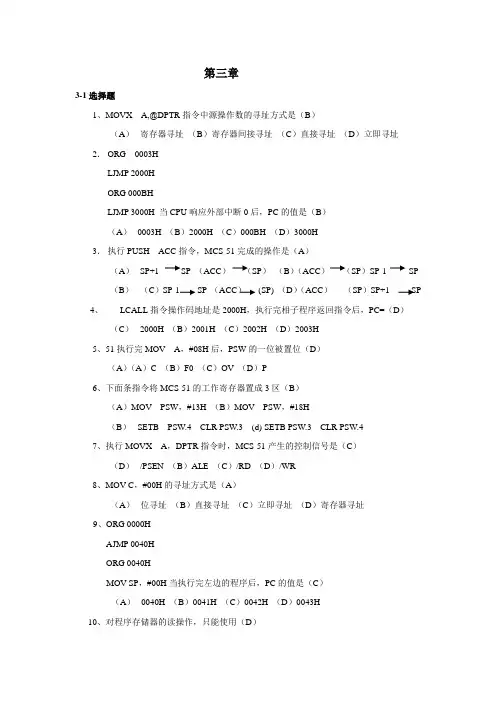

第三章3-1选择题1、MOVX A,@DPTR指令中源操作数的寻址方式是(B)(A)寄存器寻址(B)寄存器间接寻址(C)直接寻址(D)立即寻址2.ORG 0003HLJMP 2000HORG 000BHLJMP 3000H 当CPU响应外部中断0后,PC的值是(B)(A)0003H (B)2000H (C)000BH (D)3000H3.执行PUSH ACC指令,MCS-51完成的操作是(A)(A)SP+1 SP (ACC)(SP)(B)(ACC)(SP)SP-1 SP(B)(C)SP-1 SP (ACC)(SP) (D)(ACC)(SP)SP+1 SP4、LCALL指令操作码地址是2000H,执行完相子程序返回指令后,PC=(D)(C)2000H (B)2001H (C)2002H (D)2003H5、51执行完MOV A,#08H后,PSW的一位被置位(D)(A)(A)C (B)F0 (C)OV (D)P6、下面条指令将MCS-51的工作寄存器置成3区(B)(A)MOV PSW,#13H (B)MOV PSW,#18H(B)SETB PSW.4 CLR PSW.3 (d) SETB PSW.3 CLR PSW.47、执行MOVX A,DPTR指令时,MCS-51产生的控制信号是(C)(D)/PSEN (B)ALE (C)/RD (D)/WR8、MOV C,#00H的寻址方式是(A)(A)位寻址(B)直接寻址(C)立即寻址(D)寄存器寻址9、ORG 0000HAJMP 0040HORG 0040HMOV SP,#00H当执行完左边的程序后,PC的值是(C)(A)0040H (B)0041H (C)0042H (D)0043H10、对程序存储器的读操作,只能使用(D)(A)MOV指令(B)PUSH指令(C)MOVX指令(D)MOVC指令3-2判断题。

4.MCS-51的相对转移指令最大负跳距是127B。

微机原理与接口技术习题答案3

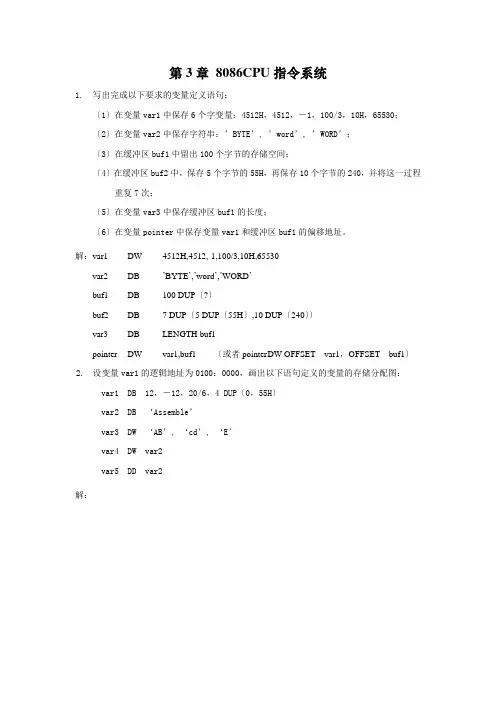

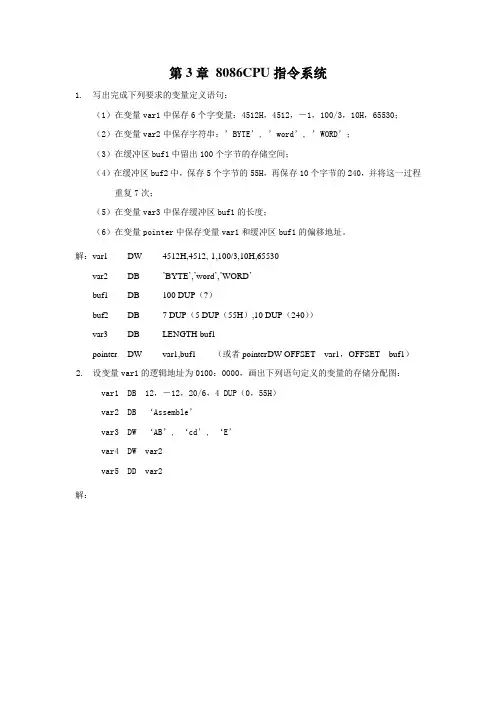

第3章8086CPU指令系统1.写出完成以下要求的变量定义语句:〔1〕在变量var1中保存6个字变量:4512H,4512,-1,100/3,10H,65530;〔2〕在变量var2中保存字符串:’BYTE’, ’word’, ’WORD’;〔3〕在缓冲区buf1中留出100个字节的存储空间;〔4〕在缓冲区buf2中,保存5个字节的55H,再保存10个字节的240,并将这一过程重复7次;〔5〕在变量var3中保存缓冲区buf1的长度;〔6〕在变量pointer中保存变量var1和缓冲区buf1的偏移地址。

解:var1 DW 4512H,4512,-1,100/3,10H,65530var2 DB ’BYTE’,’word’,’WORD’buf1 DB 100 DUP〔?〕buf2 DB 7 DUP〔5 DUP〔55H〕,10 DUP〔240〕〕var3 DB LENGTH buf1pointer DW var1,buf1 〔或者pointer D W OFFSET var1,OFFSET buf1〕2.设变量var1的逻辑地址为0100:0000,画出以下语句定义的变量的存储分配图:var1 DB 12,-12,20/6,4 DUP〔0,55H〕var2 DB ‘Assemble’var3 DW ‘AB’, ‘cd’, ‘E’var4 DW var2var5 DD var2解:3.指令正误判断,对正确指令写出源和目的操作数的寻址方式,对错误指令指出原因〔设VAR1, VAR2为字变量, L1为标号〕:〔1〕MOV SI,100 〔2〕MOV BX,VAR1[SI]〔3〕MOV AX, [BX] 〔4〕MOV AL, [DX]〔5〕MOV BP, AL 〔6〕MOV VAR1, VAR2〔7〕MOV CS, AX 〔8〕MOV DS, 0100H〔9〕MOV [BX][SI], 1 〔10〕MOV AX, VAR1+VAR2〔11〕ADD AX, LENGTH VAR1 〔12〕OR BL, TYPE VAR2〔13〕SUB [DI], 78H 〔14〕MOVS VAR1, VAR2〔15〕PUSH 100H 〔16〕POP CS〔17〕XCHG AX, ES 〔18〕MOV DS, CS〔19〕JMP L1+5 〔20〕DIV AX, 10〔21〕SHL BL, 2 〔22〕MOV AL, 15+23〔23〕MUL CX 〔24〕XCHG CL, [SI]〔25〕ADC CS:[0100], AH 〔26〕SBB VAR1-5,154解:〔1〕MOV SI,100 正确。

微机原理与接口技术习题答案3讲解

第3章8086CPU指令系统1.写出完成下列要求的变量定义语句:(1)在变量var1中保存6个字变量:4512H,4512,-1,100/3,10H,65530;(2)在变量var2中保存字符串:’BYTE’, ’word’, ’WORD’;(3)在缓冲区buf1中留出100个字节的存储空间;(4)在缓冲区buf2中,保存5个字节的55H,再保存10个字节的240,并将这一过程重复7次;(5)在变量var3中保存缓冲区buf1的长度;(6)在变量pointer中保存变量var1和缓冲区buf1的偏移地址。

解:var1 DW 4512H,4512,-1,100/3,10H,65530var2 DB ’BYTE’,’word’,’WORD’buf1 DB 100 DUP(?)buf2 DB 7 DUP(5 DUP(55H),10 DUP(240))var3 DB LENGTH buf1pointer DW var1,buf1 (或者pointer D W OFFSET var1,OFFSET buf1)2.设变量var1的逻辑地址为0100:0000,画出下列语句定义的变量的存储分配图:var1 DB 12,-12,20/6,4 DUP(0,55H)var2 DB ‘Assemble’var3 DW ‘AB’, ‘cd’, ‘E’var4 DW var2var5 DD var2解:3.指令正误判断,对正确指令写出源和目的操作数的寻址方式,对错误指令指出原因(设VAR1, VAR2为字变量, L1为标号):(1)MOV SI,100 (2)MOV BX,VAR1[SI](3)MOV AX, [BX] (4)MOV AL, [DX](5)MOV BP, AL (6)MOV VAR1, VAR2(7)MOV CS, AX (8)MOV DS, 0100H(9)MOV [BX][SI], 1 (10)MOV AX, VAR1+VAR2(11)ADD AX, LENGTH VAR1 (12)OR BL, TYPE VAR2(13)SUB [DI], 78H (14)MOVS VAR1, VAR2(15)PUSH 100H (16)POP CS(17)XCHG AX, ES (18)MOV DS, CS(19)JMP L1+5 (20)DIV AX, 10(21)SHL BL, 2 (22)MOV AL, 15+23(23)MUL CX (24)XCHG CL, [SI](25)ADC CS:[0100], AH (26)SBB VAR1-5,154解:(1)MOV SI,100 正确。

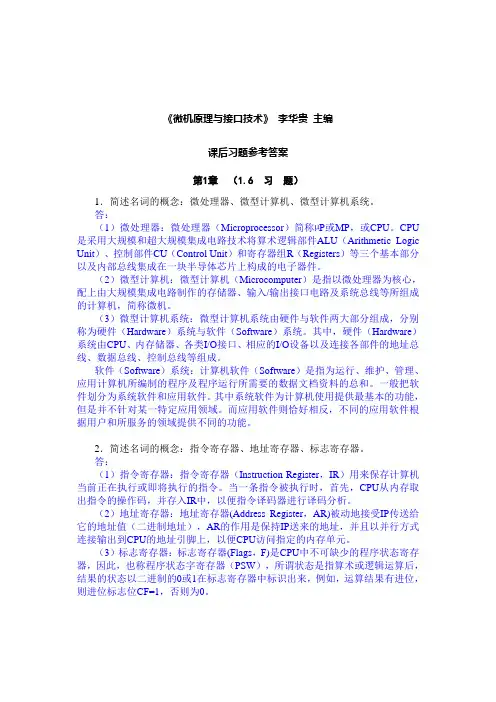

微机原理与接口技术课后习题参考答案

《微机原理与接口技术》李华贵主编课后习题参考答案第1章(1.6 习题)1.简述名词的概念:微处理器、微型计算机、微型计算机系统。

答:(1)微处理器:微处理器(Microprocessor)简称µP或MP,或CPU。

CPU 是采用大规模和超大规模集成电路技术将算术逻辑部件ALU(Arithmetic Logic Unit)、控制部件CU(Control Unit)和寄存器组R(Registers)等三个基本部分以及内部总线集成在一块半导体芯片上构成的电子器件。

(2)微型计算机:微型计算机(Microcomputer)是指以微处理器为核心,配上由大规模集成电路制作的存储器、输入/输出接口电路及系统总线等所组成的计算机,简称微机。

(3)微型计算机系统:微型计算机系统由硬件与软件两大部分组成,分别称为硬件(Hardware)系统与软件(Software)系统。

其中,硬件(Hardware)系统由CPU、内存储器、各类I/O接口、相应的I/O设备以及连接各部件的地址总线、数据总线、控制总线等组成。

软件(Software)系统:计算机软件(Software)是指为运行、维护、管理、应用计算机所编制的程序及程序运行所需要的数据文档资料的总和。

一般把软件划分为系统软件和应用软件。

其中系统软件为计算机使用提供最基本的功能,但是并不针对某一特定应用领域。

而应用软件则恰好相反,不同的应用软件根据用户和所服务的领域提供不同的功能。

2.简述名词的概念:指令寄存器、地址寄存器、标志寄存器。

答:(1)指令寄存器:指令寄存器(Instruction Register,IR)用来保存计算机当前正在执行或即将执行的指令。

当一条指令被执行时,首先,CPU从内存取出指令的操作码,并存入IR中,以便指令译码器进行译码分析。

(2)地址寄存器:地址寄存器(Address Register,AR)被动地接受IP传送给它的地址值(二进制地址),AR的作用是保持IP送来的地址,并且以并行方式连接输出到CPU的地址引脚上,以便CPU访问指定的内存单元。

微机原理与接口技术 张颖超 叶彦斐 第3章 习题解答

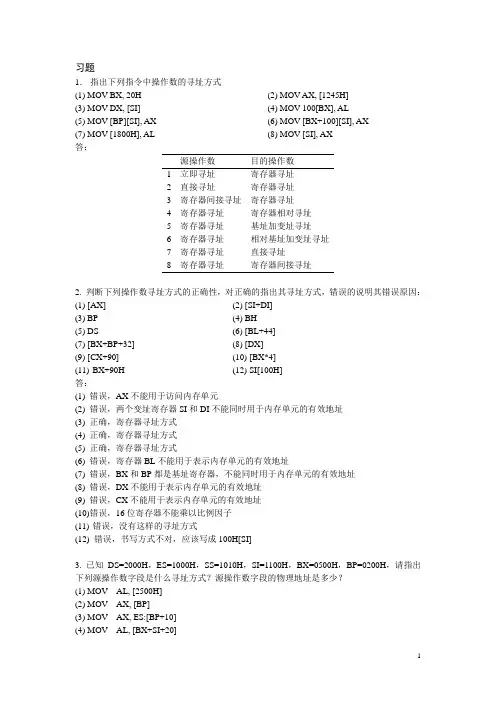

习题1.指出下列指令中操作数的寻址方式(1) MOV BX, 20H (2) MOV AX, [1245H](3) MOV DX, [SI] (4) MOV 100[BX], AL(5) MOV [BP][SI], AX (6) MOV [BX+100][SI], AX(7) MOV [1800H], AL (8) MOV [SI], AX答:源操作数目的操作数1 立即寻址寄存器寻址2 直接寻址寄存器寻址3 寄存器间接寻址寄存器寻址4 寄存器寻址寄存器相对寻址5 寄存器寻址基址加变址寻址6 寄存器寻址相对基址加变址寻址7 寄存器寻址直接寻址8 寄存器寻址寄存器间接寻址2. 判断下列操作数寻址方式的正确性,对正确的指出其寻址方式,错误的说明其错误原因:(1) [AX] (2) [SI+DI](3) BP (4) BH(5) DS (6) [BL+44](7) [BX+BP+32] (8) [DX](9) [CX+90] (10) [BX*4](11) BX+90H (12) SI[100H]答:(1) 错误,AX不能用于访问内存单元(2) 错误,两个变址寄存器SI和DI不能同时用于内存单元的有效地址(3) 正确,寄存器寻址方式(4) 正确,寄存器寻址方式(5) 正确,寄存器寻址方式(6) 错误,寄存器BL不能用于表示内存单元的有效地址(7) 错误,BX和BP都是基址寄存器,不能同时用于内存单元的有效地址(8) 错误,DX不能用于表示内存单元的有效地址(9) 错误,CX不能用于表示内存单元的有效地址(10)错误,16位寄存器不能乘以比例因子(11) 错误,没有这样的寻址方式(12) 错误,书写方式不对,应该写成100H[SI]3. 已知DS=2000H,ES=1000H,SS=1010H,SI=1100H,BX=0500H,BP=0200H,请指出下列源操作数字段是什么寻址方式?源操作数字段的物理地址是多少?(1) MOV AL, [2500H](2) MOV AX, [BP](3) MOV AX, ES:[BP+10](4) MOV AL, [BX+SI+20]答:(1)源操作数属于直接寻址,物理地址=DS⨯16+2500H=20000H+2500H=22500H;(2)源操作数属于寄存器间接寻址,物理地址=SS⨯16+(BP)=10100H+0200H=10300H(3)源操作数属于寄存器相对寻址,物理地址=ES⨯16+(BP)+100=10000H+0200H+0AH=1020AH(4)源操作数属于基址加变址寻址,物理地址=DS⨯16+(BX)+(SI)+20=20000H+0500H+1100H+14H=21614H4. 判断下列指令的对错,如果错误请说明原因。

微机原理与接口技术习题参考答案3-13章..

微机原理与接口技术习题参考答案3-13章..习题3.1 什么是总线?总线是如何分类的?答:总线,是一组能为多个功能部件服务的公共信息传送线路,是计算机各部件之间的传送数据、地址和控制信息的公共通路,它能分时地发送与接收各部件的信息。

按照总线系统的层次结构,可以把总线分为片内总线、系统总线、局部总线和外设总线。

3.2 举例说明有哪些常见的系统总线与外设总线。

答:常见的系统总线有:ISA总线、PCI总线、PCI Express总线。

常见的外设总线有:RS-232串行总线、IEEE1394串行总线、USB串行总线。

3.3 ISA总线的主要特点是什么?答:ISA总线的主要特点是:(1)总线支持力强,支持64KB的I/O地址空间、24位存储器地址空间、8/16位数据存取、15级硬件中断、7个DMA通道等。

(2)16位ISA总线是一种多主控(Multi Master)总线,可通过系统总线扩充槽中的MAST ER的信号线实现。

除CPU外,DMA控制器、刷新控制器和带处理器的智能接口卡都可以成为ISA总线的主控设备。

(3)支持8种类型的总线周期,分别为8/16位的存储器读周期、8/16位的存储器写周期、8/16位的I/O读周期、8/16位的I/O写周期、中断请求和中断响应周期、DMA周期、存储器刷新周期和总线仲裁周期。

3.4 PCI总线的主要特点是什么?答:PCI总线的特点概述如下:(1) 线性突发传输:PCI支持突发的数据传输模式,满足了新型处理器高速缓冲存储器(Cache)与内存之间的读写速度要求。

线性突发传输能够更有效地运用总线的带宽去传输数据,以减少不必要的寻址操作。

(2) 多总线主控:PCI总线不同于ISA总线,其地址总线和数据总线是分时复用的。

这样减少了接插件的管脚数,便于实现突发数据的传输。

数据传输时,一个PCI设备作为主控设备,而另一个PCI设备作为从设备。

总线上所有时序的产生与控制,都是由主控设备发起的。

微机原理与接口技术张颖超叶彦斐第3章习题答案

习题1.指出下列指令中操作数的寻址方式(1) MOV BX, 20H (2) MOV AX, [1245H](3) MOV DX, [SI] (4) MOV 100[BX], AL(5) MOV [BP][SI], AX (6) MOV [BX+100][SI], AX(7) MOV [1800H], AL (8) MOV [SI], AX答:源操作数目的操作数1 立即寻址寄存器寻址2 直接寻址寄存器寻址3 寄存器间接寻址寄存器寻址4 寄存器寻址寄存器相对寻址5 寄存器寻址基址加变址寻址6 寄存器寻址相对基址加变址寻址7 寄存器寻址直接寻址8 寄存器寻址寄存器间接寻址2. 判断下列操作数寻址方式的正确性,对正确的指出其寻址方式,错误的说明其错误原因:(1) [AX] (2) [SI+DI](3) BP (4) BH(5) DS (6) [BL+44](7) [BX+BP+32] (8) [DX](9) [CX+90] (10) [BX*4](11) BX+90H (12) SI[100H]答:(1) 错误,AX不能用于访问内存单元(2) 错误,两个变址寄存器SI和DI不能同时用于内存单元的有效地址(3) 正确,寄存器寻址方式(4) 正确,寄存器寻址方式(5) 正确,寄存器寻址方式(6) 错误,寄存器BL不能用于表示内存单元的有效地址(7) 错误,BX和BP都是基址寄存器,不能同时用于内存单元的有效地址(8) 错误,DX不能用于表示内存单元的有效地址(9) 错误,CX不能用于表示内存单元的有效地址(10)错误,16位寄存器不能乘以比例因子(11) 错误,没有这样的寻址方式(12) 错误,书写方式不对,应该写成100H[SI]3. 已知DS=2000H,ES=1000H,SS=1010H,SI=1100H,BX=0500H,BP=0200H,请指出下列源操作数字段是什么寻址方式?源操作数字段的物理地址是多少?(1) MOV AL, [2500H](2) MOV AX, [BP](3) MOV AX, ES:[BP+10](4) MOV AL, [BX+SI+20]答:(1)源操作数属于直接寻址,物理地址=DS⨯16+2500H=20000H+2500H=22500H;(2)源操作数属于寄存器间接寻址,物理地址=SS⨯16+(BP)=10100H+0200H=10300H(3)源操作数属于寄存器相对寻址,物理地址=ES⨯16+(BP)+100=10000H+0200H+0AH=1020AH(4)源操作数属于基址加变址寻址,物理地址=DS⨯16+(BX)+(SI)+20=20000H+0500H+1100H+14H=21614H4. 判断下列指令的对错,如果错误请说明原因。

微机原理与接口技术 课后答案龚尚福

微机原理与接口技术课后答案龚尚福第一章:计算机基础知识1.什么是计算机?计算机有哪些基本组成部分?–计算机是一种可以按照预定程序自动进行数值和非数值计算的设备。

–计算机的基本组成部分包括中央处理器(CPU)、存储器、输入设备、输出设备和控制器。

2.什么是微型计算机?微型计算机的特点有哪些?–微型计算机是指体积小、价格低廉的小型计算机系统。

–微型计算机的特点包括:体积小、成本低、功耗低、易于携带、可扩展性好等。

3.什么是冯·诺依曼体系结构?它包括哪些基本特点?–冯·诺依曼体系结构是一种计算机的基本设计思想,它将存储器和处理器分开,通过总线进行数据和指令的传输。

–冯·诺依曼体系结构的基本特点包括:存储程序、以二进制表示信息、存储器与处理器分离、由指令控制程序执行的顺序。

第二章:数字电路基础知识1.什么是逻辑门?常用的逻辑门有哪些?–逻辑门是一种用于实现逻辑运算的电路元件,根据输入信号的不同组合产生相应的输出信号。

–常用的逻辑门有与门(AND)、或门(OR)、非门(NOT)、异或门(XOR)等。

2.什么是布尔逻辑运算?常见的布尔逻辑运算有哪些?–布尔逻辑运算是指利用布尔代数进行逻辑运算的方法。

–常见的布尔逻辑运算有与运算(AND)、或运算(OR)、非运算(NOT)等。

3.什么是半加器和全加器?它们的作用是什么?–半加器是一种用于实现二进制数相加的电路,它可以将两个输入信号相加并产生相应的进位和和。

–全加器是一种用于实现三个二进制数相加的电路,它可以将三个输入信号相加并产生相应的进位和和。

第三章:微处理器基础知识1.什么是微处理器?它的功能有哪些?–微处理器是一种集成电路,它由控制单元、算术逻辑单元、寄存器和时钟等功能模块组成,用于执行计算机程序。

–微处理器的功能包括指令译码、执行算术和逻辑运算、读写存储器、控制外部设备等。

2.什么是指令?指令由哪些部分组成?常见的指令有哪些?–指令是微处理器执行操作的基本单位,它们以二进制的形式存储在存储器中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第三章参考答案1.按照题目中提出的要求,写出能达到要求的一条(或几条)汇编形式的指令:⑴将一个立即数送入寄存器BX;⑵将一个立即数送入段寄存器DS;⑶将变址寄存器DI的内容送入一个存储单元中;⑷从存储单元中取一个数送到段寄存器ES中;⑸将立即数0ABH与AL相加,结果送回AL中;⑹把BX与CX寄存器内容相加,结果送入BX;⑺用寄存器间接寻址方式,实现一个立即数与存储单元内容相加,结果放回存储器。

解:(1)MOV BX, 1234H(2)MOV AX, 1234HMOV DS, AX(3)MOV [BX], DI(4)MOV ES,[BX](5)ADD AL,0ABH(6)ADD BX,CX(7)MOV AX,[BX]ADD AX,1234HMOV [BX],AX2.执行下面程序,完成指令后的填空:MOV AX,2000H ;AH= 20HMOV DS,AX ;AL= 00H DS= 2000HMOV SS,AX ;SS= 2000H AX= 2000H MOV BX,2030H ;BH= 20H BL= 30H MOV SI,BX ;SI= 2030HMOV DI,3040H ;DI= 3040HMOV SI,DI ;SI= 3040HMOV SP,50FFH ;SP= 50FFHMOV DX,SP ;DH= 50H DL= FFH MOV CL,25 ;CL= 19HMOV BL,CL ;CL= 19H BL= 19HMOV AH,0F0H ;AH= F0HMOV CH,AH ;CH= F0HMOV BYTE PTR[DI],64 ;(DI)= 40HMOV WORD PTR[SI],256 ;(SI)= 00H (SI+1)= 01H MOV DL,[SI+1] ;DL= 01HMOV DH,1+[SI] ;DH= 00HMOV AL,1[SI] ;AL= 01HMOV WORD PTR[BX][SI],34 ;(BX+SI)= 22H (BX+SI+1)= 00HMOV [BX+SI+4],BL ;(BX+SI+4)= 19HMOV BP,2[BX+DI] ;BP= 00HMOV [BP],AL ;(BP)= 01HMOV AX,[BP][DI] ;AX= 0100HMOV BL,AL ;BL= 00HMOV ES,BX ;ES= 2000HPUSH BX ;SP= 50FDH (SP,SP+1)= 2000HPUSH DI ;SP= 50FBH (SP,SP+1)=F019HPOP CX ;SP= 50FDH CX= 3040HPOP DX ;SP= 50FFH DX= 2000H XCHG AX,BP ;AX= 0000H BP= 0100HXCHG DH,BL ;DH= 00H BL= 20HLAHF ;FLAG= 0002H AH= 02HSAHF ;FLAG= 0002H AH= 02HPUSHF ;SP= 50FDH (SP,SP+1)= 0002HPOPF ;SP= 50FFH FLAG= 0002H3.设DS=2000H,ES=2100H,SS=1500H,SI=00A0H。

BX=0100H,BP=0010H,数据段中变量名VAL的偏移地址值是0050H,指出下列源操作数字段的寻址方式是什么?其物理地址值是多少?⑴MOV AX,0ABH⑵MOV AX,BX⑶MOV AX,[100H]⑷MOV AX,VAL⑸MOV AX,[BX]⑹MOV AX,ES:[BX]⑺MOV AX,[BP]⑻MOV AX,[SI]⑼MOV AX,[BX+10]⑽MOV AX,VAL[BX]⑾MOV AX,[BX][SI]⑿MOV AX,VAL[BX][SI]解:(1)立即寻址方式(2)寄存器寻址方式(3)直接寻址方式;其物理地址为:20100H(4)直接寻址方式;其物理地址为:20050H(5)寄存器间接寻址方式;其物理地址为:20100H(6)寄存器间接寻址方式;其物理地址为:21100H(7)寄存器间接寻址方式;其物理地址为:15010H(8)寄存器间接寻址方式;其物理地址为:200A0H(9)寄存器相对寻址方式;其物理地址为:20110H(10)寄存器相对寻址方式;其物理地址为:20150H(11)基址变址寻址方式;其物理地址为:201A0H(12)相对基址变址寻址方式;其物理地址为:201F0H4.如果TABEL为数据段中0032H单元的符号名,其中存放的内容为1234H,试问以下两条指令有什么区别?指令执行后,AX寄存器的内容各是什么?。

MOV AX,TABELLEA AX,TABEL解:指令MOV AX,TABEL 是取出地址为TABEL的内存单元内容,执行结束后AX=1234H 指令LEA AX,TABEL 是取出符号地址的数值,执行结束后AX=0032H.5.已知堆栈段寄存器SS的内容是0FFA0H,堆栈指针寄存器SP的内容是00B0H,先执行两条把8057H和0F79H分别进栈的PUSH指令,再执行一条POP指令。

试画出堆栈区和SP的内容变化过程示意图(标出存储单元的物理地址)。

解:6.求出以下各十六进制数与十六进制数62A0H 之和,并根据结果设置标志位SF 、ZF 、CF和OF 的值。

⑴1234H⑵4321H ⑶CFA0H⑷9D60H解:(1)结果74DEH :SF=0;ZF=0;CF=0;OF=0。

(2)结果A5C1EH :SF=1;ZF=0;CF=1;OF=1。

(3)结果3240H :SF=0;ZF=0;CF=1;OF=0。

(4)结果0000H :SF=0;ZF=1;CF=1;OF=0。

7.求出以下各十六进制数与十六进制数4AE0H 的差值,并根据结果设置标志位SF 、ZF 、CF 和OF 的值。

⑴1234H⑵5D90H ⑶9090H⑷EA04H解:(1)结果:C754H ;SF=1;ZF=0;CF=1;OF=0。

(2)结果:12B0H ;SF=0;ZF=0;CF=0;OF=0。

(3)结果:45B0H ;SF=0;ZF=0;CF=0;OF=0。

(4)结果:9F24H ;SF=1;ZF=0;CF=0;OF=0。

8.假设BX =0E3H ,变量VALUE 中存放的内容为79H ,确定下列各条指令单独执行后的结果。

⑴XOR BX ,VALUE⑵AND BX ,VALUE ⑶OR BX ,VALUE⑷XOR BX ,0FFH ⑸AND BX ,0⑹TEST BX ,01H解:(1)BX=9AH (2)BX=61H (3)BX=FBH (4)BX=1CH (5)BX=00H (6)BX=E3H9.试写出执行下列指令序列后BX 寄存器的内容。

执行前BX =6D16H 。

MOV CL ,7SHR BX ,CL解:执行后BX=00DAHFFAB0HFFAAEHFFAACH10. 试分析以下程序段所完成的功能。

MOV CL,04SHL DX,CLMOV BL,AHSHL AX,CLSHR BL,CLOR DL,BL解:程序段完成由DX和AX共同组成的32位数向左移动4位。

11.写一程序段:比较两个5字节的字符串OLDS和NEWS,如果OLDS字符串不同于NEWS字符串,则执行NEW_LESS;否则顺序执行程序。

解:参考程序: MOV AX,DSMOV ES,AXMOV CX,0005HLEA SI,OLDSLEA DI,NEASCLDREPZ SCASBJNZ NEW_LESS…12.假定AX和BX中内容为带符号数,CX和DX中的内容为无符号数,请用比较指令和条件转移指令实现以下判断:⑴若DX的内容超过CX的内容,则转去执行EXCEED;⑵若BX的内容大于AX的内容,则转去执行EXCEED;⑶若CX的内容等于0,则转去执行ZERO;⑷若BX与AX的内容相比较是否产生溢出?若溢出则转OVERFLOW;⑸若BX的内容小于等于AX的内容,则转EQ_SMA;⑹若DX的内容低于等于CX的内容,则转EQ_SMA。

解:(1)CMP DX,CXJA EXCEED(2) CMP BX, AXJG EXCEED(3) CMP CX, 0JZ ZERO(4) CMP BX, AXJO OVERFLOW(5) CMP BX, AXJLE EQ_SMA(6) CMP DX, CXJBE EQ_SMA13.假设X和X+2单元的内容为双精度数p,Y和Y+2单元的内容为双精度数q(X和Y 为低位字),试说明下列程序段做什么工作?MOV DX,X+2MOV AX,XADD AX,XADC DX,X+2CMP DX,Y+2JL L2 JG L1 CMP AX ,Y JBE L2 L1: MOV AX ,1JMP SHORT EXIT L2: MOV AX ,2 EXIT : INT 20H解:当2p>q 时,AX 的内容置成1;当2p<=q 时,AX 的内容置成2。

14.要求测试STATUS 中的一个字节,如果第1、3、5位均为1则转移到ROUTINE_1;如果此三位中有两位为1则转移到ROUTINE_2;如果此三位只有一位为1则转移到ROUTINE_3;如果此3位全为0则转移到ROUTINE_4。

试画出流程图,并编制相应程序段。

解:流程图如下:转ROUTINE_3转ROUTINE_4 ROUTINE_1 转ROUTINE_2。