形式化验证工具Formalityshi实验报告

认识形式化验证

认识形式化验证 软件开发中⼀般使⽤“测试”来找bug,这种⽅法只能找到bug,不能证明程序没有bug。

形式化验证是⽤逻辑来验证程序的可靠性,就是把⼀段程序⽤逻辑的⽅法证明⼀遍,证明它能得到预期的结果,没有bug。

⼀般这类研究主要应⽤于昂贵的航天器材的操作系统、危险的医疗设备的程序之中。

因为航天器材、医疗设备牵扯到⼈的⽣命,如果操作系统出现错误,那么很危险,⼜不能⽤测试⼀遍⼀遍的测,所以⽤形式化验证来做。

⽐如美国航天局NASA就会雇佣⼤批形式化验证的专家来验证他们操作系统的正确性。

学习这个⽅向,最好有⽐较好的逻辑知识(数理逻辑、拉姆达验算),最好⽐较了解程序(⽐如操作系统的设计、编译器的设计等)。

这个⽅向是⽐较犀利的研究⽅向,但不⼤容易出论⽂,需要长时间积累才能发⼀篇好论⽂。

这个⽅向只是科研⽅向,不适合找⼯作,如果你读完硕⼠打算找⼯作⽽不做研究,这个⽅向不适合。

因为企业没⼈⽤形式化验证来验证程序。

Formal Verification(形式验证) 在计算机硬件(特别是集成电路)和软件系统的设计过程中,形式验证的含义是根据某个或某些形式规范或属性,使⽤数学的⽅法证明其正确性或⾮正确性。

形式验证是⼀个系统性的过程,将使⽤数学推理来验证设计意图(指标)在实现(RTL)中是否得以贯彻。

形式验证可以克服所有3种仿真挑战,由于形式验证能够从算法上穷尽检查所有随时间可能变化的输进值。

形式验证形式验证的出现 由于仿真对于超⼤规模设计来说太耗费时间,形式验证就出现了。

当确认设计的功能仿真是正确的以后,设计实现的每⼀个步骤的结果都可以与上个步骤的结果做形式⽐较,也就是等价检查,如果⼀致就说明设计合理,不必进⾏仿真了。

形式验证主要是进⾏逻辑形式和功能的⼀致性⽐较,是靠⼯具⾃⼰来完成,⽆需开发测试向量。

⽽且由于实现的每个步骤之间逻辑结构变化都不是很⼤,所有逻辑的形式⽐较会⾮常快。

这⽐仿真的时间要少很多。

⼀般要做形式验证的步骤有:RTL和RTL。

形式验证

在目前複雜的數位設計開發過程中,功能驗證十分重要。

雖然硬體的複雜度仍遵循摩爾定律持續成長,但是驗證的複雜性更具挑戰。

事實上,隨著硬體複雜性隨時間呈雙指數成長,驗證複雜性理論上也呈指數成長。

驗證已被公認為是設計過程中的主要瓶頸:高達70%的設計開發時間和資源花在功能驗證上。

Collett International Research認為,即使在驗證上花費如此巨大的精力和資源,功能性缺陷仍是晶片重新投片的頭號原因。

功能性驗證挑戰功能性驗證挑戰邊際情形(corner-case)的缺陷是模擬偽像,由於以模擬為基礎的驗證具有非窮盡的固有特性,因此邊際情形無法被檢測到。

事實上,不管你用多少時間模擬,也不管你的測試平台和產生器有多麼智慧,透過模擬驗證設計意圖對於最小電路以外的所有電路來說都是不完整的。

基本的模擬偽像可以被分成三類:窮盡型、可控型和可觀察型,如表1所示。

表1:模擬與形式驗證的比較。

形式驗證是一個系統性的過程,將使用數學推理來驗證設計意圖(指標)在實現(RTL)中是否得以貫徹。

形式驗證可以克服所有3種模擬挑戰(表1),因為形式驗證能夠從演算法上窮盡檢查所有隨時間可能變化的輸入值。

換句話說,沒有必要顯示如何激勵設計或製作多種條件來實現較高的可觀察性。

雖然從理論上講,模擬測試平台的輸入埠針對待驗證設計(DUV)具有較高的可控性,但測試平台對內部點的可控性一般較差。

為了使用基於模擬的方法識別設計錯誤,以下條件必須保持:* 必須產生正確的輸入激勵,以啟動(也就是感應化)設計中某個點的缺陷* 必須產生正確的輸入激勵,以便將源自缺陷的所有效果傳送到輸出埠在使用基於模擬的驗證時,需要規劃設計中需要驗證的對象:* 定義需要測試的各種輸入條件* 製作功能性覆蓋模型(確定是否做了足夠的模擬)* 搭建測試平台(檢查器,測試樁,產生器等)* 製作特定的直接測試* 成年累月的模擬現實中,工程師一直在反覆做著這些事:執行測試、除錯故障、再次模擬回歸組、觀察各種覆蓋率指標,以及調整激勵(例如操控輸入產生器)以覆蓋以前未覆蓋的設計部份。

Formily讲解_2

设置Implementation Design

• 点击Implement按钮,在Read Design Files 中点击Veril og,出现Add verilog files对话框,

• 选择netlist_w_svf目录下的verlog网表文件mR4000.gat es.v

• 选择Set Top Design,在Choose a library中选择WORK ( Design Library)

• 在Choose a design中选择顶层模块名mR4000 • 点击Set Top按钮。此时在Implementation出现绿色的

对号符。

Match

• 检查reference design 和 Implemention des

4

5 6 7

内容

形式化验证简介

形式化验证的优点

Formality同其他的工具的区别 Formality使用范围 重要概念 Formality工作流程 Formality操作方法

形式化验证简介

形式化验证方法不需要仿真向量,通过数学方法比较实现 与参考是否等价。

Reference Design

module top (…); always @ (posedge clk) . . . endmodule

• 一般调试是从cell数目最小的compare point开始 。在这里我们从第一个compare point开始。

• 选择错误点, 击鼠标右键,选择菜单中的view Lo gic Cones,出现Logic Cones View窗口。

• 在这个新窗口里显示的是reference design 和Imeplemention design的原理图,

synopsys_formality指导手册_概述说明

synopsys formality指导手册概述说明1. 引言1.1 概述在硬件设计领域,验证是一个非常重要的环节。

在设计过程中,我们需要确保设计的正确性和可靠性。

为了实现这个目标,Formality工具被广泛应用于电子设计自动化(EDA)过程中的形式验证。

Synopsys Formality是一款强大的形式验证工具,它可以帮助我们验证两个不同层次或版本的设计之间的等效性。

通过使用Formality,我们可以有效地检查逻辑门级网表和原始RTL之间是否存在功能差异或者错误。

本指导手册将介绍Formality工具的基本概念、应用场景以及使用步骤。

你将了解到如何利用Formality进行验证,并掌握其使用方法和技巧。

1.2 文章结构本文将分为以下几个部分:- 引言:对Formality进行概述并介绍文章结构。

- 正文:详细介绍Formality工具及其相关内容。

- Formality基本概念:解释Formality中涉及到的关键概念和术语。

- Formality的应用场景:探讨使用Formality解决哪些问题以及在哪些情况下选择使用该工具。

- 使用Formality进行验证的步骤:分步骤介绍如何使用Formality进行验证。

- 结论:总结本文的主要内容,并指出Formality在硬件验证中的重要性和前景。

1.3 目的本指导手册的目的是为读者提供对于Formality工具的全面理解。

通过阅读本文,读者将能够了解Formality在形式验证中的基本概念、功能和应用场景,从而能够更好地应用该工具来提高硬件设计的准确性和可靠性。

2. 正文Formality是Synopsys公司开发的一款形式验证工具,它旨在为硬件设计工程师提供一种高效且可靠的形式验证解决方案。

Formality通过比较两个逻辑设计的等效性来进行验证,确保电路实现与规范之间不存在功能差异或逻辑错误。

Formality作为一种形式验证工具,在电路设计领域中有着广泛的应用。

形式化验证方法浅析

形式化验证方法浅析随着信息技术的不断发展,软件系统已经成为现代社会和经济的基础设施之一。

软件系统的正确性和可靠性越来越受到重视,因为软件错误会带来巨大的经济损失和安全隐患。

为了提高软件系统的质量和可靠性,形式化验证方法逐渐成为了重要的研究领域。

本文将对形式化验证方法进行一定的浅析,介绍其基本概念、原理和应用。

一、形式化验证方法的基本概念形式化验证是一种基于数学逻辑的方法,通过数学语言描述待验证系统的行为规范或性质,然后利用自动化或手工化的技术对系统进行验证。

形式化验证方法主要包括模型检测、定理证明和符号执行等技术,其中模型检测和定理证明是相对常见和成熟的技术。

模型检测是一种自动化验证技术,它通过穷举系统的所有可能状态来检测系统是否满足给定的性质。

模型检测的核心就是构建系统的状态转移模型,然后利用状态空间搜索算法进行验证。

常用的状态空间搜索算法包括符号模型检测、显式状态搜索和隐式状态搜索等。

模型检测方法的优点是自动化程度高,能够发现系统中的错误和性质违反情况,但是其缺点是状态空间爆炸问题,对于大规模的系统往往难以处理。

定理证明是一种手工化验证技术,它通过数学推理和演绎来证明系统是否满足给定的性质。

定理证明的核心是将系统的行为规范或性质转化为逻辑公式,然后利用数学推理规则和定理证明工具来验证系统。

定理证明方法的优点是能够处理复杂的性质和系统,但是其缺点是依赖于人工的推理和分析,效率较低并且受到形式化规约的限制。

1. 系统建模:形式化验证的第一步是对系统进行建模,将系统的行为规范或性质形式化描述。

系统建模可以采用多种形式化语言和工具,如时序逻辑、Petri网、状态机和模型检测工具等。

建模的目的是将系统的行为抽象化和形式化,为后续的验证工作奠定基础。

2. 性质描述:形式化验证的第二步是对系统的性质进行描述,通常包括功能性要求和安全性要求。

功能性要求是描述系统的期望行为,如正确性、完备性和一致性等;安全性要求是描述系统的禁止行为,如死锁、饥饿和冲突等。

验证型实验报告格式

一、实验目的通过本次实验,验证某一理论或假设的正确性,并分析实验结果与理论或假设的符合程度。

二、实验原理简要介绍实验所依据的理论或假设,阐述实验的基本原理。

三、实验仪器与材料1. 实验仪器:- 仪器名称1:型号及规格- 仪器名称2:型号及规格- 仪器名称3:型号及规格(根据实际实验仪器填写)2. 实验材料:- 材料名称1:规格及数量- 材料名称2:规格及数量- 材料名称3:规格及数量(根据实际实验材料填写)四、实验步骤1. 准备实验仪器和材料;2. 按照实验原理,设置实验参数;3. 按照实验步骤进行操作;4. 记录实验数据;5. 对实验数据进行分析。

五、实验数据记录与分析1. 实验数据记录:| 序号 | 实验参数 | 实验结果 || ---- | -------- | -------- || 1 | 参数1 | 结果1 || 2 | 参数2 | 结果2 || 3 | 参数3 | 结果3 || ... | ... | ... |2. 实验数据分析:(1)分析实验数据与理论或假设的符合程度;(2)分析实验过程中可能存在的误差及原因;(3)总结实验结果,得出结论。

六、实验结论根据实验结果,验证理论或假设的正确性,并总结实验过程中的经验和教训。

七、实验讨论1. 分析实验结果与理论或假设的差异,探讨可能的原因;2. 对实验过程中的不足之处进行反思,提出改进措施;3. 结合实验结果,对相关理论或假设进行进一步研究。

八、实验总结1. 实验目的:验证某一理论或假设的正确性;2. 实验原理:简要介绍实验所依据的理论或假设;3. 实验仪器与材料:列举实验所需的仪器和材料;4. 实验步骤:详细描述实验操作过程;5. 实验数据记录与分析:记录实验数据,分析实验结果;6. 实验结论:验证理论或假设的正确性;7. 实验讨论:分析实验结果与理论或假设的差异,提出改进措施;8. 实验总结:总结实验过程中的经验和教训。

(注:以上为验证型实验报告格式,实际字数根据实验内容进行调整。

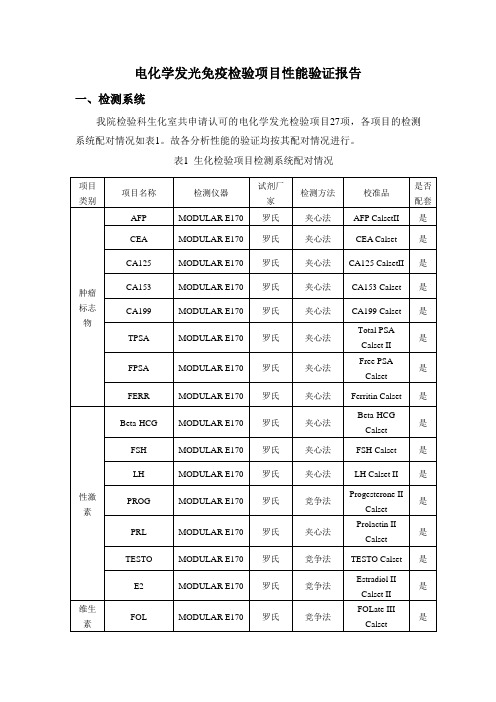

罗氏性能验证报告模板

电化学发光免疫检验项目性能验证报告一、检测系统我院检验科生化室共申请认可的电化学发光检验项目27项,各项目的检测系统配对情况如表1。

故各分析性能的验证均按其配对情况进行。

表1 生化检验项目检测系统配对情况二、范围:2.1 精密度(包括批内及日间精密度)。

2.2 准确度2.3线性范围验证:2.4 稀释度(可报告范围)2.5 生物参考区间的验证三方法1、精密度评估1.1 批内精密度;仪器:瑞士ROCHE公司MODULAR E170全自动电化学发光免疫分析仪材料:ROCHE正常肿瘤质控(批号),ROCHE病理肿瘤质控(批号);ROCHE 正常通用质控(批号),ROCHE病理通用质控(批号);ROCHE正常杂项质控(批号),ROCHE病理杂项质控(批号)。

评估步骤:在确定ROCHE MODULAR E170性能正常的情况下,重复测定20次上述各质控品,计算出各项目的均值、标准差和变异系数。

变异系数即代表精密度。

统计方法:用EXCEL来分析计算均数、标准差和变异系数。

评价方法:根据CLIA'88要求,批内精密度应≤1/4TEa,总精密度应≤1/3TEa,若CLIA'88中未做出规定,则依据中国卫生部临床检验中心室间质评要求执行或验证试剂说明书声明的精密度数据。

结论:1. 2 批间精密度;仪器:瑞士ROCHE公司MODULAR E170全自动电化学发光免疫分析仪材料:ROCHE正常肿瘤质控(批号),ROCHE病理肿瘤质控(批号);ROCHE 正常通用质控(批号),ROCHE病理通用质控(批号);ROCHE正常杂项质控(批号),ROCHE病理杂项质控(批号)。

评估步骤:在确定ROCHE MODULAR E170性能正常的情况下,在5个工作日,测定2批,每次测定2次上述质控,计算出均值,标准差和变异系数。

变异系数即代表精密度。

统计方法:用EXCEL来分析计算均数、标准差和变异系数。

评价方法:根据CLIA'88要求,批内精密度应≤1/4TEa,总精密度应≤1/3TEa,若CLIA'88中未做出规定,则依据中国卫生部临床检验中心室间质评要求执行或验证试剂说明书声明的精密度数据。

静态时序分析(PrimeTime)&形式验证(Formality)详解

摘要:本文介绍了数字集成电路设计中静态时序分析(Static Timing Analysis)和形式验证(Formal Verification)的一般方法和流程。

这两项技术提高了时序分析和验证的速度,在一定程度上缩短了数字电路设计的周期。

本文使用Synopsys 公司的PrimeTime进行静态时序分析,用Formality进行形式验证。

由于它们都是基于Tcl(Tool Command Language)的工具,本文对Tcl也作了简单的介绍。

关键词:静态时序分析形式验证 PrimeTime Formality Tcl目录第一章绪论 (1)1.1 静态时序分析1.2 时序验证技术第二章PrimeTime简介 (3)2.1 PrimeTime的特点和功能2.2 PrimeTime进行时序分析的流程2.3 静态时序分析中所使用的例子2.4 PrimeTime的用户界面第三章Tcl与pt_shell的使用 (6)3.1 Tcl中的变量3.2 命令的嵌套3.3 文本的引用3.4 PrimeTime中的对象3.4.1 对象的概念3.4.2 在PrimeTime中使用对象3.4.3 针对collection的操作3.5 属性3.6 查看命令第四章静态时序分析前的准备工作 (12)4.1 编译时序模型4.1.1 编译Stamp Model4.1.2 编译快速时序模型4.2 设置查找路径和链接路径4.3 读入设计文件4.4 链接4.5 设置操作条件和线上负载4.6 设置基本的时序约束4.6.1 对有关时钟的参数进行设置4.6.2 设置时钟-门校验4.6.3 查看对该设计所作的设置4.7 检查所设置的约束以及该设计的结构第五章静态时序分析 (18)5.1 设置端口延迟并检验时序5.2 保存以上的设置5.3 基本分析5.4 生成path timing report5.5 设置时序中的例外5.6 再次进行分析第六章 Formality简介 (22)6.1 Formality的基本特点6.2 Formality在数字设计过程中的应用6.3 Formality的功能6.4 验证流程第七章形式验证 (27)7.1 fm_shell命令7.2 一些基本概念7.2.1 Reference Design和Implementation Design7.2.2 container7.3 读入共享技术库7.4 设置Reference Design7.5 设置Implementation Design7.6 保存及恢复所作的设置7.7 验证第八章对验证失败的设计进行Debug (32)8.1 查看不匹配点的详细信息8.2 诊断程序8.3 逻辑锥8.3.1 逻辑锥的概念8.3.2 查看不匹配点的逻辑锥8.3.3 使用逻辑锥来Debug8.3.4 通过逻辑值来分析第一章 绪论我们知道,集成电路已经进入到了VLSI和ULSI的时代,电路的规模迅速上升到了几十万门以至几百万门。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验七形式化验证工具Formality

班级:XX 姓名:XX 学号:XX

1 实验目标

了解Formality工具的工作流程;

了解Formality工具的调试流程;

熟悉使用脚本进行调试,并通过图形化界面进行调试形式化验证中的不匹配点;

2 实验任务

在GUI环境下,对方使用Formality进行形式化验证的环境;

在命令行运行模式下,根据实验指导书及示例工程完成对一个简单电路的形式化验证;

3 实验环境

安装远程访问工具Xmanager/Xwin-pro的PC机:1台/生;

Linux服务器

4 实验内容

4.1 Formality工具GUI使用

按照实验指导书中的步骤,以图形方式完成对测试用例的形式化环境建立,包括参考、被测设计,库文件导入等内容。

4.2 测试用例的Formality流程

(分析第一个TCL命令的作用,并结出对应结果)

5.思考问题

(说明在进行Formality的Debug过程中的问题及解决方法)。