22.优先编码器VHDL程序设计

22.优先编码器VHDL程序设计

课名:教 师:

班级:编写时间:

课题:

优先学目的及要求:

1.掌握用VHDL设计实现优先编码器

2.掌握VHDL优先级别的设置语法

教学重点:优先编码器VHDL程序的实现

教学难点:优先级高低的实现

教学步骤及内容 :

一.复习旧课

二.新课

1.以8-3优先编码器为例,介绍优先编码的原理及VHDL实现。

ys<='1';

yex<='1';

else

ifi(7)='0' then

y<="000";

ys<='1';

yex<='0';

elsifi(6)='0' then

y<="001";

ys<='1';

yex<='0';

elsifi(6)='0' then

y<="001";

ys<='1';

yex<='0';

elsifi(5)='0' then

y<="010";

ys<='1';

yex<='0';

elsifi(4)='0' then

y<="011";

ys<='1';

yex<='0';

elsifi(3)='0' then

多路选择器与编码器的VHDL设计

实验三多路选择器与编码器的VHDL设计一. 实验目的1.掌握硬件描述语言描述多路选择器的方法。

2. 掌握硬件描述语言描述编码器的方法3.学会使用VHDL进行简单的逻辑电路设计。

4. 掌握用Quartus II进行文本输入法进行电路设计、编译和仿真方法。

二、实验仪器设备1.PC机一台2.QuartusⅡ开发软件一套3.EDA技术实验开发系统一套三. 实验任务1. 设计一个4选1多路选择器用VHDL设计的4选1多路选择器中,当控制端S=0时多路选择器有效,S=1时禁止工作,输出封锁为低电平。

d0,d1,d2,d3分别为四个数据输入端的端口名,a0,a1为通道选择控制信号输入端的端口名,y为输出端的端口名。

(1)4选1多路选择器的VHDL程序entity mux4_1 isport(d0,d1,d2,d3: in bit;a0,a1,s: in bit;y: out bit);end;architecture one of mux4_1 issignal a: bit_vector(1 downto 0);Beginprocess(a0,a1)begina<=a1&a0;if (s='0') thencase a iswhen "00"=> y <=d0;when "01"=> y <=d1;when "10"=> y <=d2;when "11"=> y <=d3;end case;else y<='0';end if;end process;end;(2)根据编写的VHDL程序并在Quartus II软件中进行输入、编译和仿真。

其功能仿真波形如下图所示,通过波形分析符合4选1多路选择器的要求。

图1VHDL程序录入图2程序仿真波形图。

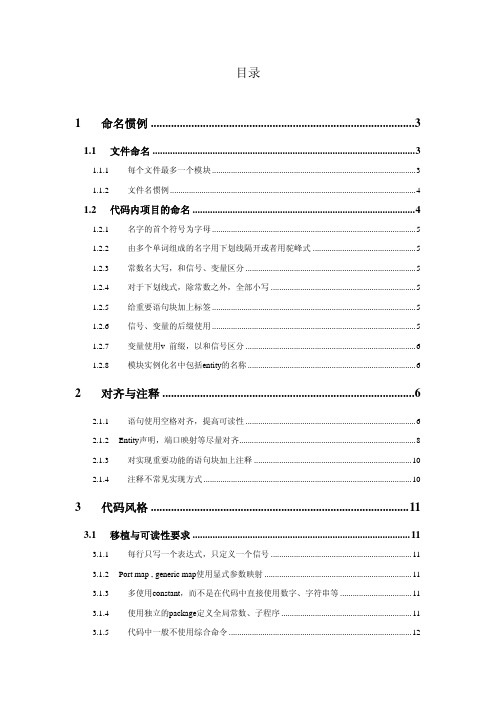

VHDL代码设计规范

文件会签页文件标题VHDL 编码规范(试用版)文件编号授权分发清单签名签名编制审核部门部门加盖受控章签名签名审核审核部门部门签名签名审核审核部门部门签名签名审核审核部门部门签名签名审核审核部门部门签名签名审核审核部门部门签名签名审核审核部门部门审批签名批准签名生效日期:文件历史记录文件编号现行版本V1.0 文件标题VHDL代码设计规范文件履历版次编制日期更改内容(条款)VHDL代码设计规范(评审稿)文件编号:编制:审核:VHDL代码设计规范(定稿)文件编号:编制:审核:可靠性审核:标准化:批准:目录1. 目的 (1)2. 范围 (1)3. 术语说明 (1)4. 规范列表 (1)5. 规范 (3)5.1. 书写规范 (3)5.1.1. 命名规范. (3)5.1.2. 注释规范. (5)5.1.3. 其他书写规范. (6)5.2. 设计规范 (6)5.2.1. 复位. (6)5.2.2. 时钟. (7)5.2.3. 状态机. (7)5.2.4. 异步信号. (7)5.2.5. 其他设计规范. (8)5.3. 设计常识 (9)6. 附录 (9)6.1. 例子说明(规范详细解释) (9)6.2. 代码模板 (18)1. 目的规范VHDL的设计风格,保证代码的可读性、重用性及与现有EDA工具的一致性,从而形成对设计代码的标准化管理。

2. 范围本标准规定了VHDL代码设计规范。

本标准适用于COMBA公司技术中心。

3. 术语说明本规范使用的术语解释如下:级别:指该规则遵循的级别,有两个级别,分别为推荐和规定。

推荐:表示在一般情况下必须遵循该规则。

规定:表示必须严格遵守该规则。

说明:对此规则或准则的必要的解释。

示例:对此规则举例进行说明,示例分为正例和反例。

正例:对此规则或准则给出的正确示例。

反例:对此规则或准则给出的反面示例。

4. 规范列表编号级别规则书写规范R1. 规定一个文件只包含一个模块,文件命名、模块命名、实体命名必须相同。

编码器的VHDL设计

END coder83_2;

பைடு நூலகம்

ARCHITECTURE behave OF coder83_2 IS BEGIN Q2 <= D4 OR D5 OR D6 OR D7; Q2=D4+D5+D6+D7 Q1 <= D2 OR D3 OR D6 OR D7; Q1=D2+D3+D6+D7 Q0=D1+D3+D5+D7 Q0 <= D1 OR D3 OR D5 OR D7; END behave;

(3)条件选择值必须覆盖“表达式”的所有取值。 )条件选择值必须覆盖“表达式”的所有取值。 因此, 因此,在END CASE前的最后一条语句总是 前的最后一条语句总是 顺序语句” “WHEN OTHERS=>顺序语句”。 顺序语句 引导的条件选择值不能重叠。 (4)不同的“WHEN”引导的条件选择值不能重叠。 )不同的“ 引导的条件选择值不能重叠 5)CASE语句是顺序语句 必须在进程中使用。 语句是顺序语句, (5)CASE语句是顺序语句,必须在进程中使用。

二case语句case语句也是分支语句的一种case语句不同于if语句它是根据所满足的条件直接执行多项顺序语句中的一项没有优先级

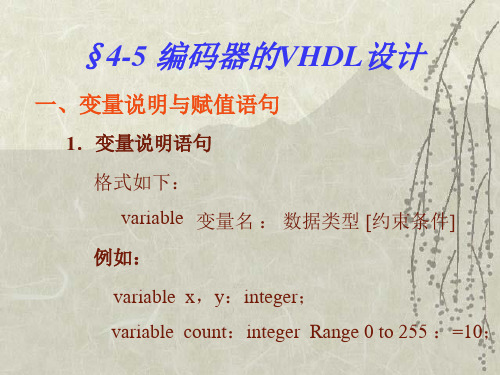

§4-5 编码器的VHDL设计

一、变量说明与赋值语句

1.变量说明语句 . 格式如下: variable 变量名 : 数据类型 [约束条件] 例如: 例如: variable x,y:integer; variable count:integer Range 0 to 255 :=10;

VHDL代码规范

3

3.1

代码风格 .........................................................................................11

移植与可读性要求 ....................................................................................... 11

3.1.1 3.1.2 3.1.3 3.1.4 3.1.5

3.1.6 3.1.7 3.1.8 3.1.9

常数之间有确定的关系时,使用关系定义 ...............................................................12 定义地址时,使用基址+偏移方式 .............................................................................13 常数可能变动的情况下使用generic map方式传递,而不是在模块中定义 ...............13 表达式使用括号表示优先级 .......................................................................................13

3.2

3.2.1 3.2.2 3.2.3 3.2.4 3.2.5 3.2.6 3.2.7 3.2.8 3.2.9

语句使用 .......................................................................................................13

基于vhdl卷积码编解码器的设计说明书

长沙理工大学《通信电路EDA》课程项目报告系别水利计通系专业通信工程班级通信1003班指导教师项目组组长学号项目组成员学号项目组成员学号项目组成员学号完成日期2012年11月14日目录1 引言 (3)1.1项目背景 (3)2 卷积码编解码器的结构概述 (4)2.1 卷积码编码器的结构 (4)2.2 卷积译码器的结构 (4)3 卷积码编解码器的VHDL 设计 (5)3.1 VHDL 设计的优点与设计方法 (5)3.2 卷积码编码器的VHDL 实现 (5)3.2.1 卷积编码器顶层建模的VHDL 描述 (5)3.2.2 用MAX+PLUSⅡ编译后生成的编码器图形符号 (7)3.2.3 卷积编码器VHDL仿真波形 (7)3.3 卷积码解码器的VHDL实现 (7)3.3.1 卷积解码器顶层建模的VHDL 描述 (7)3.3.2 用MAX+PLUSⅡ编译后生成的解码器图形符号 (9)3.3.3 卷积解码器VHDL仿真波形 (9)4 参考文献 (9)5 后记 (10)基于VHDL的卷积码编解码器的设计1 引言1.1项目背景现代数字通信有两个基本的理论基础,即信息论和纠错编码理论,它们几乎是同时在第二次世界大战结束后不久诞生的。

前者首先由Shannon以他的不朽名著“通信的数学理论”为标志建立起来的,而后者则以Hamming的经典著作“纠错和检错编码”为代表。

Shannon信息论主要讨论信息的度量,以及对于信息表示和信息传输的基本限制。

信道编码定理告诉我们,只要信息传输速率小于信道容量,则信息传输可以以任何小的错误概率进行。

但是,Shannon信息论并没有告诉我们如何去实现这一点。

Hanmming提出的纠错编码理论正是为了解决这个问题。

科学技术的发展使人类跨入了高度发展的信息化时代。

在政治、军事、经济等各个领域,信息的重要性不言而喻,有关信息理论的研究正越来越受到重视。

20世纪50年代信息论在学术界引起了巨大的反响。

vhdl编程的基本步骤

vhdl编程的基本步骤VHDL是一种硬件描述语言,可以用于描述数字系统的设计和行为。

用VHDL 编程可以帮助开发人员更好地理解数字电路的工作原理和行为,从而实现更高效和更可靠的设计。

以下是VHDL编程的基本步骤:1. 规划设计在开始VHDL编程之前,应该先确定设计的目标、所需功能和限制。

这需要考虑到系统的需求、硬件资源和性能要求。

在规划设计时,需要对整个系统进行初步的架构设计,确定输入、输出和中间信号的类型和操作。

2. 定义实体VHDL编程的第一步是定义实体(Entity)和端口(Port)。

实体是在VHDL中描述数字电路的主要部分,一般包括输入、输出和中间信号。

通过端口定义,可以定义每个信号的类型、方向和名称等信息。

在定义实体时,还需要添加注释,以帮助其他编程人员理解代码逻辑。

3. 编写结构体在定义完实体之后,可以开始编写结构体(Architecture)。

结构体描述了实体所需的内部信号和变量,以及信号之间的连接方式。

可以使用多种逻辑门和运算符来实现不同的操作。

它们可以在结构体中通过实体中定义的输入和中间信号进行操作,并将结果写入输出端口。

4. 仿真验证一旦编写好VHDL代码,就可以使用数字电路仿真工具来验证代码的正确性。

数字电路仿真工具可以使用给定的信号用数学模型来计算数字电路的输出,并通过应用测试输出和预期输出的比较来验证。

如果代码不正确,可以通过调整代码来修复错误。

5. 合成设计一旦编写好代码并对其进行验证,就可以通过数字电路合成工具将代码转换为芯片可读的硬件描述语言。

合成是将所需的硬件功能映射到芯片的布局中,以实现物理层面的元件和连接。

合成时应选择合适的芯片大小、时钟速度和其他性能参数,以满足硬件资源限制和性能要求。

6. 下载到硬件最后,开发人员将设计的硬件模块下载到实际的硬件平台上,例如FPGA或ASIC。

此时,应该进行严格的测试和验证,以确保设计符合预期的性能和功能。

如果存在问题,则可能需要通过更改VHDL代码或重新合成来修复问题,并重新验证和测试。

VHDL的编码器和译码器的设计

VHDL的编码器和译码器的设计摘要: VHDL是Very High Speed Integrated Circuit Hardware Description Language的缩写,意思是超高速集成电路硬件描述语言。

以MAX+plusII软件工具为开发环境,以可编程逻辑器件为实验载体,实现源代码编程和仿真功能。

本设计提出了一种基于VHDL语言的编码器和译码器的实现方法。

编码器与译码器是计算机电路中基本的器件,本课程设计采用VHDL设计编码和译码器。

编码器由8线-3线优先编码器作为实例代表,译码器则包含3线-8线译码器和2线-4线译码器两个实例模块组成。

课程设计采用硬件描述语言VHDL把电路按模块化方式进行设计,然后进行编程、时序仿真和分析等。

设计的系统结构简单,使用方便,具有一定的应用价值。

关键词: VHDL;MAX+plusII;编码器;译码器Encoder and decoder design based on VHDLAbstract: VHDL is the Very High Speed Integrated Circuit Hardware Description Language acronym, meaning high speed integrated circuit hardware description language.MAX+plusII software as tools for the development of the environment,programmable logic devices in experimental carrier,the realiztionof the source code programming and simulation. The paper proposes a method for encoder and decoder based on the VHDL language.Encoder and decoder is a basic computer circuit devices.This Curriculum design by VHDL design encoder and decoder.Encoders from 8 - 3 priority encoder for example,and decoder includes3 - 8 decoder and the 2 -4 examples of the two decoder modules.And then to program, the timing simulation and analysis.Curriculum design, simple system structure, easy to use and has a value.Keyword: VHDL; MAX+plusII; Encoder; Decoder基于VHDL的编码器和译码器的设计目录1 引言 (1)1.1 设计的目的 (1)1.2 设计的内容 ........................................................ 1 2 MAX+plusII及VHDL简介 .. (3)2.1 MAX+plusII 基本介绍 (3)2.1.1 MAX+plusII的概念 (3)2.1.2 使用MAX+plusII设计的特点 ................................... 3 2.2 硬件描述语言――VHDL . (3)2.2.1 VHDL的简介 (3)2.2.2 VHDL语言的特点 .............................................. 4 2.2.3 VHDL的设计流程 . (4)3 设计实现 (6)3.1编码器 (6)3.1.1 8线-3线优先编码器的工作原理 (6)3.1.2 8线-3线优先编码器的设计 ................................... 7 3.2译码器 (8)3.2.1 译码器的工作原理 (8)3.2.2 3线-8线译码器的设计 ...................................... 10 3.2.3 2线-4线译码器的设计 .. (11)4 系统仿真与时序分析 (12)4.1 8线-3线优先编码器仿真及时序分析 (12)4.2 3线-8线译码器仿真及时序分析 ................................ 13 4.3 2线-4线译码器仿真及时序分析 .. (14)5 结束语 ................................................................15 致谢 ....................................................................16 参考文献 ................................................................17 附录 ...................................................................17基于VHDL的编码器和译码器的设计第1页共20页1 引言随着社会的发展,科学技术也在不断的进步。

vhdl程序设计教学大纲

《VHDL硬件描述语言》教学大纲一、课程基本信息课程名称:VHDL硬件描述语言课程编码:31082008课程类别:学科基础选修课程适用专业:计算机科学与技术开课学期:第3学年第1学期课程学时:32课程学分:2先修课程:数字逻辑电路并修课程:算法分析课程简介:vhdl是计算机科学与技术专业选修的基础课程,主要讲述vhdl硬件描述语言的基础知识,以及用vhdl硬件描述语言设计的基本理论和方法。

数字逻辑电路课程包括vhdl程序结构和描述、vhdl 顺序语句,并行语句,数字逻辑单元的设计等内容。

二、课程教育目标通过vhdl 语言课程的学习,使学生掌握vhdl硬件描述语言的基本原理和设计方法,运用vhdl语言设计基本的数字电路设计,为以后学习计算机组成原理、计算机配置与维护等后续课程以及从事数字电子技术领域的工作打下扎实的基础。

三、课程教学内容、要求及学时安排第一章 EDA技术概述和 vhdl语言【教学内容】1. EDA技术概述2. vhdl 语言概述【教学要求】1.了解EDA技术和vhdl语言。

【教学方法】理论联系实际,课堂讲授,课后作业等。

【学时】1第二章 vhdl语言基础【教学内容】1. vhdl程序结构2. vhdl 语言描述3. vhdl语言的数据类型4. vhdl 语言的顺序描述语句5. vhdl 语言的并发描述语句【教学要求】1.掌握vhdl语言的顺序描述语句,并发描述语句。

2.熟悉vhdl语言的结构。

3.了解vhdl语言的数据类型。

【教学方法】理论联系实际,课堂讲授,课后作业等。

【学时】9第三章数字逻辑单元设计【教学内容】1.组合逻辑电路设计2.数据运算单元设计3. 时序逻辑电路设计【教学要求】1.掌握组合逻辑电路设计和时序逻辑电路设计。

2.熟悉数据运算单元设计。

3.了解总线缓冲单元设计。

【教学方法】理论联系实际,课堂讲授,课后作业等。

【学时】10四、考核及成绩评定(一)命题原则与思想综合考核所学知识、各章节的知识点、要求掌握的基本知识和基本原理,试题难易适中,学习成绩具有一定的区分度。

实验2-优先编码器

实验3:优先编码器的Verilog HDL描述及仿真一、实验目的及要求:1.掌握优先编码器的Verilog HDL描述方法2.理解逻辑综合的概念3.掌握RTL电路原理图分析的分析方法二、实验工具:Quartus_II 9.0三、实验原理:1. 优先编码器简介在数字系统中,常常需要将某一信息变换为某一特定的代码,把二进制代码按一定的规律编排,时每组代码具有一定的含义称为编码。

具有编码功能的逻辑电路称之为编码器。

常常会有几个部件同时发出服务请求的可能,而在同一时刻只能给其中一个部件发出允许操作信号。

因此,必须根据轻重缓急,规定好这些控制对象允许操作的先后次序,即优先级别。

8-3优先编码器有8个输入端,3个输出端。

还有一个输入使能,输出使能和优先编码器工作状态标志。

编码器以低为有效。

输入优先级别的次序为7,6,5,…,0。

当某一输入端有低电平输入,且比它优先级高的输入没有低电平输入时,输出端才输出相应输入端的代码。

优先编码器的真值表如下表1所示。

表1.2.Verilog程序设计与逻辑综合2.1 8-3线编码器示例always @ (din)begincase(din)8’b0000_0001: dout = 3’b000;8’b0000_0010: dout = 3’b001;8’b0000_0100: dout = 3’b010;8’b0000_1000: dout = 3’b011;…8’b1000_0000: dout = 3’b111;default : dout = 3’bx;endcaseend2.2 优先编码器设计优先编码器与上面描述的普通8-3线编码器不同,每次只需判断优先级高的输入端是否有效always @ (din)begincasex(din)8’b1xxx_xxxx: dout = 3’b111;8’b01xx_xxxx: dout = 3’b110;8’b001x_xxxx: dout = 3’b101;8’b0001_xxxx: dout = 3’b100;…8’b0000_0001: dout = 3’b000;default : dout = 3’bx;endcaseend2.3.逻辑综合逻辑综合是在标准单元库和特定的设计约束的基础上,把设计的高层次描述转换成优化的门级网表的过程。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

6.引脚指定:

指定输入输出对应的芯片的引脚,注意一些引脚不能用。选择菜单命令Assign | Pin/Location/Chip,将设计的优先编码器与目标芯片(EPM7128SLC84-10)联系起来。

7.程序下载:

Max+PlusII-progeammer-JTAG-Multi-DeviceJTAG chain setup-Select Programming file–找到.pof文件-add-OK

yex<='1';

end if;

end if;

end process;

endrtl;

4.项目编译:

选择目标器件。选择菜单命令Assign | Device,弹出Device对话框。选择对话框的Device Family下拉列表框中的目标器件(EPM7128SLC84-10)引脚指定,编译。

5.项目时序仿真:

重庆科创职业学院授课方案(教案)

课名:教 师:

班级:编写时间:

课题:

优先编码器VHDL程序设计

授课时数

2

教学目的及要求:

1.掌握用VHDL设计实现优先编码器

2.掌握VHDL优先级别的设置语法

教学重点:优先编码器VHDL程序的实现

教学难点:优先级高低的实现

教学步骤及内容 :

一.复习旧课

二.新课

1.以8-3优先编码器为例,介绍优先编码的原理及VHDL实现。

ys<='1';

yex<='1';

else

ifi(7)='0' then

y<="000";

ys<='1';

yex<='0';

elsifi(6)='0&ys<='1';

yex<='0';

elsifi(6)='0' then

y<="001";

ys<='1';

yex<='0';

2.VHDL基本知识讲解

If…else 语句的讲解。

3.设计过程:

(1)输入设计项目并将其设为当前项目;

(2)在文本编辑窗中设计输入8-3优先编码器的VHDL代码:

Libraryieee;

use ieee.std_logic_1164.all;

entity yxbm8_3 is

port(i:instd_logic_vector(7downto0);

s:instd_logic;

y:outstd_logic_vector(2 downto0);

ys,yex:outstd_logic);

end yxbm8_3;

architecturertlof yxbm8_3 is

begin

process(i,s)

旁批栏:

begin

if s='1' then

y<="111";

8.实验箱上现象的分析描述与验证。

三.小结

对学生在实验过程中遇到的问题进行分析,总结,做出合理的评价。

四.作业

将程序输入到MAX+PLUS II软件进行相关操作,完成实验报告。

旁批栏:

elsifi(5)='0' then

y<="010";

ys<='1';

yex<='0';

elsifi(4)='0' then

y<="011";

ys<='1';

yex<='0';

elsifi(3)='0' then

y<="100";

ys<='1';

yex<='0';

elsifi(2)='0' then

y<="101";

ys<='1';

yex<='0';

elsifi(1)='0' then

旁批栏:

y<="110";

ys<='1';

yex<='0';

elsifi(0)='0' then

y<="111";

ys<='1';

yex<='0';

elsifi="11111111" then

y<="111";

ys<='0';