10分钟教你学会Makefile

makefile中使用cp命令

makefile中使用cp命令介绍在编写软件项目时,为了方便管理和构建代码,我们通常会使用makefile来自动化构建过程。

makefile是一种用于描述代码构建规则的文件,其中可以包含各种命令和指令。

其中,cp命令是makefile中常用的一个命令,用于复制文件或目录。

cp命令的基本用法cp命令的基本语法如下:cp [选项] 源文件目标文件其中,选项可以用来指定一些复制的行为,例如是否覆盖目标文件、是否保留源文件的属性等。

源文件是要复制的文件或目录,目标文件是复制后的文件或目录的名称。

cp命令的常见选项cp命令有许多选项可以用来控制复制的行为,下面是一些常见的选项: - -r:递归地复制目录及其内容。

- -f:强制复制,即使目标文件已经存在也进行复制。

- -i:交互式复制,如果目标文件已经存在,会询问是否覆盖。

- -p:保留源文件的属性,包括权限、时间戳等。

- -u:只复制更新的文件,即只复制源文件比目标文件新的文件。

- -v:显示详细的复制过程。

使用cp命令复制文件在makefile中使用cp命令复制文件可以方便地将源文件复制到目标文件中。

下面是一个简单的示例:all:cp source_file.txt target_file.txt上述示例中,我们使用了makefile的规则,其中all是规则的目标,cpsource_file.txt target_file.txt是规则的命令。

当我们运行make命令时,makefile会根据规则执行相应的命令,从而完成文件的复制。

使用cp命令复制目录除了复制文件,cp命令还可以复制目录及其内容。

在makefile中,我们可以使用cp命令的-r选项来递归地复制目录。

下面是一个示例:all:cp -r source_directory target_directory上述示例中,我们使用了-r选项来递归地复制source_directory目录及其内容到target_directory目录中。

makefile all用法

makefile all用法Makefile是一种类似于脚本的文件,可以用来自动化构建、编译和整合代码。

Makefile中常常会用到all指令,可以一次性执行多个任务。

本篇文章将详细说明Makefile中all指令的用法。

一、all指令的用途在Makefile中使用all指令的语法非常简单,只需要在文件中添加如下代码即可:all:<command1><command2><command3>...<command_n>其中,<command>表示需要执行的命令,可以是编译、构建、安装等一系列操作。

在语法中,all指令后面紧跟着“:”,表示all指令执行的是“伪目标”,而不是一个真正的文件。

也就是说,all指令并不会生成任何东西,它只是用来方便执行多个任务的一个指令。

1. all指令必须放在Makefile文件的开头。

这是因为,Makefile文件中的第一个目标就是Makefile默认的目标,也就是all指令。

2. all指令的语句必须以制表符(Tab)开头,否则会出现错误。

这是因为Makefile中使用了缩进,而不是空格,来标识命令与目标之间的关系。

因此,必须使用制表符来开头。

3. 如果在执行all指令的时候,其中的某个命令失败了,则后续的命令将不再执行。

这是因为Makefile中使用的是顺序执行的方式,即一个任务执行完成后才会进行下一个任务的执行。

下面是一个简单的Makefile文件,其中包含了几个常用的构建命令:说明:4. 使用make命令时,可以通过传递参数来指定执行的目标。

比如make clean,就只会执行clean目标下的所有命令。

总结:Makefile中使用all指令能够一次性执行多个命令,方便快捷。

在Makefile文件中添加all指令时,需要注意语法和文件位置等问题,避免出现错误。

在实际开发过程中,建议在Makefile文件中添加clean等指令,用于清理生成的目标文件和可执行文件。

makefile编写规则

makefile编写规则⼀、makefile 规则:⼀般开头都是 Tab ,不能空格, include 前⾯不能是 Tab; 1、如果没编译过,将所有的(.c)⽂件编译并且链接; 2、如果有其中的(.c)⽂件改变,编译并链接改变的⽂件; 3、如果(.h)⽂件被修改,编译引⽤相应的(.c)⽂件, 链接; 4、在随意修改时间的情况下,会导致编译过程中⽣成的(.o 中间⽂件)与可执⾏⽂件时间不⼀致,此时会编译相应的⽂件,并链接,最终编译成可执⾏⽂件;⼆、第⼀版 makefile: 例如有2个 .h ⽂件(utils.h, player.h, actor.h)和 3个 .c ⽂件( main.c, player.c, actor.c)需要编译链接:/*****main.c*********/#include "utils.h"#include "player.h"void main() {// do something}/*******player.c**********/#include "utils.h"#include "actor.h"bool create_player() {// do something}/****actor.c************/#include "utils.h"bool create_actor() {// do something}/********* makefile *****************/test : main.o actor.occ -o test main.o actor.omain.o : main.c utils.h player.h actor.hcc -c main.cpalyer.o: player.c player.h actor.h utils.hcc -c player.cactor.o: actor.h utils.hcc -c actor.cclean:rm test ain.o player.o actor.o 优点:可毒性很强,思路清晰明了; 缺点:⿇烦,重复的依赖过多,当需要编译⼤量⽂件时容易出错;第⼆版:利⽤ makefile 的变量;/********* makefile *****************/OBJ = main.o actor.o // 跟第⼀版⽐较,唯⼀的区别在这test : $(OBJ) // 这⼉cc -o test $(OBJ) // 这⼉main.o : main.c utils.h player.h actor.hcc -c main.cpalyer.o: player.c player.h actor.h utils.hcc -c player.cactor.o: actor.h utils.hcc -c actor.c .PHONY : clean // 伪⽬标,避免:如果当前⽬录下存在 clean rm 指令不执⾏clean:-rm test $(OBJ) // 前⾯的(-)表⽰,执⾏过程中不 care 出错;第三版:利⽤ GUN make 的⾃动推导规则 当 make 看到(.o )⽂件,他会⾃动把(.c)⽂件加上依赖关系,包括执⾏的语句(cc -c xx.c);/********* makefile *****************/OBJ = main.o actor.o // 跟第⼀版⽐较,唯⼀的区别在这test : $(OBJ) // 这⼉cc -o test $(OBJ) // 这⼉main.o : utils.h player.h actor.hpalyer.o: player.h actor.h utils.hactor.o: actor.h utils.h .PHONY : clean // 伪⽬标,避免:如果当前⽬录下存在 clean rm 指令不执⾏clean:-rm test $(OBJ)第四版:对第三版的整理(有⼀些重复的 .h) 公共的⼀起依赖,单独的单独依赖/********* makefile *****************/OBJ = main.o actor.o // 跟第⼀版⽐较,唯⼀的区别在这test : $(OBJ) // 这⼉cc -o test $(OBJ) // 这⼉$(OBJ) : utils.h actor.omain.o player.o .PHONY : clean // 伪⽬标,避免:如果当前⽬录下存在 clean rm 指令不执⾏clean:-rm test $(OBJ)优点:简洁缺点:不好理解以上的makefike⽂件的基本写法;或许你也发现了,如果有⼏百个源⽂件咋整呢,光是⽬录就要晕死,下⾯就是针对这种情况来说⼀下⼤型⼯程 makefile 的编写设计⼆、⼤型项⽬makefile编写: Makefile 同样也有像 c / c++ 类似的include功能; 例如我们有⼀堆 a.mk , b.mk以及 foo.make和⼀个变量 $(bar),其包含了 e.mk,f.mk, 那么 include foo.make *.mk $(bar) ------- 等价-------》 include foo.make a.mk b.mk e.mk f.mk。

makefile if用法

makefile if用法Makefile 是一种常用的构建工具,用于自动化构建软件项目。

在Makefile 中,if 语句能够根据条件来选择不同的命令或变量赋值。

本文将逐步介绍Makefile 中if 语句的用法,包括条件判断、变量赋值、嵌套使用等方面的内容。

首先,我们需要了解Makefile 中if 语句的基本语法。

if 语句可以写在任何位置,但通常我们将其放在文件的顶部,用于设置全局变量或选择不同的命令。

if 语句的基本结构如下:ifeq (条件,值)# 条件成立时执行的命令或变量赋值else# 条件不成立时执行的命令或变量赋值endif在这个基本结构中,ifeq 为条件判断语句,它用于判断条件是否等于某个值。

若条件成立,则执行if 代码块内的命令或进行变量赋值,否则执行else 代码块内的命令或变量赋值。

endif 表示if 语句的结束。

接下来,我们来看一些具体的示例,以帮助理解if 语句的用法。

1. 条件判断:在Makefile 中,我们可以使用各种条件进行判断。

以下是一些常用的判断方式:- 变量是否为空:ifeq ((VAR),)# VAR 为空时执行的命令或变量赋值else# VAR 不为空时执行的命令或变量赋值endif- 变量是否等于某个值:ifeq ((VAR),某个值)# VAR 等于某个值时执行的命令或变量赋值else# VAR 不等于某个值时执行的命令或变量赋值endif- 多个条件判断:ifeq ((VAR),某个值)# VAR 等于某个值时执行的命令或变量赋值else ifeq ((VAR),另一个值)# VAR 等于另一个值时执行的命令或变量赋值else# VAR 既不等于某个值,也不等于另一个值时执行的命令或变量赋值endif2. 变量赋值:在if 语句中,我们可以根据条件选择不同的变量赋值,使得程序更具有灵活性。

以下示例展示了如何根据条件选择不同的变量赋值:ifeq ((OS),Linux)# OS 等于Linux 时,执行以下变量赋值CC = gccelse# OS 不等于Linux 时,执行以下变量赋值CC = clangendif根据上述示例,当操作系统为Linux 时,CC 的值将被赋为gcc,否则为clang。

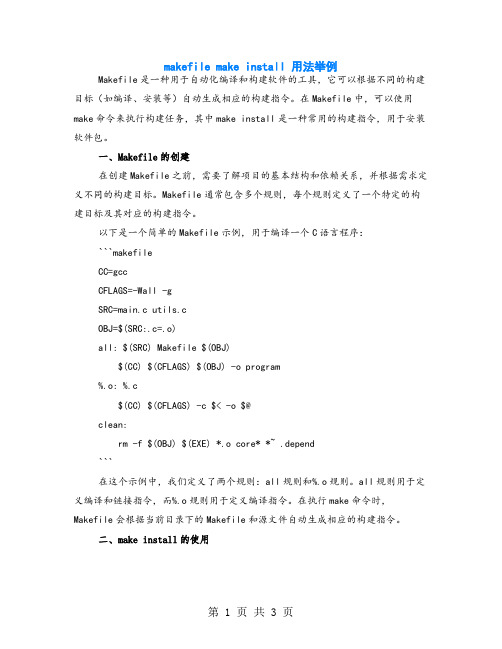

makefile make install 用法举例

makefile make install 用法举例Makefile是一种用于自动化编译和构建软件的工具,它可以根据不同的构建目标(如编译、安装等)自动生成相应的构建指令。

在Makefile中,可以使用make命令来执行构建任务,其中make install是一种常用的构建指令,用于安装软件包。

一、Makefile的创建在创建Makefile之前,需要了解项目的基本结构和依赖关系,并根据需求定义不同的构建目标。

Makefile通常包含多个规则,每个规则定义了一个特定的构建目标及其对应的构建指令。

以下是一个简单的Makefile示例,用于编译一个C语言程序:```makefileCC=gccCFLAGS=-Wall -gSRC=main.c utils.cOBJ=$(SRC:.c=.o)all: $(SRC) Makefile $(OBJ)$(CC) $(CFLAGS) $(OBJ) -o program%.o: %.c$(CC) $(CFLAGS) -c $< -o $@clean:rm -f $(OBJ) $(EXE) *.o core* *~ .depend```在这个示例中,我们定义了两个规则:all规则和%.o规则。

all规则用于定义编译和链接指令,而%.o规则用于定义编译指令。

在执行make命令时,Makefile会根据当前目录下的Makefile和源文件自动生成相应的构建指令。

二、make install的使用make install是Makefile中常用的一种构建指令,用于将软件包安装到目标系统中。

使用make install命令时,需要指定安装的目标目录和安装选项。

下面是一个简单的示例:假设我们有一个名为myapp的软件包,将其安装到/usr/local/目录下:```bashmake install prefix=/usr/local/```在这个示例中,我们使用make install命令将myapp软件包安装到/usr/local/目录下。

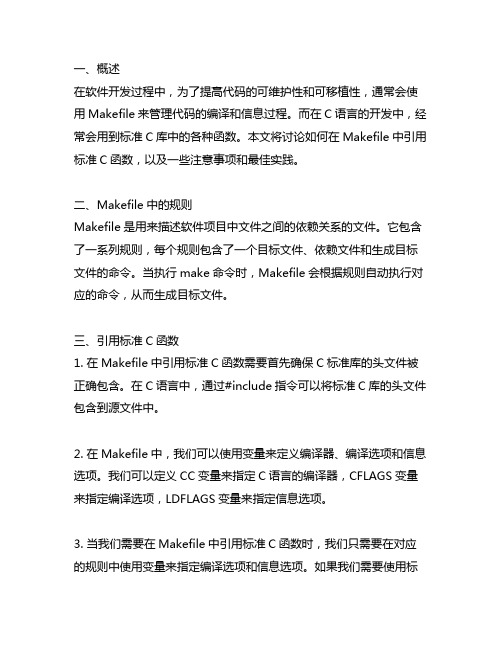

makefile引用标准c函数

一、概述在软件开发过程中,为了提高代码的可维护性和可移植性,通常会使用Makefile来管理代码的编译和信息过程。

而在C语言的开发中,经常会用到标准C库中的各种函数。

本文将讨论如何在Makefile中引用标准C函数,以及一些注意事项和最佳实践。

二、Makefile中的规则Makefile是用来描述软件项目中文件之间的依赖关系的文件。

它包含了一系列规则,每个规则包含了一个目标文件、依赖文件和生成目标文件的命令。

当执行make命令时,Makefile会根据规则自动执行对应的命令,从而生成目标文件。

三、引用标准C函数1. 在Makefile中引用标准C函数需要首先确保C标准库的头文件被正确包含。

在C语言中,通过#include指令可以将标准C库的头文件包含到源文件中。

2. 在Makefile中,我们可以使用变量来定义编译器、编译选项和信息选项。

我们可以定义CC变量来指定C语言的编译器,CFLAGS变量来指定编译选项,LDFLAGS变量来指定信息选项。

3. 当我们需要在Makefile中引用标准C函数时,我们只需要在对应的规则中使用变量来指定编译选项和信息选项。

如果我们需要使用标准C函数printf,我们只需要在对应的规则中将需要用到的标准库信息到目标文件中。

四、注意事项和最佳实践1. 在Makefile中引用标准C函数时,我们需要确保编译时能找到对应的标准C库文件。

通常情况下,标准C库文件会在系统的标准库目录下,我们需要将这些目录添加到信息选项中。

2. 在Makefile中引用标准C函数时,我们需要确保编译器能找到对应的标准C库头文件,通常情况下,标准C库头文件会在系统的标准头文件目录下,我们需要将这些目录添加到编译选项中。

3. 在Makefile中引用标准C函数时,我们需要确保编译器能正确识别和处理对应的标准C函数的参数和返回值类型。

通常情况下,标准C函数的参数和返回值类型会在对应的头文件中定义,我们需要确保这些定义被正确包含到源文件中。

make的主要用法

make的主要用法Make是一个常用的构建工具,它可以自动化地编译程序、生成文档、打包发布等操作。

Make最初是Unix系统下的一个工具,现在已经被广泛地应用于各种平台和语言中。

一、Make的基本概念1.1 MakefileMakefile是Make的配置文件,它描述了如何构建目标文件。

Make会根据Makefile中的规则来判断哪些文件需要重新编译,以及如何编译它们。

1.2 目标文件目标文件是指要生成的文件,可以是可执行程序、静态库、动态库等。

在Makefile中,每个目标都有一个对应的规则来描述如何生成它。

1.3 依赖关系依赖关系指的是目标文件与源文件之间的关系。

如果一个目标文件依赖于另外一个文件,那么在生成这个目标文件之前必须先生成它所依赖的那个文件。

1.4 规则规则描述了如何从源代码生成目标代码。

规则由三部分组成:目标、依赖和命令。

其中,目标表示要生成的文件,依赖表示该目标所依赖的其他文件,命令表示如何从依赖中生成目标。

二、Makefile语法2.1 变量定义变量可以用来存储一些常用的值,比如编译器、编译选项等。

变量的定义格式为:变量名=变量值。

2.2 目标规则目标规则描述了如何生成一个目标文件。

目标规则的格式为:目标: 依赖命令其中,目标表示要生成的文件,依赖表示该目标所依赖的其他文件,命令表示如何从依赖中生成目标。

2.3 伪目标伪目标是指不对应任何实际文件的目标,它们通常用来描述一些特殊的操作,比如清空临时文件、打包发布等。

伪目标的名称前面要加上一个“.”号。

2.4 函数Make提供了一些内置函数来方便我们编写Makefile。

常用的函数有:$(wildcard pattern)、$(patsubst pattern,replacement,text)、$(subst from,to,text)等。

三、Makefile实例下面是一个简单的Makefile示例:CC=gccCFLAGS=-Wall -gLDFLAGS=-lmall: hello_world.exehello_world.exe: hello_world.o$(CC) $(LDFLAGS) $< -o $@hello_world.o: hello_world.c$(CC) $(CFLAGS) -c $< -o $@clean:rm -f *.o *.exe这个Makefile定义了三个变量:CC表示编译器,CFLAGS表示编译选项,LDFLAGS表示链接选项。

python makefile 用法

python makefile 用法在使用Python编写程序时,我们通常需要编译和运行代码,这就需要用到makefile。

makefile是一种可以自动化地构建程序的工具,它可以根据代码修改的情况自动判断哪些文件需要重新编译,从而提高程序的编译效率。

使用makefile的基本步骤如下:1. 创建一个名为makefile的文件,通常放在程序的根目录下。

2. 在makefile中定义一些变量,如编译器、编译选项等。

3. 定义一些规则,如编译规则、目标规则等。

4. 运行make命令,根据makefile的规则进行编译和链接。

下面是一个简单的makefile示例:```# 定义编译器和编译选项CC=gccCFLAGS=-Wall -g# 定义编译规则%.o: %.c$(CC) $(CFLAGS) -c $< -o $@# 定义目标规则main: main.o sub.o$(CC) $(CFLAGS) main.o sub.o -o main# 清除中间文件clean:rm -f *.o main```在这个示例中,我们定义了两个变量CC和CFLAGS,分别表示编译器和编译选项。

接着定义了一个编译规则,表示将.c文件编译成.o文件的过程。

其中,$<表示依赖文件(即输入文件),$@表示目标文件(即输出文件)。

最后定义了一个目标规则,表示将main.o和sub.o链接成可执行文件main。

最后,我们定义了一个清除中间文件的规则,可以通过运行make clean来清除中间文件。

可以通过运行make命令来编译和链接程序。

例如,如果你有一个名为main.c和sub.c的源文件,并想将它们编译成可执行文件main,可以在终端中输入以下命令:```$ make main```这将根据makefile中定义的规则自动编译和链接程序,并生成可执行文件main。

总之,makefile是一个非常有用的编译工具,可以帮助我们自动化地构建程序,提高编译效率。

makefile编译流程

makefile编译流程Makefile是一种用于自动化编译的工具,它可以根据源代码文件的依赖关系自动编译出目标文件。

Makefile的编写需要遵循一定的规则和语法,下面将介绍Makefile的编译流程。

1. 编写Makefile文件Makefile文件是一个文本文件,其中包含了编译的规则和依赖关系。

在编写Makefile文件时,需要遵循一定的语法规则,如使用TAB键缩进、使用变量和函数等。

2. 执行make命令在Makefile文件所在的目录下执行make命令,make会自动读取Makefile文件,并根据其中的规则和依赖关系进行编译。

如果Makefile文件中没有指定目标,则默认编译第一个目标。

3. 分析依赖关系在执行make命令时,make会先分析Makefile文件中的依赖关系,确定哪些文件需要重新编译。

如果某个源文件被修改了,那么与之相关的目标文件也需要重新编译。

4. 编译源文件在确定需要重新编译的文件后,make会依次编译每个源文件,生成对应的目标文件。

编译过程中,make会根据Makefile文件中的规则和命令进行编译。

5. 链接目标文件在所有的源文件都编译完成后,make会将所有的目标文件链接起来,生成最终的可执行文件。

链接过程中,make会根据Makefile文件中的规则和命令进行链接。

6. 完成编译当所有的源文件都编译完成并链接成功后,make会输出编译成功的信息,并生成最终的可执行文件。

如果编译过程中出现错误,make会输出错误信息并停止编译。

总之,Makefile编译流程是一个自动化的过程,它可以大大提高编译的效率和准确性。

在编写Makefile文件时,需要注意语法规则和依赖关系,以确保编译过程的正确性。

makefile obj用法

文章标题:深入探讨Makefile中的Obj用法在软件开发中,Makefile是一个非常重要的工具,它帮助程序员管理项目的编译和信息过程。

而Makefile中的Obj用法则是Makefile中非常重要的一部分,它用来指定项目中的目标文件。

在本篇文章中,我们将深入探讨Makefile中的Obj用法,从简单到复杂,由浅入深,帮助读者更好地理解和运用Obj用法。

1. 什么是Makefile在开始深入探讨Makefile中的Obj用法之前,我们先来了解一下什么是Makefile。

Makefile是一种文件,其中包含了一系列规则和命令,用于指导编译器如何编译和信息项目中的源文件,最终生成可执行文件。

Makefile通过维护文件之间的依赖关系,可以使得在修改源文件后,只重新编译需要重新编译的文件,而不是整个项目。

这样可以提高编译的效率,特别是在大型项目中非常重要。

2. Obj用法的基础概念Obj用法是Makefile中用来指定目标文件的一个重要部分。

在Makefile中,通常通过指定目标文件来定义一个编译单元,Obj用法就是用来指定这些目标文件的。

在Makefile中,Obj用法通常是在规则中使用的,用来指定编译的目标文件是哪些。

我们可以这样定义一个规则:```main.o : main.cgcc -c main.c -o main.o```在这个例子中,main.o就是通过Obj用法指定的目标文件,它告诉Makefile需要生成名为main.o的目标文件,并且它是由main.c编译而来的。

3. Makefile中的Obj用法进阶除了简单地指定目标文件外,Obj用法还可以进一步扩展。

在实际开发中,一个目标文件可能由多个源文件编译而来,这时候就需要用到Obj用法的进阶用法了。

在Makefile中,我们可以使用通配符来指定一组目标文件,例如:```%.o : %.cgcc -c $< -o $@```这个规则中,%表示任意的文件名,$<表示依赖文件,$@表示目标文件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Linux基础 – Makfile

梅方靖

编译流程

编译流程: 预处理->编译->汇编->链接

Linux

每个编译的环节都会产生不同类型的文件,对于C程序: 预处理 -> .i文件 编译 -> .s文件 汇编 -> .o文件 => .a文件 .so文件 链接 -> 可执行文件 每个环节都有自己的依赖,即若想生成.o文件,那么需 要.s、.i、.c文件。

Makefile简单的练习

有三个源程序 程序fun:

程序main.c:

使用gcc编译出应用程序test: #gcc fun1.c fun2.c main.c -o test

接下来,我们使用Makefile来写一个 脚本。

Makefile简单的练习

#sample makefile script CC=gcc SRCS=fun1.c fun2.c main.c EXEC=test all: $(CC) $(SRCS) -o $(EXEC) clean: rm -rf $(EXEC)

Makefile自动检测更新

#sample makefile script CC=gcc OBJS=fun1.o fun2.o main.o EXEC=test

Makefile隐式规则

Linux

由于make有自动推导的功能,所以隐式的规则可以让程序员比较简略 地书写Makefile。 make在解释Makefile时,若目标是.o文件,那么他会自动的去寻找相 应的.c文件, 并隐式的进行编译。

Makefile隐式规则 - 简化2

#sample makefile script CC=gcc OBJS=fun1.o fun2.o main.o EXEC=test

Makefile文件的命名可以为“Makefile"或"makefile"。

如果使用非标准命名的makefile,必须用命令开关"-f" 或 “-file”。 参数 “-f <name>” 或 “--file <mane>”告诉make 读入name 作 为makefile文件。

Makefile的好处

编译器类型 编译选项, 通常为-O2 -Wall -I -L 额外链接库 应用程序名 源代码 目标文件

Makefile通用版(基本版)

# makefile example CC=gcc CFLAGS = -Wall -O2 CFLAGS += -I./ -L./ LFLAGS = -lpthread -lm SRCS = fun1.c \ fun2.c \ main.c

Makefile的命名及执行方式

Linux

使用make命令执行Makefile文件。 在默认情况下,make会执行当前目录下的Makefile文件。若当 前目录下找不到相关的Makefile文件,则会出现错误: make: *** No targets specified and no makefile found. Stop.

Makefile的规则(命令)

Linux

规则解释如何编译文件,make根据依赖关系执行产生或更新目标;规 则也说明如何和何时执行动作。有的规则看起来很复杂,但都符合下 述模式。

<target>:<depend> command1 command2

……

target是一个目标文件,可以是可执行文件或.o文件,也可以是执行动作。

Makefile的规则练习

#makefile rule example A:B @echo "A" B:C @echo "B" C:D @echo "C" D: @echo "D" G:

Linux

@echo "G"

分别执行make、make B、make G。 查看结果,并分析结果。

Makefile自动检测更新

编译思考

Linux

对于庞大的工程项目,比如内核源码中存在成千上万个源文件, 那么编译的时候,如何实现自动化编译,即源头文件与头文件 或者静、动态库之间找到彼此的依赖关系进行编译,最终生成 目标文件。 大多数的Winodws的程序员不需要深入了解自动化编译流程,因 为Windows的IDE(Integrated Development Environment)已经做 了相关的工作,比如VC,VB等。而Linux下没有这样的IDE,通常 需要程序员做用脚本自行书写。 要做一个好的professional程序员,尤其是linux程序员,至少 需要懂得设计该脚本 - Makefile。

Linux

all:$(OBJS) $(CC) $(OBJS) -o $(EXEC) fun1.o: fun2.o: main.o:

clean: rm -rf $(EXEC)

简化2: 使用隐式规则,目标文件为.o文件,make自动推导搜索.c文件,并编译。

Makefile隐式声明 - 简化3

#sample makefile script CC=gcc OBJS=fun1.o fun2.o main.o EXEC=test

Linux

Makefile带来的好处——“自动化编译”,一旦写好,只需要 一个make命令,整个工程完全自动编译,极大的提高了软件开 发的效率。 另一个好处,某工程有10万个源文件,如果其中某一个源文件 发生改变,不需要重新编译整个工程,但是我们生成应用程序 前需要将所有的源文件生成.o文件。makefile会根据文件更新 时间而判断,是否需要重新编译源文件成.o文件,在生成应用 程序时,只需要将所有的.o文件做链接即可。

注释: Makefile注释使用"#",若Makefile需要用到“#”,则需要做 转义“\#”。

Makefile的组成

#sample makefile script include other.make

注释

Linux

文件指示,包含其他文件,其他文件中的变量会被包含进来

CC=gcc

SRCS=fun1.c fun2.c main.c EXEC=test

CC,SRCS,EXEC为变量,都是字符串,使用时会完全被替 换。

makefile命令部份,变量在被引用时需要加上$()或者${}

all: $(CC) $(SRCS) -o $(EXEC)

Makefile与程序或其它脚执行顺序一样,都是自上到下。 引用未定义的变量时,不会出错,但其值为空,即什么都没有。

Linux

all:$(OBJS) $(CC) $(OBJS) -o $(EXEC) clean: rm -rf $(EXEC)

简化3: 使用隐式规则,目标的依赖为三个.o文件,fun1.o, fun2.o,main.o, make自动推导,找到相应.c文件生成找到.o文件。

Makefile的变量替换

Makefile的介绍

认识Makefile和make。

Linux

Makfile是一种纯文本的编译脚本,在其中可以指定需要编译哪 些文件,哪些先编译,哪些后编译,哪些需要重新编译,最终 需要生成怎么样的应用程序。

make是一种命令,它用来解释Makefile脚本,并根据脚本中的 指定内容,进行操作。

Linux

EXEC=test

all:$(OBJS) $(CC) $(OBJS) -o $(EXEC) clean: rm -rf $(EXEC)

Makefile的变量追加

Linux

在定义一个变量之后,我们可以继续在变量后面加上新的值。 追加的语法与C语言中复合运算的“+=”类似。 如: CFLAGS = -Wall CFLAGS += -O2 那么最终CFLAGS的值为 -Wall -O2

Linux

all:$(OBJS) $(CC) $(OBJS) -o $(EXEC) fun1.o:fun1.c $(CC) -c fun1.c fun2.o:fun2.c $(CC) -c fun2.c main.o:main.c $(CC) -c main.c clean: rm -rf $(EXEC)

depend目标的依赖,目标若需要成立,必须有依赖。一个target可以拥有多

个depend 。 command是make执行动作,一个目标依赖关系中可以包含多个命令,但是 每个command不能是空格或者其它的字符,只可以一个制表符Tab键。 注:若target缺少depend ,那么command会直接被执行。

#sample makefile script CC=gcc SRCS=fun1.c fun2.c main.c

Linux

EXEC=test

all: $(CC) $(SRCS) -o $(EXEC) 编写完后,保存,在当前目录下执行make命令,生成可执行程序test

Makefile的组成

Makefile里主要包含了五种类型的语句:

例: SRCS = fun1.c fun2.c main.c OBJS = $(SRCS:.c=.o) 那么变量OBJS值为fun1.o fun2.o main.o

Makefile优化

#sample makefile script CC=gcc SRCS=fun1.c fun2.c main.c OBJS=(SRCS:.c=.o)

Linux

工程若干个源文件中,某一个文件发生了改变,我们希望只重新编译被修改 的那一个文件,其它的文件不重新编译。 make在执行时,会确认所有target是否都是最新的,若target的某一个 depend的时间比target新,那么make会重新根据依赖关系来执行相应的命令。 对于例子中的Makefile,all没有依赖所以命令总是会执行。 这里需要修改 Makefile