基于Quartus的FPGACPLD数字系统设计精品

FPGA CPLD 数字电路设计经验分享(经典)

FPGA/CPLD数字电路设计经验分享摘要:在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的基础上,采用合理的设计方法在设计复杂数字系统是行之有效的,通过许多设计实例证明采用这种方式可以使电路的后仿真通过率大大提高,并且系统的工作频率可以达到一个较高水平。

关键词:FPGA 数字电路时序时延路径建立时间保持时间1 数字电路设计中的几个基本概念:1.1 建立时间和保持时间:最小建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。

如图1 。

数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。

PLD/FPGA开发软件可以自动计算两个相关输入的建立和保持时间(如图2)图1 建立时间和保持时间关系图注:在考虑建立保持时间时,应该考虑时钟树向后偏斜的情况,在考虑建立时间时应该考虑时钟树向前偏斜的情况。

在进行后仿真时,最大延迟用来检查建立时间,最小延时用来检查保持时间。

建立时间的约束和时钟周期有关,当系统在高频时钟下无法工作时,降低时钟频率就可以使系统完成工作。

保持时间是一个和时钟周期无关的参数,如果设计不合理,使得布局布线工具无法布出高质量的时钟树,那么无论如何调整时钟频率也无法达到要求,只有对所设计系统作较大改动才有可能正常工作,导致设计效率大大降低。

因此合理的设计系统的时序是提高设计质量的关键。

在可编程器件中,时钟树的偏斜几乎可以不考虑,因此保持时间通常都是满足的。

1.2 FPGA中的竞争和冒险现象信号在FPGA器件内部通过连线和逻辑单元时,都有一定的延时。

基于Quartus II的CPLD的数字系统设计与实现第4章 组合逻辑电路

2.设计要求

对4位超前进位加法器进行功能仿真和时序仿真,然后对仿真的结果进行分析,对比串行 进位加法器的时序,观察延时情况。

3.硬件环境

设计在CPLD开发装置上实现,CPLD型号为EPM2 40T100C5。

4.建立工程

37582Z4

主编

4.1 加法器 4.2 比较器 4.3 编码器 4.4 译码器 4.5 数据选择器 4.6 数据分配器

第4章 时序逻辑电路

4.1.1 半加器加器

1.半加器原理 2.设计要求 3.硬件环境 4.建立工程 5.编译仿真 6.硬件实现 7.创建模块符号 8.问题分析

1.半加器的原理

3.硬件环境

设计在CPLD开发装置上实现,CPLD型号为EPM2 40T100C5。

4.建立工程

建立工程的步骤方法与上文一样,这里的工程命名为SerialAdder。并将上一节设计的 半加器FullAdder bdf文件添加到此工程中。

5.编译仿真

工程设置好后,进行全程编译。

6.硬件实现

首先是将引脚与硬件对应的引脚关系锁定,在需要锁定的节点名处,双击引脚锁定区 Location,在列出的引脚号中进行选择,锁定引脚编号。

7.创建模块符号

创建模块符号时,先打开已编译成功的文件Half Adder bdf,然后选择菜单File→Create→Update →Create Symbol Files for current File,完成当前 文件HalfAdder bdf符号的创建。

8.问题分析

半加器只是实现了单纯的两位数的相加,但是在实际的算术运算中经常遇到低位向高位进 位的加法运算。而此时半加器就显得力不从心了。这个问题如何解决呢?下一节讲解带有

基于Quartus II的电路设计过程图文详解

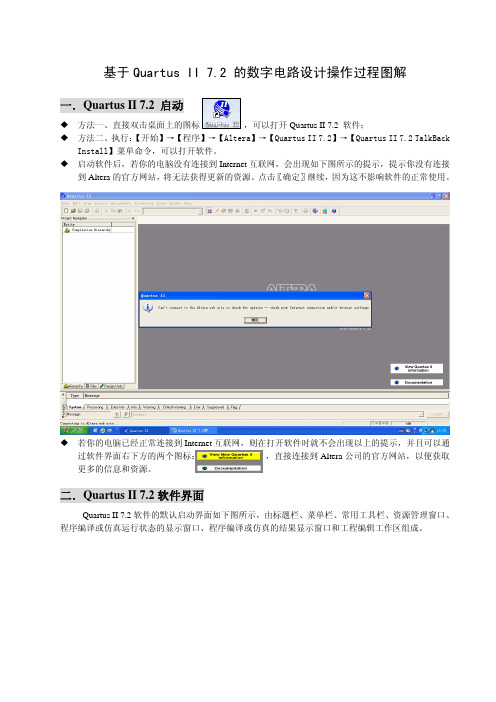

基于Quartus II 7.2 的数字电路设计操作过程图解一.Quartus II 7.2 启动方法一、直接双击桌面上的图标,可以打开Quartus II 7.2 软件;方法二、执行:【开始】→【程序】→【Altera】→【Quartus II 7.2】→【Quartus II 7.2 TalkBack Install】菜单命令,可以打开软件。

启动软件后,若你的电脑没有连接到Internet互联网,会出现如下图所示的提示,提示你没有连接到Altera的官方网站,将无法获得更新的资源。

点击〖确定〗继续,因为这不影响软件的正常使用。

若你的电脑已经正常连接到Internet互联网,则在打开软件时就不会出现以上的提示,并且可以通过软件界面右下方的两个图标:,直接连接到Altera公司的官方网站,以便获取更多的信息和资源。

二.Quartus II 7.2软件界面Quartus II 7.2软件的默认启动界面如下图所示,由标题栏、菜单栏、常用工具栏、资源管理窗口、程序编译或仿真运行状态的显示窗口、程序编译或仿真的结果显示窗口和工程编辑工作区组成。

三.Quartus II 7.2软件使用1. 新建项目工程使用QuartusII7.2设计一个数字逻辑电路,并用时序波形图对电路的功能进行仿真,同时还可以将设计正确的电路下载到可编程的逻辑器件(CPLD、FPGA)中。

因软件在完成整个设计、编译、仿真和下载等这些工作过程中,会有很多相关的文件产生,为了便于管理这些设计文件,我们在设计电路之前,先要建立一个项目工程(New Project),并设置好这个工程能正常工作的相关条件和环境。

建立工程的方法和步骤如下:(1)先建一个文件夹。

就在电脑本地硬盘找个地方注意:文件夹的命名及其保存的路径中不能有中文字符。

(2)再开始建立新项目工程,方法如右图点击:【File】菜单,选择下拉列表中的【New Project Wizard...】命令,打开建立新项目工程的向导对话框。

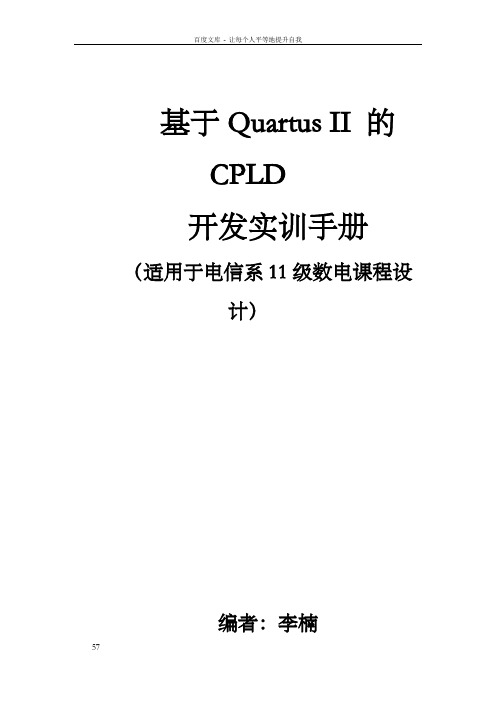

基于QuartusII的CPLD开发实训手册

基于Quartus II 的CPLD开发实训手册(适用于电信系11级数电课程设计)编者:李楠2012-9Quartus II软件利用简介Quartus II是Altera公司提供的FPGA\CPLD开发集成环境,Altera是世界上最大可编程逻辑器件供给商之一。

Quartus II界面友好、利用便捷,被誉为业界最易用易学的EDA软件。

其主要功能为数字电子系统的设计输入、编辑、仿真、下载等。

该软件支持原理图输入设计和VHDL语言(和其它硬件描述语言)输入设计和原理图与HDL混合输入设计。

硬件描述语言(HDL-Hardware Description Language)是一种用于设计硬件电子系统的运算机语言,它用软件编程的方式来描述电子系统的逻辑功能、电路结构和连接形式,与传统的门级描述方式相较,它更适合大规模系统的设计。

VHDL(Very High Speed IC Hardware Description Language)以下将详细介绍原理图输入设计方式,但读者应该更多地关注设计流程,因为除最初的图形编辑输入外,其它处置流程都与文本(如VHDL文件)输入设计完全一致。

实验一原理图方式设计二进制全加器一、设计目的一、通过设计一个二进制全加器,掌握组合逻辑电路设计的方式。

二、初步了解QuartusII采用原理图方式进行设计的流程。

3、初步掌握FPGA开发的流程和大体的设计方式、大体的仿真分析方式。

二、设计原理三、设计内容四、设计步骤1位全加器设计向导1 为本项设计成立文件夹任何一项设计都是一项工程(Project),都必需第一为此工程成立一个放置与此工程相关的所有文件的文件夹,此文件夹将被EDA软件默以为工作库(Work Library)。

一般不同的设计项目最好放在不同的文件夹中,注意,一个设计项目能够包括多个设计文件,如频率计。

打开Quartus Ⅱ,选菜单File→New,在弹出的New对话框当选择Device Design Files页的原理图文件编辑输入项Block Diagram/Schematic File,单击OK按钮后打开原理图编辑窗口如图所示。

《基于QuartusII的FPGACPLD数字系统设计与应用》范例的源程序课案

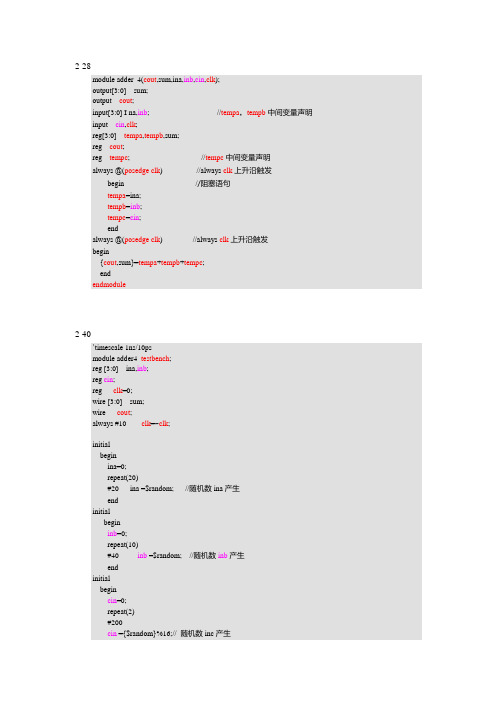

2-28module adder_4(cout,sum,ina,inb,cin,clk);output[3:0] sum;output cout;input[3:0] I na,inb; //tempa,tempb中间变量声明input cin,clk;reg[3:0] tempa,tempb,sum;reg cout;reg tempc; //tempc中间变量声明always @(posedge clk) //always clk上升沿触发begin //阻塞语句tempa=ina;tempb=inb;tempc=cin;endalways @(posedge clk) //always clk上升沿触发begin{cout,sum}=tempa+tempb+tempc;endendmodule2-40`timescale 1ns/10psmodule adder4_testbench;reg [3:0] ina,inb;reg cin;reg clk=0;wire [3:0] sum;wire cout;always #10 clk=~clk;initialbeginina=0;repeat(20)#20 ina =$random; //随机数ina产生endinitialbegininb=0;repeat(10)#40 inb =$random; //随机数inb产生endinitialbegincin=0;repeat(2)#200cin ={$random}%16;// 随机数inc产生#200 $stop;endadder4 adder4_te(.clk(clk),.sum ( sum ),.cout( cout),.ina ( ina ),.inb( inb ),.cin( cin ));initialendmodule2-73LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY SEG_7 ISPORT (SEG: IN STD_LOGIC_VECTOR(3 DOWNTO 0 ); //--四位二进制码输入Q3: OUT STD_LOGIC_VECTOR(6 DOWNTO 0) );//--输出LED七段码END SEG_7;ARCHITECTURE ART OF SEG_7 ISBEGINPROCESS(SEG)BEGINCASE SEG ISWHEN "0000" => Q3<="0000001";--0WHEN "0001" => Q3<="1001111";--1WHEN "0010" => Q3<="0010010";--2WHEN "0011" => Q3<="0000110";--3WHEN "0100" => Q3<="1001100" ; --4WHEN "0101" => Q3<="0100100";--5WHEN "0110" => Q3<="0100000";--6WHEN "0111" => Q3<="0001111";--7WHEN "1000" => Q3<="0000000";--8WHEN "1001" => Q3<="0000100";--9WHEN OTHERS => Q3<="1111111";END CASE;END PROCESS;END ART;3-1`timescale 1ns/1nsmodule Decoder2x4(A,B,EN,Z) ;input A,B,EN;output [0:3] Z;wire Abar, Bbar;assign #1 Abar=~A; // 语句1assign #1 Bbar=~B; // 语句2assign #2 Z[0]=~(Abar &Bbar&EN ) ; // 语句3assign #2 Z[1]=~(Abar & B&EN) ; // 语句4assign #2 Z[2]=~(A&Bbar&EN) ; // 语句5assign #2 Z[3]=~(A&B&EN) ; // 语句6endmodule3-3module FASeq(A, B, Cin, Sum, Cout) ;input A, B, Cin ;output Sum, Cout;reg Sum, Cout;reg T1, T2, T3;always@(A or B or Cin)beginSum=(A^B)^Cin;T1=A&Cin;T2=B&Cin;T3=A&B;Cout = (T1|T2)|T3;endendmodule3-4`timescale 1ns/1nsmodule Test(Pop,Pid);output Pop,Pid;reg Pop,Pid;initialbeginPop = 0; // 语句1Pid = 0; // 语句2Pop = #5 1; // 语句3Pid = #3 1; // 语句4Pop = #6 0; // 语句5Pid = #2 0; // 语句6endendmodule3-5Module FourBitFA(FA,FB,FCin,FSum,FCout);parameter SIZE = 4;input [SIZE:1] FA, FB;output [SIZE:1] FS uminput FCin;input FCout;wire [1: SIZE-1] FTemp;FAStrFA1( .A(FA[1]), .B(FB[1]), .Cin(FCin) , .Sum(FSum[1]), .Cout(FTemp[1] ) ),FA2( .A(FA[2]), .B(FB[2]), .Cin(FTemp[1]),.Sum(FSum[2]),.Cout(FTemp[2])) , FA3( .A(FA[3]), .B(FB[3]), .Cin(FTemp[2]) , .Sum(FSum[3]), .Cout(FTemp[3] ) ), FA4( .A(FA[4]), .B(FB[4]), .Cin(FTemp[3]),.Sum(FSum[4]),.Cout(FCout)) ;endmodule3.1beginArt = 0;Art = 1;end3.2initialbeginCbn <= 0;Cbn<=1;end3.3reg [0:2] Q State;initialbeginQ State = 3’b011;Q State <=3’b100;$display(“Current value of Q_State is”%b,Q State) ;#5; //等待一定的时延。

基于Quartus II的CPLD的数字系统设计与实现第3章 门 电 路

3. 硬件环境

这里的硬件环境与上一节的完全一样。用两个 按键控制一个发光二极管的亮灭。

4. 建立工程

图3-20 或非逻辑电路图

5. 编译仿真

图3-21 输入波形文件图 图3-22 或非逻辑功能仿真图

5. 编译仿真

图3-23 或非逻辑时序仿真图

6. 硬件实现

图3-24 引脚锁定图

3.2.3 异或逻辑电路

1. 或非逻辑原理 2. 设计要求 3. 硬件环境 4. 建立工程 5. 编译仿真 6. 硬件实现

1. 或非逻辑原理

与非门逻辑运算式表示为Y=(A+B)′。可以理解为只有A和B都为0(假)时Y才为1(真)。

2. 设计要求

对或非门进行功能仿真和时序仿真,对比两种 仿真的区别,并用硬件实现或非逻辑,用两个 按键作为输入控制一个发光二极管的亮灭,以 此来验证或非的逻辑关系。

1. 同或逻辑原理 2. 设计要求 3. 硬件环境 4. 建立工程 5. 编译仿真 6.硬件实现

1. 同或逻辑原理

同或逻辑运算式表示为Y=A·B+A′·B′。可以理解为只有A和B相等时Y才为1(真)。

2. 设计要求

对同或门进行功能仿真和时序仿真,对比两种 仿真的区别,并用硬件实现同或门逻辑,用两 个按键作为输入控制一个发光二极管的亮灭, 以此来验证同或门的逻辑关系。

3. 硬件环境

这里的硬件环境和与逻辑的完全一样。用两个 按键控制一个发光二极管的亮灭。

4. 建立工程

图3-25 异或逻辑电路图

5. 编译仿真

图3-26 输入波形文件图 图3-27 异或逻辑功能仿真图

5. 编译仿真

图3-28 异或逻辑时序仿真图

6. 硬件实现

图3-29 引脚锁定图

基于quartusii的fpgacpld数字系统设计与应用范例的源程序

2-28module adder_4(cout,sum,ina,inb,cin,clk);output[3:0] sum;output cout;input[3:0] I na,inb; lk (clk ),.sum ( sum ),.cout ( cout),.ina ( ina ),.inb ( inb ),.cin ( cin ));initialendmodule2-73LIBRARY IEEE;USE SEG_7 ISPORT (SEG: IN STD_LOGIC_VECTOR(3 DOWNTO 0 );(FA[1]), .B(FB[1]), .Cin(FCin) , .Sum(FSum[1]), .Cout(FTemp[1] ) ),FA2( .A(FA[2]), .B(FB[2]), .Cin(FTemp[1]),.Sum(FSum[2]),.Cout(FTemp[2])) ,FA3( .A(FA[3]), .B(FB[3]), .Cin(FTemp[2]) , .Sum(FSum[3]), .Cout(FTemp[3] ) ),FA4( .A(FA[4]), .B(FB[4]), .Cin(FTemp[3]),.Sum(FSum[4]),.Cout(FCout)) ;endmodulebeginArt = 0;Art = 1;endinitialbeginCbn <= 0;Cbn<=1;endreg [0:2] Q State;initialbeginQ State = 3’b011;Q State <=3’b100;$display(“Current value of Q_State is”%b,Q State) ;#5; 3’1”2”3”4”5”6”ddress_a (address),.clock0 (clock),.q_a (sub_wire0),.aclr0 (1'b0),.aclr1 (1'b0),.address_b (1'b1),.addressstall_a (1'b0),.addressstall_b (1'b0),.byteena_a (1'b1),.byteena_b (1'b1),.clock1 (1'b1),.clocken0 (1'b1),.clocken1 (1'b1),.clocken2 (1'b1),.clocken3 (1'b1),.data_a ({8{1'b1}}),.data_b (1'b1),.eccstatus (),.q_b (),.rden_a (1'b1),.rden_b (1'b1),.wren_a (1'b0),.wren_b (1'b0));defparam= "NONE",= "BYPASS",= "BYPASS",= "",= "Cyclone IV GX",= "ENABLE_RUNTIME_MOD=YES,INSTANCE_NAME=rom1",= "altsyncram",= 32,= "ROM",= "NONE",= "CLOCK0",= 5,= 8,= 1;endmodule8-3module cnt(clk,q);input clk;output[5:0] q;reg[5:0] q;always @(posedge clk)beginq<=q+1;endendmodule9-12module ep3c16_Quartus(input reset_n, nclk0 ( clk_24mhz ),.c0 ( clk_50mhz ));CPU CPU_inst lk_0 (clk_50mhz),.in_port_to_the_key (gpio[13:9]),.out_port_from_the_LCD_CLK (gpio[8]),.out_port_from_the_LCD_CS (gpio[6]),.out_port_from_the_LCD_SID (gpio[7]),.out_port_from_the_LED (led[7:0]),.reset_n (reset_n),.rxd_to_the_uart_0 (gpio[4]),.txd_from_the_uart_0 (gpio[5]));endmodule9-14while(!(UART->等待状态寄存器的接收数据: dat = '.';break;}if(dat == '.'){integer = 0;i = 1;str ++;continue;}if( integer == 1 ){rev = rev * 10 + dat;}else{rev = rev + dat / (10 * i);i = i * 10 ;}str ++;}return rev;}esult(s), .dataa(acc32), .datab(M)); ata(s), .q(acc32), .clock(clk)); (sin), .inclock(clk), .outclock(clk),.address(msbs));defparam = 8;defparam = 8;defparam = "";endmodule10-7module cacode(input clk,output out);reg[8:1]G1=12'b1111_1111;reg[8:1]G2=12'b1111_1111;always@(posedge clk)beginG1[8:1]<={G1[7:1],G1[1]};G2[8:1]<={G2[7:1],G2[1]};G1[1]<=G1[3]^G1[8];G2[1]<=G2[2]^G2[3]^G2[6]^G2[8];endassign out=G1[1]^G2[4]^G2[6];endmodule10-10`timescale 1 ns / 1 ps`include ""Module FFT256 ( CLK ,RST ,ED ,START ,SHIFT ,DR ,DI ,RDY ,OVF1 ,OVF2 ,ADDR ,DOR ,DOI );`FFT256paramnb 256CLK(CLK), .RST(RST), .ED(ED), .START(START), .DR(DR), .DI(DI), .RDY(rdy1), .DOR(dr1), .DOI(di1));FFT16 #(nb) U_FFT1(.CLK(CLK), .RST(RST), .ED(ED),.START(rdy1),.DIR(dr1),.DII(di1),.RDY(rdy2), .DOR(dr2),. DOI(di2));wire [1:0] shiftl=SHIFT[1:0];CNORM #(nb) U_NORM1( .CLK(CLK), .ED(ED), TART(rdy2), R(dr2),.DI(di2),.SHIFT(shiftl), VF(OVF1),.RDY(rdy3),.DOR(dr3),.DOI(di3)); LK(CLK),.RST(RST),.ED(ED),.START(rdy3),. DR(dr3),.DI(di3),.RDY(rdy4), .DOR(dr4), .DOI(di4));BUFRAM256C #(nb+2) U_BUF2(.CLK(CLK),.RST(RST),.ED(ED), .START(rdy4),.DR(dr4),.DI(di4),.RDY(rdy5), .DOR(dr5), .DOI(di5)); LK(CLK), .RST(RST), .ED(ED),.START(rdy5),. DIR(dr5),.DII(di5),.RDY(rdy6), .DOR(dr6), .DOI(di6));wire [1:0] shifth= SHIFT[3:2]; LK(CLK), .ED(ED),.START(rdy6), R(dr6), .DI(di6),.SHIFT(shifth), VF(OVF2),.RDY(rdy7),.DOR(dr7), .DOI(di7));BUFRAM256C #(nb+4) Ubuf3(.CLK(CLK),.RST(RST),.ED(ED),.START(rdy7),. DR(dr7),.DI(di7),.RDY(rdy8), .DOR(dr8), .DOI(di8));`ifdef FFT256parambuffers3 // 3-data buffer configuratiionalways @(posedge CLK) begin //POINTER to the result samples if (RST)addri<=8'b0000_0000;else if (rdy8==1 )addri<=8'b0000_0000;else if (ED)addri<=addri+1;endassign ADDR= addri ;assign DOR=dr8;assign DOI=di8;assign RDY=rdy8;`elsealways @(posedge CLK) begin //POINTER to the result samples if (RST)addri<=8'b0000_0000;else if (rdy7)addri<=8'b0000_0000;else if (ED)addri<=addri+1;endassign #1 ADDR= {addri[3:0] , addri[7:4]} ;assign #2 DOR= dr7;assign #2 DOI= di7;assign RDY= rdy7;`endifendmodule。

基于QuartusII的CPLD的数字系统设计与实现课程设计

基于QuartusII的CPLD的数字系统设计与实现课程设计1. 引言数字系统设计与实现是电子信息工程专业的一门重要课程,是学生掌握数字电路设计与实现的基础,具有一定的理论和实践意义。

本文将介绍基于QuartusII的CPLD的数字系统设计与实现课程设计的具体内容和实践步骤。

2. 设计背景与目的CPLD(Complex Programmable Logic Device)是一种可编程数字逻辑器件。

相比于普通的ASIC(Application-Specific Integrated Circuit)和FPGA(Field-Programmable Gate Array)器件,CPLD具有逻辑门数量多、功耗低等优点,适用于嵌入式系统、通信设备、工控设备等多个领域。

因此,CPLD的数字系统设计与实现课程设计旨在帮助学生掌握CPLD的基本原理、设计方法和实现技术,从而提高学生的数字电路设计和实现能力。

3. 设计内容3.1 设计思路本次课程设计的设计思路为:首先确定设计需求和目标,然后进行电路设计与仿真,最后实现电路并进行测试。

具体流程设计流程图设计流程图3.2 设计需求和目标本次课程设计的设计需求和目标如下:•设计一个功能较为简单的数字系统,包含输入、处理和输出三个部分。

•设计中需要使用基于QuartusII的CPLD开发板进行电路实现,并用Verilog硬件描述语言进行编程设计。

•设计需求和目标均需要满足实验要求,通过实验测试和评估。

3.3 电路设计与仿真基于上述需求和目标,我们进行了电路设计与仿真。

本课程设计的电路设计包括以下四个方面的内容:3.3.1 输入部分电路设计本文的输入部分选用拨码开关,可以通过拨动不同的拨码开关改变该输入端口的输入的状态。

3.3.2 处理部分电路设计本文的处理部分电路设计选用一个比较器。

该比较器可以将输入的二进制数与给定的比较值进行比较,然后输出比较结果,高电平表示输入数大于或等于比较值,低电平表示输入数小于比较值。

基于FPGA和Quartus_II设计的智能函数发生器_毕业设计论文 精品推荐

课程设计题目基于FPGA和Quartus II设计的智能函数发生器所在院(系)物理与电信工程学院基于FPGA和Quartus II设计的智能函数发生器[摘要] 信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的应用。

它能够产生多种波形,如三角波、锯齿波、矩形波(含方波)、正弦波等,在电路实验和设备检测中具有十分广泛的用途。

例如在通信、广播、电视系统中,都需要射频(高频)发射,这里的射频波就是载波,把音频(低频)、视频信号或脉冲信号运载出去,就需要能够产生高频的振荡器。

在工业、农业、生物医学等领域内,如高频感应加热、熔炼、淬火、超声诊断、核磁共振成像等,都需要功率或大或小、频率或高或低的信号发生器。

本设计采用FPGA来设计制作多功能信号发生器。

该信号发生器可以产生锯齿波、三角波、方波等波形。

[关键词]信号发生器;VHDL;FPGA;三角波;方波;锯齿波。

目录1.引言 (1)2.FPGA简介 (1)2.1VHDL和V ERILOG简介 (3)2.2设计工具简介 (3)3.系统设计 (3)3.1VHDL程序语言基本设计 (3)3.2波形发生器设计 (4)3.3程序设计原理框图 (4)4 系统的软件设计与仿真 (6)4.1系统仿真时序图 (6)4.2RTL仿真硬件图 (7)5总结体会与展望 (8)参考文献 (9)附录A 设计原理图 (11)附录B 系统仿真图 (11)附录C 源程序清单 (12)1.引言20世纪90年代,国际上电子和计算机技术较先进的国家,一直在积极探索新的电子电路设计方法。

电子设计自动化(EDA)工具给电子设计带来了巨大的变革,特别是可编程逻辑器件和硬件描述语言的出现和发展,解决了用传统的方法设计较大系统工程时的诸多不便,成为电子电路设计人员最得力的助手。

随着计算机和EDA技术的发展,基于FPGA的电子设计则是目前发展较为迅速的一个领域,而且广泛应用于计算机、通信等各个领域。

基于quartusii的fpgacpld数字系统设计与应用范例的源程序

2-28module adder_4(cout,sum,ina,inb,cin,clk);output[3:0] sum;output cout;input[3:0] I na,inb; lk (clk ),.sum ( sum ),.cout ( cout),.ina ( ina ),.inb ( inb ),.cin ( cin ));initialendmodule2-73LIBRARY IEEE;USE SEG_7 ISPORT (SEG: IN STD_LOGIC_VECTOR(3 DOWNTO 0 );(FA[1]), .B(FB[1]), .Cin(FCin) , .Sum(FSum[1]), .Cout(FTemp[1] ) ),FA2( .A(FA[2]), .B(FB[2]), .Cin(FTemp[1]),.Sum(FSum[2]),.Cout(FTemp[2])) ,FA3( .A(FA[3]), .B(FB[3]), .Cin(FTemp[2]) , .Sum(FSum[3]), .Cout(FTemp[3] ) ),FA4( .A(FA[4]), .B(FB[4]), .Cin(FTemp[3]),.Sum(FSum[4]),.Cout(FCout)) ;endmodulebeginArt = 0;Art = 1;endinitialbeginCbn <= 0;Cbn<=1;endreg [0:2] Q State;initialbeginQ State = 3’b011;Q State <=3’b100;$display(“Current value of Q_State is”%b,Q State) ;#5; 3’1”2”3”4”5”6”ddress_a (address),.clock0 (clock),.q_a (sub_wire0),.aclr0 (1'b0),.aclr1 (1'b0),.address_b (1'b1),.addressstall_a (1'b0),.addressstall_b (1'b0),.byteena_a (1'b1),.byteena_b (1'b1),.clock1 (1'b1),.clocken0 (1'b1),.clocken1 (1'b1),.clocken2 (1'b1),.clocken3 (1'b1),.data_a ({8{1'b1}}),.data_b (1'b1),.eccstatus (),.q_b (),.rden_a (1'b1),.rden_b (1'b1),.wren_a (1'b0),.wren_b (1'b0));defparam= "NONE",= "BYPASS",= "BYPASS",= "",= "Cyclone IV GX",= "ENABLE_RUNTIME_MOD=YES,INSTANCE_NAME=rom1",= "altsyncram",= 32,= "ROM",= "NONE",= "CLOCK0",= 5,= 8,= 1;endmodule8-3module cnt(clk,q);input clk;output[5:0] q;reg[5:0] q;always @(posedge clk)beginq<=q+1;endendmodule9-12module ep3c16_Quartus(input reset_n, nclk0 ( clk_24mhz ),.c0 ( clk_50mhz ));CPU CPU_inst lk_0 (clk_50mhz),.in_port_to_the_key (gpio[13:9]),.out_port_from_the_LCD_CLK (gpio[8]),.out_port_from_the_LCD_CS (gpio[6]),.out_port_from_the_LCD_SID (gpio[7]),.out_port_from_the_LED (led[7:0]),.reset_n (reset_n),.rxd_to_the_uart_0 (gpio[4]),.txd_from_the_uart_0 (gpio[5]));endmodule9-14while(!(UART->等待状态寄存器的接收数据: dat = '.';break;}if(dat == '.'){integer = 0;i = 1;str ++;continue;}if( integer == 1 ){rev = rev * 10 + dat;}else{rev = rev + dat / (10 * i);i = i * 10 ;}str ++;}return rev;}esult(s), .dataa(acc32), .datab(M)); ata(s), .q(acc32), .clock(clk)); (sin), .inclock(clk), .outclock(clk),.address(msbs));defparam = 8;defparam = 8;defparam = "";endmodule10-7module cacode(input clk,output out);reg[8:1]G1=12'b1111_1111;reg[8:1]G2=12'b1111_1111;always@(posedge clk)beginG1[8:1]<={G1[7:1],G1[1]};G2[8:1]<={G2[7:1],G2[1]};G1[1]<=G1[3]^G1[8];G2[1]<=G2[2]^G2[3]^G2[6]^G2[8];endassign out=G1[1]^G2[4]^G2[6];endmodule10-10`timescale 1 ns / 1 ps`include ""Module FFT256 ( CLK ,RST ,ED ,START ,SHIFT ,DR ,DI ,RDY ,OVF1 ,OVF2 ,ADDR ,DOR ,DOI );`FFT256paramnb 256CLK(CLK), .RST(RST), .ED(ED), .START(START), .DR(DR), .DI(DI), .RDY(rdy1), .DOR(dr1), .DOI(di1));FFT16 #(nb) U_FFT1(.CLK(CLK), .RST(RST), .ED(ED),.START(rdy1),.DIR(dr1),.DII(di1),.RDY(rdy2), .DOR(dr2),. DOI(di2));wire [1:0] shiftl=SHIFT[1:0];CNORM #(nb) U_NORM1( .CLK(CLK), .ED(ED), TART(rdy2), R(dr2),.DI(di2),.SHIFT(shiftl), VF(OVF1),.RDY(rdy3),.DOR(dr3),.DOI(di3)); LK(CLK),.RST(RST),.ED(ED),.START(rdy3),. DR(dr3),.DI(di3),.RDY(rdy4), .DOR(dr4), .DOI(di4));BUFRAM256C #(nb+2) U_BUF2(.CLK(CLK),.RST(RST),.ED(ED), .START(rdy4),.DR(dr4),.DI(di4),.RDY(rdy5), .DOR(dr5), .DOI(di5)); LK(CLK), .RST(RST), .ED(ED),.START(rdy5),. DIR(dr5),.DII(di5),.RDY(rdy6), .DOR(dr6), .DOI(di6));wire [1:0] shifth= SHIFT[3:2]; LK(CLK), .ED(ED),.START(rdy6), R(dr6), .DI(di6),.SHIFT(shifth), VF(OVF2),.RDY(rdy7),.DOR(dr7), .DOI(di7));BUFRAM256C #(nb+4) Ubuf3(.CLK(CLK),.RST(RST),.ED(ED),.START(rdy7),. DR(dr7),.DI(di7),.RDY(rdy8), .DOR(dr8), .DOI(di8));`ifdef FFT256parambuffers3 // 3-data buffer configuratiionalways @(posedge CLK) begin //POINTER to the result samples if (RST)addri<=8'b0000_0000;else if (rdy8==1 )addri<=8'b0000_0000;else if (ED)addri<=addri+1;endassign ADDR= addri ;assign DOR=dr8;assign DOI=di8;assign RDY=rdy8;`elsealways @(posedge CLK) begin //POINTER to the result samples if (RST)addri<=8'b0000_0000;else if (rdy7)addri<=8'b0000_0000;else if (ED)addri<=addri+1;endassign #1 ADDR= {addri[3:0] , addri[7:4]} ;assign #2 DOR= dr7;assign #2 DOI= di7;assign RDY= rdy7;`endifendmodule。