EDA技术课程设计报告

eda课程设计5篇[修改版]

![eda课程设计5篇[修改版]](https://img.taocdn.com/s3/m/a1aef8d5dd36a32d72758100.png)

第一篇:eda课程设计数字钟一、设计要求设计一个数字钟,具体要求如下:1、具有时、分、秒计数显示功能,以24小时循环计时。

2、具有清零、校时、校分功能。

3、具有整点蜂鸣器报时以及LED花样显示功能。

二、设计方案根据设计要求,数字钟的结构如图8-3所示,包括:时hour、分minute、秒second计数模块,显示控制模块sel_clock,七段译码模块deled,报时模块alert。

三、VHDL程序library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; useIEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code. --library UNISIM;--use UNISIM.VComponents.all;entityddz is port(rst,clk: in std_logic; hour_h: out std_logic_vector( 6 downto 0); hour_l: outstd_logic_vector( 6 downto 0); min_h: out std_logic_vector( 6 downto 0);min_l: out std_logic_vector( 6 downto 0);sec_h: out std_logic_vector( 6 downto 0);sec_l: out std_logic_vector( 6 downto 0)); endddz;architecture Behavioral of ddz is signalcnt: std_logic_vector(15 downto 0); signalsec_h_in: std_logic_vector( 3 downto 0); signalsec_l_in: std_logic_vector( 3 downto 0); signalmin_h_in: std_logic_vector( 3 downto 0); signalmin_l_in: std_logic_vector( 3 downto 0); signalhour_h_in: std_logic_vector(3 downto 0); signalhour_l_in: std_logic_vector(3 downto 0);signalclk_s,clk_m,clk_h: std_logic; begin process(rst,clk) begin if rst='0' then sec_h_in'0');sec_l_in'0');clk_msec_l_inifsec_h_in=5 thensec_h_inclk_melsesec_h_inclk_mend if; else sec_l_inclk_mend if; end if; end process;process(rst,clk_m) begin if rst='0' then-- min_h_in'0');min_l_in'0'); -- clk_hmin_l_inmin_h_inclk_mend if; else min_l_inend if; end if; end process;process(rst,clk_n) begin if rst='0' then-- hour_h_in'0');hour_l_in'0'); -- clk_hhour_l_inhour_h_inclk_nend if; else hour_l_inend if; end if; end process;process(sec_l_in) begin casesec_l_in iswhen "0000" =>sec_lsec_lsec_lsec_lsec_lsec_lsec_lsec_lsec_lsec_lsec_lprocess(sec_h_in) begin casesec_h_in iswhen "0000" =>sec_hsec_hsec_hsec_hsec_hsec_hsec_hsec_hsec_hsec_hsec_hprocess(min_l_in) begin casemin_l_in iswhen "0000" =>min_lmin_lmin_lwhen "0011" =>min_lmin_lmin_lmin_lmin_lmin_lmin_lmin_lprocess(min_h_in) begin casemin_h_in iswhen "0000" =>min_hmin _h min _hmin _hmin _h min _hmin _hmin _hmin _hmin _hmin _hend case; end process;process(hour_l_in) begin casehour_l_in iswhen "0000" =>hour_lhour_lhour_lhour_lhour_lhour_lhour_lhour_lhour_lhour_lhour_lprocess(hour_h_in) begin casehour_h_in iswhen "0000" =>hour_hhour_hhour_hhour_h hour _h hour _h hour _h hour _h hour _hhour_h hour _h四、VHDL仿真结果五、课程设计心得通过这次课程设计,有效得巩固了课本所学的知识,而且通过上机仿真不断发现问题并及时改正,加深了我们对该课程设计的印象。

EDA课程设计报告--EDA数字抢答器

学生课程设计报告课程名称:EDA数字抢答器目录一、课程设计目的 (3)二、课程设计题目描述和要求 (3)三、课程设计报告内容 (4)四、结论 (21)五、结束语 (22)六、参考书目 (22)一、课程设计目的.设计一个可容纳4组参赛的数字式抢答器。

通过此次设计熟练掌握VHDL 语言,并掌握设计所用的软件。

二、课程设计题目描述和要求在许多比赛活动中,为了准确、公正、直观地判断出第一抢答者通常设置一台抢答器,通过数显、灯光及音响等多种手段指示出第一抢答者。

同时,还可以设置计分、犯规及奖惩计录等多种功能。

本设计的具体要求是:(1) 设计制作一个可容纳四组参赛者的数字智力抢答器,每组设置一个抢答按钮供抢答者使用。

(2) 电路具有第一抢答信号的鉴别和锁存功能。

(3) 系统具有计分电路。

(4) 系统具有犯规电路。

系统设计方案:系统的输入信号有:各组的抢答按钮A、B、C、D,系统清零信号CLR,系统时钟信号CLK,计分复位端RST,加分按钮端ADD,计时预置控制端LDN,计时使能端EN,计时预置数据调整按钮可以用如TA、TB表示;系统的输出信号有:四个组抢答成功与否的指示灯控制信号输出口可用如LEDA、LEDB、LEDC、LEDD表示,四个组抢答时的计时数码显示控制信号若干,抢答成功组别显示的控制信号若干,各组计分动态显示的控制信号若干。

整个系统至少有三个主要模块:抢答鉴别模块;抢答计时模块;抢答计分模块,其他功能模块(犯规警告模块,输出显示模块)。

三、课程设计报告内容按照要求,我们可以将整个系统分为四个主要模块:抢答鉴别模块;抢答计时模块;抢答计分模块;译码显示模块。

对于需显示的信息,需要增加或外接译码器,进行显示译码。

考虑到实验开发平台提供的输出显示资源的限制,我们将组别显示和计时显示的译码器内设,而将各组的计分显示的译码器外接。

整个系统的大致组成框图如图2.1所示。

图2.1 LED A LED B LED C LED D3.1抢答鉴别模块3.1.1抢答鉴别模块的功能抢答队伍共分为四组A,B,C,D。

EDA课程设计报告

EDA课程设计报告•相关推荐EDA课程设计报告在我们平凡的日常里,报告的使用成为日常生活的常态,报告中涉及到专业性术语要解释清楚。

那么报告应该怎么写才合适呢?以下是小编为大家整理的EDA课程设计报告,希望对大家有所帮助。

EDA课程设计报告1实训任务:一、实训目的和要求:(1)熟练掌握keil c51集成开发环境的使用方法(2)熟悉keil c51集成开发环境调试功能的使用和dp?51pro。

net单片机仿真器、编程器、实验仪三合一综合开发平台的使用。

(3)利用单片机的p1口作io口,学会利用p1口作为输入和输出口。

(4)了解掌握单片机芯片的烧写方法与步骤。

(5)学会用单片机汇编语言编写程序,熟悉掌握常用指令的功能运用。

(6)掌握利用protel 99 se绘制电路原理图及pcb图。

(7)了解pcb板的制作腐蚀过程。

二、实训器材:pc机(一台)pcb板(一块)520ω电阻(八只)10k电阻(一只)led发光二极管(八只)25v 10μf电容(一只)单片机ic座(一块)at89c51单片机芯片(一块)热转印机(一台)dp?51pro。

net单片机仿真器、编程器、实验仪三合一综合开发平台(一台)三、实训步骤:(2)将流水灯程序编写完整并使用tkstudy ice调试运行。

(4)打开电源,将编写好的程序运用tkstudy ice进行全速运行,看能否实现任务要求。

(6)制板。

首先利用protel 99 se画好原理图,根据原理图绘制pcb图,然后将绘制好的pcb布线图打印出来,经热转印机转印,将整个布线图印至pcb板上,最后将印有布线图的pcb板投入装有三氯化铁溶液的容器内进行腐蚀,待pcb板上布线图外的铜全部后,将其取出,清洗干净。

(7)焊接。

将所给元器件根据原理图一一焊至pcb板相应位置。

(8)调试。

先把at89c51芯片插入ic座,再将+5v电源加到制作好的功能板电源接口上,观察功能演示的整个过程(看能否实现任务功能)。

eda课程设计报告

eda课程设计报告一、课程目标知识目标:1. 学生能理解EDA(电子设计自动化)的基本概念,掌握EDA工具的使用方法。

2. 学生能运用EDA软件进行电路设计与仿真,理解并掌握数字电路的设计原理。

3. 学生了解并掌握基础的硬件描述语言(如VHDL/Verilog),能完成简单的数字系统设计。

技能目标:1. 学生通过EDA软件的操作,培养电子电路设计、仿真与验证的实际操作能力。

2. 学生通过小组合作完成设计项目,提高团队协作与沟通技巧。

3. 学生能够运用所学知识解决实际问题,具备一定的创新意识和动手能力。

情感态度价值观目标:1. 学生在EDA课程学习中,培养对电子科学技术的兴趣和探究精神。

2. 学生通过课程实践,增强自信心和成就感,激发进一步学习的动力。

3. 学生在学习过程中,树立正确的工程伦理观念,认识到技术发展对社会的责任和影响。

课程性质:本课程为电子信息工程及相关专业高年级学生的专业核心课程,旨在通过理论与实践相结合的教学,提高学生的电子设计能力。

学生特点:学生已具备一定的电子技术基础,具有较强的学习能力和实践欲望,对新技术和新工具充满好奇心。

教学要求:结合学生特点,注重培养实际操作能力,鼓励学生创新思维,提高解决实际问题的能力。

通过课程目标分解,确保学生在知识、技能和情感态度价值观方面的全面成长。

后续教学设计和评估将以此为基础,关注学生的学习成果。

二、教学内容根据课程目标,教学内容分为以下三个模块:1. EDA基本概念与工具使用- 教材章节:第一章 EDA技术概述,第二章 EDA工具简介- 内容列举:EDA发展历程,常用EDA软件介绍,软件安装与配置,基本操作流程。

2. 数字电路设计与仿真- 教材章节:第三章 数字电路设计基础,第四章 仿真技术- 内容列举:数字电路设计原理,EDA软件电路设计流程,仿真参数设置,波形分析与验证。

3. 硬件描述语言与数字系统设计- 教材章节:第五章 硬件描述语言,第六章 数字系统设计实例- 内容列举:硬件描述语言基础,VHDL/Verilog语法要点,简单数字系统设计方法,设计实例分析与实操。

电子行业EDA课程设计报告

电子行业EDA课程设计报告1. 引言本文档是电子行业EDA课程的设计报告,旨在介绍课程的设计目标、内容、实施过程以及所取得的成果。

EDA(Electronics Design Automation)是指电子设计自动化,是电子行业中一种重要的设计和开发方法。

本课程旨在培养学生掌握EDA的基本概念、流程和工具,从而提高他们在电子行业中的设计能力和竞争力。

2. 设计目标本课程的设计目标如下:1.培养学生掌握EDA的基本概念和原理。

2.培养学生熟练掌握EDA工具的使用和应用。

3.培养学生具备独立进行EDA项目设计和开发的能力。

4.提高学生的团队合作和沟通能力。

3. 课程内容本课程的内容主要包括以下几个方面:3.1 EDA基础知识在本节课程中,学生将学习EDA的基本概念和原理,包括电子设计流程、硬件描述语言、电路仿真和验证等方面的知识。

3.2 EDA工具的使用本节课程将介绍常用的EDA工具,包括电路设计工具、电路仿真工具和电路布局工具等。

学生将学习如何使用这些工具进行电路设计、仿真和验证。

3.3 EDA项目设计与开发在本节课程中,学生将进行一个EDA项目的设计与开发实践。

学生将根据给定的项目需求,使用所学的EDA工具进行电路设计、仿真和验证,并最终提交一个完整的EDA项目报告。

3.4 团队合作与项目管理本节课程将讲解团队合作和项目管理的基本原理和方法,包括任务分配、进度管理和沟通协作等方面的内容。

学生将通过分组合作,在完成EDA项目的过程中提高团队合作和沟通能力。

4. 实施过程本课程的实施过程主要包括以下几个阶段:4.1 阶段一:知识讲解在此阶段,教师将讲解EDA的基本概念、流程和工具使用方法。

学生将通过课堂听讲和课后阅读相关资料,对EDA的基础知识进行学习和理解。

4.2 阶段二:工具练习在此阶段,学生将通过实际操作,熟悉常用的EDA工具的使用方法。

教师将提供实验环境和相关实验指导,学生将利用课余时间进行工具的练习和实践。

EDA课程设计报告

串入并出移位寄存器一、设计任务与要求1.设计一个4位的串入并出移位寄存器;2.要求能分别输入两组4位数据,同时输出显示。

二、方案设计与论证移位寄存器除了具有存储代码的功能以外,还具有移位功能。

所谓移位功能,是指寄存器里存储的代码能在移位脉冲的作用下依次左移或右移。

因此,移位寄存器不但可以用来寄存代码,还可用来实现数据的串并转换、数字的运算以及数据处理等。

所谓的串入/并出移位寄存器,即输入的数据是一个接着一个有序地进入,输出时则一起送出。

两组数据伴随着时钟信号依次输入,输出时消除延时。

三、单元电路设计与参数计算程序代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity sipo isport(d_in:in std_logic;clk:in std_logic;d_out:out std_logic_vector(3 downto 0));end sipo;architecture a of sipo issignal q:std_logic_vector(3 downto 0);beginp1:process(clk)beginif clk'event and clk='1'thenq(0)<=d_in;for i in 1 to 3 loopq(i)<=q(i-1);end loop;end if;end process p1;d_out<=q;end a;四、总原理图及元器件清单1.总原理图1.元件清单(或程序清单)五、安装与调试输入的数据为“1010”、“0111”两组4 位数据。

因输入的数据是每次一位依序进入,故输入、输出信号之间有 4 个CLK 时间的延迟。

为了过滤中间没用的数据,只读取完整的存储数据,实用上可将取样脉冲的周期设定成CLK 脉冲的四倍,也就是说,每经过4 个CLK 脉冲后实验连线输入信号D-IN(代表一位的串行数据输入)和CLK(代表抽样时钟信号),CLK 时钟信号接适配器板子上的时钟信号,频率建议取在1Hz 左右,D-IN 接拨码开关或按键;输出信号有D-OUT0~D-OUT3(代表4位并行数据输出),接发光二极管。

eda课程设计时间报告

eda课程设计时间报告一、课程目标知识目标:1. 学生能理解EDA(电子设计自动化)的基本概念,掌握EDA工具的使用方法。

2. 学生能运用EDA软件完成基本的电路设计,如数字电路、模拟电路等。

3. 学生了解并掌握电路仿真、波形分析等技能。

技能目标:1. 学生能独立使用EDA工具进行电路设计和仿真。

2. 学生具备分析电路原理和优化电路设计的能力。

3. 学生能够通过团队合作,共同完成一个综合性的电路设计项目。

情感态度价值观目标:1. 学生培养对电子工程的兴趣,激发创新意识和探索精神。

2. 学生树立正确的工程观念,注重实践操作和工程应用。

3. 学生在团队协作中学会沟通、分享和承担责任,培养合作精神。

课程性质:本课程为实践性较强的课程,结合理论教学和实际操作,培养学生运用EDA工具进行电路设计和仿真的能力。

学生特点:本年级学生具备一定的电子基础知识,具有较强的学习能力和动手能力,对新鲜事物充满好奇心。

教学要求:结合学生特点和课程性质,注重理论与实践相结合,充分调动学生的主观能动性,培养其创新意识和实践能力。

在教学过程中,将目标分解为具体的学习成果,便于教学设计和评估。

二、教学内容本课程教学内容主要包括以下三个方面:1. EDA基本概念与工具使用- 了解EDA的发展历程、基本概念及其在电子工程设计中的应用。

- 学习并掌握主流EDA软件(如Multisim、Protel等)的基本操作和使用方法。

2. 电路设计与仿真- 学习数字电路、模拟电路的基本原理和设计方法。

- 利用EDA软件进行电路设计与仿真,分析电路性能,优化设计方案。

教学大纲:- 数字电路设计:组合逻辑电路、时序逻辑电路设计。

- 模拟电路设计:放大器、滤波器等电路设计。

- 电路仿真:仿真参数设置、波形分析、性能评估。

3. 综合性项目实践- 学生分组进行项目实践,运用所学知识完成一个具有实际意义的电路设计项目。

- 项目过程中,培养学生的团队协作、沟通能力及解决问题的能力。

EDA技术课程设计报告

课程设计任务书设计题目1:数码管显示数字钟设计院(系)分管领导:教研室主任:指导教师:2017年 6月 23日目录第1章引言 0第2章电路原理 0第3章程序设计 (1)3.1 顶层模块设计 (2)3.2 时钟分频模块设计 (2)3.3 按键驱动模块设计 (2)3.4 时钟计数模块设计 (3)3.5 整点报时模块 (4)3.6 LED灯花样显示模块 (5)3.7 数码管显示模块设计 (6)第4章调试、测试分析及结果 (8)4.1 调试 (8)4.2 测试分析 (8)4.3 结果 (9)第5章小结 (10)参考文献 (11)附录电路图及程序 (12)第1章引言EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪60年代中期从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL 或者Verilog HDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

此次课程设计我们运用QuartusⅡ这个软件,使用Verilog HDL语言进行编程。

数字钟是一种用数字电路技术实现时、分、秒计时的钟表。

与机械钟相比具有更高的准确性和直观性,具有更长的使用寿命,已得到广泛的使用。

数字钟的设计方法有许多种,例如可用中小规模集成电路组成电子钟,也可以利用专用的电子钟芯片配以显示电路及其所需要的外围电路组成电子钟,还可以利用单片机来实现电子钟等等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

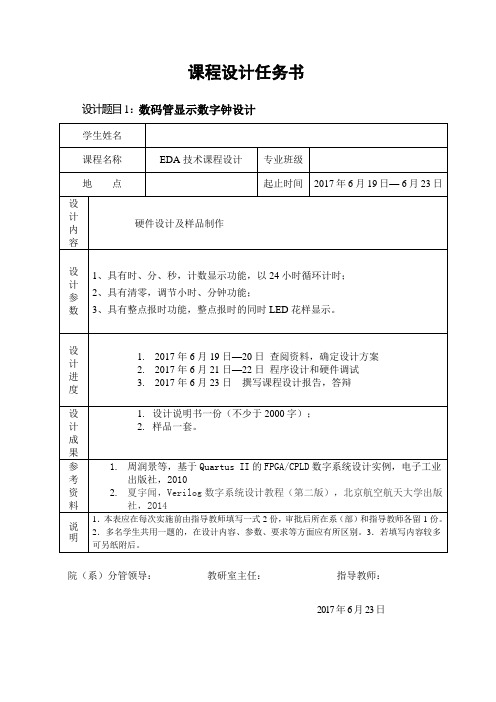

课程设计任务书设计题目1:数码管显示数字钟设计学生姓名课程名称EDA技术课程设计专业班级地点起止时间2017年6月19日— 6月23日设计内容硬件设计及样品制作设计参数1、具有时、分、秒,计数显示功能,以24小时循环计时;2、具有清零,调节小时、分钟功能;3、具有整点报时功能,整点报时的同时LED花样显示。

设计进度1.2017年6月19日—20日查阅资料,确定设计方案2.2017年6月21日—22日程序设计和硬件调试3.2017年6月23日撰写课程设计报告,答辩设计成果1. 设计说明书一份(不少于2000字);2. 样品一套。

参考资料1.周润景等,基于Quartus II的FPGA/CPLD数字系统设计实例,电子工业出版社,20102.夏宇闻,Verilog数字系统设计教程(第二版),北京航空航天大学出版社,2014说明1.本表应在每次实施前由指导教师填写一式2份,审批后所在系(部)和指导教师各留1份。

2.多名学生共用一题的,在设计内容、参数、要求等方面应有所区别。

3.若填写内容较多可另纸附后。

院(系)分管领导:教研室主任:指导教师:2017年 6月 23日EDA技术课程设计报告目录第1章引言 (1)第2章电路原理 (2)第3章程序设计 (3)3.1 顶层模块设计 (3)3.2 时钟分频模块设计 (4)3.3 按键驱动模块设计 (4)3.4 时钟计数模块设计 (4)3.5 整点报时模块 (5)3.6 LED灯花样显示模块 (7)3.7 数码管显示模块设计 (7)第4章调试、测试分析及结果 (10)4.1 调试 (10)4.2 测试分析 (10)4.3 结果 (12)第5章小结 (13)参考文献 (14)附录电路图及程序 (15)EDA技术课程设计报告第1章引言EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪60年代中期从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL 或者Verilog HDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

此次课程设计我们运用QuartusⅡ这个软件,使用Verilog HDL语言进行编程。

数字钟是一种用数字电路技术实现时、分、秒计时的钟表。

与机械钟相比具有更高的准确性和直观性,具有更长的使用寿命,已得到广泛的使用。

数字钟的设计方法有许多种,例如可用中小规模集成电路组成电子钟,也可以利用专用的电子钟芯片配以显示电路及其所需要的外围电路组成电子钟,还可以利用单片机来实现电子钟等等。

这些方法都各有其特点,其中利用单片机实现的电子钟具有编程灵活,以便于功能的扩展。

本次课程设计要求利用EDA技术,设计一个数码管显示数字钟的样品,数字钟要求具备以下功能:1、具有时、分、秒,计数显示功能,以24小时循环计时;2、具有清零,调节小时、分钟功能;3、具有整点报时功能,整点报时的同时LED花样显示。

1EDA技术课程设计报告第2章电路原理数码管显示数字钟设计,运用到8位数码管,要求其中6位数码管动态显示,分别显示时、分、秒的计数,同时对时间进行设置,数字钟的总体功能按照要求可以分为基本的数字时钟显示(具有时、分、秒,计数显示功能,以24小时循环计时)、手动校准(具有清零,调节小时、分钟功能)、整点报时、LED灯花样显示四大部分。

其总体功能设计框图如图2.1所示:数码管显示数字钟数字时钟显示手动校准整点报时LED灯花样显示图2.1 数字钟总体功能设计框图2EDA 技术课程设计报告3第3章 程序设计其中,“时钟分频模块”用于对芯片晶振提供的时钟信号进行分频,然后给其他模块分配需要的时钟频率。

按键输入的信号经过按键去抖后传送给“时钟计数模块”。

正常计数时,“时钟计数模块”将处理好的时、分、秒数据实时传送给“数码管显示模块”,当有来自“按键驱动模块”的信号时,改变相应的时、分、秒计数器中的值,实现调整时间的作用。

“数码管显示模块”实时将“时钟计数模块”的数据转换成数码管动态显示信号进行显示。

最后,加上一个“整点报时”模块和“LED 灯花样显示模块”经过时钟分频信号,传递给“数码管显示模块”,实现所需功能。

数字钟设计原理如图3.1所示:3.1 顶层模块设计顶层模块设计如附录图3所示,其RTL 电路图如附录图4所示。

顶层模块包含四个输入:系统时钟输入“clk ”,秒设置信号“sset ”,分钟设置信号“mmset ”,小时设置信号“hset ”。

一个8位的段选数码管显示值输出“seg ”,一个8位的片选数码管显示哪一个数码管输出“dig ”,将输出给数码管进行动态显示。

“时钟分频模块”电路符号名为“int _ div ”,“按键驱动模块”电路符号名慰“an _ jian ”,“时钟计数模块”内部采用三格计数器级联的方式分别驱动时、分、秒计数,秒计数器和分计数器均为60进制计数器,小时计数器为24进制计数器,电路符号名分别为两个“ji _ shu _ 60”和一个“ji _ shu _ 24”。

时钟分频模块 按键驱动模块 时钟计数模块整点报时模块LED 灯花样显示模块数码管显示模块图3.1 数字钟设计原理图EDA 技术课程设计报告43.2 时钟分频模块设计“时钟分频模块”直接使用老师上课所给的分频程序,加入两个分频模块,与“时钟计数模块”和“按键驱动模块”进行连接。

3.3 按键驱动模块设计按键驱动模块使用原理图方法设计,采用在按键信号传输过程中串联触发器实现按键去抖,保证触发器两次触发的间隔远大于按键抖动的时间,而远小于人动作反应的时间。

另外因为实例用独立按键按下后是低电平,所以在触发器后面串联一个非门,使其变为高电平有效。

附录图1所示为按键驱动模块原理图,图3.2所示为按键驱动模块封装而成的电路元件。

该模块包括四个输入,时钟信号clk ,秒设置输入s _ in ,分钟设置输入m _ in ,小时设置输入h _ in ;三个输出,秒设置输出s _ out ,分钟设置输出m _ out ,小时设置输出h _ out 。

从该模块的原理图可以看出,时、分、秒三个按键的去抖原理完全一样,这里提取小时输入和输出进行仿真验证,得到的结果如图4.1所示,每一个时钟上升沿h _ out 的值都保持和h _ in 的值相反,该设计能够达到预期设计要求。

3.4 时钟计数模块设计如附录图2所示。

“时钟计数模块”内部采用三个计数器级联的方式分别驱动时、分、秒计数,秒计数器和分钟计数器均为60进制计数器,小时计数器为24进制计数器,为方便驱动数码管,三个计数器的输出均为两位的十进制数据。

秒调整信号通过一个或门和秒进位信号一起驱动分钟计数器;小时调整和分钟调整同理。

60进制计数器主要Verilog HDL 代码如下: beginif(!rst) //0图 3.2 按键驱动模块封装而成的电路元EDA技术课程设计报告beginq1<=0; q2<=0;endelsebegin q1[3:0]=q1[3:0]+1; co<=0;if(q1[3:0]>9) begin q1[3:0]=0;q2[3:0]=q2[3:0]+1;if(q2[3:0]>5) begin q2[3:0]=0; co<=1;endendelse q1=q1;endend24进制计数器主要Verilog HDL代码如下:beginco=0;q1[3:0]=q1[3:0]+1;if(q1[3:0]>9) begin q1[3:0]=0; q2[3:0]=q2[3:0]+1;endif(q1==4)if(q2==2) begin q1=0;q2=0; end end如图4.2所示该模块中60进制模块与24进制模块的仿真波形,60进制模块设置qs0、qs1分别为个位、十位,个位计数到9之后清零,十位计数到5之后清零,24进制模块设置qh0、qh1分别为个位、十位,个位计数到9之后清零,十位计数到2之后清零。

3.5 整点报时模块整点报时模块的设计思路是当数字钟计数到一个整点时间时,蜂鸣器开始响5EDA 技术课程设计报告6鸣。

蜂鸣器的封装设计如图3.3所示,程序设计为一段乐谱,主要Verilog HDL 代码如下:always @(posedge clk_4Hz) begin case(j)'d1:origin='d4916; //low 'd2:origin='d6168; 'd3:origin='d7281; 'd4:origin='d7791; 'd5:origin='d8730; 'd6:origin='d9565; 'd7:origin='d10310;'d8:origin='d010647; //middle 'd9:origin='d011272; 'd10:origin='d011831; 'd11:origin='d012087; 'd12:origin='d012556; 'd13:origin='d012974; 'd14:origin='d013346; 'd15:origin='d13516; //high 'd16:origin='d13829; 'd17:origin='d14108; 'd18:origin='d11535;'d19:origin='d14470; 'd20:origin='d14678; 'd21:origin='d14864; default:origin='d011111;图3.3 蜂鸣器封装模EDA技术课程设计报告endcaseendalways @(posedge clk_4Hz) //乐谱beginif(len==63)len=0;elselen=len+1;case(len)0:j=3;1:j=3;2:j=3;3:j=3;4:j=5;5:j=5;6:j=5;7:j=6;8:j=8;9:j=8;10:j=8; 11:j=6;12:j=6;13:j=6;14:j=6;15:j=12;16:j=12;17:j=12;18:j=15;19:j=15;20: j=15;21:j=15;22:j=15;23:j=9;24:j=9;25:j=9;26:j=927:j=9;28:j=9;29:j=9;30 :j=9;31:j=9;32:j=9;33:j=9;34:j=10;35:j=7;36:j=7;37:j=6;38:j=6;39:j=5;40 :j=5;41:j=5;42:j=6;43:j=8;44:j=8;45:j=9;46:j=9;47:j=3;48:j=3;49:j=8;50: j=8;51:j=8;52:j=5;53:j=5;54:j=8;55:j=5;56:j=5;57:j=5;58:j=5;59:j=5;60:j =5;61:j=5;62:j=5;63:j=5;endcaseend3.6 LED灯花样显示模块LED灯花样显示模块是与整点报时模块同时工作,当蜂鸣器响鸣时LED灯闪烁。