8086简易计算器的设计 微机原理 计硬报告

8086实现计算器实验报告

实验报告一、题目:数字计算器的汇编语言实现二、设计任务:利用8086微处理器,可编程并行通信接口芯片 8255A等相关器件在proteus中设计仿真一个简单数字计算器,利用8086汇编语言编写完成加、减、乘、除、幂运算、阶乘运算、求余运算等功能,能实现键盘十进制运算表达式的输入和显示,按“=”后输出十进制表示的运算结果。

三、需求分析:(一)根据数据的输入要求对键盘(本实验中用4X5按钮阵来代替键盘)的数据读取及运算符号读取进行定义,根据8255A的相关性质对其进行编程实现,使每一个按钮对应一个十以内的整数或者某一个运算符号。

(二)根据8255A的输出性质,选择输出端口,对其进行编程,8255A为8086微处理器与外部设备之间提供并行输入/输出的通道。

不用附加外部电路,并行接口是在多根数据线上,以数据字节/字与I/O设备交换信息。

(三)数据的显示有LED数码管显示,LED数码管有7个字符段和一个小数点段组成,每段对应一个二极管,当二极管点亮时,相应的的字符段点亮,可以进行数据的显示。

四、总体方案首先利用程序不断扫描所设的按钮键盘是不是有输入,如果没有就一直扫描,如果有就调用子程序进行判断,是数值则进行存储并同时进行显示,是运算符号等就调用相应的子程序进行操作,操作后则继续利用程序不断扫描键盘是不是有输入,从而实现部分十进制数的加、减、乘、除、幂运算、阶乘运算、求最大公约数的运算。

运算完成后根据程序将运算的结果储存到锁存器中并显示到LED显示器上。

五、硬件设计本次实验需要的元器件有:8086微处理器、可编程并行通信接口芯片8255A、输入输出锁存器74LS373、LED数码显示管、若干按钮组成的4X5矩阵按键、若干电阻、总线等。

1、8086微处理器当引脚接高电平时,CPU工作于最小模式。

此时,引脚信号24~31的含义及其功能如下:(1)IO/M:存储器、I/O端口选择控制信号。

信号指明当前CPU是选择访问存储器还是访问I/O端口。

微型计算机原理及接口技术实验报告

成都理工大学微型计算机原理及接口技术实验报告学院: 核技术与自动化工程学院专业: 电气工程及其自动化班级:学号:姓名:指导老师:完成时间:实验一EMU 8086软件的使用1、实验目的通过对emu8086的使用,来理解《微型计算机原理及接口技术》课本上的理论知识,加深对知识的运用,以及emu8086交互式学习汇编语言(Assembly Language)、计算机结构(Computer Architecture)和逆向工程(Reverse Engineering)的完整仿真体系。

以及了解创建,编译,链接,调试运行,拟屏幕、源代码观察、复位、辅助工具、变量、DEBUG、堆栈及FLAGS(标志寄存器)观察等功能。

2、实验环境及设备实验中用到的硬件:记本电脑。

软件:emu8086编程程序emu8086.exe。

3、实验内容1.emu8086的编辑面板:其中编程时要做好三个要点1.数据段:segmentends2.堆栈段:segmentends3.代码段e segmentends这三个框架。

编辑好程序如下; multi-segment executable file template.data segment; add your data here!a db 0b db 1c db 0pkey db "press any key...$"endsstack segmentdw 128 dup(0)endscode segmentstart:; set segment registers:mov ax, datamov ds, axmov es, ax; add your code heremov al ,aadd al,bmov c,allea dx, pkeymov ah, 9int 21h ; output string at ds:dx; wait for any key....mov ah, 1int 21hmov ax, 4c00h ; exit to operating system.int 21hendsend start ; set entry point and stop the assemble d1 segment进行编译后:无错误后点击运行:程序中实现了赋值,传址,加法,中断等功能。

8086微机原理实验报告

8086微机原理实验报告实验名称:8086微机原理实验实验目的:1.深入了解8086微处理器的内部结构和指令系统。

2.掌握汇编语言的编程方法和技巧。

3.熟悉微机系统的输入输出操作原理。

4.掌握8086微机系统的调试方法和程序调试技巧。

实验器材:1.8086微处理器芯片2.Intel 8086学习板3.编程器4.示波器5.实验箱实验步骤:1.熟悉8086微处理器的内部结构和指令系统在开始实验前,首先需要熟悉8086微处理器的内部结构和指令系统。

通过阅读教材和讲义,了解到8086微处理器采用16位结构,具有4个寄存器组,支持16种不同寻址方式的指令。

熟练掌握常用的指令系统和汇编语言的编程方法。

2.设计并编制简单的汇编程序在熟悉8086微处理器的内部结构和指令系统后,我们开始设计并编制简单的汇编程序。

本实验中,我们编写了一个简单的汇编程序,用于实现两个数的加法操作,并将结果存储在内存中。

程序中使用了mov指令将操作数送入寄存器,add指令将它们相加,再用mov指令将结果存储到内存中。

程序流程图如下所示:a. 将第一个数送入累加器A中。

b. 将第二个数送入寄存器B中。

c. 执行add指令,将A和B相加,结果保存在A中。

d. 将结果存储到内存中。

e. 程序结束。

3.调试程序并进行测试在完成汇编程序的编写后,我们需要使用调试器对程序进行调试,并进行测试。

首先,将程序加载到学习板上进行调试。

在调试过程中,我们使用示波器观察各个信号的波形,以确定程序的正确性。

通过逐步单步执行程序并观察寄存器和标志位的变化,我们验证了程序的正确性。

接下来,我们使用输入设备输入两个数,并观察输出结果是否正确。

测试结果表明程序正确实现了两个数的加法操作。

4.总结体会和改进建议通过本次实验,我们深入了解了8086微处理器的内部结构和指令系统,掌握了汇编语言的编程方法和技巧,熟悉了微机系统的输入输出操作原理,以及掌握了8086微机系统的调试方法和程序调试技巧。

8086汇编语言程序设计 微机实验报告

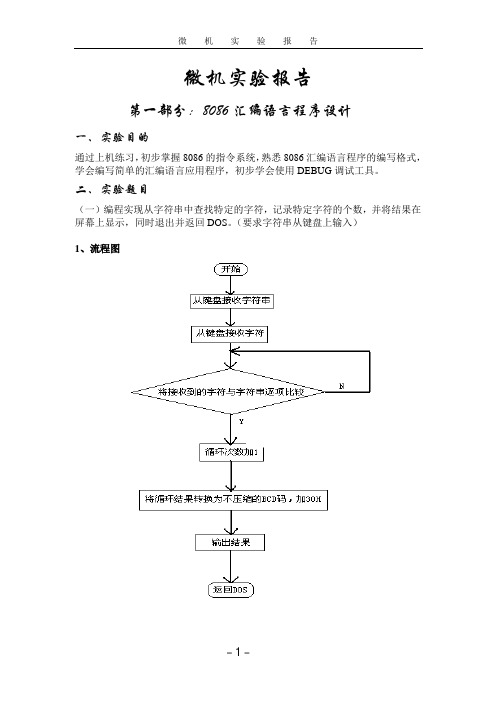

微机实验报告第一部分:8086汇编语言程序设计一、实验目的通过上机练习,初步掌握8086的指令系统,熟悉8086汇编语言程序的编写格式,学会编写简单的汇编语言应用程序,初步学会使用DEBUG调试工具。

二、实验题目(一)编程实现从字符串中查找特定的字符,记录特定字符的个数,并将结果在屏幕上显示,同时退出并返回DOS。

(要求字符串从键盘上输入)1、流程图2、实验程序及注释DATA SEGMENTBUFSIZE DB 20 ;数据段ACTCHAR DB ? ;定义字符串CHARTEXT DB 20 DUP(?) ;给输入字符分配内存DB '$'CNT DB 0 ;给计数器分配内存STRING1 DB 'PLEASE INPUT THE STRING:','$'STRING2 DB 0AH,0DH,'INPUT THE WORD YOU WANT TO CHECK:','$' STRING3 DB 0AH,0DH,'THE NUMBER OF THE WORD IS:','$'DATA ENDS ;数据段结束COSEG SEGMENT ;代码段ASSUME CS:COSEG,DS:DATASTART: MOV AX,DATAMOV DS,AXMOV DX,OFFSET STRING1 ;显示提示语:请输入字符串MOV AH,09H ;输出字符串STRING1INT 21HMOV DX,OFFSET BUFSIZE ;从键盘输入字符串存入BUFSIZEMOV AH,0AH ;并送显INT 21HMOV DX,OFFSET STRING2 ;显示提示语:想查询的字符是MOV AH,09H ;输出字符串STRING2INT 21HMOV AH,01H ;从键盘上输入字符到AL中并送显INT 21HMOV BX,OFFSET CHARTEXT ;将字符串首地址存入BXMOV CL,ACTCHAR ;置循环次数CX=字符串长度XOR CH,CHLP1: CMP AL, [BX] ;字符串从头开始与键入字符AL比较JZ LP2 ;相等则转入LP2INC BX ;指针指向字符串下一个字符DEC CX ;循环次数减一JNZ LP1 ;若还有未比较的字符,继续循环LP1JMP FINI ;若全部比较完毕,跳转FINILP2: INC CNT ;计数器增一INC BX ;指针指向字符串下一个字符DEC CX ;循环次数减一JNZ LP1 ;若还有未比较的字符,跳至LP1 FINI: MOV DX,OFFSET STRING3 ;显示提示语:所查询的字符个数:MOV AH,09HINT 21HMOV AL,CNT ;将计数器的值送ALAAM ;将此值转换成非压缩BCD码ADD AH,30H ;将BCD码转换为ASCⅡ码MOV DL,AH ;高位送显MOV AH,02HINT 21HMOV AL,CNT ;再将计数器的值送ALAAMADD AL,30H ;将BCD码转换为ASCⅡ码MOV DL,AL ;低位送显MOV AH,02HINT 21HMOV AH,4CH ;结束INT 21HCOSEG ENDS ;代码段结束END START ;程序结束3、运行结果PLEASE INPUT THE STRING(先输入字符串):ASDFAAD↙INPUT THE WORD YOU WANT TO CHECK(输入待查找字符): A↙THE NUMBER OF THE WORD IS(数量为):3↙PLEASE INPUT THE STRING(先输入字符串):ASDFAAD↙INPUT THE WORD YOU WANT TO CHECK(输入待查找字符):9↙THE NUMBER OF THE WORD IS(数量为):0↙PLEASE INPUT THE STRING(先输入字符串):ASDFAAD↙INPUT THE WORD YOU WANT TO CHECK(输入待查找字符): S↙THE NUMBER OF THE WORD IS(数量为):1↙4、程序改进○1循环次数的改进原来的程序:MOV CX,19改进原因:此程序表明无论输入的字符串多长,即使没有达到限定的最大字符串的长度,也要循环19次。

8086简易计算器的设计微机原理计硬报告DOC

简易计算器的设计 自动化(电站方向)计算机硬件技术实践报告题目 姓名 专业 班级学号上海电力学院自动化工程学院 实践报告内容(目录)一. 设计题目二.开发目的三.小组成员分工及成果四.设计方案以及论证五. 硬件原理图(包括芯片的选型介绍)六. 程序流程图(包括各个子系统和子过程的程序流程)七. 程序清单,要有适当的注释八. 程序运行结果分析与预测九. 结果评述或总结(对实验结果进行分析,对实验过程进行总结,系统改进升级建议或者提出新的方案等。

)8255 控制键. 设 计题目 :用 8086 设计一个能实现 0~9 整数加法运算的计算器 , 并用 2 位 LED 数码显示 . 键盘包 括0-9 , + , - ,*, / , =, ON/C;共16个按键.能实现简单的清零操作,减法运算,乘法运算.. 开发目的 :通过课程设计,熟悉和掌握微机系统的软件、硬件设计的方法、设计步骤,得到微机 开发应用方面的初步训练。

培养集体讨论设计题目的总体设计方案、 编程、软件硬件调试、 编写设计报告等问题,做到理论联系实际,提高动手能力和分析问题、解决问题的能力,实现由学习知识到应用知识的初步过渡。

通过本次课程设计熟练运用程序对 盘和LED 显示的控制,完成计算器加减法的应用,并熟练应用8086汇编语言编写应用程序和实际设计中的硬软件调试方法和步骤,熟悉微机系统的硬软件开发工具的使用方法。

本组的三个成员一起讨论研究简易计算器设计的主要方案。

粗略设计程序流程图以确定简易计算器设计的大概框架。

明确目的后各自查询资料了解设计原理、逐步清晰设计思路。

以下为大体分工:主要负责: 1 、设计主要程序,编写;2、查找资料验证修改;主要负责: 1、选择需要用的各个芯片;2、设计硬件原理图;主要负责: 1、各个芯片功能的资料查找;2 、设计程序流程图四. 设计方案以及论证利用程序不断扫描所设的按钮键盘是不是有输入,如果没有就一直扫描,如果有就调 用子程序进行判断,是数值则进行存储并同时进行显示,是运算符号等就调用相应的子程 序进行操作,操作后则继续利用程序不断扫描键盘是不是有输入,从而实现部分十进制数 的加、减、乘、除的运算。

微机原理上机实验(八+十二)实验报告 8086中断实验 步进电机实验

微机原理上机实验报告实验八:8086中断实验实验十二:步进电机实验微机原理上机实验(八)实验报告实验八:8086中断实验一、实验目的1、了解8086内部响应中断的机制;掌握中断向量的作用。

2、利用实验仪上单脉冲、74HC244电路,不使用8259,实现一个中断实例。

3、复习本节实验内容,可尝试自行编写程序,做好实验准备工作,填写实验报告。

二、实验内容1、编制程序:拨动单脉冲开关,“”送给8086的INTR,触发中断;8086通过INTA信号,读取中断向量;8086计数中断次数,显示于F5区的数码管上注意:给INTR高电平信号,8086就会相应中断,所以实验开始前,保证单脉冲开关给8086低电平;中断程序中,加一个较长的延时程序,在中断结束前,有时间拨动单脉冲开关,恢复给8086低电平。

三、实验原理图本实验,通过F4区的8个拨动开关,给74HC244设定中断向量;本实验的中断向量是08H,即IN7-IN0位数据是00001000。

同学可以自定义中断向量,实验程序中处理中断向量部分程序作相应调整四、实验步骤1、连线说明:B4区:CS244、BLE ——C1区:GNDB4区:RD(IO区)——A3区:INTAA3区:INTR ——B2区:单脉冲B4区:JP57(D0..D7) ——A3区:JP41B4区:JP52(IN0..7) ——F4区:JP27(1..8)D3区:CS、A0、A1 ——A3区:CS1、A0、A1D3区:PC0、PC1 ——F5区:KL1、KL2D3区:JP20、B、C ——F5区:A、B、C2、运行程序3、实验开始前,保证单脉冲开关给8086低电平;运行程序;向下拨动开关(触发中断),立即向上拨动开关,产生一个“”,观察结果,数码管上显示的次数与拨动开关次数是否对应。

五、实验代码EXTRN InitKeyDisplay:NEAR, Display8:NEAR_STACK SEGMENT STACKDW 100 DUP(?)_STACK ENDS_DATA SEGMENT WORD PUBLIC 'DATA'BUFFER DB 8 DUP(?)Counter DB ?ReDisplayFlag DB 0_DATA ENDSCODE SEGMENTSTART PROC NEARASSUME CS:CODE, DS:_DATA, SS:_STACKMOV AX,_DATAMOV DS,AXMOV ES,AXNOPCALL InitKeyDisplay ;对键盘、数码管控制器8255初始化CALL WriIntverMOV Counter,0 ;中断次数MOV ReDisplayFlag,1 ;需要显示STI ;开中断START1: LEA SI,BufferCALL Display8CMP ReDisplayFlag,0JZ START1CALL LedDisplayMOV ReDisplayFlag,0JMP START1WriIntver PROC NEARPUSH ESMOV AX,0MOV ES,AXMOV DI,20HLEA AX,INT_0STOSWMOV AX,CSSTOSWPOP ESRETWriIntver ENDPLedDisplay PROC NEARMOV AL,CounterMOV AH,ALAND AL,0FHMOV Buffer,ALAND AH,0F0HROR AH,4MOV Buffer + 1,AHMOV Buffer + 2,10H ;高六位不需要显示MOV Buffer + 3,10HMOV Buffer + 4,10HMOV Buffer + 5,10HMOV Buffer + 6,10HMOV Buffer + 7,10HRETLedDisplay ENDPINT_0: PUSH DXPUSH AXMOV AL,CounterADD AL,1DAAMOV Counter,ALMOV ReDisplayFlag,1CALL LedDisplayDELAY: PUSH BXPUSH CXPUSH DIPUSH SIMOV CX,20DELAY1: LEA SI,BufferCALL Display8loop DELAY1POP SIPOP DIPOP CXPOP BXPOP AX六、实验思考题1.绘制本实验的详细实验电路图?微机原理上机实验(十二)实验报告实验十二:步进电机实验一、实验目的1、了解步进电机的基本原理,掌握步进电机的转动编程方法2、了解影响电机转速的因素有那些二、实验内容编写程序:使用F5区的键盘控制步进电机的正反转、调节转速,连续转动或转动指定步数;将相应的数据显示在F5区的数码管上。

8086微机汇编实验报告

电梯模拟实验一、实验目的通过综合实验使学员复习并熟练掌握各个模块电路功能、基本原理、线路连接和驱动方法。

自己编写嵌入式代码进行驱动,掌握相关的程序设计、电路测试的基本能力。

通过动手实践进一步加深对理论知识的理解,提高动手能力。

二、实验原理1.使用模块:本实验使用了8254、8255、七段数码管、4*4键盘、步进电机、喇叭6大模块来进行模拟电梯的综合实验。

2.连接电路:(1).使用8255的C口的PC0~PC7连接4*4键盘的行3~列0,接收4*4键盘输入;(2).将8255的A口PA0~PA7分别与七段数码管的段码驱动输入端a~dp相连,位码驱动输入端S0接+5V,S1~S3接GND,编程实现在其显示电梯所处的楼层;(3).使用8255的B口的PB0~PB3分别与步进电机的驱动输入端BA~BD相连,编程实现根据键盘输入实现顺时针(反时针)转动;(4).8254的CLK0接1MHz时钟,GATE0接8255的PB5,OUT0和8255的PB4分别接与门的两个输入端A和B,与门输出端Y连接喇叭,编程实现电梯到达所要求的楼层后发出设定的声音进行提示,具体实验电路如下图.3.接线:4.程序流程三、关键点及难点1.关键点(1).8255的控制方式8255是通用并行接口芯片,但在具体应用时,要根据实际情况选择工作方式,连接硬件电路(外设),待进行初始化编程之后才能成为某一专用的接口电路。

8255的初始化编程比较简单,只需要一个方式控制字就把3个端口设置完成。

方式控制字决定端口A、B和C的工作方式,如下图所示。

(2).I/O端口值的读写实验中,会对大量的I/O端口进行读写操作,我们通过I/O端口对相关的硬件进行数据的读写,在进行数据读写的过程中,要清楚相关的函数操作以及写入的bit位的值对硬件起到怎样的控制。

下面是C语言方式对I/O端口读写进行操作的相关函数:(3).七段数码管工作原理实验所用的七段数码管为共阴型,段码采用同相驱动,输入加高电平,选中的数码管亮,位码加反相驱动器,位码输入端高电平选中。

简易计算器的设计

学号:课程设计题目简易计算器的设计学院自动化专业电气工程及其自动化班级姓名指导教师2014 年1月9日课程设计任务书学生姓名:专业班级:指导教师:工作单位:自动化学院题目: 简易计算器的设计初始条件:用8086CPU、8255A并行通信接口、七段LED数码管接口、小键盘控制电路接口、外围电路芯片及元器件实现一个简易计算器,完成相应的程序编写。

要求完成的主要任务: (包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)(1)可进行2位十进制的加减乘除法运算。

(2)键盘输入数据,同时LED数码管显示,模拟计算器的工作。

(3)键盘上要求有0~9数字键,+、-、×、÷、=功能键,清除键C。

(4)撰写课程设计说明书。

内容包括:摘要、目录、正文、参考文献、附录(程序清单)。

正文部分包括:设计任务及要求、方案比较及论证、软件设计说明(软件思想,流程,源程序设计及说明等)、程序调试说明和结果分析、课程设计收获及心得体会。

时间安排:12月26日----- 12月 28 日查阅资料及方案设计12月29日----- 1 月 2 日编程1 月 3日----- 1 月 7日调试程序1 月 8日----- 1 月 9日撰写课程设计报告指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (1)1设计的任务及要求 (2)2方案的设计 (3)2.1方案设计论证 (3)2.2方案概述与原理硬件电路图 (3)3系统模块与功能 (5)3.18086CPU芯片 (5)3.2 8255A 并行通信接口芯片 (5)3.3 译码电路 (6)3.4 小键盘电路 (6)3.5 四位七段 LED 数码管显示电路 (7)4软件设计框图与程序 (8)4.1计算器系统程序总体流程图 (8)4.2 模块程序流程图与程序 (8)4.2.1流程图 (8)4.2.2键盘扫描流程图 (9)4.3输入运算 (10)4.3.1输入运算的流程图 (10)4.3.2输入运算程序 (10)4.4显示部分 (11)4.4.1显示部分流程图 (11)4.4.2显示部分程序 (12)5系统仿真 (14)6小结与体会 (15)参考文献 (16)附录:设计源程序 (17)本科生课程设计成绩评定表摘要这次微机原理的课程设计的题目是简易计算器的设计,设计一个可以实现2位十进制加减乘除运算功能的电路,并用LED显示出来。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

计算机硬件技术实践报告题目简易计算器的设计姓名专业自动化(电站方向)班级学号上海电力学院自动化工程学院实践报告内容(目录)一. 设计题目二. 开发目的三. 小组成员分工及成果四. 设计方案以及论证五. 硬件原理图(包括芯片的选型介绍)六. 程序流程图(包括各个子系统和子过程的程序流程)七. 程序清单,要有适当的注释八. 程序运行结果分析与预测九. 结果评述或总结(对实验结果进行分析,对实验过程进行总结,系统改进升级建议或者提出新的方案等。

)一. 设计题目:用8086设计一个能实现0~9整数加法运算的计算器,并用2位LED数码显示. 键盘包括0-9,+ ,-,*,/,=,ON/C;共16个按键.能实现简单的清零操作,减法运算,乘法运算.二.开发目的:通过课程设计,熟悉和掌握微机系统的软件、硬件设计的方法、设计步骤,得到微机开发应用方面的初步训练。

培养集体讨论设计题目的总体设计方案、编程、软件硬件调试、编写设计报告等问题,做到理论联系实际,提高动手能力和分析问题、解决问题的能力,实现由学习知识到应用知识的初步过渡。

通过本次课程设计熟练运用程序对8255控制键盘和LED显示的控制,完成计算器加减法的应用,并熟练应用8086汇编语言编写应用程序和实际设计中的硬软件调试方法和步骤,熟悉微机系统的硬软件开发工具的使用方法。

三.小组成员分工及成果:本组的三个成员一起讨论研究简易计算器设计的主要方案。

粗略设计程序流程图以确定简易计算器设计的大概框架。

明确目的后各自查询资料了解设计原理、逐步清晰设计思路。

以下为大体分工:主要负责:1、设计主要程序,编写;2、查找资料验证修改;主要负责:1、选择需要用的各个芯片;2、设计硬件原理图;主要负责:1、各个芯片功能的资料查找;2、设计程序流程图四.设计方案以及论证:利用程序不断扫描所设的按钮键盘是不是有输入,如果没有就一直扫描,如果有就调用子程序进行判断,是数值则进行存储并同时进行显示,是运算符号等就调用相应的子程序进行操作,操作后则继续利用程序不断扫描键盘是不是有输入,从而实现部分十进制数的加、减、乘、除的运算。

运算完成后根据程序将运算的结果储存到锁存器中并显示到LED 显示器上。

主要器件选择是采用8086CPU做主控制器,8255作为并行接口电路实现按键扫描以及数码管的显示。

通过8255A的C口和A口实现键盘的接入,通过键盘的不断扫描,如果有键按下,通过查表法分别将输入的数据读到AL中并保存在第一个和第二个数里,将8255A的B端口接上共阴极LED灯,将输入的数据通过查表法,将四段码送共阴极LED 灯显示,当按下‘=’时,通过判断字符,8086来实现不同的操作,并将结果在LED灯上显示,当按下“C”时,将数据先清零,同时LED灯上显示为“00”。

五.硬件原理图(包括芯片的选型介绍):芯片选型及介绍:(1)8086CPU:8086通过数据总线、地址总线、控制总线完成对8253和8255的读写工作,与接口部件实现数据传送,让接口部件实现预计的功能.8086CPU的40条引脚信号可按功能分可分为四类,它们是:地址总线,数据总线,控制总线,其它(时钟与电源)。

最小模式下一些引脚功能(MN/MX接+5V):AD15~AD0,地址/数据总线A19/S6~A16/S3,地址/状态总线RD,读信号WR,写信号M/IO,存储器/输入输出控制信号ALE,地址锁存允许信号READY(Ready),准备就绪信号INTR,可屏蔽中断请求信号INTA,中断响应信号NMI,非屏蔽中断请求信号RESET,系统复位信号DEN,数据允许信号DT/R,数据发送/接收控制信号HOLD,总线保持请求信号输入HLDA,总线保持响应信号TEST,测试信号CLK,时钟输入信号VCC(+5V),GND(2)8255A可编程并行接口芯片:Intel 8086/8088 系列的可编程外设接口电路(Programmable Peripheral Interface)简称 PPI,型号为8255(改进型为8255A及8255A-5),具有24条输入/输出引脚、可编程的通用并行输入/输出接口电路。

它是一片使用单一+5V电源的40脚双列直插式大规模集成电路。

8255A的通用性强,使用灵活,通过它CPU可直接与外设相连接。

8255A可为8086微处理器与外部设备之间提供并行输入/输出的通道。

通过编程可以设置芯片的工作方式,并行接口是在多根数据线上,以数据字节/字与I/O设备交换信息。

8255A由数据总线缓冲器、读/写控制逻辑电路、A组和B组控制电路以及数据端口A、B和C组成。

数据总线缓冲器是8255A与系统数据总线的接口,CPU输入输出的数据、CPU输出的控制字和外设的状态信息都是通过这个缓冲器传送的。

读/写控制逻辑电路把CPU的控制命令或输出数据送至相应的端口,把外设的状态信息或输入数据通过相应的端口送至CPU。

数据端口PA和PB都包含一个8位输出锁存器/缓冲器和一个8位输入锁存器,(3)74HC373:其中D0-D7为数据输入端,Q0-Q7为输出端。

当三态允许控制端OE为低电平时,Q0-Q7为正常逻辑状态,可用来驱动负载或总线,当OE为高电平时,Q0-Q7成高阻态,不驱动总线。

当锁存允许端LE为高电平时,Q随数据D而变,当LE为低电平D被锁存在已建立的数据电平。

(4)74HC138:74HC138是一款高速CMOS器件,74HC138引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC138译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC138特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高,74HC138为反相输出,它按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器。

六.程序流程图:七.程序清单DATA SEGMENTNUM1 DB 03H DUP(0) NUM DB 03H DUP(0) DATA ENDSSTACK SEGMENTDW 100 DUP(0)STACK ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA,SS:STACK PORTA EQU 30HPORTB EQU 32HPORTC EQU 34HPORT8255 EQU 36HMAIN PROC FARSTART: MOV AX,DATAMOV DS,AXMOV DX,PORT8255MOV AL,81HOUT DX,ALLOPL: XOR AH,AHCALL KEYCMP AH,00HJZ LOPLCMP AL,0FHJZ CCCLCMP AL,0AHJZ LOPLJNC LOPLOUT 32H,ALLOPL2:LEA SI,NUMMOV [SI],ALPUSH AXLOPL1: XOR AH,AHCALL KEYCMP AH,00HJZ LOPL1CMP AL,0FHJZ CCCLCMP AL,0AHJZ XX1CMP AL,0BHJZ XX2CMP AL,0CHJZ XX3DCMP AL,0DHJZ XX4DJMP LOPL1 CCCL: MOV AL,00HOUT 32H,ALJMP LOPLXX3D: CALL XX3XX4D: CALL XX4MAIN ENDPXX1 PROCNOP ;加LOPL3: XOR AH,AHCALL KEYCMP AH,00HJZ LOPL3CMP AL,0FHJZ CCCLCMP AL,0AHJZ LOPL3JNC LOPL3OUT 32H,ALPUSH AXLEA SI,NUMMOV [SI+1],ALLOPL4: XOR AH,AHCALL KEYCMP AH,00HJZ LOPL4CMP AL,0FHJZ CCCLCMP AL,0EHJZ XXX1JMP LOPL4XXX1: LEA SI,NUMMOV AL,[SI]AND AL,0FHMOV DL,[SI+1]AND DL,0FHADD AL,DLDAAOUT 32H,ALJMP LOPLXX1 ENDPXX2 PROCNOP ;减LOPL5: XOR AH,AHCALL KEYCMP AH,00HCMP AL,0FHJZ CCCLCMP AL,0AHJZ LOPL5JNC LOPL5OUT 32H,ALPUSH AXLEA SI,NUMMOV [SI+1],ALLOPL6:XOR AH,AHCALL KEYCMP AH,00HJZ LOPL6CMP AL,0FHJZ CCCL7CMP AL,0EHJZ XXX2JMP LOPL6XXX2: LEA SI,NUMMOV AL,[SI]AND AL,0FHMOV DL,[SI+1]AND DL,0FHSUB AL,DLADD AL,00HDAAOUT 32H,ALJMP LOPLCCCL7: MOV AL,00HOUT 32H,ALJMP LOPLXX2 ENDPXX3 PROCLOPL7: XOR AH,AHCALL KEY ;乘 CMP AH,00HJZ LOPL7CMP AL,0FHJZ CCCL2CMP AL,0AHJNC LOPL7OUT 32H,ALPUSH AXLEA SI,NUMMOV [SI+1],ALLOPL8: XOR AH,AHCALL KEYCMP AH,00HJZ LOPL8CMP AL,0FHJZ CCCL3CMP AL,0EHJZ XXX3JMP LOPL8XXX3: LEA SI,NUMMOV AL,[SI]AND AL,0FHMOV DL,[SI+1]AND DL,0FHMUL DLAAMMOV CL,4SAL AH,CLOR AL,AHOUT 32H,ALJMP LOPLCCCL2: MOV AL,00HOUT 32H,ALJMP LOPLCCCL3: MOV AL,00HOUT 32H,ALJMP LOPLXX3 ENDPXX4 PROC ;除LOPL9: XOR AH,AHCALL KEYCMP AH,00HJZ LOPL9CMP AL,0FHJZ CCCL5CMP AL,0AHJZ LOPL9JNC LOPL9OUT 32H,ALPUSH AXLEA SI,NUMMOV [SI+1],AL LOPL10: XOR AH,AHCALL KEYCMP AH,00HJZ LOPL10CMP AL,0FHJZ CCCL4CMP AL,0EHJZ XXX4JMP LOPL10 XXX4: LEA SI,NUMMOV AL,[SI] AND AL,0FHMOV BL,[SI+1] AND BL,0FHAND AX,000FH DIV BLOUT 32H,ALJMP LOPL CCCL4: MOV AL,00H OUT 32H,ALJMP LOPL CCCL5: MOV AL,00H OUT 32H,ALJMP LOPLXX4 ENDPKEY PROCNOPLEA SI,NUM1MOV AL,0EHOUT 30H,ALIN AL,34HCMP AL,07HJZ LL7CMP AL,0BHJZ LL8CMP AL,0DHCMP AL,0EH JZ LDIVSS1: MOV AL,0DH OUT 30H,AL IN AL,34H CMP AL,07H JZ LL4CMP AL,0BH JZ LL5CMP AL,0DH JZ LL6CMP AL,0EH JZ LMUL SS2: MOV AL,0BH OUT 30H,AL IN AL,34H CMP AL,07H JZ LL1CMP AL,0BH JZ LL2CMP AL,0DH JZ LL3CMP AL,0EH JZ LSUB SS3: MOV AL,07H OUT 30H,AL IN AL,34H CMP AL,07H JZ SCLCCMP AL,0BH JZ LL0CMP AL,0DH JZ LEQUCMP AL,0EH JZ LADDJMP KCLC LDIV: MOV AL,0DH JMP LCLCLL0: MOV AL,00H JMP LCLCLL1: MOV AL,01H JMP LCLCLL2: MOV AL,02HLL3: MOV AL,03H JMP LCLCLL4: MOV AL,04H JMP LCLCLL5: MOV AL,05H JMP LCLCLL6: MOV AL,06H JMP LCLCLL7: MOV AL,07H JMP LCLCLL8: MOV AL,08H JMP LCLCLL9: MOV AL,09H JMP LCLC LADD: MOV AL,0AH JMP LCLC LSUB: MOV AL,0BH JMP LCLC LMUL: MOV AL,0CH JMP LCLCLEQU: MOV AL,0EH JMP LCLC SCLC: MOV AL,0FH LCLC: MOV [SI],AL MOV AH,01H KCLC:RETKEY ENDPCODE ENDSEND START八.程序运行结果分析与预测:连接完线路图后把编好的程序关联到8086CPU中进行运行调试,肯定可以实现加减乘除运算,例如3+8=11,通过按键分别输入“3”, “+”,“8”, “=”后,LED灯上将显示出“11”.能实现清零操作,当按下“ON/C”时,LED上显示“00”。