二级运算放大电路版图设计

两级运算放大器的版图设计(版图设计实验报告)

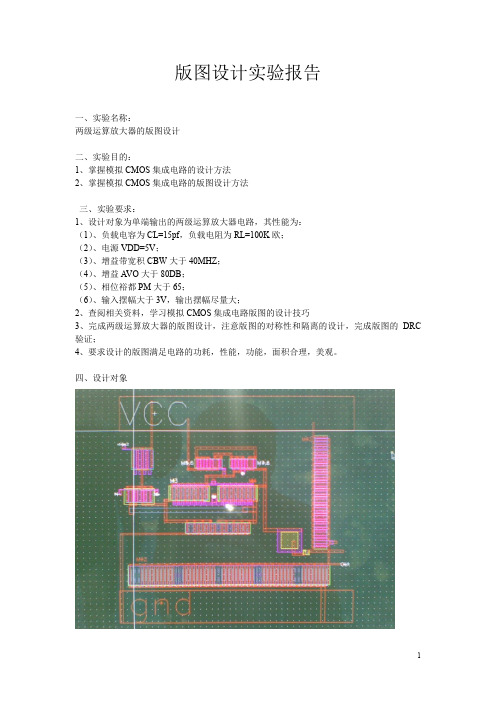

版图设计实验报告一、实验名称:两级运算放大器的版图设计二、实验目的:1、掌握模拟CMOS集成电路的设计方法2、掌握模拟CMOS集成电路的版图设计方法三、实验要求:1、设计对象为单端输出的两级运算放大器电路,其性能为:(1)、负载电容为CL=15pf,负载电阻为RL=100K欧;(2)、电源VDD=5V;(3)、增益带宽积CBW大于40MHZ;(4)、增益AVO大于80DB;(5)、相位裕都PM大于65;(6)、输入摆幅大于3V,输出摆幅尽量大;2、查阅相关资料,学习模拟CMOS集成电路版图的设计技巧3、完成两级运算放大器的版图设计,注意版图的对称性和隔离的设计,完成版图的DRC 验证;4、要求设计的版图满足电路的功耗,性能,功能,面积合理,美观。

四、设计对象仿真后MOS管的宽长比如下图:备注:电阻:R1为180欧电容:C1为2.62pf五、实验步骤1、观察模型文件(.SCS文件)或通过对CMOS管点单电路的DC分析并查看MOS管的直流工作点参数,得到PMOS,NMOS的基工艺参数(TOX,Cox,VthN,VthP等)2、确定具体的设计方案3、在schematic中画出电路图4、开始设计电路的版图5、修改版图,使之通过DRC验证6、优化版图使面积合理、美观六、实验结果面积:120*180=22680(um)七、实验心得第二次做版图设计,相较上次的实习难度提升了些许,最关键的是即将步入工作的我们重拾了那些被淡化和遗忘的知识,重新刷新脑子,和团队紧密合作,细致的分工,相互的监督和检验,我们一步步的完成脑中的想法,在有限的时间内完成老师的作业,这让我们感觉就是在工作间里。

然而每一步的前进总是让我们明白我们的不足和问题,知识的模糊,对版图设计的有限了解,粗糙的设计,迟钝的软件操作,这些都让我们反思了很久也想了很多,无论如何,经过了再一次的版图设计,我还是能够感到自己的进步,无论是对知识的理解还是对学习知识的渴求,而后者让我感到格外珍贵。

两级运算放大器设计文档-20150116

点,使补偿后的运放只有一个极点。这就要求:

fZ

1

2

CC

(

g

m

1 6

RZ

)

gm6

2 CL

RZ

CC CL gm6 CC

(b) 消去零点。即将零点移至无穷远处。这就要求

gm6Rz 1

(c) 将零点移到左半平面略大于 GBW 的位置。一般为 1.2 倍 GBW 处(why?), 原因:1,2GBW 处的零点既不影响幅度特性,又能很好地贡献相位裕度。

=

������������ ������������

=

������������1 2������������������

=

������������1 ������������1

������������1

1 2������������������

(5)

B 相位补偿分析:

如图 1 电路,加入一个与 Cc 的串联电阻之后,电路的零点变为:

第六章 仿真

6.1 直流增益、带宽和相位裕度

结果说明

A1 A2 增益 3dB带宽 增益带宽积 相位裕度

16.64 20.8 50.8dB 4.2MHZ 1.88GHZ 62deg

仿真结果图示

6.2 偏置电路设计:

注:此电路没有做输入偏置,后续工作应做一个 342mv 的偏置供输入。

放大器 symbol 测试

W 502.392u 502.392u 155.416u 155.416u 342.083u 104.154u 849.32u 306.99u

5.4 计算&仿真参数

DC参数 Vout Vp Vgs1 Vgs2 id1 id2

两级CMOS运算放大器的前仿-版图及后仿

的前仿图形 (dc=0V)

图23

1 CM RR

的后仿图形 (dc=0V2)3

两级CMOS运算放大器的后仿

图24

1 PSRR

和1 PSRR

前仿图形(dc=0V)

24

两级CMOS运算放大器的后仿

图25

1 PSRR

和1 PSRR

后仿图形(dc=0V)

25

两级CMOS运算放大器的后仿

表4 设计要求、Cadence前仿结果、HSPICE仿真结果

参数 设计要求 Cadence前仿结果 HSPICE前仿结果 HSPICE后仿结果

ICMR 1V~2V

1 V2.4 V

0 .9 9 7 V2 .3 8 V 0 .9 9 7 V2 .3 5 V

V out

2V

2 .0 4 7 V2 .0 9 V 2 .4 4 V2 .4 2 V 2 .4 7 V2 .4 2 V

• 为了拓宽3 dB带宽,应该使用调零电阻补偿 。 • 软件的使用方法,版图的设计规则,某些程序

的语法。

27

心得体会

• 仿真可以对理论计算进行很好的验证。 • 实训中存在很多问题,需要进一步学习。 • 实训可以检验自己的不足,丰富自己的

实际经验。

28Biblioteka 谢谢!29感谢您的阅读收藏,谢谢!

两级CMOS运算放大器的 设计

1

两级CMOS运算放大器的设计

• 两级CMOS运算放大器的前仿 • 两级CMOS运算放大器的版图 • 两级CMOS运算放大器的后仿 • 存在的问题 • 心得体会

2

两级CMOS运算放大器的前仿

表1 设计要求

VDD C L

V o u t ICMR S R

2两级放大电路原理图的绘制

新课教学(2)保存项目;执行菜单命令[File]/[Save Project],在弹出的对话框中,选择保存路径,在文件名栏中键入“放大电路”,文件类型为Project file(*。

prjpcb),单击“保存"即可(3)关闭项目;执行【文件】--【关闭】即可.(4)新建原理图文件,执行【文件】--【创建】--【原理图】菜单命令;或用鼠标选中项目名称,在右键快捷菜单中执行【追加新文件到项目中】--【原理图Schematic】菜单命令。

表1—1 Protel dxp 文件类型二、自由文件(Freedocuments)1、创建自由文件2、项目中的文件转换为自由文件3、将自由文件添加到项目中三、原理图图纸设置和绘制步骤执行【设计】—-【文档选项.。

.】菜单命令。

1、图纸大小设置2、图纸方向设置3、原理图网格设置4、图纸尺寸单位设置5、文档参数设置绘制步骤见图1-2任务驱动教学法电阻元件Res开头电感元件Inductor电容元件Cap开头变压器Transfer三极管NPN或PNN 开关元件SW二极管Diode 串行接口Connector数码管Dpy开头外接接口Header电解电容Cap Pol 耳机接口Phonejack六、放置元件1、放置元件2、旋转元件:鼠标左键按住元件不放,按空格键一次,转向90度。

3、移动、复制元件。

4、元器件的阵列粘贴。

七、修改元件名称及参数八、原理图工作窗口的显示鼠标拖曳原理图图纸,【PgUp】【PgDn】放大缩小图纸,以方便绘制修改元件.中心位置定位显示,用【Home】键;更新用【End】键。

九、导线的绘制与移动在工具栏中单击按钮,进入绘制导线状态.(快捷键PW);连接时元件引脚上出现一个红色的十字型光标,表示该点可以具备电气属性,即导线与元件导通。

修改导线属性,如宽度、颜色等,在放置导线时单击【Tab】键即可。

十、导线的节点。

实验一 二级运放

(1)准备 (2)加热被焊件 (1) 准备 ( 图 a): 准备好焊锡丝和烙铁。此时特别 (3) 熔化焊料(图c): 当焊件加热到能熔化焊料的温度 强调的是烙铁头要保持干净。 后将焊丝置于焊点,焊料开始熔化。 (2) 加热焊件 (图 b): 将烙铁接触焊接点,首先要 (4) 移开焊锡 (图 d): 当熔化一定量的焊锡后将焊锡 丝移开。 注意保持烙铁加热焊件各部分,例如印制板上引 (5) 移开烙铁(图e): 当焊锡完全润湿焊点后移开烙 线和焊盘都使之受热。 铁,注意移开烙铁的方向应该是大致45°的方向。

万能板(洞洞其板上布满 标准的IC间距(2.54mm)的圆型独立的焊 盘,看起来整个板子上都是小孔,所以也 俗称为“洞洞板”。相比专业的PCB印刷电 路板,洞洞板具有成本低、使用方便、扩 展灵活等特点。也叫万能电路板,万用板、 实验板

万能板的使用

2.五步焊接法

NE5532引脚图

由原理图画接线图(纸上)

• 1、先画ne5532的引脚图(实物),根据原 理图,按照ne5532的引脚,画出与外部的 接线。 • 2、画出其他部分,如,电源,地线等 • 3、整理原理图,即使接线图符合电路板, 使布线简单、整洁、易焊接等。

实验步骤

• • • • • 1、根据原理图在纸上画出接线图 2、根据万能板的形状、大小调节接线图。 3、在万能板上安装元器件 4、焊接元器件 5、走线:用导线在万能板上根据接线图, 将每个元器件接线。

万能板洞洞板万能板简介一种通用设计的电路板通常其板上布满标准的ic间距254mm的圆型独立的焊盘看起来整个板子上都是小孔所以也俗称为洞洞板

实验一 运算放大器组成的二级 放大电路

2014年4月25

一、原理图

NE5532资料

• 1、实物图

两级运算放大器设计

运算放大器的仿真分析结果如下。

静态工作点:(1)运放的输入失调电压仿真通过仿真运放的直流传输特性是测量其输入失调电压。

运放的电源电压为5V,在开环状态下,其反相端接2.5V直流电压,同相端加从2.45V到2.55V的直流扫描电压,做DC 仿真得到的运放的直流传输特性如图7.19所示,其输入失调电压为3mV,满足了通用运放失调电压的要求。

图7.19 运放的直流传输特性分析(2)运放的共模输入范围运放的共模输入范围是运放的输入输出跟随特性。

运放的电源为5V,运放的反相端和输出相连,构成缓冲器;同相端加直流扫描从0到5V,经仿真得到的运放输入输出跟随特性如图7.20所示,其输入共模电压范围从0.1V到4.6V,满足了设计指标的要求。

图7.20 运放的共模输入范围(3)运放的输出电压摆幅特性运放的输出电压摆幅特性是仿真运放的输出电压最大值和最小值。

运放的输出电压摆幅特性仿真电路如图7.21所示,其反相比例放大器增益为10。

Vin1M10M+2.5V +5VV out图7.21 运放的输出电压摆幅特性仿真电路正输入端接2.5V的直流电压,V in输入端加从0到5V的直流扫描电压,经仿真得到的运放输出电压摆幅特性见图7.22,运放的输出电压摆幅是从0到5V,满足了运放指标对输出电压摆幅的要求。

图7.22 运放的输出电压摆幅特性(4)运放的小信号相频和幅频特性运放的小信号相频和幅频特性是仿真运放的开环小信号放大倍数及其相位随频率的变化趋势,从而得到运放的相位裕度和单位增益带宽指标,并进一步鉴别运放的放大能力、稳定性和工作带宽。

运放的输出端接2pF的负载电容,电源电压为5V,共模输入电压为2.5V,差模输入幅度为1V的交流信号,即两输入端的输入交流信号相位相反。

做交流小信号分析,可以得到运放的小信号相频和幅频特性如图7.23所示。

从仿真结果可以看出,运放采用RC补偿,在满足单位增益带宽的同时,能很好的调节相位裕度。

二级密勒补偿运算放大器设计(西安邮电大学)

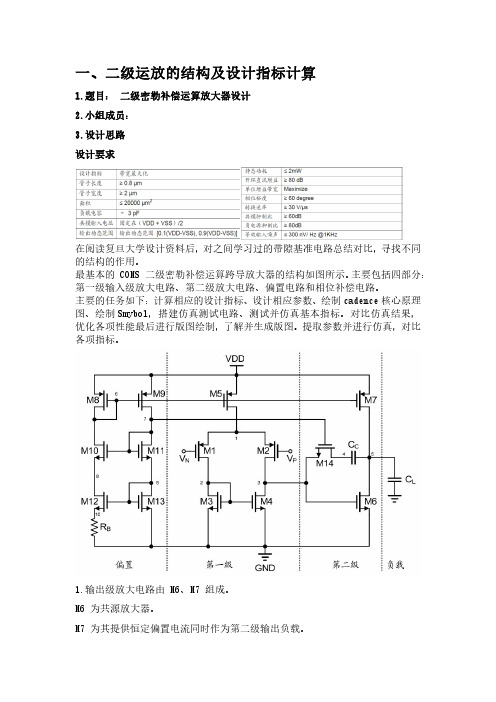

一、二级运放的结构及设计指标计算1.题目:二级密勒补偿运算放大器设计2.小组成员:3.设计思路设计要求在阅读复旦大学设计资料后,对之间学习过的带隙基准电路总结对比,寻找不同的结构的作用。

最基本的COMS二级密勒补偿运算跨导放大器的结构如图所示。

主要包括四部分:第一级输入级放大电路、第二级放大电路、偏置电路和相位补偿电路。

主要的任务如下:计算相应的设计指标、设计相应参数、绘制cadence核心原理图、绘制Smybol,搭建仿真测试电路、测试并仿真基本指标。

对比仿真结果,优化各项性能最后进行版图绘制,了解并生成版图。

提取参数并进行仿真,对比各项指标。

1.输出级放大电路由M6、M7组成。

M6为共源放大器。

M7为其提供恒定偏置电流同时作为第二级输出负载。

M14和Cc构成相位补偿电路。

因为M14工作在线性区,通过m14的直流电流为0,所以M14可等效为一个电阻,m14与电容Cc构成RC密勒补偿2.输出级放大电路由M6、M7组成。

M6为共源放大器。

M7为其提供恒定偏置电流同时作为第二级输出负载。

M14和Cc构成相位补偿电路。

因为M14工作在线性区,通过m14的直流电流为0,所以M14可等效为一个电阻,m14与电容Cc构成RC密勒补偿3.偏置电路由M8~M13和RB组成。

M8和M9宽长比相同。

M12与M13相比,源极加入了电阻RB,组成微电流源,产生电流IB。

对称的M11和M12构成共源共栅结构,减小沟道长度调制效应造成的电流误差。

在提供偏置电流的同时,还为M14栅极提供偏置电压。

M1和M2为第一级差分输入跨导级,将差分输入电压转换为差分电流;M3和M4为第一级负载,将差模电流恢复为差模电压;M6为第二级跨导级,将差分电压信号转换为电流;M7再将此电流信号转换为电压输出。

4.等效电路图5.静态功耗一旦电源电压确定,静态功耗取决于各支路静态电流总和。

考察各路电路,可以知道,此运放的静态功耗为6.单位增益带宽单位增益带宽是运放最重要的指标之一,它定义为当运放增益为1时,所加输入信号的频率,7.共模抑制比共模抑制比的定义为其中Adm是差模增益,Acm是共模增益。

二级运算放大电路版图设计

目录1前言1 2二级运算放大器电路1电路结构 1 设计指标 2 3 Cadence仿真软件3schematic原理图绘制 3 生成测试电路 3电路的仿真与分析 444版图绘制5677DRC & LVS版图验证 8 DRC验证8LVS验证8 4结论95参考文献9摘要本文利用cadence软件简述了二级运算放大器的电路仿真和版图设计。

以传统的二级运算放大器为例,在ADE电路仿真中实现工艺,输入直流电源为5v,直流电流源范围27~50uA,根据电路知识,设置各个MOS管合适的宽长比,调节弥勒电容的大小,进入stectre仿真使运放增益达到40db,截止带宽达到80MHz和相位裕度至少为60。

版图设计要求DRC验证0错误,LVS验证使电路图与提取的版图相匹配,观看输出报告,要求验证比对结果一一对应。

关键词:cadence仿真,设计指标,版图验证。

AbstractIn this paper, the circuit simulation and layout design of two stage operational amplifier are briefly described by using cadence software. In the traditional two stage operational amplifier as an example, the realization of technology in ADE circuit simulation, the input DC power supply 5V DC current source 27~50uA, according to the circuit knowledge, set up each MOS tube suitable ratio of width and length, the size of the capacitor into the regulation of Maitreya, the simulation of stectre amplifier gain reaches 40dB, the cut-off bandwidth reaches 80MHz and the phase margin of at least 60.. The layout design requires DRC to verify 0 errors, and LVS validation makes the circuit map matching the extracted layout, viewing the output report, and requiring verification to verify the comparison results one by one.Key words: cadence simulation, design index, layout verification.1前言近几年来,人们已投入很大力量研究版图设计自动化,计算机辅助设计方法学在给定所需功能行为描述的数字系统设计自动化方面已经非常成功。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1前言12二级运算放大器电路 12.1电路结构 12.2设计指标 23 Cadence仿真软件 33.1 schematic原理图绘制 33.2 生成测试电路 33.3 电路的仿真与分析 43.1.1直流仿真 43.1.2交流仿真 43.4 版图绘制 53.4.1差分对版图设计 63.4.2电流源版图设计 73.4.3负载MOS管版图设计 73.5 DRC & LVS版图验证 83.5.1 DRC验证 83.5.2 LVS验证 8 4结论 95参考文献 9本文利用cadence软件简述了二级运算放大器的电路仿真和版图设计。

以传统的二级运算放大器为例,在ADE电路仿真中实现0.16umCMOS工艺,输入直流电源为5v,直流电流源范围27~50uA,根据电路知识,设置各个MOS管合适的宽长比,调节弥勒电容的大小,进入stectre仿真使运放增益达到40db,截止带宽达到80MHz和相位裕度至少为60。

版图设计要求DRC验证0错误,LVS验证使电路图与提取的版图相匹配,观看输出报告,要求验证比对结果一一对应。

关键词:cadence仿真,设计指标,版图验证。

AbstractIn this paper, the circuit simulation and layout design of two stage operational amplifier are briefly described by using cadence software. In the traditional two stage operational amplifier as an example, the realization of 0.16umCMOS technology in ADE circuit simulation, the input DC power supply 5V DC current source 27~50uA, according to the circuit knowledge, set up each MOS tube suitable ratio of width and length, the size of the capacitor into the regulation of Maitreya, the simulation of stectre amplifier gain reaches 40dB, the cut-off bandwidth reaches 80MHz and the phase margin of at least 60.. The layout design requires DRC to verify 0 errors, and LVS validation makes the circuit map matching the extracted layout, viewing the output report, and requiring verification to verify the comparison results one by one.Key words: cadence simulation, design index, layout verification.1前言近几年来,人们已投入很大力量研究版图设计自动化,计算机辅助设计方法学在给定所需功能行为描述的数字系统设计自动化方面已经非常成功。

希望用以代替设计师的一部分劳动。

但这并不适用于模拟电路设计。

较复杂的场合,有些程序的应用遇到了阻力,需要人工干预帮助解决问题。

因此,仔细研究模拟电路的设计过程,熟悉那些提高设计效率、增加设计成功机会的原则是非常必要的。

人工设计得到的器件版图密度一般高于用自动化版图设计和布线程序所得到的密度,因而人机交互式版图设计和布线程序得到了广泛的应用。

我们这次做的仅是基本方法,对于比较复杂的电路版图设计则不仅需要很多诸如图论在内的数据结构算法的知识应用,而且多年的电路版图设计经验也同样是非常重要的。

2二级运算放大器电路运算放大器(简称运放)是许多模拟系统和混合信号系统中的一个完整部分。

各种不同复杂程度的运放被用来实现各种功能:从直流偏置的产生到高速放大或滤波。

运算放大器的设计可以分为两个较为独立的两个步骤。

第一步是选择或搭建运放的基本结构,绘出电路结构草图。

一般来说,决定好了电路结构以后,便不会更改了,除非有些性能要求必须通过改变电路结构来实现。

为了满足运放的交流和直流要求,所有管子都应被设计出合适的尺寸。

然后在手工计算的基础上,运用计算机模拟电路可以极大的方便对电路进行调试和修改。

2.1 电路结构传统的二级运算放大电路的结构主要包括四部分:第一级输入级放大电路,第二级放大电路,偏置电路和相位补偿电路。

电路图如图2.1所示。

图2.1 二级运算放大器电路2.2 设计指标表1.1 二级运算放大器设计指标 (1)电压放大倍数二级运算放大器相比于共源共栅运放最大的优势就是既能提供高增益,又能提供打的摆幅。

根据电路知识,我们可求得第一级和第二级增益,而电路的整体增益是两部分增益相乘的结果。

由此可知,二级运算放大器可以提供高的增益。

)()(27666766242514211λλλλ+-=+-=+-=+-=I g g g g A I g g g g A m ds ds m V m ds ds m V 第二级增益:第一级增益: (2)单位增益带宽(GWB )单位增益带宽是指运放增益为1时,电路所输入信号的频率,这是电路所能正常工作的最大频率,它是运放重要的指标之一,其中角频率的表示方法如下:Cc GB m 1g =单位增益带宽: (3)相位裕度电路有至少四个极点和两个零点,假定 z2、p3、p4 以及其它寄生极点都远大于 GBW ,若不考虑零点z1,仅考虑第二极点p2,那么这是一个典型的两极点决定的系统。

为保证系统稳定,通常要求有 63°左右的相位裕度,即保持频率阶跃响应的最大平坦度以及较短的时间响应。

但在考虑 z1之后, 这个右半平面 (RHP ) 的零点在相位域上相当于左半平面 (LHP )的极点,所以相位裕度会得到恶化。

同时如果为了将两个极点分离程度增大,则补偿电容Cc 就要增大,这也会使得零点减小,进一步牺牲相位裕度。

(4)最终设计参数:m1 pmos w=32u l=1.6um2 pmos w=32u l=1.6um3 nmos w=4u l=1.6um4 nmos w=4u l=1.6um5 pmos w=32u l=1.6um6 pmos w=32u l=1.6um7 pmos w=20u l=1.6um8 nmos w=8u l=1.6uC 0.15PFR1 0.1k直流电源 5v交流电压源 1v静态电压源 2.5v直流电流源 35uA3 cadence软件仿真3.1 schematic原理图绘制根据上述设计好的指标,在schemetic中绘制电路图,其中一点值得注意的是这里所用到的MOS管宽长都比较大,所以采用将各个管拆分成多个管并联的方式进行电路图绘制,这样还能减少栅极上的寄生电阻。

电路图检测没有错误后,然后生成符号,如图 3.2所示。

图3.1 二级运算放大电路schematic原理图图3.2 二级运算放大器生成符号3.2 生成测试电路仿真的电路图连接方式有两种,一种是利用上述电路检查并保存后建立symbol模型,在此模型的基础上进行直流电源,直流电流源以及交流源的连接如图。

另一种可以直接在电路图的基础上添加激励源然后进行仿真;两种连接方式如下图。

图3.3 二级运算放大电路生成测试图(1)图3.4 二级运算放大电路生成测(2)3.3 电路的仿真与分析对于模拟设计环境ADE 来说,默认的仿真器是 spectre ,这里直接采用 spectre 对设计进行仿真和分析。

3.3.1直流仿真为了让运放正常工作,保证8个MOS 管工作饱和区,要求VTH VGS VDS ->,同时过驱动电压不能太大,否则沟道长度调制效应明显,而且输出摆幅受到限制。

其仿真报告如下:图3.5 直流仿真 图3.6 仿真报告 通过一一验证检查,报告结果显示8个管子均处于饱和状态,这说明二级运算放大器可以正常放大工作,在此基础上接下来可以进行交流仿真的工作。

3.3.2交流仿真根据增益的基本公式inout v V V A =,要想观察二级运放的增益特性曲线,我们可以使输入交流电压为1V ,通过交流仿真得到输出电压与频率的关系曲线,那么该曲线就是我们想 要的增益特性曲线。

图像如图所示:图3.7为二级运算放大器的增益仿真,运放增益达到40db ,截止频率接近80MHz ,这一结果符合题目要求。

图3.8为二级运算放大器的相位仿真,通常相位裕度达到60度时,电路比较稳定,由于各种原因,本次实验结果中显示在频率接近80MHz ,相位并未 达到60度。

图3.7 增益仿真图3.8 相位仿真3.4 版图绘制在二级运算放大器中,我们要求输出差分对管m1和m2对称,电流源m5、m6和m7对称,有源负载m3和m4对称,其中的电阻和电容不要求对称性,而且对电容的上下极板的接法没有要求。

图3.9是二级运算放大器的整体版图设计,因为考虑到LVS验证并不比对各个MOS管的宽长比,所以本次版图每个MOS管的宽长比并没有与电路图MOS管一一对应。

本次版图设计我们主要考虑的是MOS管的对称性,所以对各个部分的MOS管的对称问题上进行了详细的说明。

图3.9 二级运算放大器版图绘制3.4.1差分对版图设计设计规则:(1)为了保证差分对管m1和m2的对称性,采用共质心设计将m1拆分成m1a和m1b,将m2拆分成m2a和m2b,交叉放置。

(2)如果输入管宽长比较大,将m1a、m1b、m2a和m2b管拆分成多个管并联的方式,还能减少栅极上的寄生电阻。

(3)差分对管m1和m2为PMOS管,为保证两个管良好的对称性,最后在周围布上一圈N阱接触。

(4)为提高差分对管m1和m2结构的匹配性,差分对管端的连线尽量在m1和m2之间通过。

(5)为了保证运算放大器的对称性,运算放大器中所有晶体管的栅极都要朝着同一个方向。

(6)输入引线一定要尽量短,而且尽量用最上级层金属设计,且输入输出引线尽量远离尽量不要交叉。

图3.10 差分对版图设计3.4.2电流源版图设计二级运放电器的电流源由m5、m6和去m7构成,由于一般电流源要求几个MOS管之间的对称,因此一般采用叉指结构实现,假设电流源m6、m5和去m7 的宽长的比例为1:2:4,将3个MOS拆分,也是重点考虑m5和m7管的对称性的高优先级,将m5和m7管利用叉指结构方式设计,属于高度对称版图设计。