mcos运算放大器版图的设计--毕业设计

两级运算放大器的版图设计(版图设计实验报告)

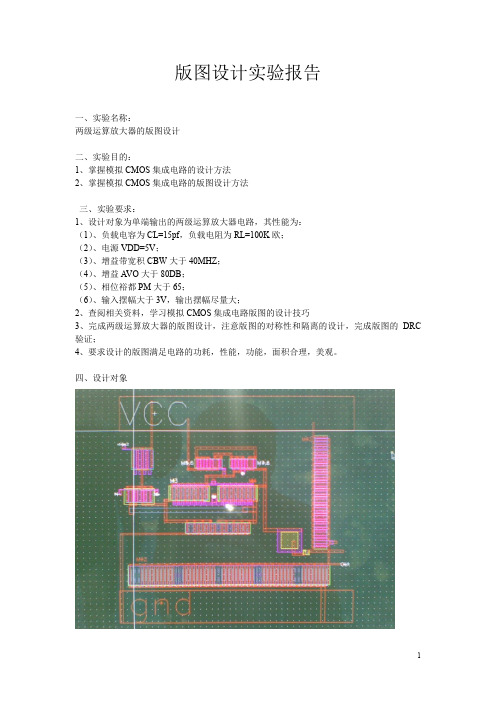

版图设计实验报告一、实验名称:两级运算放大器的版图设计二、实验目的:1、掌握模拟CMOS集成电路的设计方法2、掌握模拟CMOS集成电路的版图设计方法三、实验要求:1、设计对象为单端输出的两级运算放大器电路,其性能为:(1)、负载电容为CL=15pf,负载电阻为RL=100K欧;(2)、电源VDD=5V;(3)、增益带宽积CBW大于40MHZ;(4)、增益AVO大于80DB;(5)、相位裕都PM大于65;(6)、输入摆幅大于3V,输出摆幅尽量大;2、查阅相关资料,学习模拟CMOS集成电路版图的设计技巧3、完成两级运算放大器的版图设计,注意版图的对称性和隔离的设计,完成版图的DRC 验证;4、要求设计的版图满足电路的功耗,性能,功能,面积合理,美观。

四、设计对象仿真后MOS管的宽长比如下图:备注:电阻:R1为180欧电容:C1为2.62pf五、实验步骤1、观察模型文件(.SCS文件)或通过对CMOS管点单电路的DC分析并查看MOS管的直流工作点参数,得到PMOS,NMOS的基工艺参数(TOX,Cox,VthN,VthP等)2、确定具体的设计方案3、在schematic中画出电路图4、开始设计电路的版图5、修改版图,使之通过DRC验证6、优化版图使面积合理、美观六、实验结果面积:120*180=22680(um)七、实验心得第二次做版图设计,相较上次的实习难度提升了些许,最关键的是即将步入工作的我们重拾了那些被淡化和遗忘的知识,重新刷新脑子,和团队紧密合作,细致的分工,相互的监督和检验,我们一步步的完成脑中的想法,在有限的时间内完成老师的作业,这让我们感觉就是在工作间里。

然而每一步的前进总是让我们明白我们的不足和问题,知识的模糊,对版图设计的有限了解,粗糙的设计,迟钝的软件操作,这些都让我们反思了很久也想了很多,无论如何,经过了再一次的版图设计,我还是能够感到自己的进步,无论是对知识的理解还是对学习知识的渴求,而后者让我感到格外珍贵。

测量放大器的设计与实现的毕业设计论文

测量放大器的设计姓名院系专业年级学号 2指导教师年月日独创声明本人郑重声明:所呈交的毕业论文(设计),是本人在指导老师的指导下,独立进行研究工作所取得的成果,成果不存在知识产权争议。

尽我所知,除文中已经注明引用的内容外,本论文(设计)不含任何其他个人或集体已经发表或撰写过的作品成果。

对本文的研究做出重要贡献的个人和集体均已在文中以明确方式标明。

此声明的法律后果由本人承担。

作者签名:年月日毕业论文(设计)使用授权声明本人完全了解关于收集、保存、使用毕业论文(设计)的规定。

本人愿意按照学校要求提交论文(设计)的印刷本和电子版,同意学校保存论文(设计)的印刷本和电子版,或采用影印、数字化或其它复制手段保存论文(设计);同意学校在不以营利为目的的前提下,建立目录检索与阅览服务系统,公布论文(设计)的部分或全部内容,允许他人依法合理使用。

(保密论文在解密后遵守此规定)论文作者(签名):年月日姓名性别男学院年级学号题目测量放大器的设计课题来源教师推荐课题类别应用研究选题意义(包括科学意义和应用前景,研究概况,水平和发展趋势,列出主要参考文献目录):测量放大器是一种高增益、直流耦合放大器,它具有差分输入、高输入阻抗和高共摸抑制比等特点,因此得到广泛的应用。

在工业自动控制等领域中,常需要对远离运放的多路信号进行测量,由于信号远离运放,两者地电位不统一,不可避免地长存在长线干扰和传输网络阻抗不对称引入的误差。

为了抑制干扰,运放通常采用差动输入方式,对微弱信号放大一定的倍数,内置计权网络的低噪声高增益。

但是由于远程电路传输分析复杂,通常只给出理想情况下放大器的差模增益,而难以给出其在非理想情况下的共模抑制比表达式。

几乎现阶段每个完整的电子产品中都离不开放大器,而放大器性能的提高对电子产品的功能起着重要的决定作用,所以精密运算放大器是未来发展的重大方向。

主要参考文献:[1].《模拟电子技术基础》,吴友宇主编,清华大学出版社,2009[2].《新型集成电路的应用-电子技术基础课程设计》,梁宗善主编,华中科技大学出版社[3].《电子线路设计•实验•测试》第三版,谢自美主编,华中科技大学出版社[4].实用单元电路及其应用,黄继昌、张海贵,人民邮电出版社[5].《模拟电子电路基础》,王卫东、江晓安,西安电子科技大学出版社,2003[6].《电路与电子简明教程》,王槐斌、吴建国、周国平,华中科技大学出版社,2006[7].《电子技术基础课程设计》,孙梅生等编著,高等教育出版社研究主要内容和预期结果(说明具体研究内容和拟解决的关键问题,预期结果和形式,如在理论上解决哪些问题及其价值,或应用的可能性及效果):首先要了解方案的设计与论证,其次要掌握设计原理及主要电路的参数计算,最后仿真分析。

Bi-CMOS集成运算放大器的电路分析及版图设计毕业论文

论文题目: Bi-CMOS集成运算放大器的电路分析及版图设计摘要集成运算放大器是一种重要电子元器件,在电子产品中得到广泛应用,可作为误差放大器、比较器、滤波器等。

理想的放大器应该无噪声、具有无穷大增益和输入阻抗、无穷小输出阻抗以及零失调电压等。

在这篇论文中,我本文主要研究了运算放大器电路的工作原理和版图设计,同时还了简要解了Bi-CMOS工艺步骤。

运算放大器电路主要包括输入级、偏置电路、中间级和输出级,输入信号加载到输入级并在合适的偏置下通过输出级得到放大信号。

版图设计主要是熟悉设计规则,布局布线合理美观,并要进行DRC验证和LVS 验证。

Bi-CMOS工艺可满足现代大规模集成电路对器件性能的要求,特别适用于高压和大电流的功率电路,在今后的高性能集成电路中有很大的发展潜力。

通过本次毕业设计,我完成了一个增益为86dB,输出共模范围为3.5V,失调电压为6.5mV,摆率较小的放大器电路设计。

绘制出了放大器的版图,并且通过了进行DRC验证和LVS验证。

关键词:放大器,电路,版图,工艺Subject: Analysis and layout design of CMOS integrated OPAbstractIntegrated operational amplifier is an important electronic components, it is used in electronic applications is very extensive currently, for example, it can be used as amplifiers, comparators, filters, etc. The ideal amplifier should without noise, has infinite gain and input impedance, infinite output impedance and zero offset voltage.In this paper, I mainly study the works of the op amp circuit principle and layout design, and also study briefly the solution of the Bi-CMOS process steps. The op amp circuit including the input stage, bias circuit, the middle stage and output stage. The input signal is loaded into the input stage and output stage amplifies the signal in the right bias. Layout design main is familiar with the design rules, the layout wiring reasonable and beautiful, and must carry on the DRC validation and LVS verification. Bi-CMOS technology to meet the requirements of modern LVSI device performance, especially suitable for high voltage and high current power circuit, there is great potential in future high performance integrated circuits.By the graduation project, I completed a gain of 86dB; the output common-mode range is 3.5V, the offset voltage of 6.5mV, smaller slew rate amplifier circuit design. Map out the territory of the amplifier, and through the DRC verification and LVS verification.Keywords: Amplifier, Circuit, Layout, Process毕业设计(论文)原创性声明和使用授权说明原创性声明本人郑重承诺:所呈交的毕业设计(论文),是我个人在指导教师的指导下进行的研究工作及取得的成果。

CMOS运算放大器版图设计毕业论文

CMOS运算放大器版图设计毕业论文目录前言 (5)第1章绪论 (6)1.1 课题背景 (6)1.1.1 研究背景 (6)1.1.2研究容 (7)1.2 电路设计流程 (8)1.3 主要工作以及任务分配 (10)1.3.1主要工作 (10)1.3.2 任务分配 (10)第2章版图基础知识 (11)2.1 版图的设计简介 (11)2.1.1 版图的概念 (11)2.1.2 版图中层的意义 (11)2.2 CMOS工艺技术 (14)2.2.1概述 (14)2.2.2 CMOS工艺的一些主要步骤 (15)2.2.3 CMOS制造工艺的基本流程 (16)2.3 设计规则 (18)2.4 MOS集成运放的版图设计 (22)第3章 CMOS运算放大器简介 (23)3.1 概述 (23)3.2两级CMOS运算放大器的优点 (24)3.3 两级运算放大器原理简单分析 (24)第4章 CMOS运算放大器的仿真 (27)4.1 概述 (27)4.2 MOS运算放大器技术指标总表 (27)4.3仿真数据 (29)4.3.1 DC分析 (29)4.3.2测量输入共模围 (30)4.3.3 测量输出电压围 (31)4.3.4 测量增益与相位裕度 (33)4.3.5 电源电压抑制比测试 (34)4.3.6 运放转换速率和建立时间分析 (36)4.3.7 CMRR的频率响应测量 (38)第5章算放大器版图设计 (40)5.1 Cadence使用说明 (40)5.2 版图设计 (42)5.3 CMOS运放版图 (43)第6章总结 (44)参考文献 (44)致谢词 (45)外文资料原文 (45)外文资料译文 (46)第1章绪论1.1 课题背景1.1.1 研究背景运算放大器(简称运放)是具有很高放大倍数的电路单元。

在实际地电路中,通常结合反馈网络共同组成某种功能模块。

由于早期应用于模拟计算机中,用以实现数字运算,故得名“运算放大器”。

毕业设计(论文)-cmos运算放大电路的版图设计[管理资料]

![毕业设计(论文)-cmos运算放大电路的版图设计[管理资料]](https://img.taocdn.com/s3/m/15f996a177232f60dccca185.png)

目录摘要 (3)第一章引言 (3)§ (3)§ CMOS 电路的发展和特点 (5)第二章CMOS运算放大器电路图 (8)§Pspice软件介绍 (8)Pspice运行环境 (12)Pspice功能简介 (12)§CMOS运算放大器电路图的制作 (14)§小结 (20)第三章版图设计 (20)§L-EDIT软件介绍 (20)§设计规则 (21)§集成电路版图设计 (24)PMOS版图设计 (24)NMOS版图设计 (27)CMOS运算放大器版图设计 (27)优化设计 (32)第四章仿真 (40)§DRC仿真 (41)§LVS 对照 (42)第五章总结 (48)附录 (50)参考文献 (52)致谢 (53)摘要介绍了CMOS运算放大电路的版图设计。

并对PMOS、NMOS、CMOS运算放大器版图、设计规则做了详细的分析。

通过设计规则检查(DRC)和版图与原理图对照(LVS)表明,此方案已基本达到了集成电路工艺的要求。

关键词:CMOS 放大器 NMOS PMOS 设计规则检查版图与原理图的对照AbstractThe layout desigen of CMOS operation amplifer is presented in this the layouts and design rules of PMOS,NMOS, and CMOS operation amplifer. The results of design rule check(DRC)and layout verification schmatic(LVS) shown that the project have already met to the needs of IC fabricated processing. Keywords: CMOS Amplifer NMOS PMOS DRC LVS第一章引言1.1 集成电路版图设计的发展现状和趋势集成电路的出现与飞速发展彻底改变了人类文明和人们日常生活的面目。

COMS运算放大器版图设计

电子科技大学实验报告课程名称集成电路原理实验四:CMOS运算放大器版图设计指导教师:于奇学生姓名:学号:201203实验地点:211楼606室实验时间:2015-6-19一、实验室名称:微电子技术实验室二、实验项目名称:CMOS运算放大器版图设计三、实验原理:1、版图设计方法的分类⑴全自动设计方法。

在版图自动设计系统数据库中,基于特定的EDA设计平台预先设计好各种电路单元结构的电路图、电路性能参数版图,并生成一系列数据文件。

⑵半自动设计方法。

在计算机上利用符号进行版图输入,符号代表不同层的版图信息,然后通过自动转换程序将符号转换成版图。

⑶手工设计方法。

人工设计版图室指利用版图的设计工具,通过编辑基本图形(如连线、矩形、多边形等)得到晶体管和其他基本元件的版图。

2、版图设计的一般步骤版图设计要同时满足电路性能要求以及相应的工艺条件要求,因此版图设计是一项复杂而精细的工作。

通常情况下版图设计分为布局、布线和验证三个阶段。

版图布局是指将设计好的功能模块合理地安排在芯片上,规划好它们的位置。

其任务是要为每个模块和整个芯片选择一个好的布局方案,在划分好模块后,一般根据其包含的器件数估计模块的面积、每个组元以及整个设计的尺寸,完成该设计的整体层次划分和区域划分,并且还要指定进行内部布线和信号连接的区域,确定每个互联区域的布线层。

由于版图布局问题比较复杂,通常把布局分成两步来完成:初始布局和改进布局。

一般情况下,在初始布局时用构造的方法给出布局问题的初始解,然后通过迭代以改进和优化布局结果。

版图布线阶段的首要任务是完成模块间的互联,其次是在完成布线的前提下进一步优化布线结果,如提高电性能、减小通孔数、缩小芯片面积等。

版图布线也是一个比较复杂的过程,通常分成两步来完成:总体布线和详细布绞。

版图验证是对布线后的版图进行DRC,电器特征检查等步骤以保证集成电路版图与电路所包含的信息完全一致,且复合工艺要求。

目前,版图验证项目主要包括DRC、电学规则检查(electrical rule check,ERC)、LVS、LPE、寄生电阻提取(parasitic resistance extraction,PRE),其中,DRC和LVS必须通过,其余视实际情况而定。

基于CMOS全差分运算放大器的全集成有源滤波器的设计_解读

天津大学硕士学位论文基于CMOS全差分运算放大器的全集成有源滤波器的设计姓名:刘莉申请学位级别:硕士专业:电路与系统指导教师:滕建辅20090501摘要随着集成电路技术和通信技术的发展,全集成有源滤波器的设计已经成为国际学术界所关注的前沿课题之一。

特别是近年来,片上系统(System…on a Chip 的发展也迫切需要解决有源滤波器的全集成问题。

本文在全面归纳总结国内外全集成有源滤波器的研究现状和发展动态的基础上,从网络综合理论出发,较系统地研究了基于信号流图模拟法的全集成有源滤波器的设计技术,利用双端接载的无源LC梯形滤波电路具有响应对元件变化灵敏度低的优点,将其作为原型滤波器,详细地推导了六阶Butterworth低通滤波器和六阶Chebyshev带通滤波器的信号流图,并实现了相应的基于反相积分器的有源RC滤波器和全差分有源RC滤波器。

并从全集成的角度出发,着重研究了作为滤波器的关键部分的全差分运算放大器的特性对全集成有源滤波器的性能的影响,在此基础上设计了一种适合于本文中所设计的全集成有源RC低通和带通滤波器的宽摆幅、低功耗的全差分运算放大器。

在设计及仿真过程中,具体的研究了运算放大器的各项性能指标对全集成有源滤波器的选频特性和稳定性的影响,给出了在滤波器设计过程中如何选择适当的运算放大器的方法。

滤波器电路采用了特许半导体(Chartered0.35urn CMOS工艺进行设计。

通过使用Cadence设计环境下的Spectre工具仿真,运放单位增益带宽达到 128MHz,相位裕度为61。

,低频增益78dB,功耗小于1.3mW,保证了全集成有源滤波器的选频特性和稳定性。

仿真结果表明,全集成有源RC低通和带通滤波器的各项性能指标都满足设计要求,并实现了滤波器的低功耗设计。

关键词:全集成有源滤波器信号流图CMOS全差分运算放大器AB STRACTWith the development of integrated circuit and telecommunication technologies, the design of full-integrated active filters has become one of the mo st important advances in analog VLSI and attracted much attention in the academic world. Particularly,in recent years,the problem,which cries for solving,isthe full.integration of the active filters,for the development of System-on-a-Chip.In this dissertation,the international and national researches status quo and the developing trends ofthe full-integrated active filters are systematically reviewed.The design technology of full-integrated active filters that based on the theory of network synthesis and signal flow graph is deeply studied.On the basis of the doubly terminated LC ladder prototype,whose magnitude response is extraordinarily insensitive to perturbations of the LC elements and to the terminating resistances,the detailed signal flow graphs of sixth-order Butterworth low-pass fiker and sixth—order Chebyshev band-pass filter are derived respectively,and the corresponding active RC filters based on inverting integrator and full-differential active RC filters are realized. Focusing on the full-integration,special emphasis is laid tO po缸OUt the influence that the performance of the fully differential operational amplifier makes to the active filters.According tO the analysis,a fully differential operational amplifier with wider unity・gain bandwidth and low power is designed for the sixth-order Butterworth low-pass filter and sixth-order Chebyshev band—pass filter inthis paper,and then a practical method for choosing the suitable operational amplifieris proposed.Filter ckcuk is designed with Chartered O.35I_tm CMOS technology ckcuit is simulated by the Spectre in Cadence,Unity-gain bandwidth of operational amplifier is reached 128MHz,phase margin is 61。

运算放大器设计

题目:运算放大器电路的设计系(部):控制系专业班:姓名:学号:指导教师:2012年1 月摘要本次设计是以 CMOS 管为基础,实现运算放大器的设计,使其达到一定的性能 要求。

关键词: CMOS 运算放大器目录错误!未定义书签。

2 参数设计 ................2.1 电路图 .......... 2.2 工艺参数 ........ 2.3 计算过程 ........ 2.3.1 计算各管子尺寸 2.3.2 仿真以修正参数错误!未定义书签。

3.1 总体网表编写过程 ............................................ 3.2 输入共模电压摆幅 ............................................ 3.2.1 测试电路 ................................................. 3.2.2 网表编写 ................................................. 3.2.3 测试结果 .................................................3.3 输出电压摆幅 ................................................3.3.1 测试电路 ................................................. 3.3.2 网表编写 ................................................. 3.3.3测试结果 ................................................. 3.4 电压增益及带宽 ............................................... 3.3.1 测试电路 ................................................. 3.3.2网表编写 ................................................. 3.3.3 测试结果 . (4)设计总结和体会5 致 谢 .................................................................................................................6参 考 文 献 .......................................................................................................1 题目要求..... 错 误!未定义书签。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

摘要集成电路掩膜版图设计是实现电路制造所必不可少的设计环节,它不仅关系到集成电路的功能是否正确,而且也会极大程度地影响集成电路的性能、成本与功耗。

本文依据基本CMOS集成运算放大电路的设计指标及电路特点,绘制了基本电路图,通过Spectre进行仿真分析,得出性能指标与格元器件参数之间的关系,据此设计出各元件的版图几何尺寸以及工艺参数,建立出从性能指标到版图设计的优化路径。

运算放大器的版图设计,是模拟集成电路版图设计的典型,利用Spectre 对设计初稿加以模拟,然后对不符合设计目标的参数加以修改,重复这一过程,最终得到优化设计方案。

最后根据参数尺寸等完成了放大器的版图设计以及版图的DRC、LVS验证。

关键词:集成电路,运算放大器,版图设计,仿真ABSTRACTIntegrated circuit layout design is an essential design part to realize circuit mask manufacturing, it is not only related to the integrated circuit to function correctly, but also can greatly affect the performance of the integrated circuit, the cost and the power consumption.Based on the basic CMOS integrated operational amplifier circuit characteristic and design target, we have rendered the basic circuit diagram, and simulation by Spectre, the simulated results are derived parameters and their relationship between determining factors, thereby defining a line with the design target domain size and processing parameters, finally we builded an optimization from the performance index to layout design .Operational amplifier IC layout design, is the design model of analog integrated circuit layout . Here we used Spectre to design draft which should be simulated, then modified which do not comply with the design goals of the parameters , repeat the process, and finally get the optimization design scheme. Finally, according to the parameters such as size finished the amplifier layout design and the DRC, LVS verification.KET WORDS: Integrated circuit, Operational amplifier, layout design, Simulation目录前言 (5)第1章绪论 (6)1.1 课题背景 (6)1.1.1 研究背景 (6)1.1.2研究内容 (7)1.2 电路设计流程 (8)1.3 主要工作以及任务分配 (10)1.3.1主要工作 (10)1.3.2 任务分配 (10)第2章版图基础知识 (11)2.1 版图的设计简介 (11)2.1.1 版图的概念 (11)2.1.2 版图中层的意义 (11)2.2 CMOS工艺技术 (14)2.2.1概述 (14)2.2.2 CMOS工艺的一些主要步骤 (15)2.2.3 CMOS制造工艺的基本流程 (16)2.3 设计规则 (18)2.4 MOS集成运放的版图设计 (22)第3章CMOS运算放大器简介 (23)3.1 概述 (23)3.2两级CMOS运算放大器的优点 (25)3.3 两级运算放大器原理简单分析 (25)第4章CMOS运算放大器的仿真 (28)4.1 概述 (28)4.2 MOS运算放大器技术指标总表 (29)4.3仿真数据 (30)4.3.1 DC分析 (30)4.3.2测量输入共模范围 (31)4.3.3 测量输出电压范围 (32)4.3.4 测量增益与相位裕度 (34)4.3.5 电源电压抑制比测试 (35)4.3.6 运放转换速率和建立时间分析 (37)4.3.7 CMRR的频率响应测量 (40)第5章算放大器版图设计 (41)5.1 Cadence使用说明 (41)5.2 版图设计 (44)5.3 CMOS运放版图 (44)第6章总结 (46)参考文献 (47)致谢词 (48)外文资料原文........................................................................... 错误!未定义书签。

外文资料译文........................................................................... 错误!未定义书签。

前言集成电路(Integrated Circuit)是把大量有源和无源器件及它们之间的互连线路集成在一起,形成一个具体的功能模块。

集成电路的出现和迅速发展,彻底改变了人类文明和人们的日常生活。

集成电路电子电路,但它不同于数以万计的一般意义上的电子电路集成在一个微型芯片的晶体管,电阻,电容和电感等电子元件,这是一个奇妙的设计和制造方法,人类社会的进步,创造前所未有的奇迹,现实是奇迹集成电路版图设计。

相对于数字集成电路的规律性和离散性,计算机辅助设计方法学在给定所需功能行为描述的数字系统设计自动化方面已经非常成功。

但并不适用于模拟电路设计。

一般来说,模拟电路设计仍然需要手工进行。

因此,仔细研究模拟电路的设计过程,熟悉那些提高设计效率、增加设计成功机会的原则是非常必要的。

模拟集成电路的设计流程可以分为前段设计和后端设计两大部分。

前段设计包括电路的设计、原理图输入和电路仿真;后端设计(又称为物理设计)包括版图的绘制与验证。

根据参数要求设计好电路后,在设计环境中输入原理图并对设计的电路进行仿真,也就是对电路结构、元件尺寸的设计、负载估计及布局前电路的模拟。

对电路的分析主要包括直流分析、瞬态分析、交流分析、噪声分析、模拟参数分析、温度分析等。

后端绘制的版图后首先要通过版图验证,版图验证包括设计规则验证、电气规则检查、版图与电路原理图对比验证。

运算放大器(简称运放)是许多混合信号系统和模拟系统中的一个组成部分。

不同层次的复杂的运算放大器是用来实现多种功能的:高速放大或过滤的直流偏置。

每一代 CMOS技术,由于供应减少电压和晶体管沟道长度的运算放大器的设计,继续为运放的设计提出一个复杂的问题。

本文依据基本CMOS集成运算放大电路的设计指标及电路特点,绘制基本电路图,用Spectre进行仿真模拟,从模拟的结果中推导出各个参量和其决定因素之间的关系,从而确定出符合设计指标所的版图几何尺寸以及工艺参数。

利用Spectre对设计初稿加以模拟,然后对不符合设计目标的参数加以修改,重复这一过程,最终得到优化设计方案。

最后根据参数尺寸等进行版图设计以及验证。

第1章绪论1.1 课题背景1.1.1 研究背景运算放大器(简称运放)是具有很高放大倍数的电路单元。

在实际地电路中,通常结合反馈网络共同组成某种功能模块。

由于早期应用于模拟计算机中,用以实现数字运算,故得名“运算放大器”。

运算放大器(简称运放)是许多混合信号系统和模拟系统中的一个组成部分。

不同层次的复杂的运算放大器是用来实现多种功能的:高速放大或过滤的直流偏置。

每一代 CMOS技术,由于供应减少电压和晶体管沟道长度的运算放大器的设计,继续为运放的设计提出一个复杂的问题。

我们粗略地把运放定义为“高增益的差动放大器”。

所谓“高”,指的是对应用,10。

由于运放一般用来实现一个反馈系统,其增益已足够了,通常增益范围在10~5其开环增益的大笑根据闭环增益电路的精度要求来选取。

20年前,大多数的运放是各种应用的一个通用模块。

这些努力试图创造一个“理想”的运算放大器,例如,高电压增益,高输入阻抗和低输出阻抗。

然而,却要牺牲成本费用的其他性能如输出幅度,速度和功耗。

与次相反,今天的运放设计,放大器的设计从开始就认识到妥协之间的各种参数,这样一个妥协,最终将需要更多地考虑整体的设计,因此,我们需要知道满足每个人从适当的值的参数。

例如,如果高速度的要求,增益误差要求不高的选择电路结构应有利于前者,后者可以牺牲。

运算放大器的版图设计,是模拟集成电路版图设计的典型,利用Cadence对设计初稿加以模拟,然后对不符合设计目标的参数加以修改并进行模拟,重复这一过程,最终得到优化设计方案,其关键在于寻找目标与决定因素之间的关系。

1.1.2研究内容模拟集成电路设计过程可以分为俩大部分设计的前端和后端。

前段设计包括设计电路、输入原理图和仿真电路;后端设计(也可以叫物理设计)包括版绘制版图及其验证。

前段设计包括设计电路结构和输入原理图。

根据要求参数设计所需电路后,把原理图输入到设计环境中并对其进行电路仿真,也就是对元件尺寸的设计、电路的结构、布局前电路及负载估计进行模拟。

在此过程中要求芯片的生产厂家提供出可以模拟库文件以便用于仿真。

分析电路主要还包括瞬态分析、直流分析、交流分析、温度分析、模拟参数分析、噪声分析等。

如果仿真结果完全符合了设计的要求以后就可以将电路提供给后端从而进行版图方面的设计。

后端中在绘制完成版图后最初要通过版图的一些验证,版图的验证包括版图与电路原理图的对比验证(LVS; Layout Versus Schematic)、电气规则的检查(ERC; Electrical Rule Check)、设计规则的验证(DRC; Design Rule Check)。

DRC验证是对电路的一些布局进行几何空间的验证从而保证厂家在工艺技术方面可以实现线路的连接;ERC验证用来检查电气连接中的一些错误,像电源和地是否短路、器件是否悬空等等所制定的一些电特性。