共源级放大器的电路设计及版图实现

共源极放大器电路及原理

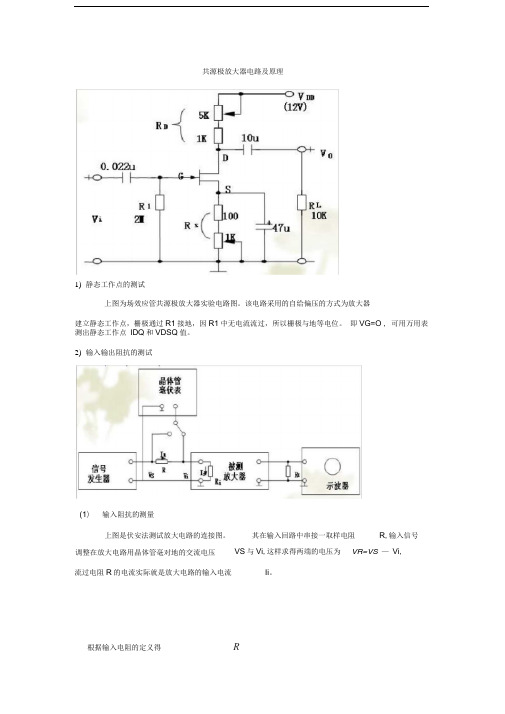

根据输入电阻的定义得 R1) 静态工作点的测试上图为场效应管共源极放大器实验电路图。

该电路采用的自给偏压的方式为放大器建立静态工作点,栅极通过R1接地,因R1中无电流流过,所以栅极与地等电位。

即VG=O , 可用万用表测出静态工作点 IDQ 和VDSQ 值。

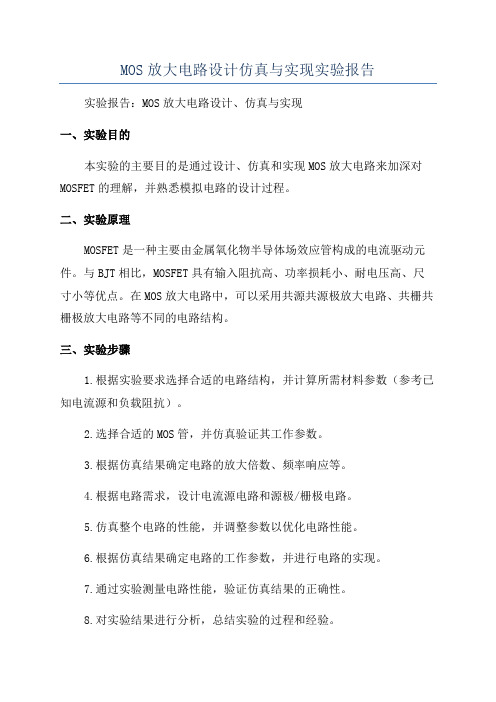

2) 输入输出阻抗的测试VS 与Vi ,这样求得两端的电压为 VR=VS — Vi ,流过电阻R 的电流实际就是放大电路的输入电流Ii 。

共源极放大器电路及原理上图是伏安法测试放大电路的连接图。

其在输入回路中串接一取样电阻 R ,输入信号调整在放大电路用晶体管毫对地的交流电压 (1) 输入阻抗的测量2)输出阻抗的测量放大器输出阻抗的大小,说明该放大器带负载的能力。

用伏安法测试放大电路的输出阻抗的测试电路如下图所示。

放大器输出阻抗的大小,说明该放大器带负载的能力。

用伏输入信号的频率仍选择在放大电路的中频段,输入信号的大小仍调整到确保输出信号不失真为条件,因此仍须用示波器监视输出信号的波形。

第一步在不接负载RL的情况下,用毫伏表测得输出电压第二步在接上负载RL的情况下,用毫伏表测得输出电压心=(尹-叽3)高输入阻抗Zi的测试前面讲了一般放大器输入阻抗的测量方法, F面以场效应管源极跟随器为例,介绍高输入放大器的输入阻抗的测试方法。

类似于源极跟随器这样的高输入阻抗放大器的输入阻抗•往往可以等效成一个输入电阻Z i和一个输入电容Ci的并联形式,因此,必须分辨测出Ri和Ci的值才能确定输入阻抗Zi的值。

测量Ri,由于被测电路的输入阻抗很高,可以和毫伏表的输入阻抗相比拟,若将毫伏表直接接到被测放大电路的输入端,会引起严重的测试误差. 为了减少小毫伏表并联接入引起的测量误差,要求毫伏表的输入电阻远大于被测电路的输入电阻,一般要求大于20倍以上•对于一般的毫伏表来说,是无法满足这样的要求的•但是被测电路是一的源极跟随器•具有高输入阻抗,低输出阻抗的特点,因而,可以不直接测试放大电路的输入电压,而V01。

折叠式共源共栅运算放大器设计说明

折叠式共源共栅运算放大器设计说明一、设计原理二、设计步骤1.确定规格要求:根据实际应用需求确定输入阻抗、输出阻抗、增益、带宽等参数。

2.选择管子:根据需求选择合适的场效应管。

通常选择具有良好参数的MOS管,如低频用的2N7000,高频用的BF861A等。

3.设计共源级:首先设计共源级,这是整个电路的放大核心。

根据增益要求和输入阻抗要求,确定共源电阻的值,再根据场效应管的参数计算源极电流和电压。

同时,要保证共源级的电流和电压工作在合适的范围内,不引起过大的功耗和失真。

4.设计共栅级:共栅级起到输出驱动的作用,可以提供较低的输出阻抗。

根据输出阻抗和带宽要求,选择合适的共栅电阻值和驱动电路的参数。

同时要注意共栅级的工作点和共源级的匹配,以保证电路的整体性能。

5.接入电源电压:根据电路需求,确定合适的电源电压。

注意电源电压的选择要与场效应管的参数相匹配,避免电压过高或过低导致管子失效或工作不稳定。

6.进行仿真和调试:在完成电路设计后,进行电路仿真和调试,检查电路的增益、带宽等参数是否满足设计要求。

可以使用SPICE电路仿真软件进行仿真,根据仿真结果对电路进行调整和优化。

7.布局和绘制电路板:根据电路设计,进行布局和绘制电路板。

布局过程中要注意相邻元件的干扰和电路的稳定性。

绘制电路板时要保持线路的规整和排布的合理性。

8.组装和测试:完成电路板制作后,进行元件的组装和焊接。

然后进行电路的测试和调试,检查电路的工作状态和各项指标是否满足要求。

三、注意事项1.设计时要考虑到电压的限制,避免电路失效或工作不稳定。

2.选择合适的场效应管,根据具体需求选择低频或高频的管子。

3.设计时要注意电路整体性能,使其在增益、带宽等方面满足要求。

4.在进行仿真时,要根据仿真结果对电路进行调整和优化,确保电路性能达到最佳状态。

5.布局和绘制电路板时要注意干扰和稳定性,保持线路的规整和排布的合理性。

6.组装和测试时要仔细检查,确保电路的工作状态和各项指标达到要求。

MOS放大电路设计仿真与实现实验报告

MOS放大电路设计仿真与实现实验报告实验报告:MOS放大电路设计、仿真与实现一、实验目的本实验的主要目的是通过设计、仿真和实现MOS放大电路来加深对MOSFET的理解,并熟悉模拟电路的设计过程。

二、实验原理MOSFET是一种主要由金属氧化物半导体场效应管构成的电流驱动元件。

与BJT相比,MOSFET具有输入阻抗高、功率损耗小、耐电压高、尺寸小等优点。

在MOS放大电路中,可以采用共源共源极放大电路、共栅共栅极放大电路等不同的电路结构。

三、实验步骤1.根据实验要求选择合适的电路结构,并计算所需材料参数(参考已知电流源和负载阻抗)。

2.选择合适的MOS管,并仿真验证其工作参数。

3.根据仿真结果确定电路的放大倍数、频率响应等。

4.根据电路需求,设计电流源电路和源极/栅极电路。

5.仿真整个电路的性能,并调整参数以优化电路性能。

6.根据仿真结果确定电路的工作参数,并进行电路的实现。

7.通过实验测量电路性能,验证仿真结果的正确性。

8.对实验结果进行分析,总结实验的过程和经验。

四、实验设备和材料1.计算机及电子仿真软件。

2.实验电路板。

3.集成电路元器件(MOSFET、电阻等)。

4.信号发生器。

5.示波器。

6.万用表等实验设备。

五、实验结果与分析通过仿真和实验,可以得到MOS放大电路的电压增益、输入输出阻抗、频率响应等参数。

根据实验结果,可以验证设计的合理性,并进行参数调整优化。

在实际应用中,MOS放大电路被广泛应用于音频放大器、功率放大器、运算放大器等场合。

因为MOSFET具有较大输入阻抗,所以MOS放大电路可以在输入端直接连接信号源,而不需要额外的输入电阻。

此外,MOS放大电路的功率损耗较小,适用于各种功率要求不同的应用场合。

六、实验心得通过设计、仿真和实现MOS放大电路的实验,我更加深入地理解了MOSFET的原理和应用。

在实验过程中,我通过不断调整电路参数和元器件选择,逐步提高了电路的性能。

通过与实验结果的对比,我发现仿真和实验结果基本吻合,验证了仿真的准确性。

共源共栅运算放大器的设计

共源共栅运算放大器的设计共源共栅运算放大器,也称为共源共栅放大器或共栅源跟随器,是常用的运算放大器电路结构。

它由共源放大器和共栅放大器组成,可以提供高增益、宽带宽并具有高输入电阻和低输出阻抗的特点。

下面将详细讨论共源共栅运算放大器的设计。

设计目标:1.高增益:希望放大器具有高增益,以提供较大的放大倍数。

2.宽带宽:希望放大器具有较宽的频带,以传输更高频率的信号。

3.高输入电阻:希望放大器具有较高的输入电阻,以不对被测电路产生影响。

4.低输出阻抗:希望放大器具有较低的输出阻抗,以不对后级电路产生影响。

设计步骤:1.选择晶体管:选择性能良好、参数稳定的晶体管作为放大器的关键部件。

常用的晶体管有MOSFET和JFET,选用适合的型号,使其性能满足设计的要求。

2.偏置电路设计:根据晶体管的工作条件,设计偏置电路以保证放大器的工作稳定性。

通常采用电流源和电阻网络来实现晶体管的偏置。

3.增益极化设计:确定放大器的增益级数和增益大小,并选择适当的分压比例和电阻值,使得输出电压能够满足要求。

同时考虑增益的稳定性,防止输出波形失真。

4.频率补偿设计:由于共源共栅放大器的频率响应受到极点和零点的影响,需要设计频率补偿电路来提高带宽。

常用的频率补偿方法有米勒补偿电容和并联补偿电容等。

5.输入和输出阻抗设计:通过选择合适的电路参数和组件数值,使得输入电阻和输出电阻达到所需的要求。

一般采用反馈电阻网络来实现输入和输出阻抗的调节。

6.功耗和温度设计:考虑到功耗和温度对放大器性能的影响,需要进行功耗和热量分析,并选择适当的散热器来保证放大器的长期稳定工作。

7.电源设计:根据放大器的电源需求,选择适当的电源电压和电源过滤电路,以保证放大器的工作正常和稳定性。

以上是共源共栅运算放大器的设计步骤。

在设计过程中,需要综合考虑各种因素,并根据具体的应用场景和要求进行优化。

通过合理的设计和调试,可以获得性能良好的共源共栅运算放大器。

11.1 共源放大器的设计.

菜单Place/ Part,或图标

,打开元件库

• 添加元件库 Add Lib__Analog 、pwrmos 、Source

• 提取元件 • 2n7000

元件库说明 参见教材

3.1.5 P24 表3.1.4

2020/3/2

返回

18

2.2 元件移动、旋转和删除

选中元器件:或工具栏的

用鼠标左键单击,此时元器件变为红色

已知条件

技术指标要求

+VCC=+12V RL=5.1k Vi=10mV(有效值) Rsi=50

AV>30 Ri>100k Ro<5.1k fL<100Hz fH>100kHz 电路稳定性好。

返回

三、电路设计一般流程

2020/3/2

返回

三、电路设计

4

的一般流程

四、共源放大器原理与设计举例

根据对FL,FH的要求,选择电容Cb1、Cb2

和C 2020/3/2

返回

s

8

画出带具体参数的电路连接原理图

根据上述设计,得到放大器的电路图如下:

调节Rp可改 变静态工作点 VB的值

Rp

Rd

Cb2

+ vi -

2020/3/2

返回

Cb1 +

Rg1 T1

d

io

B

g1 s Rg2

9

VDD vo

RL

五、共源放大器设计方案仿真验证

返回

7

3、电路参数确定的步骤:

选定VGSQ,VGSQ> VTN >0,或(1/3~1/5)VCC

选定IDQ, VDSQ ,并确定Rd;

iD K n (vGS VTN )2

折叠式共源共栅放大器设计

折叠式共源共栅放大器设计

下面是一个折叠式共源共栅放大器的设计示例:

1.选择合适的工作频率:首先确定设计的工作频率范围,根据应用需

求选择合适的频率。

2.确定器件参数:根据工作频率选择适合的MOSFET器件,并确定器

件的尺寸和工作点。

3.进行小信号分析:通过小信号等效电路分析,得到输入输出阻抗、

增益和带宽等参数。

4.设计输入匹配网络:设计输入匹配网络,使得输入阻抗与传输线匹配,以最大化输入信号的传输。

5.设计输出匹配网络:设计输出匹配网络,使得输出阻抗与负载匹配,以最大化输出信号的传输。

6.进行直流仿真:通过仿真软件,对折叠式共源共栅放大器的直流偏

置和工作点进行仿真和优化。

7.进行射频仿真:通过射频仿真软件,对折叠式共源共栅放大器的增益、带宽等性能进行仿真和优化。

8.PCB布局和封装:设计合适的PCB布局,使得折叠式共源共栅放大

器具有良好的抗干扰能力和稳定性。

选择合适的封装,以满足散热和尺寸

要求。

9.进行实验验证:通过PCB制作和实验验证,对设计的折叠式共源共

栅放大器进行性能测试和调整。

10.进行优化调整:根据实验结果,对折叠式共源共栅放大器进行优化和调整,以达到设计要求。

总结:折叠式共源共栅放大器设计需要从选择工作频率、器件参数确定到小信号分析、匹配网络设计、仿真优化、PCB布局和实验验证等多个步骤。

通过科学合理的设计和优化调整,可以实现折叠式共源共栅放大器的高效、低功耗和稳定工作。

mos管共源、共漏、共栅三种组态放大电路

mos管共源、共漏、共栅三种组态放大电路下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by the editor. I hope that after you download them, they can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you!In addition, our shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!共源、共漏、共栅三种组态放大电路是常见的MOS管放大电路配置,它们在集成电路设计中起到非常重要的作用。

共源级放大器电路实验报告

模拟集成电路设计基础实验报告1实验目的1.1掌握并熟练cadence 软件对原理图进行电路仿真;1.2了解基本电路的输入输出特性和工作原理;1.3深入理解mos 管参数的改变对电路的影响。

2实验要求2.1启动cadence ,建立库及Cellview 文件;2.2输入电路图;2.3设置仿真环境;2.4仿真并查看仿真结果,绘制曲线;2.5改变mos 管参数并分析结果。

2.6为了便于计算,根据一级spice 模型,nmos 器件理论值为:2ox /9.6C um fF =, s v cm u //1002p = , s v cm u //3502n =v 7.0v TH =,41.3422510//n ox C F V s μ-≈⨯,53.83510//p ox C F V s μ-≈⨯ 3共源级放大器性能分析3.1采用电阻负载共源级3.1.1电路图图1 电阻负载的共源级电路2))(/()2/1(v out in ox n dd out v v l w C Ru v --=(忽略沟道长度调制效应)(1)直流分析dd V =1.8V,in V 参数扫描范围0-2V ,R=5k Ω,nmos 宽长比3.6u/180n=20.图2 直流仿真结果MOS 管工作在饱和区时:2))(/()2/1(V TH in ox n dd out V V l w C Ru V --=.MOS 管工作在线性区时:)V 2)(/()2/1(V 2out V V V l w C Ru V TH in ox n dd out ---=)(图3 g m 图在饱和区))(/(g m TH gs ox n V V l w C u -=,当in V >TH V 时,跨导开始增大;在线性区DS ox n V l w C u )/(g m =,当in V >m ax V 时,m g 将会下降.m ax V -TH V =2))(/()2/1(V TH in ox n dd out V V l w C Ru V --=这个仿真结果表示,当in V =0.72V 时跨导最大。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(1-7)

小信号增益: (1-8)

(1-9)

(1-10)

(1-11)

总结:在CMOS工艺下,精确阻值的电阻难加工,阻值小时增益小,阻值大时电阻的尺寸太大,还会降低输出摆幅,一般采用MOS管代替电阻做负载。

2

电阻负载共源级放大器电路图如图2-3所示。

图2-3电阻负载共源级放大器电路图

对完成的电路图进行验证:选择Tools——Design Checks点击,验证结果如下图2-4所示。

对SPICE文件进行设置,包括加载包含文件、设定电源电压、输入信号、分析设定、设定输出[6]等。设定好后T-SPICE文件中会多出如图2-5信息,设定好后需要保存SPICE文件。

选择File——Export——Export SPICE把设计好的共源极放大器电路图输出成SPICE文件,输出的SPICE文件打开后最后面会看到如下图2-5的文字。

2.1.5

DRC规则检查如下图所示。

图2-9电阻负载的共源级放大器版图

关键词:共源级放大器;版图;Tanner Tools

Circuit Design and Layout Implementation oftheDommon-sourceAmplifier

Abstract

IC design technology is now one of the key technologies of the information age, today's VLSI (VLSL) has been inseparable from computer-aided design (CAD). Tanner is a CAD software, which is based IC design software tools for windows platform, powerful functionality of the software developed by the Tanner Research, analog circuit design, analysis of the circuit layout can be realized. This design is the circuit diagram tanner common source software based amplifier design and layout drawing. Is a common-source amplifier circuit of the basic CMOS gain stage. It is a typical inverting amplifier, or the load may be an active load current source. Common-source amplifier needs to be greater than the active load amplifier gain. Design current source load common-source amplifier IC has to learn to understand the nature of the help and improve, which is a combination of theory and practice. This thesis amplifier circuit design three cases, they are a common source amplifier resistive load of source-level amplifier and a current source diode connected load of the load common source amplifier circuit, amplifier design by these three make us more Use good common source amplifier.

1.1Tanner Tools软件的组成

Tanner Tools工具包括S-Edit、T-Spice、W-Edit、L-Edit与LVS五个相关软件。它们的主要实现功能如下:

(1)S-Edit:S-Edit主要功能是编辑电路图,每个电路图都有电路图和符号图两种模式。Tanner EDA格式的电路图具有等级结构电路图,由不同等级的模块组成这种电路图,高等级的模块是由低等级的模块组成。S-Edit还可以使当前模块的电路图转化为不同的网表。

图2-5电阻负载共源级放大器SPICE文件

分析及输出设定:分析设定如下图2-6,输出设定如下图。

图2-6电阻负载共源级放大器SPICE文件

2

电阻共源级放大器电路图仿真图如图2-7所示。

图2-7电阻负载共源级放大器电路图仿真图

2.1.4

电阻共源级放大器版图如图2-8所示。

图2-8电阻负载的共源级放大器版图

1

由Tanner Research公司基于Windows平台开发的TannerTools设计软件用于集成电路的设计[3],从电路设计、分析模拟到电路布局一一俱全。其中国内广泛应用的L-Edit版图编辑器,知名度很高。由Tanner EDA[4]软件公司所出品的L-Edit Pro是一个IC设计及验证的高性能软件系统模块,具有效率高,交互式等特点,从IC设计到输出,以及最后的加工服务完善且强大的功能,完全可以和百万美元级的IC设计软件媲美。L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了设计与验证的完整IC解决方案。L-Edit Pro快速、易用、精确的设计系统工具为每个IC设计者及生产商提供了完善丰富的功能。通过这款软件可完成IC的设计、版图编辑、自动布局布线、波形仿真和模拟验证等一系列的功能;它的编辑功能全面、电路图处理快速和模拟仿真及波形功能较好。主要解决电路图的电路设计,版图规划及它们相应的模拟仿真验证等问题。

图2-4电路图验证

2

T-SPICE主要的功能是电路分析和模拟,T-SPICE电路模拟器是由Tanner公司提供的专门用来模拟仿真电路的软件程序。T-SPICE的文本文件窗口中可以编辑、创建和打开各种文本文件,还可以在打开的文件中写入各种T-SPICE命令。T-SPICE输入用T-SPICE电路描述语言写成的输入文件后,就可以对输入文件进行模拟仿真。

(3)W-Edit:W-Edit的主要功能是显示T-SPICE的模拟结果,即显示T-SPICE模拟出的波形图,可进行简单的设置使得更加方便清晰观察模拟出的波形图。

(4)L-Edit:设计规则及检查、编辑布局版图、截面观察、电路转换、自动配置与绕线;

(5)LVS:对比布局图和电路图的网表。

1.2 Tanner Tools设计综合流程

先用S-Edit编辑要设计电路的电路图,然后将该电路图导出Spice文件。接着利用T-Spice软件将电路图模拟并输出成Spice文件,设置输入电平参数,然后进行运行,用W-Edit观察输出波形。假如模拟结果不对,接着回到S-Edit检查电路图,如果T-Spice没有错误,就用L-Edit对照电路图进行版图设计。版图绘制完后要以DRC进行设计规则检查,如果没有违反设计规则,再将版图进行修改直到设计规则检查没有错误为止。然后将验证过的版图导出Spice文件,再利用T-Spice模拟,如果有错误,再回到L-Edit修改版图设计。最后利用LVS进行S-Edit电路图导出的Spice文件和L-Edit版图导出的Spice文件对比,如果结果对比不相等,则回去修改S-Edit图或者L-Edit图。直到验证没有错误后,将L-Edit设计好的版图输出成GDSII类型文件,最后交给工厂去制作半导体过程中需要的光罩,流程如图2-1所示。

图2-1设计综合流程图

2

电阻负载共源级放大器由于自身的跨导,MOS管可以将栅-源电压的变化转换成小信号[5]漏极电流,于是输出电压由小信号漏电流流过电阻产生,如图2-2所示。

图2-2小信号分析

当 ,M1截止: (1-1)

饱和区: (1-2)

转折点: (1-3)

线性区: (1-4)

深线性区: (1-5)

大规模IC制造技术、IC版图设计技术、ASIC测试和封装技术、FPGA/CPLD编程下载技术及自动测试技术等在硬件实现方面融合了EDA[1]技术;在计算机辅助工程方面融合了计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)技术以及多种计算机语言的设计概念。随着集成电路发展的要求,集成电路EDA[2],准确地说是整个电子设计自动化必须要有大的发展。EDA的优点在于不是对单个单元的优化,而是对于全局的优化,从总体出发,保证其形状和尺寸最适于总的布局,是引线占的面积尽可能的小。EDA的重要性在于使设计便于处理,具有处理高度复杂电路而不出错的能力。集成电路的的飞速发展不仅给人们的生活带来了便捷,同时在军事,医学,科技等各方面发挥着巨大的作用。随着科技的不断进步,对集成电路的要求也在越来越高,设计出面积小、功耗低、成本低、性能良好的集成电路越发的重要。在现代科技中,计算机辅助设计的科学技术得以飞速发展。所以EDA技术是一门综合性学科,渗透于各个学科之中,EDA技术是电子设计与应用的发展方向。

Key word:CAD;TANNER;Common-sourceAmplifier

引言

1947年在美国的新泽西州的贝尔实验室诞生世界上第一个晶体管,自此开始了集成电路的发展,在1958年,基尔比德州仪器工程师发明了世界上第一个集成电路(IC)。而正是这枚小小的IC拉开了微电子学的大幕,从此集成电路的发展便开始走上了一条飞速发展的道路。1964年,摩尔提出了著名的摩尔定律:晶体管的集成度每18个月翻一倍。集成电路的的飞速发展不仅给人们的生活带来了便捷,同时在军事、医学、科技等各方面发挥着巨大的作用。电路物理实现的设计实际是为集成电路的版图设计,称其为物理设计。IC设计生产的基础是集成电路的版图设计,将电路的逻辑描述形式转化成版图的描述形式是版图设计的任务,并通过Mask光刻从而实现版图到集成电路芯片的物理转化。集成电路的版图设计关系到集成电路的功能是否正确,同时还关系到集成电路的性能、成本、面积和功耗的大小。因此设计出性能较高、功耗低、并能实际可靠地工作的版图相当重要。