运算放大器电路及版图设计报告

运算放大电路实验报告

运算放大电路实验报告运算放大电路实验报告引言运算放大电路是电子工程领域中一种常见的电路,它广泛应用于信号放大、滤波、积分、微分等功能。

本实验旨在通过搭建运算放大电路并进行实际测试,探究其工作原理和特性。

实验目的1. 了解运算放大电路的基本原理和组成结构;2. 熟悉运算放大电路的实际搭建和调试方法;3. 掌握运算放大电路的特性参数测量方法。

实验器材1. 运算放大器(OP-AMP);2. 电阻、电容等元件;3. 示波器、函数发生器等测试仪器。

实验步骤1. 搭建基本的非反馈运算放大电路。

将运算放大器的正、负输入端分别连接到电压源和接地,输出端接入负载电阻。

根据实验要求选择适当的电阻值,并使用示波器检测输出信号。

2. 测试运算放大器的放大倍数。

将输入信号接入运算放大器的正输入端,通过函数发生器输入不同频率和幅度的信号,并测量输出信号的幅度。

根据测量结果计算得到运算放大器的放大倍数。

3. 探究运算放大器的输入阻抗和输出阻抗。

使用电压源作为输入信号,通过改变输入电阻的值,测量输入电压和输出电压之间的关系。

同样地,通过改变负载电阻的值,测量输出电压和负载电阻之间的关系。

分析测量结果,得出运算放大器的输入阻抗和输出阻抗。

4. 实现运算放大器的反相放大功能。

在基本的非反馈运算放大电路的基础上,引入反馈电阻,并调整电阻的值,使得输出信号与输入信号呈反相关系。

通过示波器观察和测量输入信号和输出信号的波形,验证反相放大的功能。

实验结果与分析1. 在搭建基本的非反馈运算放大电路后,通过示波器观察到输出信号与输入信号具有相同的波形,且幅度有所放大。

这表明运算放大器实现了信号的放大功能。

2. 在测试运算放大器的放大倍数时,发现输出信号的幅度与输入信号的幅度成正比。

根据测量数据计算得到的放大倍数与理论值相符合,说明运算放大器具有较好的放大性能。

3. 通过测量输入电压和输出电压之间的关系,得到运算放大器的输入阻抗约为几十兆欧姆,说明输入电阻较高,不会对输入信号产生较大的负载效应。

两级运算放大器的版图设计(版图设计实验报告)

版图设计实验报告一、实验名称:两级运算放大器的版图设计二、实验目的:1、掌握模拟CMOS集成电路的设计方法2、掌握模拟CMOS集成电路的版图设计方法三、实验要求:1、设计对象为单端输出的两级运算放大器电路,其性能为:(1)、负载电容为CL=15pf,负载电阻为RL=100K欧;(2)、电源VDD=5V;(3)、增益带宽积CBW大于40MHZ;(4)、增益AVO大于80DB;(5)、相位裕都PM大于65;(6)、输入摆幅大于3V,输出摆幅尽量大;2、查阅相关资料,学习模拟CMOS集成电路版图的设计技巧3、完成两级运算放大器的版图设计,注意版图的对称性和隔离的设计,完成版图的DRC 验证;4、要求设计的版图满足电路的功耗,性能,功能,面积合理,美观。

四、设计对象仿真后MOS管的宽长比如下图:备注:电阻:R1为180欧电容:C1为2.62pf五、实验步骤1、观察模型文件(.SCS文件)或通过对CMOS管点单电路的DC分析并查看MOS管的直流工作点参数,得到PMOS,NMOS的基工艺参数(TOX,Cox,VthN,VthP等)2、确定具体的设计方案3、在schematic中画出电路图4、开始设计电路的版图5、修改版图,使之通过DRC验证6、优化版图使面积合理、美观六、实验结果面积:120*180=22680(um)七、实验心得第二次做版图设计,相较上次的实习难度提升了些许,最关键的是即将步入工作的我们重拾了那些被淡化和遗忘的知识,重新刷新脑子,和团队紧密合作,细致的分工,相互的监督和检验,我们一步步的完成脑中的想法,在有限的时间内完成老师的作业,这让我们感觉就是在工作间里。

然而每一步的前进总是让我们明白我们的不足和问题,知识的模糊,对版图设计的有限了解,粗糙的设计,迟钝的软件操作,这些都让我们反思了很久也想了很多,无论如何,经过了再一次的版图设计,我还是能够感到自己的进步,无论是对知识的理解还是对学习知识的渴求,而后者让我感到格外珍贵。

折叠式共源共栅运算放大器的设计报告

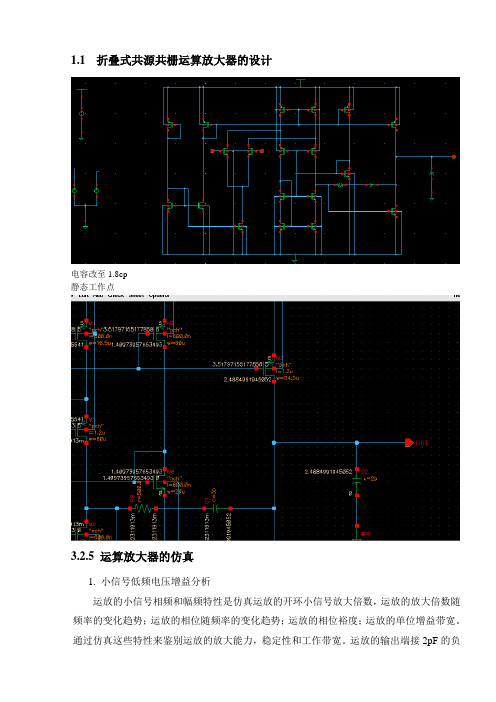

1.1折叠式共源共栅运算放大器的设计电容改至1.8cp静态工作点3.2.5 运算放大器的仿真1. 小信号低频电压增益分析运放的小信号相频和幅频特性是仿真运放的开环小信号放大倍数,运放的放大倍数随频率的变化趋势;运放的相位随频率的变化趋势;运放的相位裕度;运放的单位增益带宽。

通过仿真这些特性来鉴别运放的放大能力,稳定性和工作带宽。

运放的输出端接2pF的负载电容,在电源电压为5V ,共模输入电压为2.5V ,在运放输入端接差分交流信号1V ,两输入端的输入交流信号相位相反的条件下做交流小信号分析,可以得到运放的小信号相频和幅频特性如图(3.4)所示。

电路图连接如图3.3,仿真程序见附录1.12.5VAC.1图3.3 低频小信号特性仿真电路连接图图3.4 低频小信号电压增益分析图该运算放大器的小信号低频电压增益可以看出是112.793dB 。

满足设计指标。

2. 单位增益带宽程序跟测量小信号低频电压增益时相同,仿真波形如图3.5所示。

该运算放大器的单位增益带宽可以看出100.927MHz.满足设计指标。

图3.5 低频小信号单位带宽分析图3. 相位裕度仿真:从图上看出相位裕度为180°-127°=53°,满足设计指标。

程序和测量小信号低频电压增益时相同。

仿真波形如图3.6。

图3.6 相位裕度分析图4. 转换速率(slew rate)运放的转换速率是分析运放在大信号作用下的反映速度。

仿真运放的转换速率可将运放的输出端和反相输入端相连构成单位增益结构。

运放的同相输入端输入2V到3V的阶跃信号,利用仿真软件对该电路做瞬态分析得到的输出波形见图3.8,从仿真波形得到:在输出上升曲线的10%和90%处,其电压分别为2.9V和2.1V;时间分别为10.7ns和3.32ns。

运放的转换速率SR=(2.9V-2.1V)/( 10.7nS—3.32nS)=108.4 V/μs,满足运放的转换速率的指标要求。

案例2-OTA运算放大器的设计

案例2-OTA运算放⼤器的设计简单运算放⼤器的设计1.运算放⼤器的电路设计图1所⽰是⼀个电容性负载的两级CMOS基本差分运算放⼤器。

其中P1为运算放⼤器的电流偏置电路,为了减⼩电源电压波动的影响,改偏置电路采⽤了在改进型威尔逊电流镜电路中⼜增加了⼀个电阻R1的结构;P2为运算放⼤器的第⼀级放⼤器;P3为运算放⼤器的第⼆级放⼤器。

为使运算放⼤器的⼯作稳定,在第⼀级放⼤器和第⼆级放⼤器之间采⽤补偿⽹络来消除第⼆个极点对低频放⼤倍数、单位增益带宽和相位裕度的影响。

在运算放⼤器的电路结构图中,M1、M2、M3、M4、M5构成PMOS对管作为差分输⼊对,NMOS电流镜作为输⼊对管负载,PMOS管M5作为尾电流源的标准基本差分运算放⼤器;M6、M7构成以PMOS管作为负载的NMOS共源放⼤器;M14(⼯作在线性区)和电容Cc 构成运算放⼤器的第⼀级和第⼆级放⼤器之间的补偿⽹络;M9~M13以及R1组成运算放⼤器的偏置电路。

运算放⼤器的设计指标如表1.其设计流程是:⾸先根据技术指标,⼿⼯估算电路中各晶体管的宽长⽐;然后在对其进⾏仿真;通过反复的仿真和修改各个晶体管的参数,进⾏电路参数的优化,最终达到设计要求的性能指标。

图1两级CMOS 基本差分运算放⼤器2. 运算放⼤器的⼿⼯计算从该运放设计所采⽤的⼯艺模型mm0355v .l 中查得以下⼯艺参数: Kn=179.8µA/V 2 Vthn=0.55V Kp=-63.8µA/V 2 |Vthp|=0.73V1)通过压摆率SR 求M5的漏极电流若⽶勒补偿电容Cc=2pF ,因为SR=I D5/Cc 。

要求SR>10V/µS ,假设SR=100V/µS,ID5为M5的漏极电流,则:ID5=SR×Cc=100 V/µS×2E -12=200µA 。

由于流过M5的电流为200µA ,则流过M1、M2、M3和M4的电流为200µA/2=100µA 。

放大器电路设计报告

放大器电路设计报告1. 介绍放大器是电子设备中常见的一种电路,它可以将输入信号放大到所需的幅度,在实际应用中起到增强信号的作用。

本报告将详细介绍一个放大器电路的设计过程和相关参数选择。

2. 设计目标本次设计的放大器电路的主要目标是能够将输入信号放大10倍,并在频率范围内保持较低的失真。

3. 电路设计放大器电路通常由三个主要部分组成:输入级、放大级和输出级。

输入级用于将输入信号转换成适合放大的形式,放大级将信号放大到所需的幅度,输出级则用于将放大后的信号输出。

3.1 输入级设计输入级需要能够将输入信号转换成适合放大的形式,并具有较好的输入阻抗。

一种常见的输入级设计是使用一个共射放大器,它能够提供较高的电压放大倍数和较低的输入阻抗。

根据设计目标,我们选择一个放大倍数为5的共射放大器。

3.2 放大级设计放大级的主要任务是将输入信号放大到所需的幅度。

在本次设计中,放大级需要实现10倍的放大倍数,并保持较低的失真。

根据要求,我们选择使用一个共射放大器作为放大级。

3.3 输出级设计输出级的主要任务是将放大后的信号输出,并且需要具有较低的输出阻抗,以便能够驱动后续的负载。

在本次设计中,我们选择使用一个共射跟随器作为输出级,它能够提供较低的输出阻抗和较大的输出电流能力。

4. 参数选择在进行设计之前,我们需要选择一些相关的参数来满足设计要求。

4.1 输入级参数选择为了保证输入级具有较好的放大倍数和较低的输入阻抗,我们选择晶体管型号为2N3904,其电流放大倍数为100,输入阻抗大约为\`100kΩ\`。

4.2 放大级参数选择为了满足放大10倍的要求,我们选择晶体管型号为2N3904,其电流放大倍数为100。

通过电流分配可以计算出电阻值。

4.3 输出级参数选择为了满足较低的输出阻抗和较大的输出电流能力,我们选择晶体管型号为2N3904,其输出阻抗大约为\`10Ω\`。

5. 结果验证完成电路设计后,我们进行了模拟仿真,并测量了实验电路的参数。

毕业设计(论文)-cmos运算放大电路的版图设计[管理资料]

![毕业设计(论文)-cmos运算放大电路的版图设计[管理资料]](https://img.taocdn.com/s3/m/15f996a177232f60dccca185.png)

目录摘要 (3)第一章引言 (3)§ (3)§ CMOS 电路的发展和特点 (5)第二章CMOS运算放大器电路图 (8)§Pspice软件介绍 (8)Pspice运行环境 (12)Pspice功能简介 (12)§CMOS运算放大器电路图的制作 (14)§小结 (20)第三章版图设计 (20)§L-EDIT软件介绍 (20)§设计规则 (21)§集成电路版图设计 (24)PMOS版图设计 (24)NMOS版图设计 (27)CMOS运算放大器版图设计 (27)优化设计 (32)第四章仿真 (40)§DRC仿真 (41)§LVS 对照 (42)第五章总结 (48)附录 (50)参考文献 (52)致谢 (53)摘要介绍了CMOS运算放大电路的版图设计。

并对PMOS、NMOS、CMOS运算放大器版图、设计规则做了详细的分析。

通过设计规则检查(DRC)和版图与原理图对照(LVS)表明,此方案已基本达到了集成电路工艺的要求。

关键词:CMOS 放大器 NMOS PMOS 设计规则检查版图与原理图的对照AbstractThe layout desigen of CMOS operation amplifer is presented in this the layouts and design rules of PMOS,NMOS, and CMOS operation amplifer. The results of design rule check(DRC)and layout verification schmatic(LVS) shown that the project have already met to the needs of IC fabricated processing. Keywords: CMOS Amplifer NMOS PMOS DRC LVS第一章引言1.1 集成电路版图设计的发展现状和趋势集成电路的出现与飞速发展彻底改变了人类文明和人们日常生活的面目。

运算放大电路试验报告

运算放大电路试验报告.docx实验报告课程名称:电子电路设计与仿真实验名称:集成运算放大器的运用班级:计算机18亨VrR输入电阻:Ri00输出电阻:Ro0同相比例放大电路仿真电路图电压输入输出波形图差动放大电路电路图差动放大电路仿真电路图五:实验步骤:1.反相比例运算电路(1)设计一个反相放大器,Au12V。

(2)输入f1kHz、ui100mV的正弦交流信号,测量相应的uo,并用示波器观察uo和ui的波形和相位关系,记录输入输出波形。

测量放大器实际放大倍数。

(3)保持ui30mV不变,测量放大的上截止频率,并在上截止频率,并在上截止频率点时在同一坐标系中记录输入输出信号的波形。

七:实验数据分析:1.在反相比例运算电路中当输入f1kHz、ui100mV的正弦交流信号时测得输入与输出反相,且放大倍数Au5,产生了误差应该主要是因为电路板上的电阻的标称值并不准确。

2.当ui等于30mV时测出上截止频率为219kHz,然而此时输入和输出的相位差已经不是180,原因应该是芯片中的电容元件在高频的情况下使得输出电压的相位产生了异于原来的改变。

3.在反相加法器电路的实验中,产生的输出波形基本上符合理论的预测,但是uo的直流分量稍小于ui1的两倍,这应该也是因为电阻的标称值不准,而且主要还是因为分压电路分出的电压并没有1V因为在分压电路上与1kQ并联的实验电路实际上让ui1小于1V4.在积分电路试验中,一开始输出波形有着很大的直流分量,到后来将Rf改为由1M改到20kQ解决了这个问题。

分析后发现应该是由于Rf 的支路上存在一个很小的电压,但是一旦Rf很大其两端就会产生一个很大的电位差,这就是uc(0),也就是波形中的直流分量,因此减/J、Rf即可解决问题心得体会在做实验的时候发现一个小现象,就是发现直流电源不通时会得到完全不同的输出波形,只有接通是得到正确波形。

后来我仔细想了一下,应该是电路已经变了,这个时候就要换思路想了。

电路模电实验之运算放大器实验报告

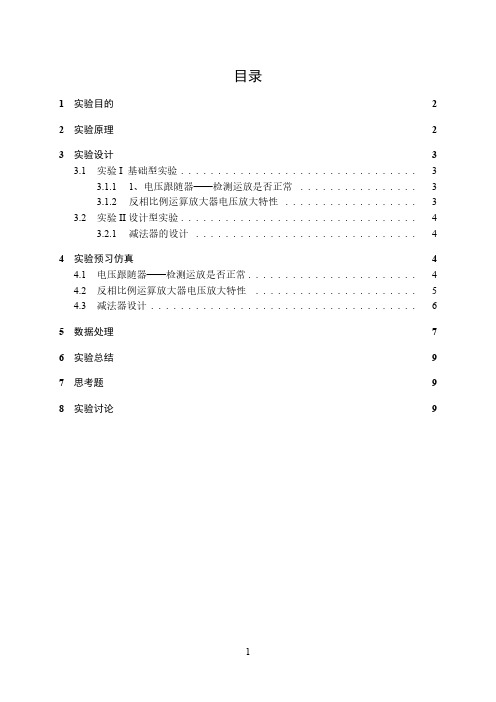

目录1实验目的2 2实验原理23实验设计33.1实验I基础型实验 (3)3.1.11、电压跟随器——检测运放是否正常 (3)3.1.2反相比例运算放大器电压放大特性 (3)3.2实验II设计型实验 (4)3.2.1减法器的设计 (4)4实验预习仿真44.1电压跟随器——检测运放是否正常 (4)4.2反相比例运算放大器电压放大特性 (5)4.3减法器设计 (6)5数据处理7 6实验总结9 7思考题9 8实验讨论91实验目的•深刻理解集成放大器工作在线性工作区时,遵循的两条基本原则——虚短、虚断•熟悉集成运算放大器的线性应用。

•掌握比例运算等电路、训练设计运放电路的能力。

2实验原理集成运算放大器是一种高电压放大倍数的多级直耦放大电路,在深度负反馈条件下,集成运放工作在线性工作区,它遵循两条基本原则:1.虚短:U i=U−−U+≈02.虚断:I N≈I p≈0(非线性区也成立)用途:广泛应用于各种信号的运算处理、测量以及信号的产生、变换等电路中。

图1:运算放大器符号3实验设计3.1实验I基础型实验3.1.11、电压跟随器——检测运放是否正常3.1.2反相比例运算放大器电压放大特性3.2实验II设计型实验3.2.1减法器的设计1.自行设计运放电路,要求实现u0=2u i2−u i12.将u i分别设置为以下两组信号,验证电路是否满足要求4实验预习仿真4.1电压跟随器——检测运放是否正常图2:Multisim接线图3:Multisim结果4.2反相比例运算放大器电压放大特性图4:Multisim 接线图5:Multisim 结果U i (V )理论值(V )实测值(V )U N U P U O U O U iU N U P U O U O U i-0.300310455.314µV 564.134µV 3.012V 10.040.3-310563.904µV489.999µV-2.987V9.964.3减法器设计设计如图所示:表3:验证结果波形频率u i u0直流0u i1=1V,u i2=2V3.04V正弦波500Hz u i1=1V,u i2=2V2.98V5数据处理表1U i(V)理论值(V)实测值(V)U N U P U O U OU iU N U P U O U OU i-0.3003100.1mV0.2mV 3.66V12.20.300-310-0.1mV0-3.65V12.16表2波形频率u i u0直流0u i1=1V,u i2=2V 3.00V正弦波500Hz u i1=1V,u i2=2V 3.24V1.完成表1,并绘制基础型实验的运放的电压传输特性;2.列出基础型实验中U i和U o理论关系式,并和仿真数据、实际数据比较;•电压跟随器u i=u o仿真数据中u i=u o,实验数据u i=1.00V,u o=1.04V,在误差允许范围内,所以等式也成立。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录摘要 (2)第一章引言 (3)第二章基础知识介绍 (4)2.1 集成电路简介 (4)2.2 CMOS运算放大器 (4)2.2.1理想运放的模型 (4)2.2.2非理想运算放大器 (5)2.2.3运放的性能指标 (5)2.3 CMOS运算放大器的常见结构 (6)2.3.1单级运算放大器 (6)2.3.2简单差分放大器 (6)2.3.3折叠式共源共栅(Folded-cascode)放大器 (7)2.4版图的相关知识 (8)2.4.1版图介绍 (8)2.4.2硅栅CMOS工艺版图和工艺的关系 (8)2.4.3 Tanner介绍 (9)第三章电路设计 (10)3.1总体方案 (10)3.2各级电路设计 (10)3.2.1第三级电路设计 (10)3.2.2第二级电路设计 (11)3.2.3第一级电路设计 (12)3.2.4三级运放整体电路图及仿真结果分析 (14)第四章版图设计 (15)4.1版图设计的流程 (15)4.1.1参照所设计的电路图的宽长比,画出各MOS管 (15)4.1.2 布局 (17)4.1.3画保护环 (17)4.1.4画电容 (17)4.1.5画压焊点 (18)4.2 整个版图 (19)第五章 T-Spice仿真 (21)5.1提取T-Spice文件 (21)5.2用T-Spice仿真 (24)5.3仿真结果分析 (26)第六章总结 (27)参考文献 (28)摘要本次专业综合课程设计的主要内容是设计一个CMOS三级运算跨导放大器,该放大器可根据不同的使用要求,通过开关的开和闭,选择单级、两级、三级组成放大器,以获得不同的增益和带宽。

用ORCAD画电路图,设计、计算宽长比,仿真,达到要求的技术指标,逐级进行设计仿真。

然后用L-Edit软件根据设计的宽长比画版图,最后通过T-Spice仿真,得到达到性能指标的仿真结果。

设计的主要结果归纳如下:(1)运算放大器的基本工作原理(2)电路分析(3)设计宽长比(4)画版图(5)仿真(6)结果分析关键词:CMOS运算跨导放大器;差分运放;宽长比;版图设计;T-Spice仿真第一章引言众所周知,微电子技术、电力电子技术和计算机技术在相互渗透、相互支撑和相互促进的紧密关系中,均得到了飞速的发展。

现代信息社会的支柱——计算机和通讯,其主要硬件设备是集成电路。

以集成电路的发展为标志的微电子技术无所不在,己成为现代信息社会的基础。

自从60年代世界上第一块集成电路在美国诞生以来,集成电路技术以惊人的速度发展。

第一块集成电路上只有四个晶体管,而目前的集成电路已经可以在一片硅片上集成几千万只晶体管,甚至上亿只晶体管。

集成电路的发展经历7小规模IC (SSI)、大规模IC (LSD 、超大规模IC (VLSI)和特大规模(ULSI)的不同阶段,集成电路的性能(高集成度、高速度和低功耗等)迅速提高。

集成电路工艺已发展到深亚微米,特征带宽可达到0.18 um,甚至更小。

运算放大器在模拟电路中是个非常重要而且非常复杂的模块。

它非常广泛的应用于开关电容滤波器、调解器、整流器、峰探测器、模拟到数字(AID)和数字到模拟(D/A)转换器等模块中。

它的性能直接影响着整个电路的动态范围和高频的应用。

本次课程设计从运算放大器结构特点及其工作原理出发,对其各种参数的定义和它们之间相互关系作了详细的阐述。

为保证放大器的稳定性,选作单级放大器时,需米勒补偿,作为两级或单级放大时需进行极间补偿。

用ORCAD画电路图,并设计合适的宽长比,模拟仿真,使其达到设计要求;根据所设计的宽长比用L-Edit软件进行版图设计,从版图中提取T-Spice 文件;根据版图中提取的参数利用T-Spice软件进行仿真,仿真结果与ORCAD仿真结果进行比较,不满足设计指标,则修改版图,再提取参数,做仿真比较,使其结果满足所设计要求。

第二章基础知识介绍2.1 集成电路简介集成电路(integrated circuit),一种微型电子器件或部件。

采用一定的工艺,把一个电路中所需的晶体管、二极管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构;其中所有元件在结构上已组成一个整体,这样,整个电路的体积大大缩小,且引出线和焊接点的数目也大为减少,从而使电子元件向着微小型化、低功耗和高可靠性方面迈进了一大步。

集成电路具有体积小,重量轻,引出线和焊接点少,寿命长,可靠性高,性能好等优点,同时成本低,便于大规模生产。

它不仅在工、民用电子设备如收录机、电视机、计算机等方面得到广泛的应用,同时在军事、通讯、遥控等方面也得到广泛的应用。

用集成电路来装配电子设备,其装配密度比晶体管可提高几十倍至几千倍,设备的稳定工作时间也可大大提高。

2.2 CMOS运算放大器从运放的模型出发来分析理想运放和实际的运放的差别,探讨了测量运算放大器的各种性能指标,然后,介绍一下当今比较常见的放大器的结构。

2.2.1理想运放的模型运算放大器的符号如图一,理想运算放大器的理想参数为: (1)差模信号的开环电压增益为无穷大,即 Av=∞ ;(2) 差动 +输入电阻为无穷大,即Rin=∞; (3)输出 + +电阻为零,即Rout=0;(4)开环频带宽度为无穷大; (5)当输入同相端(“+”)与反相端(“一”)的电压相等时,输出电压Vout=0。

_ _ _图2.1 运算放大器符号上述条件下,运算放大器的两输入端之间为零端口化,即所谓“虚短”状态。

零端口是一个二端网络.它的电压和电流同时为零,其特性可由下式表示2.2.2非理想运算放大器实际的运算放大器只能十分接近上述的理想放大器,或者说在理想运算放大器中增加一系列的模型参数,使其更接近实际情况,如差动输入电阻、差动输入电容、输出电阻共模输入电阻等。

2.2.3运放的性能指标(1)增益对于实际的运算放大器,电压增益是有限的,在低频和小信号情况下,典型值是从到。

(2)线性范围输出电压在一定的范围内,与输入电压的线性关系=A(-)才成立。

一般情况下,的最大值是比正的电源电压要小;而的最小值要比负的电源电压大一些。

(3) 失调电压对于理想的运算放大器来说,如果,则。

但在实际的器件中,这种关系并不完全正确。

当输入短接时,在输出端电压 , 与运放的增益成正比,因此,用输入失调电压(使的差分输入电压)来表示更为方便。

其典型值在士2mV 到10 mV之间。

(4)共模抑制比(CMRR)共模电压增益为差分电压增益为共模抑制比(CMRR)被定义为差分电压增益与共模电压增益的比值,即或者等于。

对于CMOS放大器,其值大致在60dB80dB之间。

共模抑制比表明的是运算放大器抑制噪声的能力,因此一个大的CMRR值是很重要的。

(5)频率响应由于存在寄生电容、有限的载流子迁移率等原因,在高频的情况下,电压增益会随着频率的增加而减小,通常用单位增益带宽(即在电压增益为电压1时的频率)来描述。

单位增益带宽通常在1100 Mhz范围内。

(6)非零输出电阻实际的运算放大器的开环输出电阻并不为零。

带输出缓冲的放大器,它的输出电阻大致在0.1 5kΩ范围内;而不带输出缓冲级的放大器,它的输出电阻要大的多,这将增加对连接到输出的电容充放电的时间,也就是降低了运算放大器的速度和最高的信号频率。

(7)噪声MOS晶体管由于它本身的结构、工艺技术和在运算放大器中的偏置条件等原因,在低频情况下显示了较高的闪烁噪声,而在高频情况下热噪声是主要的。

这些噪声晶体管在运放的输出端产生了噪声电压,除以电压增益等效为输入噪声电压源,它严重影响了运算放大器的动态范围。

(8)DC功耗理想放大器中没有任何的直流功耗,而在实际的运放中,运算放大器的直流功耗的典型值为0.2510mW。

上述描述的都是在实际的运算放大器的设计过程中所要考虑的主要参数,但这些参数之间的实现是相互矛盾的。

要实现某些参数就要以牺牲其它性能指标为代价,因此,要设计一个高性能的运算放大器,多方面的优化是一个非常关键的问题。

2.3 CMOS运算放大器的常见结构2.3.1单级运算放大器运算放大器是一种有足够高的正向增益的放大器(受控源),当加上负反馈时,其闭环转移函数和运放增益无关。

根据不同的应用,运算放大器所采用的结构是不一样的,运放的基本结构图如图2.2所示。

图2.2 运放基本结构单级放大器的增益 ,式中为输入端跨导,为输出电阻。

2.3.2简单差分放大器如图2.3是单端输出的差分放大器的结构图。

电路的小信号、低频电压增益等于//),大约在50倍左右。

可以看出,简单差分放大器的增益比较低。

增加增益的方法有两种:增加输入器件的跨导或者是增加整个电路的输出电阻。

器件的跨导,减小器件的沟道长度可以增加跨导,但同时它也降低了输出电阻(由于沟道调制效应)。

因此,它是降低而不是增加了放大器的增益。

另外,从电路的面积和功耗方面来说,靠增加器件的宽度和偏置电流来增大器件的跨导也是不可取的。

总的来说,最直接有效的方法就是增加放大器的输出电阻。

图2.3 简单差分放大器2.3.3折叠式共源共栅(Folded-cascode)放大器折叠式共源共栅放大器是目前使用最为广泛的单级放大器之一,它解决了套叠式共源共栅放大器无法连接成单位缓冲器结构的缺陷.由于它的输出电阻比较高,因此常做单级运算跨导放大器(OTA)来使用。

图2.4是采用n沟道差分输入的共源共栅放大器。

电路中,负载电容和补偿电容是同一器件。

在两极放大器中因负载电容而产生的非主极点在此电路中并不存在,因此它可以获得较高的闭环增益带宽。

同时,共源共栅结构本身的Mille电容小,在高频下,电源抑制作用也没有降低。

图2.4折叠式共源共栅放大器2.4版图的相关知识2.4.1版图介绍集成电路版图是电路系统与集成电路工艺之间的中间环节,是一个必不可少的重要环节。

通过集成电路版图设计,可以将立体的电路系统变为一个二维的平面图形,再经过工艺加工还原为基于硅材料的立体结构。

因此,版图设计是一个上承电路系统,下接集成电路芯片制造的中间桥梁。

2.4.2硅栅CMOS工艺版图和工艺的关系1. N阱——做N阱的封闭图形处,窗口注入形成P管的衬底2. 有源区——做晶体管的区域(G,D,S,B区),封闭图形处是氮化硅掩蔽层,该处不会长场氧化层3. 多晶硅——做硅栅和多晶硅连线。

封闭图形处,保留多晶硅。

4. 有源区注入——P+,N+区。

做源漏及阱或衬底连接区的注入5. 接触孔——多晶硅,扩散区和金属线1接触端子。

6. 金属线1——做金属连线,封闭图形处保留铝7. 通孔——两层金属连线之间连接的端子8. 属线2——做金属连线,封闭图形处保留铝2.4.3 Tanner介绍Tanner集成电路设计软件是基于Windows平台的用于集成电路设计的工具软件,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。