《超大规模集成电路设计》考试习题(含答案)完整版

《超大规模集成电路设计》考试习题(含答案)完整版

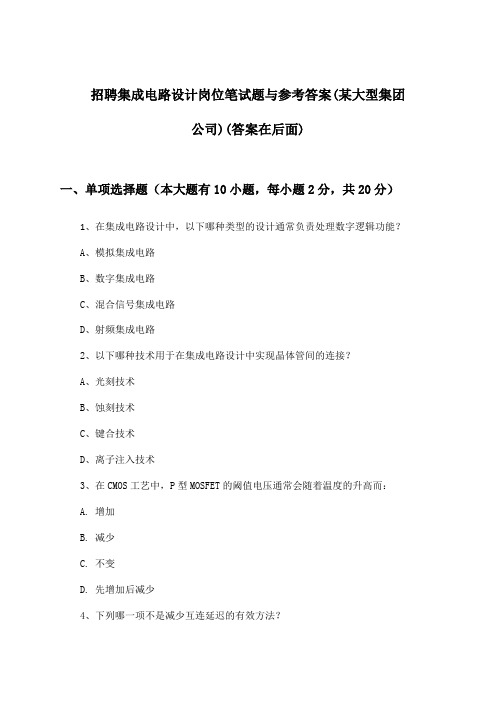

1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC,SSI)•中规模集成电路(Medium Scale IC,MSI)•大规模集成电路(Large Scale IC,LSI)•超大规模集成电路(Very Large Scale IC,VLSI)•特大规模集成电路(Ultra Large Scale IC,ULSI)•巨大规模集成电路(Gigantic Scale IC,GSI)划分集成电路规模的标准2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得.3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

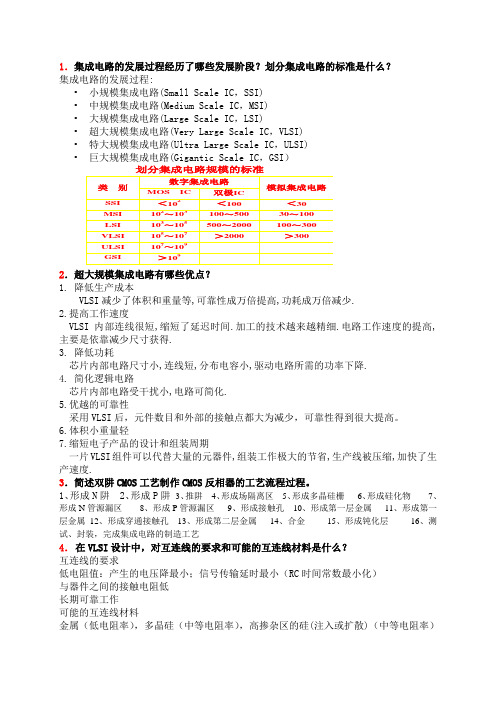

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。

1、形成N阱2、形成P阱3、推阱4、形成场隔离区5、形成多晶硅栅6、形成硅化物7、形成N管源漏区8、形成P管源漏区9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么?互连线的要求低电阻值:产生的电压降最小;信号传输延时最小(RC时间常数最小化)与器件之间的接触电阻低长期可靠工作可能的互连线材料金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率)5.在进行版图设计时为什么要制定版图设计规则?—片集成电路上有成千上万个晶体管和电阻等元件以及大量的连线。

集成电路设计岗位招聘笔试题与参考答案(某大型集团公司)

招聘集成电路设计岗位笔试题与参考答案(某大型集团公司)(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1、在集成电路设计中,以下哪种类型的设计通常负责处理数字逻辑功能?A、模拟集成电路B、数字集成电路C、混合信号集成电路D、射频集成电路2、以下哪种技术用于在集成电路设计中实现晶体管间的连接?A、光刻技术B、蚀刻技术C、键合技术D、离子注入技术3、在CMOS工艺中,P型MOSFET的阈值电压通常会随着温度的升高而:A. 增加B. 减少C. 不变D. 先增加后减少4、下列哪一项不是减少互连延迟的有效方法?A. 使用更细的金属线B. 使用更高介电常数的绝缘材料C. 减少金属层之间的距离D. 使用铜代替铝作为互连线材料5、集成电路设计中,以下哪种工艺主要用于制造CMOS(互补金属氧化物半导体)逻辑电路?A. 双极型工艺B. 金属氧化物半导体工艺C. 双极型/金属氧化物半导体混合工艺D. 双极型/CMOS混合工艺6、在集成电路设计中,以下哪个参数通常用来描述晶体管的开关速度?A. 饱和电压B. 输入阻抗C. 开关时间D. 集成度7、在集成电路设计中,用于描述电路逻辑功能的硬件描述语言不包括以下哪一种?A. VerilogB. VHDLC. C++D. SystemVerilog8、下列选项中,哪一个不是ASIC(专用集成电路)设计流程中的一个阶段?A. 逻辑综合B. 布局布线C. 系统集成D. 物理验证9、以下哪种工艺技术通常用于制造高性能的集成电路?A. 混合信号工艺B. CMOS工艺C. GaN(氮化镓)工艺D. BiCMOS工艺二、多项选择题(本大题有10小题,每小题4分,共40分)1、在CMOS工艺中,关于阱(well)的概念,下列说法正确的有:A. NMOS晶体管通常位于P型阱中B. PMOS晶体管通常位于N型阱中C. N阱用于隔离不同区域的晶体管,防止电流泄露D. P阱可以与N阱共存于同一层硅片上而不会相互影响2、关于集成电路版图设计中的DRC(Design Rule Check)规则,下列哪些陈述是正确的?A. DRC规则是为了确保电路性能优化B. DRC规则定义了最小特征尺寸、最小间距等制造限制C. 违反DRC规则可能会导致制造缺陷,如短路或开路D. DRC规则在所有半导体制造工艺中都是相同的3、关于集成电路设计,以下哪些是典型的电路设计类型?()A、模拟电路设计B、数字电路设计C、混合信号电路设计D、射频电路设计E、光电子电路设计4、在集成电路设计中,以下哪些因素会影响电路的功耗?()A、晶体管的工作状态B、电源电压C、电路的复杂度D、芯片的温度E、外部负载5、在集成电路设计过程中,下列哪些技术用于提高电路的性能?A. 使用更先进的制程技术B. 优化电路布局减少信号延迟C. 增加电源电压以提升速度D. 减少电路层数降低制造成本E. 应用低功耗设计方法6、下列哪些是实现CMOS逻辑门时需要考虑的关键因素?A. 输入电平的阈值B. 输出驱动能力C. 功率消耗D. 静态电流消耗E. 电路的工作频率7、以下哪些技术或方法属于集成电路设计中的模拟设计领域?()A. 信号处理算法B. 逻辑门电路设计C. 模拟电路仿真D. 功耗分析E. 版图设计8、在集成电路设计中,以下哪些步骤是进行版图设计的必要阶段?()A. 电路原理图设计B. 布局规划C. 逻辑分割D. 布局布线E. 版图检查9、在CMOS工艺中,影响MOSFET阈值电压的因素有哪些?A. 氧化层厚度B. 衬底掺杂浓度C. 栅极材料类型D. 源漏区掺杂浓度E. 温度F. 器件尺寸三、判断题(本大题有10小题,每小题2分,共20分)1、集成电路设计岗位的工程师需要具备扎实的数学基础和电子工程知识。

《超大规模集成电路设计》考试习题(含答案)完整版分析

1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC,SSI)•中规模集成电路(Medium Scale IC,MSI)•大规模集成电路(Large Scale IC,LSI)•超大规模集成电路(Very Large Scale IC,VLSI)•特大规模集成电路(Ultra Large Scale IC,ULSI)•巨大规模集成电路(Gigantic Scale IC,GSI)划分集成电路规模的标准2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得.3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。

1、形成N阱2、形成P阱3、推阱4、形成场隔离区5、形成多晶硅栅6、形成硅化物7、形成N管源漏区8、形成P管源漏区9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么?互连线的要求低电阻值:产生的电压降最小;信号传输延时最小(RC时间常数最小化)与器件之间的接触电阻低长期可靠工作可能的互连线材料金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率)5.在进行版图设计时为什么要制定版图设计规则?—片集成电路上有成千上万个晶体管和电阻等元件以及大量的连线。

超大规模集成电路答案

⎞ ⎟⎠

(1

+

λnVM

)

= 115×10−6 × 2× 0.63× (1.05 − 0.4 − 0.63 / 2)(1+ 0.06×1.05)

= 52 ×10−6 A

g = − k Vn DSATn + k Vp DSATp

ID

(VM

)(λn

−

λ p

)

= − 1 2 ×115×10−6 × 0.63 + 3× 30×10−6 ×1

A:Al1 导线平面电容:(0.1×103μm2) ×30aF/μm2=3pF Al1 导线边缘电容:2×(0.1×106μm) ×40aF/μm=8pF Al1 导线总电容:CW=11pF Al1 导线电阻:RW=0.075Ω/□×(0.1×106μm)/ (1μm)=7.5kΩ Al1 导线的 r 和 c 值:c=110aF/μm;r=0.075Ω/μm

由VD2 > VDSATn ,确定 M2 发生速度饱和,因此

ID

=

kn

⎛ ⎜⎝ (VGS 2

− VT 2 )VDSAT

2

− VDSAT 2

⎞ ⎟⎠

,

VGS 2

= VT 2

+

⎛ ⎜ ⎝

ID kn

2

+ VDSAT 2

VDSAT

⎞ ⎟ ⎠

,

VGS 2

=

0.94

+

⎛ ⎜⎝

பைடு நூலகம்

0.2 ×10−3 3× 8.9 ×10−5

( ) ID

=

kn 2

VGS 2 − VT 2

2 , VGS 2 = VT 2 +

2ID kn

集成电路设计岗位招聘笔试题及解答(某世界500强集团)2024年

2024年招聘集成电路设计岗位笔试题及解答(某世界500强集团)(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1、下列晶体管类型的半导体材料中,通常用于集成电路制造中的集电极,其来源最为广泛且成本较低的是?A. 氮化镓 (GaN)B. 硅 (Si)C. 锗 (Ge)D. 金刚石2、在集成电路设计行业中,总线宽度是指一次可以传输的信号数量。

下列总线的有效性排列中,哪一组是可以用在8位处理器的?A. 1位或4位总线B. 4位或8位总线C. 8位或16位总线D. 4位或16位总线3、下列哪种电路拓扑结构通常用于实现高增益放大器?A.மமமமமமமமமமB. 喜欢的肯定是什么?4、CMOS工艺中,为降低漏电流和提高开关速度,通常采用什么措施?A. 增加阈值电压B. 减少阈值电压C. 降低工作电压D. 提高工作电压5.在集成电路设计中,以下哪个因素对芯片的性能有最大影响?A. 电流大小B. 电压水平C. 晶体管尺寸D. 电阻值6.在设计集成电路时,以下哪种布局方法可以最小化信号传输延迟?A. 混合布局B. 紧凑布局C. 顺序布局D. 扇形布局7、数字选数字。

在模拟到数字转换电路中,使用最多的技术是()。

A、反相放大器B、运算放大器C、二极管放大器D、集成运放放大器8、数字选数字。

双极型晶体管在半导体工艺中,通常使用()掺杂技术。

A、P区掺杂B、N区掺杂C、平面掺杂D、表面掺杂9、设一款MMIC Amplifier电路的截止频率为10GHz,其放大倍数为20dB,则该放大器在1kHz处的增益 (以分贝为单位)A.约为20dBB.约为1.2dBC.约为0dBD.约为200dB 10、下列哪种晶体管的工作原理是基于电流的控制效果?A.MOSFETB.BJTTFETD.FinFET二、多项选择题(本大题有10小题,每小题4分,共40分)1.集成电路设计中,以下哪个因素对芯片性能影响最大?A. 电流大小B. 电压频率C. 电磁干扰D. 噪声大小2.在CMOS工艺中,以下哪种器件主要用于实现逻辑非功能?A. 二极管B. 晶体管C. 互连D. 电容3、集成电路设计中,每种不同类型的门电路都有其组成形式和特性方程,其中三态门(Out,tree)电路的特性方程,下述的英文表达准确的为:() A) Out = (A!) B) Out = ( *mc*ai) C) Out = ( ) is not the right choice D)Out = 0并且向上false4、某一电路的表达式为 Out = ( * ),( ) 表示废物符号,关于此电路的描述正确的是哪些?( ) A)只要有一个输入为1,则 Out=1,其 Low电平比单输出 t 高B)当 A,B,C 三个输入都为 0 时, Out=0 C)若 C=0,无论输入为0,1均不产生 anything D)三种输入相等时,三种条件下的结果一样5、下列关于 CMOS 集成电路的描述,哪些是正确的?( )A. CMOS 电路采用互补型 MOSFET 作为开关元件B. CMOS 电路在高速工作时功耗较低C. CMOS 电路主要用于模拟信号处理D. CMOS 电路在静态功耗方面较低6、下列关于设计流程中布局規劃的描述,哪些是正确的?( )A. 布局规划直接影响到芯片的性能B. 布局规划需要考虑每一级线路的容量C. 布局规划主要关心电路的功能实现D. 布局规划阶段可以随意修改电路结构7、在数字电路设计中,以下哪些电压类型是常见的逻辑门电压()。

(完整版)集成电路设计复习题及解答

集成电路设计复习题绪论1.画出集成电路设计与制造的主要流程框架。

2.集成电路分类情况如何?集成电路设计1.层次化、结构化设计概念,集成电路设计域和设计层次2.什么是集成电路设计?集成电路设计流程。

(三个设计步骤:系统功能设计逻辑和电路设计版图设计)3.模拟电路和数字电路设计各自的特点和流程4.版图验证和检查包括哪些内容?如何实现?5.版图设计规则的概念,主要内容以及表示方法。

为什么需要指定版图设计规则?6.集成电路设计方法分类?(全定制、半定制、PLD)7.标准单元/门阵列的概念,优点/缺点,设计流程8.PLD设计方法的特点,FPGA/CPLD的概念9.试述门阵列和标准单元设计方法的概念和它们之间的异同点。

10.标准单元库中的单元的主要描述形式有哪些?分别在IC设计的什么阶段应用?11.集成电路的可测性设计是指什么?Soc设计复习题1.什么是SoC?2.SoC设计的发展趋势及面临的挑战?3.SoC设计的特点?4.SoC设计与传统的ASIC设计最大的不同是什么?5.什么是软硬件协同设计?6.常用的可测性设计方法有哪些?7. IP的基本概念和IP分类8.什么是可综合RTL代码?9.么是同步电路,什么是异步电路,各有什么特点?10.逻辑综合的概念。

11.什么是触发器的建立时间(Setup Time),试画图进行说明。

12.什么是触发器的保持时间(Hold Time),试画图进行说明。

13. 什么是验证,什么是测试,两者有何区别?14.试画图简要说明扫描测试原理。

绪论1、 画出集成电路设计与制造的主要流程框架。

2、集成电路分类情况如何?集成电路设计1. 层次化、结构化设计概念,集成电路设计域和设计层次分层分级设计和模块化设计.将一个复杂的集成电路系统的设计问题分解为复杂性较低的设计级别,⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎩⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎧⎪⎪⎪⎪⎩⎪⎪⎪⎪⎨⎧⎩⎨⎧⎩⎨⎧⎪⎪⎪⎪⎩⎪⎪⎪⎪⎨⎧⎪⎪⎪⎪⎪⎪⎩⎪⎪⎪⎪⎪⎪⎨⎧⎩⎨⎧⎪⎪⎪⎪⎩⎪⎪⎪⎪⎨⎧⎩⎨⎧⎪⎩⎪⎨⎧按应用领域分类数字模拟混合电路非线性电路线性电路模拟电路时序逻辑电路组合逻辑电路数字电路按功能分类GSI ULSI VLSI LSI MSI SSI 按规模分类薄膜混合集成电路厚膜混合集成电路混合集成电路B iCMOS B iMOS 型B iMOS CMOS NMOS PMOS 型MOS双极型单片集成电路按结构分类集成电路这个级别可以再分解到复杂性更低的设计级别;这样的分解一直继续到使最终的设计级别的复杂性足够低,也就是说,能相当容易地由这一级设计出的单元逐级组织起复杂的系统。

大规模集成电路习题与答案

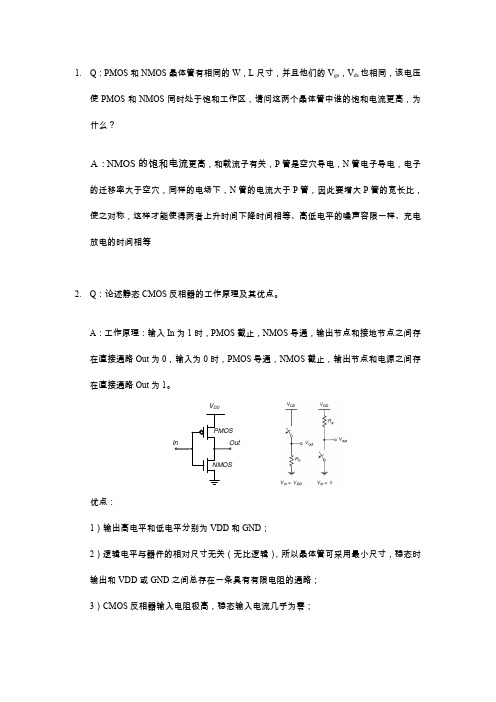

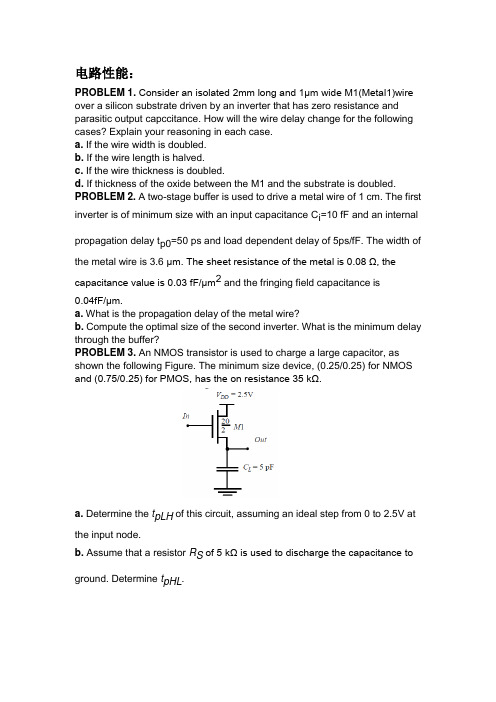

电路性能:PROBLEM 1. Consider an isolated 2mm long and 1μm wide M1(Metal1)wire over a silicon substrate driven by an inverter that has zero resistance and parasitic output capccitance. How will the wire delay change for the following cases? Explain your reasoning in each case.a. If the wire width is doubled.b. If the wire length is halved.c. If the wire thickness is doubled.d. If thickness of the oxide between the M1 and the substrate is doubled. PROBLEM 2. A two-stage buffer is used to drive a metal wire of 1 cm. The first inverter is of minimum size with an input capacitance C i=10 fF and an internalpropagation delay t p0=50 ps and load dependent delay of 5ps/fF. The width of the metal wire is 3.6 μm. The sheet resistance of the metal is 0.08 Ω, the capacitance value is 0.03 fF/μm2 and the fringing field capacitance is0.04fF/μm.a. What is the propagation delay of the metal wire?b. Compute the optimal size of the second inverter. What is the minimum delay through the buffer?PROBLEM 3. An NMOS transistor is used to charge a large capacitor, as shown the following Figure. The minimum size device, (0.25/0.25) for NMOS and (0.75/0.25) for PMOS, has the on resistance 35 kΩ.a. Determine the t pLH of this circuit, assuming an ideal step from 0 to 2.5V at the input node.b. Assume that a resistor R S of 5 kΩ is used to discharge the capacitance toground. Determine t pHL.c. The NMOS transistor is replaced by a PMOS device, sized so that k p is equal to the k n of the original NMOS. Will the resulting structure be faster? Explain why or why not.PROBLEM 4.The figure below assembles a RTL circuit where the active device is a NMOS transistor which has a resistive load. Assume the switch model behavior of the NMOS transistor. When V in <1.25V, the resistance of the transistor is infinite. When V in ≥1.25V, the transistor can be modeled as having a resistance of 150 ohms.A. Determine the values for V OH and V OL . Explain your answer.B. Calculate t pLH and t pHL to obtain the average propagation delay, t p .Solution:Vin 50fFPROBLEM 5. The next figure shows two implementations of MOS inverters. The first inverter uses only NMOS transistors.a. Calculate V OH, V OL, V th for each case.b. Find V IH, V IL, N ML and N MH for each inverter and comment on the results. How can you increase the noise margins and reduce the undefined region? 0.25um CMOS工艺(L=Lmin) MOS管参数Problem 6: We want to design a minimum sized CMOS inverter with 0.25um process( =0.12um). The minimum sized NMOS transistor ’s layers are listed and shown below in Figure below.A. Determine and list the following:a. Minimum Transistor Lengthb. Minimum Transistor Widthc. Minimum Source/Drain Aread. Minimum Source/Drain PerimeterPlease list the design rules you come across that lead to your results.B. We desire the minimum sized CMOS inverter with a symmetrical VTC (V Th =V DD /2) in the 0.25um technology. Calculate the following for the pull-up PMOS transistor in the design.a. Minimum Transistor Lengthb. Minimum Transistor Widthc. Minimum Source/Drain Aread. Minimum Source/Drain PerimeterAssume the following:V DD = 2.5V, and refer to the tables in the below.C. Using the same minimum size inverter from part B, determine the input capacitance (i.e. the load it presents when driven) and the total load capacitance that the inverter presents.D. Calculate t pLH and t pHL to obtain the average propagation delay, t p .Rules are:i) Poly minimum width = 0.24umii) Minimum active width = 0.36umiii) Minimum contact size = 0.24um*0.24umiv) Minimum spacing from contact to gate = 0.24umv) Active enclosure of contact = 0.12umAnswer:A:a. L = 0.24umb. W = 0.48umc. L drain = 0.24um+0.24um+0.12um = 0.6umA D =A S = 0.48 * 0.6um = 0.288 um 2d. P D =P S =0.6um*2+0.48um = 1.68umB:2n T0,Th Th p T0,DD p n R R R p T0,DD n T0,Th V V V V V k k 得出k k 11k 1)V (V V V ⎪⎪⎭⎫ ⎝⎛--+==+⋅++=查表得出一下参数:V T0p = -0.43V V T0n = 0.4V K n ’=115×10-6 A/V 2 K p ’=30×10-6A/V 2 另:L=0.24um, W n =0.48um带入上述公式计算得出:K R =0.965 W p =1.907umWe assume u n =2.5u p and can calculatea. Lp=0.24µmb. W p = 1.907 µmc. A D = 1.907µm *0.6µm =1.1442 µm 2d. P D = 2*0.6µm +1.2µm =3.107 µmC:NMOS:C gn = C ox L n W n = 0.6912 fFNMOS 管衬底接0V ,输出从1→0(V 1=-2.5V 变为V 2=-1.25V):()()()[]()()()[]0.615264fFC C C fF0.2869940.61281.68K C P C 0.44m 0.61V φV φm)(1V V φK fF 32832057022880K C A C 0.5m 0.57V φV φm)(1V V φK dbsw db dbn1eqsw j D dbsw m 11bsw m 12bsw 12m bsw eq eq j D db m 11b m 12b 12m b eq =+==⨯⨯====---⋅----==⨯⨯====---⋅----=----.0侧壁:...底部:输出从0→1(V 1=0V 变为V 2=-1.25V):()()()[]()()()[]fF0.836064C C C fF0.3810240.81281.68K C P C 0.44m 0.81V φV φm)(1V V φK fF 0.455040.7920.288K C A C 0.5m 0.79V φV φm)(1V V φK dbsw db dbn2eqsw j D dbsw m 11bsw m 12bsw 12m bsw eq eq j D db m 11b m 12b 12m b eq =+==⨯⨯====---⋅----==⨯⨯====---⋅----=----.0侧壁:底部:PMOS:C gp = C ox L p W p ) =2.74608 fFPMOS 管衬底接2.5V ,输出从1→0(V 1= 0V 变为V 2=-1.25V):()()()[]()()()[]fF2C C C fF0.58784440.8622K C P C 0.32m 0.86V φV φm)(1V V φK fF 10.7911K C A C 0.48m 0.79V φV φm)(1V V φK dbsw db dbp1eqsw j D dbsw m 11bsw m 12bsw 12m bsw eqsw eq j D db m 11b m 12b 12m b eq 3052886..0109.3侧壁:7174442.9.1442.=+==⨯⨯====---⋅----==⨯⨯====---⋅----=----底部:输出从0→1(V 1=-1.25V 变为V 2= -2.5V):()()()[]()()()[]fF1.7614342C C C fF0.4787860.70.223K C P C 0.32m 0.7V φV φm)(1V V φK fF 10.591.91K C A C 0.48m 0.59V φV φm)(1V V φK dbsw db dbp2eqsw j D dbsw m 11bsw m 12bsw 12m bsw eqsw eq j D db m 11b m 12b 12m b eq =+==⨯⨯====---⋅----==⨯⨯====---⋅----=----109.侧壁:2826482.1442.底部:如果m 以0.5计算:NMOS 管衬底接0V ,输出从1→0(V 1=-2.5V 变为V 2=-1.25V):()()()[]0.596448fFC C C fF0.268120.57281.68K C P C fF 32832057022880K C A C 0.57V φV φm)(1V V φK K dbsw db dbn1eqsw j D dbsw eq j D db m 11b m 12b 12m b eqsw eq =+==⨯⨯===⨯⨯===---⋅----==--.0...底部: 输出从0→1(V 1=0V 变为V 2=-1.25V):()()()[]fF0.826656C C C fF0.3716160.79281.68K C P C fF0.455040.7920.288K C A C 0.79V φV φm)(1V V φK K dbsw db dbn2eqsw j D dbsw eq j D db m 11b m 12b 12m b eqsw eq =+==⨯⨯===⨯⨯===---⋅----==--.0底部:PMOS 管衬底接2.5V ,输出从1→0(V 1= 0V 变为V 2=-1.25V):()()()[]fF 2C C C fF0.54034420.7922K C P C fF1.71744420.79911K C A C 0.79V φV φm)(1V V φK K dbsw db dbp1eqsw j D dbsw eq j D db m 11b m 12b 12m b eqsw eq 2577884..0109.3.1442.=+==⨯⨯===⨯⨯===---⋅----==--底部:输出从0→1(V 1=-1.25V 变为V 2= -2.5V):()()()[]fF 1.6290372C C C fF0.38986860.570.22K C P C fF10.571.91K C A C 0.57V φV φm)(1V V φK K dbsw db dbp2eqsw j D dbsw eq j D db m 11b m 12b 12m b eqsw eq =+==⨯⨯===⨯⨯===---⋅----==--109.32391686.1442.底部:D :C load 计算:C load =C wire +C g +C gd,n +C gd,p +C db,n +C db,p≈C g +C db,n +C db,pC g = C gn + C gp =0.6912+2.74608=3.43728 fF输出从1→0(V 1= 0V 变为V 2=-1.25V):C load≈C g +C db,n +C db,p =6.3578326 fF16.32ps1V )V 4(V ln V V 2V )V (V k C A/V 10230k L W k DD T0n DD T0n DD T0n T0n DD n load PHL 26'n nn n =⎥⎦⎤⎢⎣⎡⎪⎪⎭⎫ ⎝⎛--+--=⨯=⨯=-τ 输出从0→1(V 1=-1.25V 变为V 2= -2.5V):C load≈C g +C db,n +C db,p =6.0347782 fF15.33ps 1V )V 4(V ln V V V 2)V (V k C A/V 10238.375k L W k DD T0p DD T0pDD T0p T0pDD p load PLH 26'p p p p =⎥⎥⎦⎤⎪⎪⎭⎫ ⎝⎛--+⎢⎢⎣⎡--=⨯=⨯=-τ如果以m=0.5,则:输出从1→0(V 1= 0V 变为V 2=-1.25V):C load≈C g +C db,n +C db,p =6.2915162 fF16.147ps1V )V 4(V ln V V 2V )V (V k C DD T0n DD T0n DD T0n T0n DD n load PHL =⎥⎦⎤⎢⎣⎡⎪⎪⎭⎫ ⎝⎛--+--=τ 输出从0→1(V 1=-1.25V 变为V 2= -2.5V):C load≈C g +C db,n +C db,p =5.8929732 fFps 1V )V 4(V ln V V V 2)V (V k C DD T0p DD T0p DD T0p T0pDD p load PLH 97.14=⎥⎥⎦⎤⎪⎪⎭⎫ ⎝⎛--+⎢⎢⎣⎡--=τ PROBLEM 7.We want to design a minimum sized CMOS inverter with 0.25um process(λ=0.12um) and desire the inverter with a symmetrical VTC (V Th =V DD /2) . The minimum sized NMOS transistor’s layers are shown as problem 6. Assume the following:V DD = 2.5V, and refer to the tables in the below.A. Determine the input capacitance (i.e. the load it presents when driven) and the total load capacitance that the inverter presents.B. Calculate t pLH and t pHL to obtain the average propagation delay, t p .PROBLEM 8. Sizing a chain of inverters.a. In order to drive a large capacitance (CL = 20 pF) from a minimum size gate (with input capacitance Ci = 10fF), you decide to introduce a two-staged buffer as shown in the following figure. Assume that the propagation delay of a minimum size inverter is 70 ps. Also assumethat the input capacitance of a gate is proportional to its size. Determine the sizing of the two additional buffer stages that will minimize the propagation delay.b. If you could add any number of stages to achieve the minimum delay, how many stages would you insert?What is the propagation delay in this case?c. Describe the advantages and disadvantages of the methods shown in (a) and (b).PROBLEM 9. Consider a CMOS inverter with the following parameters:V T0,n=1.0V V T0,p=-1.2V μn C ox=45uA/V2μp C ox=25uA/V2 (W/L)n=10 (W/L)p=20The power supply voltage is 5V, and the output load capacitance is 1.5pF.a. Calculate the rise time and the fall time of the output signal using average current method.b. Determine the maximum frequency of a periodic square-wave input signal so that the output voltage can still exhibit a full logic swing from 0V to 5V in each cycle.c. Calculate the dynamic power dissipation at this frequency.d. Assume that the output load capacitance is mainly dominated by fixedfan-out component( which are independent of W n and W p). We want tore-design the inverter so that the propagation delay times are reduced by 25%. Determine the required channel dimensions of the nMOS and the pMOS transistors. How does this re-design influence the switching (inversion) threshold?PROBLEM 10. Consider the following low swing driver consisting of NMOS devi ces M1 and M2. Assume that the inputs IN and IN’ have a 0V to 2.5V swing and that V IN = 0V when V IN’ = 2.5V and vice-versa. Also assume thatthere is no skew between IN and IN’ (i.e., the inverter delay to derive IN from IN is zero).a. What voltage is the bulk terminal of M2 connected to?b. What is the voltage swing on the output node as the inputs swing from 0V to2.5V. Show the low value and the high value.c. Assume that the inputs IN and IN have zero rise and fall times. Assume a zero skew between IN and IN’. Determine the low to high propagation delay for charging the output node measured from the the 50% point of the input to the 50% point of the output. Assume that the total load capacitance is 1pF, including the transistor parasitics.MOS管参数参照题4。

大规模集成电路设计题目及答案

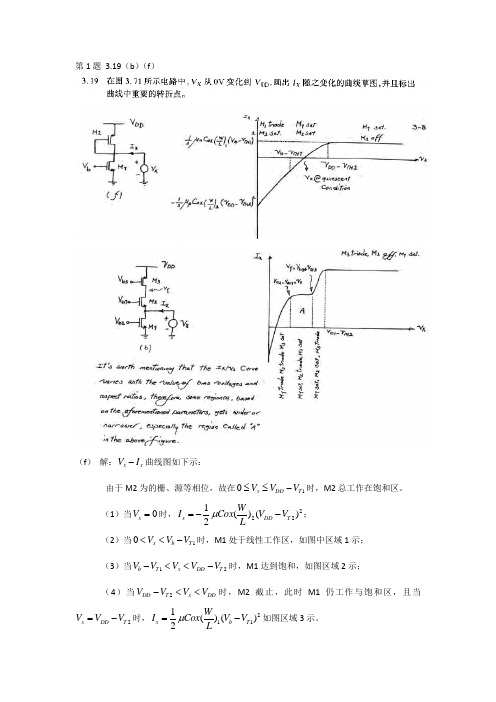

第1题 3.19(b )(f )(f ) 解:x x V I -曲线图如下示:由于M2为的栅、源等相位,故在10x DD T V V V ≤≤-时,M2总工作在饱和区。

(1)当0x V =时,2221()()2x DD T WI Cox V V Lμ=--; (2)当10x b T V V V <<-时,M1处于线性工作区,如图中区域1示; (3)当12b T x DD T V V V V V -<<-时,M1达到饱和,如图区域2示;(4)当2DD T x DD V V V V -<<时,M2截止,此时M1仍工作与饱和区,且当2x DD T V V V =-时,2111()()2x b T WI Cox V V Lμ=-如图区域3示。

(b )解:x x V I -曲线图如下示:(1)当0x V =时,此时M3接DD V 使其饱和,而M1、M2漏源所加电压为零,工作于线性工作区。

当x V 上升至21b T V V -时,M1达到饱和,故当210x b T V V V <<-时,M1、M2工作于线性工作区,M3处于饱和状态,电流变化曲线如区域1所示;(2)随着x V 的继续升高,Y V 也将升高,且当其等于33b T V V +时,此时的M3将由饱和区转为线性工作区,设此时对应的x V 记为xY V ,因此当21b T x xY V V V V -<<时,M1、M3工作于饱和区,M2工作与线性放大区,如图中区域2示。

由于Y V 的变化幅度各个MOS 管的参数有很大的关系,因此此区域的面积有很大的可变性;(3)M3工作于饱和的临界条件为12x b T V V V =-,因此当12xY x b T V V V V <<-时,M1、M2工作于饱和区,M3处于线性工作区,如图中区域3示;(4)当12b T x DD V V V V -<<时,M2关断,M1处于饱和,M3工作于线性放大区,如图中区域4示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC,SSI)•中规模集成电路(Medium Scale IC,MSI)•大规模集成电路(Large Scale IC,LSI)•超大规模集成电路(Very Large Scale IC,VLSI)•特大规模集成电路(Ultra Large Scale IC,ULSI)•巨大规模集成电路(Gigantic Scale IC,GSI)划分集成电路规模的标准2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得.3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。

1、形成N阱2、形成P阱3、推阱4、形成场隔离区5、形成多晶硅栅6、形成硅化物7、形成N管源漏区8、形成P管源漏区9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么?互连线的要求低电阻值:产生的电压降最小;信号传输延时最小(RC时间常数最小化)与器件之间的接触电阻低长期可靠工作可能的互连线材料金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率)5.在进行版图设计时为什么要制定版图设计规则?—片集成电路上有成千上万个晶体管和电阻等元件以及大量的连线。

描述这些基本单元的版图,是一系列几何图形有规则的排列。

为了保证由这些基本单元及其相互连线构成的版图能够在工艺线上生产出来,必须制定版图设计规则。

在芯片尺寸尽可能小的前提下,使得即使存在工艺偏差也可以正确的制造出IC,尽可能地提高电路制备的成品率。

6.版图验证和检查主要包括哪些方面?DRC(Design Rule Check):几何设计规则检查;对IC的版图做几何空间检查,保证能在特定的工艺条件下实现所设计的电路,并保证一定的成品率;ERC(Electrical Rule Check):电学规则检查;检查电源(power)/地(ground)的短路,浮空的器件和浮空的连线等指定的电气特性;LVS(Loyout versus Schematic):网表一致性检查;将版图提出的网表和原理图的网表进行比较,检查电路连接关系是否正确,MOS晶体管的长/宽尺寸是否匹配,电阻/电容值是否正确等;LPE(Layout Parameter Extraction):版图寄生参数提取;从版图中提取晶体管的尺寸、结点的寄生电容、连线的寄生电阻等参数,并产生SPICE 格式的网表,用于后仿真验证;POSTSIM:后仿真,检查版图寄生参数对设计的影响;提取实际版图参数、电阻、电容,生成带寄生量的器件级网表,进行开关级逻辑模拟或电路模拟,以验证设计出的电路功能的正确性和时序性能等,并产生测试向量。

7.版图设计规则是根据什么制定出来的?为什么说它是集成电路的性能和集成度与成品率之间的折衷?从图形如何精确地光刻到芯片上出发,可以确定一些对几何图形的最小尺寸限制规则,这些规则被称为设计规则。

设计规则是电路性能和成品率之间的折中,设计规则保守则成品率高,但电路面积大、性能差一些;设计规则激进,则电路性能好、面积小,但成品率低。

8.简述λ设计规则与微米设计规则各自的优缺点?以λ为单位:把大多数尺寸(width,space等等)约定为λ的倍数λ与工艺线所具有的工艺分辨率有关,是线宽偏离理想特征尺寸的上限以及掩膜版之间的最大套准偏差,一般等于栅长度的一半。

优点:版图设计独立于工艺和实际尺寸,改变λ值就可以得到不同的设计规则;缺点:容易造成芯片面积浪费和工艺难度增加;以微米为单位:现代IC设计普遍采用的方法,每个尺寸之间没有必然的比例关系,提高每一尺寸的合理程度;简化度不高。

9.标准单元法与门阵列法比较有何优点和缺点?标准单元法与门阵列法比较有明显的优点:(1) 芯片面积的利用率比门阵列法要高。

芯片中没有无用的单元,也没有无用的晶体管。

(2) 可以保证100%的连线布通率。

(3) 单元可以根据设计要求临时加以特殊设计并加入库内,因而可以得到较佳的电路性能。

(4) 可以与全定制设计法相结合功能块。

在芯片内放入经编译得到的宏单元或人工设计的功能块。

标准单元法也存在缺点和问题;(1) 原始投资大。

单元库的开发需要投入大量的人力物力;当工艺变化时,单元的修改工作需要付出相当大的代价。

因而如何建立一个在比较长的时间内能适应技术发展的单元库是一个突出问题。

(2) 成本较高。

由于掩膜版带要全部定制,芯片的加工也要经过全过程,因而成本较高。

因此只有芯片产量达到某一定额(几万至十几万),其成本才可接受。

10.随着工艺进入深亚微米,IC器件的物理实现出现了哪些方面的变化?随着工艺进入深亚微米,IC器件的物理实现出现了以下3个方面的变化:(1) 逻辑单元的几何尺寸和逻辑单元之间的距离随着特征尺寸的减小而减小,从而使总延时减小。

(2) 由于特征尺寸的减小,导线电阻增加。

为了抵消导线横向尺寸的减小,导线侧向尺寸即厚度被适度增加,以使导线电阻的增加不至于过大,从而导致纵向分布电容和边缘分布电容的增加,这两种分布电容都具有导致导线间耦合的性质。

(3) 连线延时(主要是侧向分布电容和边缘分布电容引入的延时)在总延时中占据了主导地位,而输入延时也由于工作频率的提高而变得不容忽视。

11.FPGA与CPLD有何相似之处和不同之处?FPGA是CPLD的一个发展最快的分支,复杂的可编程逻辑器件CPLD是由PLD或GAL发展而来. CPLD延伸出两大分支,即可擦除可编程的逻辑器件EPLD和现场可编程门阵列器件FPGA.中的数据丢失。

因此,需在FPGA外加EPROM,将配置数据写入其中,系统每次上电自动将数据引入SRAM 中。

CPLD器件一般采用EEPROM存储技术,可重复编程,并且系统掉电后,EEPROM中的数据不会丢失,适于数据的保密。

3.FPGA器件含有丰富的触发器资源,易于实现时序逻辑,如果要求实现较复杂的组合电路则需要几个CLB结合起来实现。

CPLD的与或阵列结构,使其适于实现大规模的组合功能,但触发器资源相对较少。

4.FPGA为细粒度结构,CPLD为粗粒度结构。

5.FPGA为非连续式布线,CPLD为连续式布线。

12.可测试性设计的对象是什么?为什么要从事VLSI的可测试性设计?电路的可控制性和可观察性。

Pin数目有限,大量芯片内部的信息无法访问。

在尽可能少地增加附加引线脚和附加电路,并使芯片性能损失最小的情况下,满足电路可控制性和可观察性的要求。

13. 为什么说MOS 管的工作速度与2L 成反比?提高MOS 管的工作速度方法有哪些?(见18题答案)14.某CMOS 电路负载电容近似等于g C e 8,g C 为标准反相器栅电容。

已知标准反相器的平均延迟时间ns t av 2=。

试求:(1)用标准反相器直接驱动负载电容的延迟时间。

(2)用逐级放大反相器直接驱动负载电容的最小延迟时间。

15.什么是可测性设计?可测性设计包括哪些技术?可测试性包括哪些重要方面? 可测性设计: 在尽可能少地增加附加引线脚和附加电路,并使芯片性能损失最小的情况下,满足电路可控制性和可观察性的要求。

可测性设计技术:主要包括分块测试技术、扫描测试技术、特征量分析分块测试技术、边界扫描分块测试技术等。

可测试性的三个重要方面:故障模型的提取:将电路失效抽象为故障模型。

测试生成:产生验证电路的一组测试矢量。

测试设计:考虑测试效率问题,加入适当的附加逻辑或电路以提高芯片的测试效率。

16.目前VLSI 系统设计普遍采用的方法是什么?它的基本思想什么?试列举几种设计方法。

可编程逻辑器件设计方法(PLD 方法)。

用户通过生产商提供的通用器件自行进行现场编程和制造,或者通过对与或矩阵进行掩膜编程,得到所需的专用集成电路。

PLA 、PAL 和GAL FPGA 和CPLD17.半定制设计方法可分为哪几种方法?它们各自的特点和不足之处是什么?半定制的设计方法分为门阵列(GA :Gate Array )法和门海(GS :Sea of Gates )法两种。

门阵列方法的设计特点:设计周期短,设计成本低,适合设计适当规模、中等性能、要求设计时间短、数量相对较少的电路。

不足:设计灵活性较低;门利用率低;芯片面积浪费。

门海方法的设计特点:门利用率高,集成密度大,布线灵活,保证布线布通率。

不足:仍有布线通道,增加通道是单元高度的整数倍,布线通道下的晶体管不可用。

18.试分析提高MOS 管工作速度方法。

1. 提高IC 加工精度 减小沟道长度. 2. 加强MOS 管的驱动电压(Vgs-Vt ),可以减小管子的内阻,加快工作速度。

3. 由于 ,所以NMOS 管的工作速度比PMOS 管快得多。

可以用NMOS 工艺代替PMOS 工艺。

19.画出C M O S 反相器电压传输特性曲线图,并写出相应的电流方程。

电流方程如下:设 Vtp=-Vtn2.5n p μμ≈。