北京邮电大学1997年试题 TTL与非门的开门电平和关门电平的大小

数字电子技术综合试题

《数字电子技术》综合试题(A)一、单选题(每题1分)1. 二进制数1110111.11转换成十进制数是 ( )。

A .119. 125B .119. 3C .119 . 375D .119.75 2. 已知逻辑函数的真值表如下,用卡诺图化简其逻辑表达式是( )。

A .C Y = B .ABC Y = C .C AB Y += D .C AB Y +=图1-13. 下列逻辑门类型中,可以用( )一种类型门实现另三种基本运算。

A .与门B .非门C .或门D .与非门 4. 根据反演规则,E DE C C A Y ++⋅+=)()(的反函数为( )。

A. E E D C C A Y ⋅++=)]([B. E E D C C A Y ⋅++=)(C. E E D C C A Y ⋅++=)(D. E E D C C A Y ⋅++=)( 5. 为实现数据传输的总线结构,要选用( )门电路。

A 或非 B OC C. 三态 D 与或非6. 输出端可直接连在一起实现“线与’’逻辑功能的门电路是( )。

A 与非门B 或非门C 三态门D OC 门7. TTL 与非门的关门电平是0.8V ,开门电平是2V ,当其输入低电平为0.4V ,输入高电平为3.2V 时, 其低电平噪声容限为( )。

A 0.4VB 1.2VC 1.8VD 2.4V 8. 门电路的平均传输延迟时间是( )。

C t pd =(t PHL + t PLH )/2 D t pd =(t PHL - t PLH )/29. 维持一阻塞D触发器是( )。

A下降沿触发 B上升沿触发C高电平触发 D低电平触发10. 能把缓慢变化的输入信号转换成矩形波的电路是 ( )。

A 单稳态触发器;B 多谐振荡器;C 施密特触发器;D 边沿触发器二、判断题(每题1分)1. 格雷码具有任意两组相邻代码之间只有一位不同的特性。

()2. 逻辑函数表达式的化简结果是唯一的。

电子线路基础数字电路试验2TTL与非门逻辑功能及参数测试

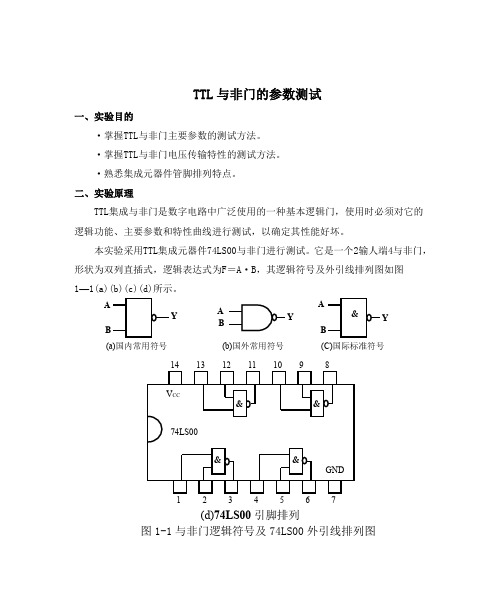

实验二TTL与非门逻辑功能及参数测试一、实验目的1、熟悉TTL与非门外型和管脚引线排列。

2、掌握TTL门电路逻辑功能测试方法。

3、掌握TTL门电路传输特性及主要参数的测试方法。

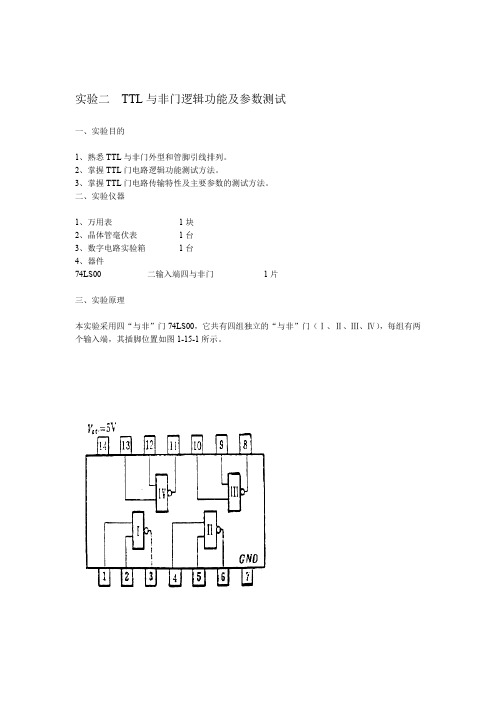

二、实验仪器1、万用表1块2、晶体管毫伏表1台3、数字电路实验箱1台4、器件74LS00 二输入端四与非门1片三、实验原理本实验采用四“与非”门74LS00,它共有四组独立的“与非”门(Ⅰ、Ⅱ、Ⅲ、Ⅳ),每组有两个输入端,其插脚位置如图1-15-1所示。

图1-15-1 74LS00引线排列图1-15-2 74LS00与非门(一组)每组的构造和逻辑功能相同。

现以其中一组说明如下:TTL与非门电路如图1-15-2所P AB “与非”TTL。

为输出端。

逻辑功能为P为“与非”门的二个输入端,B和A示。

.门的主要参数有:1、扇入系数N和扇出系数N:能使电路正常工作的输入端数目称为扇入系数N,电i0i路正常工作时能带动的同类门的数目称为扇出系数N。

02、输出高电平V:一般V≥3V。

OHOH3、输出低电平V:一般V≤0.3V。

OLOL4、电压传输特性曲线,开门电平V和关门电平V:图1-15-3所示之V~V关系曲0ONOFFi线称为电压传输特性曲线。

使输出电压V刚刚达到低电平V时的最低输入电压V称为开i0OL门电平V。

使输出电压V刚刚达到高电平V时的输入电压V称为关门电平V。

OFFOHON0i图1-15-3 电压传输特性曲线图1-15-4 输出波形延迟于输入波形5、输入短路电流I:一个输入端接地,其它输入端悬空时,流过该接地输入端的电流RD为输入短路电流I。

RD6、空载导通功耗P:指输入全部为高电平输出为低电平时的功率损耗。

ON7、空载截止功耗P:指输入为低电平输出为高电平时的功率损耗。

OFF8、抗干扰噪声容限:电路能够保持正确的逻辑关系所允许的最大干扰电压值,称为噪声容限。

其中输入低电平时的噪声容限为V=V-V,而输入高电平时的噪声容限为ILNLOFF V=V-V。

例1某TTL与非门电压传输特性如图2-1(精)

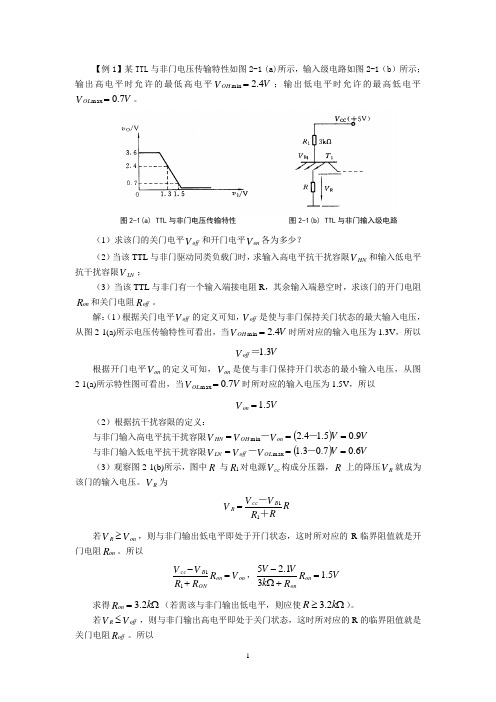

【例1】某TTL 与非门电压传输特性如图2-1 (a)所示,输入级电路如图2-1(b )所示;输出高电平时允许的最低高电平V V OH 4.2min =;输出低电平时允许的最高低电平V V OL 7.0max =。

图2-1(a) TTL 与非门电压传输特性 图2-1(b) TTL 与非门输入级电路(1)求该门的关门电平V off 和开门电平V on 各为多少?(2)当该TTL 与非门驱动同类负载门时,求输入高电平抗干扰容限V HN 和输入低电平抗干扰容限V LN ;(3)当该TTL 与非门有一个输入端接电阻R ,其余输入端悬空时,求该门的开门电阻R on 和关门电阻R off 。

解:(1)根据关门电平V off 的定义可知,V off 是使与非门保持关门状态的最大输入电压,从图2-1(a)所示电压传输特性可看出,当V V OH 4.2min =时所对应的输入电压为1.3V ,所以V V off 3.1=根据开门电平V on 的定义可知,V on 是使与非门保持开门状态的最小输入电压,从图2-1(a)所示特性图可看出,当V V OL 7.0max =时所对应的输入电压为1.5V ,所以V V on 5.1=(2)根据抗干扰容限的定义:与非门输入高电平抗干扰容限()V V V V V on OH HN 9.05.14.2min ===-- 与非门输入低电平抗干扰容限()V V V V V OL off LN 6.07.03.1max ===--(3)观察图2-1(b)所示,图中R 与R 1对电源V cc 构成分压器,R 上的降压V R 就成为该门的输入电压。

V R 为RR R V V V B cc R +-11=若V V on R ≥,则与非门输出低电平即处于开门状态,这时所对应的R 临界阻值就是开门电阻R on 。

所以V R R R V V on on ON B cc =+-11,V R R k V V on on5.131.25=+Ω- 求得Ω=k R on 2.3(若需该与非门输出低电平,则应使Ω≥k R 2.3)。

TTL与非门主要外部特性参数

TTL与非门主要外部特性参数2.主要外部特性参数TTL与非门的主要外部特性参数有输出逻辑电平、开门电平、关门电平、扇入系数、扇出系数、平均传输时延和空载功耗等。

(1)输出高电平V oH:输出高电平V oH是指至少有一个输入端接低电平时的输出电平。

V oH的典型值是3.6V。

产品规范值为V oH≥ 2.4V,标准高电平V SH=2.4V。

(2)输出低电平V oL:输出低电平V oL是指输入全为高电平时的输出电平。

V oL的典型值是0.3V,产品规范值为V oL≤ 0.4V,标准低电平V SL= 0.4V。

(3)开门电平V ON:开门电平V ON是指在额定负载下,使输出电平达到标准低电平V SL的输入电平,它表示使与非门开通的最小输入电平。

V ON的典型值为1.5V,产品规范值为V ON≤1.8V。

开门电平的大小反映了高电平抗干扰能力,V ON愈小,在输入高电平时的抗干扰能力愈强。

(4)关门电平V OFF:关门电平V OFF是指输出空载时,使输出电平达到标准高电平V SH的输入电平,它表示使与非门关断所允许的最大输入电平。

V OFF的典型值为1V,产品规范值V OFF≥ 0.8V。

关门电平的大小反映了低电平抗干扰能力,V OFF越大,在输入低电平时的抗干扰能力越强。

(5)扇入系数N i:扇入系数N i是指与非门允许的输入端数目。

一般N i为2~5,最多不超过8。

(6)扇出系数N o:扇出系数N o是指与非门输出端连接同类门的最多个数。

它反映了与非门的带负载能力。

一般N o≥ 8。

扇入和扇出是反映门电路互连性能的指标。

(7)输入短路电流I iS:输入短路电流I iS是指当与非门的某一个输入端接地而其余输入端悬空时,流过接地输入端的电流。

在实际电路中,I iS是流入前级与非门的灌电流,它的大小将直接影响前级与非门的工作情况。

因此,对输入短路电流要加以限制,产品规范值I iS≤1.6mA。

(8)高电平输入电流I iH:高电平输入电流I iH是指某一输入端接高电平,而其他输入端接地时,流入高电平输入端的电流,又称为输入漏电流。

《数字逻辑》第3章作业与习题_单选题第六小题已更正版本

。

20.如果某 TTL 与非门的输入低电平噪声容限 VNL=0.7V,输入低电平

ViL=0.2V,那么它的关门电平 Voff 为

。

21.对于或非门,只要有一个输入为高电平,则输出就为 电平,所以

对或非门多余输入端的处理不能接 电平。

22.对于 TTL 与非门,只要有一个输入为低电平,则输出就为 电平,

为

,按抗干扰能力强弱的顺序依次为

,按静态功耗低和高的顺序依次为

。

6. 假设 VGS(TH)为开启电压,一般在 1~3V 范围内,则 NMOS 管当

时

截止,当

时导通;PMOS 管当

时截止,当

时

导通。

7. CMOS 反相器是由

作为驱动管,

作为负载管形成了 电

路结构。

2)单选题

1.硅二极管导通和截止的条件是( )。

不形成

;在外电场作用下,

和

均能参与导电。

7. 半导体中载流子的两种运动方式指

运动和

运动。

8. 硅二极管的截止条件是

,导通条件是

。

9. 数字电路中的晶体三极管作为开关元件,主要工作在

和

。

10. 三种基本逻辑门是

、

、

。

11. 与门是可以实现

的电路。

12. 在 TTL 电路中,输入端悬空等效于逻辑 电平,但为了避免引入干

② 输出端能带同类门的输入端个数

③ 输出端能带同类门的个数

④ 输入端数

7.输出端可直接连在一起实现“线与”逻辑功能的门电路是( )。

① 与非门

② 或非门 ③ OC 门

④ 异或门

8.两输入变量 A、B 的逻辑门的输出、输入如图所示,根据输出波形 Y,该

数字电子技术基础课后习题答案第2章习题答案

思考题:题2.1.1 答:肖特基二极管(SBD)、分流。

题2.1.2 答:基区、滞后。

题2.1.3 答:(A)、(B) 。

题2.1.4 答:对。

题2.2.1 答:A、B。

题2.2.2 答:C、D。

题2.2.3 答:4ns。

题2.2.4 答:(A)、(C)、。

题2.2.5 答:降低、降低。

题2.2.6 答:0、1和三态题2.2.7 答:若一个输出高电平,另一个输出低电平时,会在T4和T5间产生一个大电流,烧毁管子。

OC门“线与”在输出接一电阻和一5-30V电源电压。

题2.2.8 答:能、分时。

题2.2.9 答:1. 为了缩短传输延迟时间,电路中使用肖特基管和有源泄放电路,另外,还将输入级的多发射极管改用SBD代替,由于SBD没有电荷存储效应,因此有利于提高电路的工作速度。

电路中还接入了D3和D4两个SBD,当电路的输出端由高电平变为低电平时,D4经T2的集电极和T5的基极提供了一条通路,一是为了加快负载电容的放电速度,二是为了加速T5的导通过程。

另外,D3经T2的集电极为T4的基极提供了一条放电通路,加快了T4的截止过程。

2. 为降低功耗,提高了电路中各电阻的阻值,将电阻R5原来接地的一端改接到输出端,以减小T3导通时电阻R5上的功耗。

题2.3.1 答:A。

题2.3.2 答:A。

题2.3.3 答:A。

题2.3.4 答:导通。

题2.3.5 答:B、C。

思考题:题2.4.1 答:(A)分流。

题2.4.2 答:(B) 内部电阻和容性负载。

题2.4.3 答:(B) 3.3V;(C)5V;(D) 30V。

题2.4.4 答:CMOS反相器和CMOS传输门。

题2.4.5 答:加入缓冲器保证输出电压不抬高或者降低,正逻辑变负逻辑或者相反,与非变成或非,或者或非变为与非。

题2.4.6 答:(C)低、高。

题2.4.7答:(A) OD门;(B) OC门;(C)三态门。

16题2.4.8 答:(A)驱动大负载;(B)电平移位。

TTL与非门参数测试

2.根据实验数据画出传输特性曲线,试在曲线上标出VOH、VOL、VON、VOFF,计算VNH和VNL。

六、思考题

1.TTL电路多余的输入端应如何处理?为什么?

与非门多余的输入端:①悬空;②接高电平;③与一个有效端接在一起。或非门多余的输入端①接地②与一个有效端接在一起。其原则是无效输入端不能影响输入和输出之间的逻辑关系。

表一

带负载

开路

VOH(V)

VOL(V)

VOH(V)

VOL(V)

3.59

0.296

4.04

0.08

(2)测量输入开门电平VON和关门电平VOFF

表二

VOH(V)

VOFF(V)

VOL(V)

VON(V)

3.59

1.14

0.296

1.92

(3)测量低电平输入电流IIL和高电平输入电流IIH;

表三

IIL(mA)

(4)输入开门电平VON和关门电平VOFF

VON是指与非门输出端接额定负载时,使输出处于低电平状态时所允许的最小输入电压。换句话说,为了使与非门处于导通状态,输入电平必须大于VON。

VOFF是指使与非门输出处于高电平状态所允许的最大输人电压。

(5)扇出系数N0

N0是说明输出端负载能力的一项参数,它表示驱动同类型门电路的数目。N0的大小主要受输出低电平时,输出端允许灌人的最大电流的限制,如灌人负载电流超出该数值,输出低电平将显著抬高,造成下一级逻辑电路的错误动作。

V0(V)

1.60

1.70

1.80

1.90

2.00

2.5

3.0

3.5

4.0

4.5

5.0

V0(V)

23TTL与非门

外接电阻RL的选择:

RL(min)<RL< RL(max)

三、三态输出“与非”门电路:

1、电路:

2、符号:

三、三态输出“与非”门电 路:

三态门的第三个状态:高阻。

使能控制端EN=1时,P=1, 三态门是一个与非门:

Y AB

使能控制端:EN=0时,P=0, D三导态通门,呈T高4截阻止状;态T。1导通,T5截止,

入下脉降冲延下迟降时沿间的t5pL0H%:,从到输 输出脉冲上升沿的50%所 持续的时间。

平均传输延迟时间:

tpd=( tpHL + tpLH )/2:

7、电压传输特性:

8、主要参数值:

参数 UOHmin UOLmax IOHmax IOLmin UIHmin UILmax IIH

器件类型

(V) (V) (mA) (mA) (V) (V) (uA)

符号:

输出端直接 并联:

二、集电极开路“与非”门电路(OC 门):

1、电路:

二、集电极开路“与非”门电路(OC 门): 2、符号:

3、OC门的应用: 1)输出端可以直 接并联; 2)可以控制输出 电平。

4、OC门的应用举例: 1)输出端直接并联的“线与”功能:

2)外接电阻RL与外接电源VCC’:

ห้องสมุดไป่ตู้

2、电压传输特性:

CMOS非门(又称CMOS 反向器)的传输特性 入图,由于T1和T2的特性完全对称,所以ui= 1/2VDD时两管的导通内阻相等,uO=1/2VDD,即 工作电压传输特性转折的中点。因此, CMOS 反 向器的阈值电压为:VTH=1/2 VDD。

3、 CMOS与非门:

CMOS与非门用两个是P沟道增强型MOS管T1、 T3并联、两个N沟道增强型MOS管T2、T4串联构成 的。 工作情况如表:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

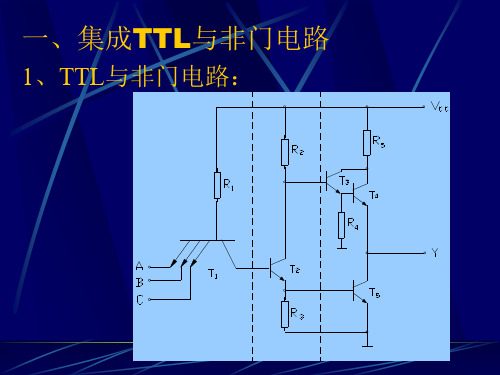

北京邮电大学1997年试题TTL与非门的开门电平和关门电平的大小,将直接影响器件的哪个性能指标?(A)抗干扰能力(B)输出电平(C)高电平负载能力(D)扇出系数【分析】TTL与非门的电路图和电路符号如图3.14所示,与非门的与功能由多发射极管T1来实现的。

T1的射极是与的输入端,T1的集极是与的输出。

(a)电路图(b)电路符号图3.14简化的TTL与非门下面列出了TTL与非门的参数。

空载导通功耗PcTTL门在静态未带负载时的功耗(功耗指器件在工作时所消耗的功率)。

由于输出为低电位时的静态功耗大于输出为高电位的功耗,故常测输出为低电位时的功耗(导通功耗)。

输入短路电路IISIIS是指当一个输入端接地,而其他输入端开路时,流向接地端的电流。

输入开门电平V on和输入关门电平V off开门电平V on指的是:当电路输出端接额定负载时,使电路输出端处于低电位状态所允许的最小输入电压。

关门电平V off指的是:当电路输出端接额定负载时,使电路输出端处于高电位状态所允许的最大输入电压。

关门电平和开门电平越靠近,越接近同一个数值(阈值电压),说明传输特性曲线越接近理想特性,并且抗干扰能力越强。

输出高电平VOH和输出低电平VOL输出高电平VOH的测试方法:输入端全接地,输出端空载条件下测得的输出端电压称为输出高电平VOH。

输出低电平VOL的测试方法:输入端为开门电平,输出端接316Ω负载电阻条件下测得的输出端电压称为输出低电平VOL。

输入漏电流IIHIIH指当一个输入端接高电位,而其他输入端接地时的输入电流。

扇入系数和扇出系数扇入系数指门的输入端数,扇出系数指一个门能够驱动同类型门的个数。

传输延时tpd和速度-功耗积传输延时是指与非门输出波形相对于输入波形的延时,如图3.15所示。

输出波形下降沿的50%相对输入波形上升沿的50%之间的时间间隔叫做导通延时tpHL;输出波形上升沿的50%相对输入波形下降沿的50%之间的时间间隔叫做关闭延时tpLH;平均传输延时(简称传输延时)tpd=(tpHL+tpLH)/2。

TTL门的传输延时在3ns到40ns之间。

延迟时间门的传输延时和空载导通功耗的乘积称为速度-功耗积,其值越小越好。

【解答】由分析部分得知,开门电平和关门电平的大小影响器件的抗干扰能力,所以本题的答案为(A)。

【扩展】集电极开路输出的TTL门电路也称OC门。

集电极开路输出与非门称为开路与非门。

集电极开路与非门有以下特点:①可以对它们进行线与逻辑(形如F=A·B·…·M的逻辑)。

几个OC与非门输出直接相连,构成线与逻辑。

例如,两个OC与非门输出相连构成一个与或非门,即:注意,形如F=A+B+…+M的逻辑叫线或逻辑,例如F=(AB)+(CD)是(AB)与(CD)进行线或操作。

②电路的上升延迟变大摘要:提出了在TMS320C6000系列DSP上应用McBSP实现I2C总线接口协议的方法,使DSP可以接入其他需要I2C总线配置的智能器件,系统结构简单,硬件设计容易,资源消耗小。

关键字:I2C总线 GPIO McBSP DSP1 引言TI公司的TMS320C6000[1,2]系列是高性能的DSP,可广泛的用于XDSL、无线基站、数字图像处理等方面。

在进行数字图像处理时,通常需要视频解码器诸如SAA7111A之类的模拟视频前端,而大多数的视频解码器进行初始化通常是通过两线的I2C总线接口,但是现在的DSP和MCU大部分都没有I2C总线接口,在这种情况下我们可以应用两个通用的IO线,通过软件的方法来模拟I2C总线的协议,继而完成I2C总线的接口。

在TMS320C6000中通常都有两个或两个以上的多通道缓冲串行接口McBSP,McBSP不仅可以配制成串行接口还可以独立的配制成通用的输入(GPI)、输出(GPO)和输入输出端口(GPIO)。

I2C[3]串行总线是用双向数据线(SDA)和串行时钟线(SCL)两根信号线,在连接到该总线的器件之间传送信息。

总线上的每个器件均可设置一个唯一地址,然后根据所设的功能进行信息的发送或接收。

除了作为发送器和接收器以外,在执行数据传输时,总线的器件还可以设定为主控器和受控器。

通常由主控器启动总线上的数据传输,并产生数据传输所需的时钟信号。

而被其寻址的其它器件均为受控器,这意味着总线上可连接多个有控制总线的器件。

I2C总线上的数据传输率为100kbit/s,快速方式下可达400kbit/s。

连接到总线上的器件数仅受400pF的总线电容的限制。

同时,为了避免总线信号的混乱,要求连接到总线上的各器件输出端必须是集电极开路或漏极开路,以便产生“线与”功能。

I2C总线上的SDA和SCL线都是双向传输线,它们可通过一个电阻连接到正电源端,当总线处于空闲状态时,两条线均为高电平。

2 硬件设计I2C总线的硬件设计非常方便,只需要将SDA 和SCL连接即可,在I2C总线上只允许有一个主控器,其余的都是受控器。

当节点的个数大于了400pF的限制时,可以通过总线驱动器如82B715来进行总线扩展。

连接见图13 软件设计3.1 McBSP的配置I2C总线应用McBSP的两个管脚,首先禁用McBSP功能以便将McBSP的管脚配制成GPI、GPO、GPIO。

本文应用McBSP0的CLKX0作为I2C总线的SCL,FSX0作为I2C总线的SDA,McBSP的DX,DR,通常不能配置成I2C的SDA,因为SDA是双向的,而DX,DR只能配制成单一的输入或输出。

配置代码如下:McBSP0_SPCR=0x00000000;//McBSP0 发送和接收复位McBSP0_PCR=0x00003F00;// McBSP0的所有的管脚都配置为GPIO,CLKX0和FSX0为输出对于主机来说SCL总是输出,所以它的方向是保持不变的,SCL应该输出0,1作为接口的时钟,为了实现此功能我们定义一个宏(MACROS):SET_SCLHI( ) SET_SCLLO( )#define Set_SCLHi( ) McBSP0_SPSA = PCR; McBSP0_SPSA |= 0x00000002#define Set_SCLLo( ) McBSP0_SPSA = PCR; McBSP0_SPSA &= 0XfffffffdI2C总线的数据线SDA当写的时候是输入,读的时候是输出。

为了改变SDA的方向可以定义Set_SDADirOut( ) Set_SDADirIn( )#define Set_SDADirOut( ) McBSP0_SPSA = PCR; McBSP0_SPSA | = 0x00000800#define Set_SDADirIn( ) McBSP0_SPSA = PCR; McBSP0_SPSA &= 0xFFFFF7FFSDA应该依照数据位的0,1来变化,为了输出1,0定义Set_SDAHi( ) Set_SDALo( )#define Set_SDAHi( ) McBSP0_SPSA = PCR; McBSP0_SPSA |= 0x00000008#define Set_SDALo( ) McBSP0_SPSA = PCR; McBSP0_SPSA &= 0xFFFFFFF7定义好之后可以模拟I2C总线的协议进行传送,例如在SAA7111A上的I2C总线接口是用来对SAA7111A进行初始化用的,SCL的频率可以从0到400KHZ,为了控制SCL的频率可以应用DSP的TIMER0来控制。

当CPU为100MHZ时:TCR = 0x00000010; // 停止 TIMER0 and TDDR=0PRD = 6249; // TIMER0 rate = CPU-Frequency/(PDR+1) = 100MHz/6250 = 16kHz...TCR &= 0xFFFFFFEF; // 开始 TIMER03.2 I2C总线协议编程3.2.1 I2C总线协议读写数据流的编程为了进行I2C总线的通讯,我们选用每位数据流4帧(FRAMES),以便延迟和噪声干扰最小,4帧每位的数据流保证了SDA不会变化在SCL的边沿处,仅仅允许数据变化在FRAME0,读仅在FRAME2。

如图2所示I2C总线的写程序如下void I2CWrite(unsigned int WriteBit){Set_SDADirOut( ); // 设置SDA为输出switch(FrameCount){case(0): // 起始帧Set_SCLLo( ); // SCL 为 0if (WriteBit == 0) // SDA = WriteBitSet_SDALo( );elseSet_SDAHi( );break;case(3): // 第4帧Set_SCLLo( ); //break;default: // 在第2,3帧Set_SCLHi( ); // SCL 为 1}FrameCount += 1; // 帧计数if (FrameCount > 3){FrameCount = 0;BitIndex = (BitIndex >> 1); } // 准备下一个发送位}I2C总线的读程序与写程序很类似,只需要改变SDA为输入即可。

3.2.2 I2C总线的开始位和停止位的编程I2C总线的开始位和停止位有3帧产生,在I2C总线传输过程中,仅当总线空闲(SCL线和SDA线均为高电平)时,数据传送才能开始,此时总线上的任何器件均可以控制总线。

其中当SCL线为高电平且SDA线由高变低时为开始条件;而当SCL线为高电平且SDA线由低变高时为结束条件。

如图3所示开始位:void I2CSTA ( ){ // I2C 开始位Set_SDADirOut ( );//定义SDA为输出switch ( FrameCount ){case (1): // 第2帧Set_SCLHi ( );Set_SDALo( );break;case (2): // 第三帧Set_SCLLo ( );Set_SDALo( );break;default: // 第一帧Set_SCLHi ( );Set_SDAHi ( );}FrameCount += 1; // 帧计数if ( FrameCount > 2 ){FrameCount = 0;BitIndex = 0x0080; } // 定义的低8位}停止位的编程方法只需要按照上面所说的将SCL线为高电平且SDA线由低变高即可。

3.2.3 I2C总线的数据格式起始位受控器件地址读写控制位0/1 应答位数据应答位…停止位I2C总线数据传输格式[3]如图4。