51单片机IO及上拉电阻

51单片机的IO口

51单片机的I O口.2P0口作为普通I/O口:①输出时,CPU发出控制电平"0"封锁"与"门,将输出上拉场效应管T1截止,同时使多路开关MUX把锁存器与输出驱动场效应管T2栅极接通。

故内部总线与P0口同相。

由于输出驱动级是漏极开路电路,若驱动NMOS或其它拉流负载时,需要外接上拉电阻。

P0的输出级可驱动8个LSTTL负载。

②输入时--分读引脚或读锁存器读引脚:由传送指令(MOV)实现;下面一个缓冲器用于读端口引脚数据,当执行一条由端口输入的指令时,读脉冲把该三态缓冲器打开,这样端口引脚上的数据经过缓冲器读入到内部总线。

读锁存器:有些指令如:ANLP0,A称为"读-改-写"指令,需要读锁存器。

上面一个缓冲器用于读端口锁存器数据。

*原因:如果此时该端口的负载恰是一个晶体管基极,且原端口输出值为1,那么导通了的PN结会把端口引脚高电平拉低;若此时直接读端口引脚信号,将会把原输出的"1"电平误读为"0"电平。

现采用读输出锁存器代替读引脚,图中,上面的三态缓冲器就为读锁存器Q端信号而设,读输出锁存器可避免上述可能发生的错误。

*说明:nP0口必须接上拉电阻;n在读信号之前数据之前,先要向相应的锁存器做写1操作的I/O口称为准双向口;n三态输入缓冲器的作用:n(ANLP0,A)准双向口:从图中可以看出,在读入端口数据时,由于输出驱动FET并接在引脚上,如果T2导通,就会将输入的高电平拉成低电平,产生误读。

所以在端口进行输入操作前,应先向端口锁存器写"1",使T2截止,引脚处于悬浮状态,变为高阻抗输入。

这就是所谓的准双向口。

2、P0作为地址/数据总线在系统扩展时,P0端口作为地址/数据总线使用时,分为:(1)P0引脚输出地址/数据信息:CPU发出控制电平"1",打开"与"门,又使多路开关MUX把CPU的地址/数据总线与T2栅极反相接通,输出地址或数据。

51单片机上拉电阻如何取值

51单片机上拉电阻如何取值有很多朋友在学习51单片机的时候,都会对其P0口上拉电阻阻值的取值问题而头疼。

其实,P0口接不接上拉电阻,电阻值该选择多大的都是根据不同的情况来选择的。

下面来简单分析下如下的几种情况:第一种:P0口作为共阳极LED数码管的驱动端口。

这种情况下,P0口主要是以吸收电流来作为有效工作方式,不对外输出高电平,此时,不应接上拉,任何上拉都不要接。

接多少丢多少。

不仅增加成本,而且增大了工作电流。

至于数码管的鬼影问题,那是程序部分的问题,与硬件无关。

第二种:P0口作为数据传输接口。

这种情况下,P0口需要输出高电平,而高电平的输出其实就是来自于上拉电阻。

在数据输出状态下,P0口的负载都是逻辑器件,不需要大的输入功率,那么,就可以采用电阻值较大的电阻器作为上拉电阻,电阻过小会导致系统的工作电流加大。

常用的5V电压下,其取值范围在4.7K-47K之间。

减小电阻有利于提高系统的抗干扰能力,但是会增大系统的功耗,尤其是上拉电阻较多的情况下此现象会更加明显。

第三种:P0口作为控制接口。

这种情况下,P0口需要输出高电平或者低电平作为有效控制信号。

如果需要输出高电平作为有效信号,加之一般控制的器件是NPN 的三极管,那么,其上拉电阻的取值范围多在470-4.7K之间,取值越小,三极管导通程度越大,三极管本身的损耗就会越小,但是对单片机本身的考验就会越大。

取值越大,则单片机负担越小,则三极管的导通程度就会越小,导致三极管本身的损耗加大,甚至会跳出开关状态转至放大状态。

如果需要控制的三极管功率过大,那么需要在控制电路中间加一级隔离放大。

如果单片机的P0口需要输出低电平作为有效控制信号,那么,其上拉电阻的作为就不是用来输出高电平了,而是为了给PNP型被控器件提供一个防止意外导通的电压,此举可以提高抗干扰能力,提高可靠性。

那么,其电阻的阻值取值范围多在4.7K-47K之间。

同样的,阻值越大,单片机负担越小,抗干扰能力越小,阻值越小,单片机负担越大,抗干扰能力越大。

51单片机高低电平

关于51单片机输入/输出口电压和电流以及加驱动电路的问题悬赏分:5 - 解决时间:2007-9-13 08:24各位好,我在查找用51单片机I/O模拟电压和电流以及用三极管驱动相关资料时看到下面的三种不同表述,请问哪一种是正确的呢,希望高手能综合点解释一下,谢谢!!1、51单片机I/O口为集电极上拉输出方式,高电平输出电流等于上拉电阻的电流,这个电流比较小,低电平输出是内部晶体管吸收的电流,最大可以达到10mA,但是整个端口的总电流不能超过24mA。

电平低于0.7V就是低电平,高于1.8V就是高电平。

在这个之间不确定。

2、51单片机的I/O口可以理解为一个开路的NPN三极管加一个上拉电阻,驱动PNP三极管最方便,驱动NPN三极管也没有问题,是靠上拉电阻驱动,所以不好。

况且51单片机复位时所有I/O口是高电平,就造成NPN三极管导通,这在大多数电路里是不允许的。

复位时,I/O口为高阻的单片机驱动三极管就无所谓了。

3、51系列单片机引脚电平与TTL电平兼容,也就是输入高电位大于2.0V,低电位小于0.8V,输出高电位大于2.4V,低电位小于0.4V。

一般情况下,若电源电压为5V,输出高电位电压也是5V左右,低电位电压接近0V.看上面的第三种论述好象还需要区分输入和输出两种情况,我都晕了。

问题补充:上面的论述中提到了输入和输出两中情况,输入是指象电源等这样的输入还是说P口从外部读取数据时的“输入”?而输出就应该是P口正常的输出了吧?提问者:zhangxb1393112 - 初学弟子一级最佳答案作为输出端口:P0可吸收可输出电流,多大不是很清楚,驱动LED没问题,驱动NPN、PNP 三极管都没有问题。

P1P2P3只能吸收电流,不能输出电流(如第一种说法中提的“这个电流比较小”,而第二种说法里的“驱动NPN三极管也没有问题”就需要实验证明一下了,因为这个电流实在太小了),如特别需要,可外接上拉电阻。

输出电流指得是输出1时带负载,吸收电流指得是输出0时带负载。

51单片机驱动能力(拉电流_灌电流)及上拉电阻

看来很多网友都搞不清灌电流和拉电流的概念,下面就此解释一下,希望看过本文后不再就此困扰。

一个重要的前提:灌电流和拉电流是针对端口而言的。

名词解释——灌:注入、填充,由外向内、由虚而实。

渴了,来一大杯鲜榨橙汁,一饮而尽,饱了,这叫“灌”。

灌电流(sink current),对一个端口而言,如果电流方向是向其内部流动的则是“灌电流”,比如一个IO通过一个电阻和一个LED连接至VCC,当该IO输出为逻辑0时能不能点亮LED,去查该器件手册中sink current参数。

名词解释——拉:流出、排空,由内向外,由实而虚。

一大杯鲜橙汁喝了,过会儿,憋的慌,赶紧找卫生间,一阵“大雨”,舒坦了,这叫“拉”。

拉电流(sourcing current),对一个端口而言,如果电流方向是向其外部流动的则是“拉电流”,比如一个IO通过一个电阻和一个LED 连至GND,当该IO输出为逻辑1时能不能点亮LED,去查该器件手册中sourcing current参数。

/viewthread.php?tid=219138&highlight=%2Byez hubenyue单片机输出低电平时,将允许外部器件,向单片机引脚内灌入电流,这个电流,称为“灌电流”,外部电路称为“灌电流负载”(sink current)单片机输出高电平时,则允许外部器件,从单片机的引脚,拉出电流,这个电流,称为“拉电流”,外部电路称为“拉电流负载“(source current)这些电流一般是多少?最大限度是多少?这就是常见的单片机输出驱动能力的问题。

分析一下TTL 的输入特性,就可以发现,51 单片机基本上就没有什么驱动能力。

它的引脚,甚至不能带动当时的LED 进行正常发光。

记得是在AT89C51 单片机流行起来之后,做而论道才发现:单片机引脚的能力大为增强,可以直接带动LED 发光了。

看看下图,图中的D1、D2 就可以不经其它驱动器件,直接由单片机的引脚控制发光显示。

MCS-51单片机IO口详解

单片机IO口结构及上拉电阻MCS-51有4组8位I/O口:P0、P1、P2和P3口,P1、P2和P3为准双向口,P0口则为双向三态输入输出口,下面我们分别介绍这几个口线。

一、P0口和P2口图1和图2为P0口和P2口其中一位的电路图。

由图可见,电路中包含一个数据输出锁存器(D触发器)和两个三态数据输入缓冲器,另外还有一个数据输出的驱动(T1和T2)和控制电路。

这两组口线用来作为CPU与外部数据存储器、外部程序存储器和I/O扩展口,而不能象P1、P3直接用作输出口。

它们一起可以作为外部地址总线,P0口身兼两职,既可作为地址总线,也可作为数据总线。

图1 单片机P0口内部一位结构图图2 单片机P0口内部一位结构图P2口作为外部数据存储器或程序存储器的地址总线的高8位输出口AB8-AB15,P0口由ALE选通作为地址总线的低8位输出口AB0-AB7。

外部的程序存储器由PSEN信号选通,数据存储器则由WR和RD读写信号选通,因为2^16=64k,所以MCS-51最大可外接64kB的程序存储器和数据存储器。

二、P1口图3为P1口其中一位的电路图,P1口为8位准双向口,每一位均可单独定义为输入或输出口,当作为输入口时,1写入锁存器,Q(非)=0,T2截止,内上拉电阻将电位拉至"1",此时该口输出为1,当0写入锁存器,Q(非)=1,T2导通,输出则为0。

图3 单片机P2口内部一位结构图作为输入口时,锁存器置1,Q(非)=0,T2截止,此时该位既可以把外部电路拉成低电平,也可由内部上拉电阻拉成高电平,正因为这个原因,所以P1口常称为准双向口。

需要说明的是,作为输入口使用时,有两种情况:1.首先是读锁存器的内容,进行处理后再写到锁存器中,这种操作即读—修改—写操作,象JBC(逻辑判断)、CPL(取反)、INC(递增)、DEC(递减)、ANL(与逻辑)和ORL(逻辑或)指令均属于这类操作。

2.读P1口线状态时,打开三态门G2,将外部状态读入CPU。

51单片机各针脚介绍

51单片机各针脚介绍51单片机是一款广泛应用于嵌入式系统中的微控制器,它在电子行业中具有重要的地位。

了解51单片机的各个针脚和其功能对于学习和应用它来说至关重要。

本文将为读者介绍51单片机的各个针脚以及它们的功能。

1. VCC和GND:VCC代表供电正极,GND代表接地。

这两个针脚是最基本的供电和接地连接,使用者需要将这两个引脚连接到电源,以提供电压和地线。

2. P0.0 - P0.7:P0口是51单片机最常用的8位通用I/O口之一。

每个引脚可以被配置为输入或输出,用于连接和控制外部设备。

3. P1.0 - P1.7:P1口也是一个8位通用I/O口,具有与P0口相同的功能。

P1口的特点是它具备上拉电阻功能,可以用于外部开关和按钮的输入控制。

4. P2.0 - P2.7:P2口也是一个8位通用I/O口,同样可以作为输入或输出引脚。

与P1口类似,P2口也具备上拉电阻功能。

5. P3.0 - P3.7:P3口是最后一个8位通用I/O口,同样可用作输入或输出引脚。

与P2口类似,P3口具备上拉电阻功能。

6. RST:RST是复位控制引脚,用于将51单片机重启至复位状态。

当对RST引脚施加低电平脉冲时,单片机将会重新启动,并执行初始化操作。

7. EA/VPP:EA/VPP引脚具有两个不同的功能。

在系统中,EA引脚必须连接到GND,以选择外部程序存储器;VPP引脚在烧录代码时使用,通常连接到12V电压。

8. ALE/PROG:ALE/PROG引脚也有两种功能,ALE用于地址锁存器的时钟输入,PROG用于编程电平切换。

在应用中,ALE通常用于与外部设备进行时序协调。

9. PSEN:PSEN引脚用于外部程序存储器的读取操作。

当进行指令获取或通信时,PSEN引脚连接到程序存储器并发送读取控制信号。

10. XTAL1和XTAL2:这两个引脚用于外部晶振或陶瓷谐振器的连接。

XTAL1接收晶振信号输入,XTAL2输出晶振信号。

51单片机IO口驱动能力

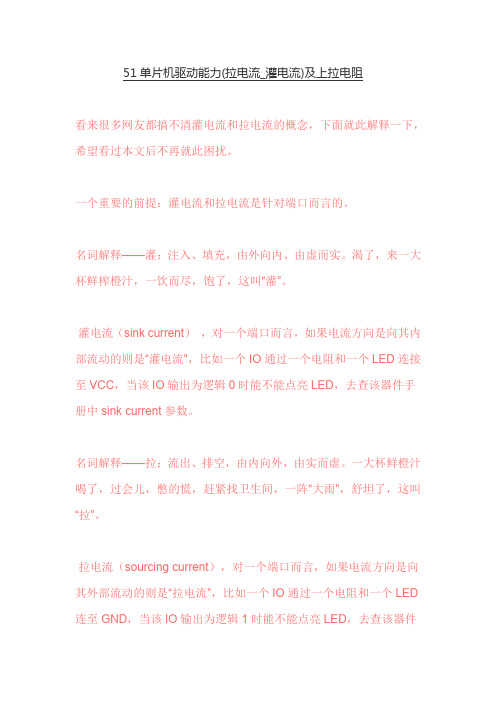

单片机输出低电平的时候,单个的引脚,向引脚灌入的最大电流为 10 mA;一个 8 位的接口(P1、P2 以及 P3),灌入的总电流最大为 15 mA,P0 允许灌入的最大总电流为 26 mA;全部的四个接口所允许的灌电流之和,最大为 71 mA。

但是当引脚输出高电平的时候,它们的“拉电流”能力可就差多了,竟然还不到 1 mA。

为了合理利用IO引脚的低电平能力强的特点,在外接耗电较大的器件(如LED数码显示器、继电器等)的时候,应该优先选用低电平输出来驱动外部器件。

使用IO口输出高电平驱动负载,就是一个错误的选择。

下图是一个直接利用单片机IO引脚驱动LED的电路。

图中P0口使用低电平驱动方式,只要加上约1K的限流电阻即可,甚至不需要常见的P0口上拉电阻。

发光的段,每个引脚灌电流约为3mA,不发光的段,电流为0。

即使各个段全都发光,电流也不超过P0所容许的电流,这是一个合理的驱动方式。

图中P3口使用了高电平驱动方式,这就必须加上上拉电阻来帮助IO接口输出电流。

电阻也采用了1K,发光的段,LED上的电流约为3mA,不发光的段,电流则为5mA,灌入了单片机的IO引脚。

单片机输出低电平的时候,LED不亮,此时VCC通过上拉电阻把电流全部灌进单片机IO口,并且电流是5mA,单片机输出高电平的时候,VCC通过上拉电阻将电流注入到LED中,led亮。

注意到了吗?LED 不发光的时候,上拉电阻给的电流全部灌入单片机的引脚了!如果在一个 8 位的接口,安装了 8 个 1k 的上拉电阻,当单片机都输出低电平的时候,就有 40mA 的电流灌入这个 8 位的接口!如果四个 8 位接口,都加上 1k 的上拉电阻,最大有可能出现32 × 5 = 160mA 的电流,都流入到单片机中!这个数值已经超过了单片机手册上给出的上限。

此时单片机就会出现工作不稳定的现象。

而且这些电流,都是在负载处于无效的状态下出现的,它们都是完全没有用处的电流,只是产生发热、耗电大、电池消耗快...等后果。

51单片机-IO口实验报告

《信息技术综合实践》课程实验报告

1.打开KeiluVision2应用程序,新建一个工程,将IO.c文件添加到新建的工程中(将头文件中的头文件中的regx修改为reg),在输出中选择生成相应的HEX文件并保存到相应文件夹中

2.打开KeiluVision2应用程序,新建一个工程,将IO.c文件添加到新建的工程中(将头文件中的头文件中的regx修改为reg),在输出中选择生成相应的HEX文件并保存到相应文件夹中,进行文件的编译和调试。

3.进行实验箱的连线。

4.打开下载器,擦除并将生成的HEX文件调入Flash,然后选择“自动”。

5.通过示波器观察实验现象

5.1 示波器波形图

5.1.1(i的范围是小于500,波形图如下所示)

由图可知:当不修改i的范围时,波形的频率比较高,约在150Hz左右。

5.1.2(将代码中i的范围修改为小于20000,波形图如下所示)

由图可知:将i的范围变大以后,波形的频率变低并且稳定在5Hz左右。

5.2 小灯闪烁视频

(灯亮时的图片)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

单片机IO口结构及上拉电阻

[ 2009-12-1 2:40:00 | By: zydlyq ]

8051有4组8位I/O口:P0、P1、P2和P3口,P1、P2和P3为准双向口,P0口则为双向三态输入输出口,下面我们分别介绍这几个口线:

·P0口和P2口:

右图为P0口和P2口其中一位的电路图,由图可见,电路中包含一个数据输出锁存器和两个三态数据输入缓冲器,另外还有一个数据输出的驱动和控制电路。

这两组口线用来作为CPU与外部数据存储器、外部程序存储器和I/O扩展口,而不能象P1、P3直接用作输出口。

它们一起可以作为外部地址总线,P0口身兼两职,既可作为地址总线,也可作为数据总线。

参考图2。

P2口作为外部数据存储器或程序存储器的地址总线的高8位输出口AB8-AB15,P0口由ALE选通作为地址总线的低8位输出口AB0-AB7。

外部的程序存储器由PSEN信号选通,数据存储器则由WR和RD读写信号选通,因为216=64k,所以8051最大可外接64kB的程序存储器和数据存储器。

·P1口:

右图为P1口其中一位的电路图,P1口为8位准双向口,每一位均可单独定义为输入或输出口,当作为输入口时,1写入锁存器,Q(非)=0,T2截止,内上拉电阻将电位拉至"1",此时该口输出为1,当0写入锁存器,Q(非)=1,T2导通,输出则为0。

作为输入口时,锁存器置1,Q(非)=0,T2截止,此时该位既可以把外部电路拉成低电平,也可由内部上拉电阻拉成高电平,正因为这个原因,所以P1口常称为准双向口。

需要说明的是,作为输入口使用时,有两种情况,其一是:首先是读锁存器的内容,进行处理后再写到锁存器中,这种操作即读—修改—写操作,象JBC(逻辑判断)、CPL(取反)、INC(递增)、DEC(递减)、ANL(与逻辑)和ORL(逻辑或)指令均属于这类操作。

其二是:读P1口线状态时,打开三态门G2,将外部状态读入CPU。

·P3口:

P3口的电路如上图所示,P3口为准双向口,为适应引脚的第二功能的需要,增加了第二功能控制逻辑,在真正的应用电路中,第二功能显得更为重要。

由于第二功能信号有输入输出两种情况,我们分别加以说明。

P3口的输入输出及P3口锁存器、中断、定时/计数器、串行口和特殊功能寄存器有关,P3口的第一功能和P1口一样可作为输入输出端口,同样具有字节操作和位操作两种方式,在位操作模式下,每一位均可定义为输入或输出。

我们着重讨论P3口的第二功能,P3口的第二功能各管脚定义如下:

·P3.0 串行输入口(RXD)

·P3.1 串行输出口(TXD)

·P3.2 外中断0(INT0)

·P3.3 外中断1(INT1)

·P3.4 定时/计数器0的外部输入口(T0)

·P3.5 定时/计数器1的外部输入口(T1)

·P3.6 外部数据存储器写选通(WR)

·P3.7 外部数据存储器读选通(RD)

对于第二功能为输出引脚,当作I/O口使用时,第二功能信号线应保持高电平,与非门开通,以维持从锁存器到输出口数据输出通路畅通无阻。

而当作第二功能口线使用时,该位的锁存器置高电平,使与非门对第二功能信号的输出是畅通的,从而实现第二功能信号的输出。

对于第二功能为输入的信号引脚,在口线上的输入通路增设了一个缓冲器,输入的第二功能信号即从这个缓冲器的输出端取得。

而作为I/O口线输入端时,取自三态缓冲器的输出端。

这样,不管是作为输入口使用还是第二功能信号输入,输出电路中的锁存器输出和第二功能输出信号线均应置“1”。

1. p0作为地址数据总线时,T1和T2是一起工作的,构成推挽结构。

高电平时,T1打开,T2截止;低电平时,T1截止,T2打开。

这种情况下不用外接上拉电阻.而且,当T1打开,T2截止,输出高电平的时候,因为内部电源直接通过T1输出到p0口线上,因此驱动能力(电流)可以很大,这就是为什么教科书上说可以"驱动8个TTL负载"的原因。

2. p0作为一般端口时,T1就永远的截止,T2根据输出数据0导通和1截止,导通时拉地,当然是输出低电平;要输出高电平,T2就截止,p0口就没有输出了,(注意,这种情况就是所谓的高阻浮空状态),如果加上外部上拉电阻,输出就变成了高电平1。

3. 其他端口p1,p2,p3,在内部直接将p1口中的T1换成了上拉电阻,所以不用外接,但内部上拉电阻太大,电流太小,有时因为电流不够,也会再并一个上拉电阻。

4. 在某个时刻,p0口上输出的是作为总线的地址数据信号还是作为普通I/O口的电平信号,是依靠多路开关MUX来切换的.而MUX的切换,又是根据单片机指令来区分的.当指令为外部存储器/IO口读/写时,比如 MOVX A,@DPTR ,MUX是切换到地址/数据总线上;而当普通MOV传送指令操作p0口时,MUX是切换到内部总线上的。

5. p0(i/o),p1,p2,p3口用于输入时,需要写1使IO下拉的MOS管截止,以免MOS管导通将输入拉底为0,当一直用于输入时不用置1(先使用该IO输出,该IO锁存器里可能是0,再用该IO输入则会使

MOS管导通),将IO写1后,该IO锁存器不会变了,所以再一直用于输入不用置1。

p0用于地址数据线时输入不用写1,因为MUX没和锁存器相连。

PS:

Because Ports 1, 2, and 3 have fixed internal pullups, they are sometimes called “quasi- bidirectional” ports.

因为端口1、2、3有固定的内部上拉,所以有时候他们被称为"准双向"口。

Port 0, on the other hand, is considered “true” bidirectional, because when configured as an input it floats.

端口0, 从另外一方面来说,就被认为是"真正的"双向,因为当它被设置为输入的时候是浮空(高阻态)的。

P0口上拉电阻选择

如果是驱动led,那么用1K左右的就行了。

如果希望亮度大一些,电阻可减小,最小不要小于200欧姆,否则电流太大;如果希望亮度小一些,电阻可增大,增加到多少呢,主要看亮度情况,以亮度合适为准,一般来说超过3K以上时,亮度就很弱了,但是对于超高亮度的LED,有时候电阻为10K时觉得亮度还能够用。

我通常就用1k的。

对于驱动光耦合器,如果是高电位有效,即耦合器输入端接端口和地之间,那么和LED的情况是一样的;如果是低电位有效,即耦合器输入端接端口和VCC之间,那么除了要串接一个1——4.7k之间的电阻以外,同时上拉电阻的阻值就可以用的特别大,用100k——500K之间的都行,当然用10K的也可以,但是考虑到省电问题,没有必要用那么小的。

对于驱动晶体管,又分为PNP和NPN管两种情况:对于NPN,毫无疑问NPN管是高电平有效的,因此上拉电阻的阻值用2K——20K之间的,具体的大小还要看晶体管的集电极接的是什么负载,对于LED类负载,由于发管电流很小,因此上拉电阻的阻值可以用20k的,但是对于管子的集电极为继电器负载时,由于集电极电流大,因此上拉电阻的阻值最好不要大于4.7K,有时候甚至用2K的。

对于PNP管,毫无疑问PNP 管是低电平有效的,因此上拉电阻的阻值用100K以上的就行了,且管子的基极必须串接一个1——10K的电阻,阻值的大小要看管子集电极的负载是什么,对于LED类负载,由于发光电流很小,因此基极串接的电阻的阻值可以用20k的,但是对于管子的集电极为继电器负载时,由于集电极电流大,因此基极电阻的阻值最好不要大于4.7K。

对于驱动TTL集成电路,上拉电阻的阻值要用1——10K之间的,有时候电阻太大的话是拉不起来的,因此用的阻值较小。

但是对于CMOS集成电路上拉电阻的阻值就可以用的很大,一般不小于20K,我通常用100K的,实际上对于CMOS电路,上拉电阻的阻值用1M的也是可以的,但是要注意上拉电阻的阻值太大的时候,容易产生干扰,尤其是线路板的线条很长的时候,这种干扰更严重,这种情况下上拉电阻不宜过大,一般要小于100K,有时候甚至小于10K。

(注:专业文档是经验性极强的领域,无法思考和涵盖全面,素材和资料部分来自网络,供参考。

可复制、编制,期待你的好评与关注)。