北航 计算机组成原理 第五部分:CPU控制单元设计

合集下载

北航16春《计算机组成原理》在线作业一

北航16春《计算机组成原理》在线作业一北航16春《计算机组成原理》在线作业一

##目录

-[导语](#导语)

-[1.寻址方式](-寻址方式)

-[2.指令系统](-指令系统)

-[3.CPU的流水线技术](-CPU的流水线技术)

-[4.整数运算](-整数运算)

-[5.控制单元](-控制单元)

-[总结](#总结)

##导语

计算机组成原理是一门非常重要的基础课程,它的内容包括对计算机

组成原理的概念、算法和实现方法的研究。

本文就计算机组成原理的主要

内容作出详细的介绍,主要包括寻址方式、指令系统、CPU的流水线技术、整数运算、控制单元等几个方面。

##1.寻址方式

寻址是指计算机系统中访问存储器的方式,确定存储器中一些位置的

字节的地址。

常见的寻址方式有:直接寻址、寄存器寻址和间接寻址。

###(1)直接寻址

直接寻址是一种最简单的寻址方式,它的特点是,指令中包含要访问的存储单元的绝对地址或者该地址的偏移量。

当指令被解释执行时,指令解释器便可以根据地址来访问相应的存储单元,因此它的操作简单,但是地址可能变化,因此会出现地址失效的情况。

###(2)寄存器寻址

寄存器寻址是指指令中使用寄存器来保存要访问的存储单元地址的方式。

白中英 第五版 计算机组成原理第5章.

[思考]

用二进制码表示的指令和数据都放在内存里, 那么CPU是怎样识别出它们是数据还是指令呢?

从时间上来说:

▴ ▴

取指发生在指令周期的第一个CPU周期; 取数发生在后面几个CPU周期,即 “执行指令”阶段。

从空间上来说:

▴ 送指令寄存器IR —指令 ▴

送运算器 — 数据。

计算机组成原理

30

5.3

时序产生器和控制方式

送操作 数地址

取出操 作数

取指令阶段

计算机组成原理

执行指令阶段

16

LAD指令的指令周期——执行

play 计算机组成原理

17

5.2.4

ADD指令的指令周期

ADD R1, R2是一条RR指令

计算机组成原理

18

ADD指令的指令周期——执行

play

计算机组成原理

19

5.2.5

STO指令的指令周期

STO R2, (R3)是一条RS指令

5.4.1 微命令和微操作

▲ 微命令:控制部件通过控制线向执行部件发出的各种

控制命令。

▲ 微操作:执行部件接受微命令后所进行的操作。 ▲ 微操作可分为相容性和相斥性两种。 在同时或同一个CPU周期 内可以并行执行的微操作 不能在同时或同一个CPU 周期内并行执行的微操作

7

计算机组成原理

5.1.4 操作控制器与时序产生器

数据通路: 是许多寄存器之间传送信息的通路。 操作控制器的功能 : 根据指令操作码和时序信号,产 生各种操作控制信号,以便正确地建立数据通路, 从而完成取指令和执行指令的控制。 根据设计方法不同,操作控制器可分为:

1.硬布线控制器 2.微程序控制器

;(R1)→R0 ;(6)→ R1

用二进制码表示的指令和数据都放在内存里, 那么CPU是怎样识别出它们是数据还是指令呢?

从时间上来说:

▴ ▴

取指发生在指令周期的第一个CPU周期; 取数发生在后面几个CPU周期,即 “执行指令”阶段。

从空间上来说:

▴ 送指令寄存器IR —指令 ▴

送运算器 — 数据。

计算机组成原理

30

5.3

时序产生器和控制方式

送操作 数地址

取出操 作数

取指令阶段

计算机组成原理

执行指令阶段

16

LAD指令的指令周期——执行

play 计算机组成原理

17

5.2.4

ADD指令的指令周期

ADD R1, R2是一条RR指令

计算机组成原理

18

ADD指令的指令周期——执行

play

计算机组成原理

19

5.2.5

STO指令的指令周期

STO R2, (R3)是一条RS指令

5.4.1 微命令和微操作

▲ 微命令:控制部件通过控制线向执行部件发出的各种

控制命令。

▲ 微操作:执行部件接受微命令后所进行的操作。 ▲ 微操作可分为相容性和相斥性两种。 在同时或同一个CPU周期 内可以并行执行的微操作 不能在同时或同一个CPU 周期内并行执行的微操作

7

计算机组成原理

5.1.4 操作控制器与时序产生器

数据通路: 是许多寄存器之间传送信息的通路。 操作控制器的功能 : 根据指令操作码和时序信号,产 生各种操作控制信号,以便正确地建立数据通路, 从而完成取指令和执行指令的控制。 根据设计方法不同,操作控制器可分为:

1.硬布线控制器 2.微程序控制器

;(R1)→R0 ;(6)→ R1

2021年计算机组成原理第5章.pptx

⑨

REG间接寻址

12

10

(3)加法指令(ADD)执行过程

─需求细化

*取指令阶段:取指令+分析指令,(PC)=12H 上条指令结果

取指令操作步骤— 同取数指令(①~④,仅PC值不同)

分析指令的结果— ADD指令,R0←(R0)+(R3)

主存

②+“1”

10H 00100100

R0 17H ⑥

R1 73H

15H 10000000

16H 00010000

17H 01110011

*执行指令阶段:实现当前指令功能 ,设(R0)=17H

操作步骤— R0-⑥→MAR-⑦→MEM读-⑧→MDR-⑨→R1

REG间接寻址

11

(2)存数指令(ST)执行过程

─需求细化

*取指令阶段:取指令+分析指令,(PC)=11H 上条指令结果

*CPU功能与组成部件: 指令控制— PC、IR、ID 操作控制 时间控制 —时序系统、控制信号形成电路 数据加工— ALU及状态REG、REG组 中断处理— 中断机构

*CPU基本结构:运算器,CU、BIU、中断机构,数据通路

CPU …

…

REG0

REG(n-1)

内 部

数

ALU

据

通

状态REG

路

MAR MDR

需求细化—有序的操作串-→CPU基本操作序列-→原子操作序列

需求实现—CU实现原子操作及序列

*CPU基本操作:

部件复用→降低成本

定义—CPU内部的实现基本功能的操作 分步骤保存

要求—提供及接收操作数据的须为时序部件或MEM

*CPU基本操作的类型: REG间传送— R源→R目标 存 储 器 读 — MAR→MEM(读)→MDR 存 储 器 写 — MAR及MDR→MEM(写) 算 逻 运 算 — R源1及R源2→ALU(运算)→R结果

REG间接寻址

12

10

(3)加法指令(ADD)执行过程

─需求细化

*取指令阶段:取指令+分析指令,(PC)=12H 上条指令结果

取指令操作步骤— 同取数指令(①~④,仅PC值不同)

分析指令的结果— ADD指令,R0←(R0)+(R3)

主存

②+“1”

10H 00100100

R0 17H ⑥

R1 73H

15H 10000000

16H 00010000

17H 01110011

*执行指令阶段:实现当前指令功能 ,设(R0)=17H

操作步骤— R0-⑥→MAR-⑦→MEM读-⑧→MDR-⑨→R1

REG间接寻址

11

(2)存数指令(ST)执行过程

─需求细化

*取指令阶段:取指令+分析指令,(PC)=11H 上条指令结果

*CPU功能与组成部件: 指令控制— PC、IR、ID 操作控制 时间控制 —时序系统、控制信号形成电路 数据加工— ALU及状态REG、REG组 中断处理— 中断机构

*CPU基本结构:运算器,CU、BIU、中断机构,数据通路

CPU …

…

REG0

REG(n-1)

内 部

数

ALU

据

通

状态REG

路

MAR MDR

需求细化—有序的操作串-→CPU基本操作序列-→原子操作序列

需求实现—CU实现原子操作及序列

*CPU基本操作:

部件复用→降低成本

定义—CPU内部的实现基本功能的操作 分步骤保存

要求—提供及接收操作数据的须为时序部件或MEM

*CPU基本操作的类型: REG间传送— R源→R目标 存 储 器 读 — MAR→MEM(读)→MDR 存 储 器 写 — MAR及MDR→MEM(写) 算 逻 运 算 — R源1及R源2→ALU(运算)→R结果

计算机组成原理(CPU的控制器部件)

控制器的组成

指令寄存器

用于存储从内存中读取的指令。

指令译码器

将指令寄存器中的指令进行译码,确定需要执行的操作。

控制信号发生器

根据指令译码器的输出,产生控制信号,控制CPU各部件的工作。

时序电路

产生各种时钟信号,控制CPU的工作节拍。

控制器的实现方式

硬布线控制器

通过硬件逻辑电路实现控制信号的产生。

根据指令要求,控制 CPU内部各部件的操作

方式。

数据传输控制

控制CPU内部和外部的 数据传输。

控制器的组成

控制单元

负责指令译码、时序产生和操 作控制。

指令寄存器

存储正在执行的指令。

地址寄存器

存储CPU要访问的内存单元的 地址。

状态寄存器

记录CPU的工作状态和结果。

控制器的功能

指令执行控制

按照指令要求,控制指令的执行顺序和时间。

计算机组成原理(CPU的控制 器部件)

• CPU的控制器概述 • 指令系统 • 指令流水线 • 控制器的工作原理 • CPU控制器的组成与实现

01

CPU的控制器概述

控制器的作用

指令控制

按照指令要求,控制指 令的执行顺序和时间。

时序产生

产生各种时序信号,控 制CPU内部各部件的工

作节奏。

操作控制

指令的分类

数据传输类指令

用于在寄存器之间或内存与寄存器之 间传输数据。

算术运算类指令

用于执行加、减、乘、除等算术运算。

逻辑运算类指令

用于执行逻辑与、或、非等逻辑运算。

控制转移类指令

用于改变程序的执行流程,如跳转、 子程序调用等。

指令的执行过程

解码

北航计算机体系结构方向实验介绍

综合实验:主要完成各种控制电路和一些实用数字系统的设计,包括8

位16进制频率计、电子秒表电路、数码管扫描显示电路、全自动洗衣机控制 器 交通灯控制器 电子抢答器 乐曲演奏电路 卡式电话计费器的设计等, 器、交通灯控制器、电子抢答器、乐曲演奏电路、卡式电话计费器的设计等, 共10个。

设计创新实验:主要训练学生综合应用各种EDA工具完成一个大型实际

16

北航计算机体系结构方向实验ห้องสมุดไป่ตู้绍

数字逻辑实验 部分实验大纲 数字逻辑实验-部分实验大纲

课程实验(实验2-3)-选作实验 实验名称:数码管扫描显示电路(2学时,设 计型) 实验目的:了解数码管扫描显示电路的原理。 掌握数码管扫描显示电路的设计方法。 实验内容:利用人眼的视觉暂留效应,设计数 码管扫描显示电路,使6个数码管完成小时、分 钟 秒的扫描显示 要求有启动计时和异步清 钟、秒的扫描显示。要求有启动计时和异步清 零的功能

9

北航计算机体系结构方向实验介绍

MIPS-C核心介绍 MIPS C核心介绍 MIPS-C多周期数据通路

10

北航计算机体系结构方向实验介绍

MIPS-C核心介绍 MIPS C核心介绍 MIPS-C外部接口 UART接口 支持9600 115200波特率 支持9600~115200波特率 UART内部包括6个寄存器:数据寄存器、 中断允许寄存器 中断识别寄存器 线路控 中断允许寄存器、中断识别寄存器、线路控 制寄存器、线路状态寄存器和除数寄存器 支持 级中断 支持3级中断

11

北航计算机体系结构方向实验介绍

MIPS-C核心介绍 MIPS C核心介绍 MIPS-C外部接口 存储器接口 CPU外部可以连接FLASH和SDRAM FLASH为 8位 16M SDRAM为 32位 128M

北航计算机组成原理讲义_5.cpu与微程序设计

CPMDR CPPC

调整PC

M1.T4

MDR(指令)送IR

IB MDR

CPIR

2.2 指令流程与微操作时间表

时间节拍 完成功能 需要的微操作信号

结构图

需要的控制脉冲

M2.T1

取 变 址 值 M2.T2 M2.T3

PC送MAR

从存储器读取1000H

IB PC

AB MAR, RD, W/B

PC+1

IB MDR

IB GR, RDGR, W/B, ADD

CPPC

CPD BX地址, CPZ CPMAR

取 数 周 期

M3.T1 M3.T2 M3.T3 M3.T4

IB Z

AB MAR, RD, W/B

MDR DB

CPMDR

2.2 指令流程与微操作时间表

结构图

时间节拍 M4.T1 执 行 周 期 M4.T2 M4.T3 M4.T4

模型机总体结构 指令流程与组合逻辑控制器 微程序原理 微程序控制器设计

2.1 控制方式与时序系统

控制方式

同步控制方式 异步控制方式

时序系统

脉冲时序信号:主时钟脉冲

节拍信号:T1,T2,T3,T4 机器周期信号:M1,M2,M3,M4

指令周期

指令周期、机器周期、节拍周期

2.1 控制方式与时序系统

1.2 模型机的指令系统

双操作数指令格式

6

Opcode

1 1 2

d M W O D

3

REG

3

R/M

8

Data_Low

8

Data-High

8

Disp_Low

8

计算机组成原理chp5

计算机科学与技术学院系统教研室

指令寄存器IR(Instruction Register)

2、CPU的基本组成

指令译码器ID(Instruction Decoder)

暂存在指令寄存器中的指令只有在其操作码部分经译码后才 能识别出是一条什么样的指令。 译码器经过对指令进行分析和解释,产生相应的控制信号提 供给时序控制信号形成部件。 由脉冲源产生一定频率的脉冲信号作为整个机器的时钟脉冲 时序控制信号形成部件又称微操作信号发生器,真正控制各 部件工作的微操作信号是由指令部件提供的操作信号、时序 部件提供的时序信号、被控制功能部件所反馈的状态及条件 综合形成的。

计算机科学与技术学院系统教研室

5.2.3LAD指令的指令周期

取指周期 执行周期

计算机科学与技术学院系统教研室

5.2.3LAD指令的指令周期

计算机科学与技术学院系统教研室

5.2.5 ADD指令的指令周期

计算机科学与技术学院系统教研室

5.2.5ADD指令的指令周期

计算机科学与技术学院系统教研室

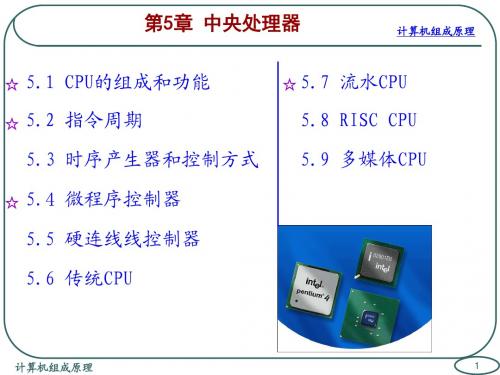

第五章 中央处理器

第五章 中央处理器

5.1CPU功能和组成 5.2指令周期 5.3时序产生器 5.4微程序控制器及其设计 5.5硬布线控制器及其设计 5.6传统CPU 5.7流水CPU 5.8RISC的CPU 5.9多媒体CPU

计算机科学与技术学院系统教研室

5.1 CPU的功能和组成

1、CPU的功能

计算机科学与技术学院系统教研室

5.2 指令周期

计算机科学与技术学院系统教研室

5.2.1 指令周期的基本概念

概念

指令周期:指取指令、分析指令到执行完该指令所需的全部 时间。 各种指令的指令周期相同吗?为什么? 机器周期通常又称CPU周期, 通常把一条指令周期划分为若干个机器周期,每个机器周期 完成一个基本操作。 主存的工作周期(存取周期)为基础来规定CPU周期,比如, 可以用CPU读取一个指令字的最短时间来规定CPU周期 不同的指令,可能包含不同数目的机器周期。 一个机器周期包含若干个时钟周期(节拍脉冲或T脉冲)。 CPU周期规定,不同的计算机中规定不同

指令寄存器IR(Instruction Register)

2、CPU的基本组成

指令译码器ID(Instruction Decoder)

暂存在指令寄存器中的指令只有在其操作码部分经译码后才 能识别出是一条什么样的指令。 译码器经过对指令进行分析和解释,产生相应的控制信号提 供给时序控制信号形成部件。 由脉冲源产生一定频率的脉冲信号作为整个机器的时钟脉冲 时序控制信号形成部件又称微操作信号发生器,真正控制各 部件工作的微操作信号是由指令部件提供的操作信号、时序 部件提供的时序信号、被控制功能部件所反馈的状态及条件 综合形成的。

计算机科学与技术学院系统教研室

5.2.3LAD指令的指令周期

取指周期 执行周期

计算机科学与技术学院系统教研室

5.2.3LAD指令的指令周期

计算机科学与技术学院系统教研室

5.2.5 ADD指令的指令周期

计算机科学与技术学院系统教研室

5.2.5ADD指令的指令周期

计算机科学与技术学院系统教研室

第五章 中央处理器

第五章 中央处理器

5.1CPU功能和组成 5.2指令周期 5.3时序产生器 5.4微程序控制器及其设计 5.5硬布线控制器及其设计 5.6传统CPU 5.7流水CPU 5.8RISC的CPU 5.9多媒体CPU

计算机科学与技术学院系统教研室

5.1 CPU的功能和组成

1、CPU的功能

计算机科学与技术学院系统教研室

5.2 指令周期

计算机科学与技术学院系统教研室

5.2.1 指令周期的基本概念

概念

指令周期:指取指令、分析指令到执行完该指令所需的全部 时间。 各种指令的指令周期相同吗?为什么? 机器周期通常又称CPU周期, 通常把一条指令周期划分为若干个机器周期,每个机器周期 完成一个基本操作。 主存的工作周期(存取周期)为基础来规定CPU周期,比如, 可以用CPU读取一个指令字的最短时间来规定CPU周期 不同的指令,可能包含不同数目的机器周期。 一个机器周期包含若干个时钟周期(节拍脉冲或T脉冲)。 CPU周期规定,不同的计算机中规定不同

计算机组成原理CPU的控制器部

微指令格式与编码

微指令的基本格式

微指令通常由操作码和地址码两部分组成。操作码用于指定该微指令所要执行的操作类型,地址码用于指定操作数的 地址或寄存器的编号。

微指令的编码方式

微指令的编码方式有多种,如直接编码、字段直接编码、字段间接编码等。不同的编码方式具有不同的特点和适用范 围,需要根据具体的应用场景进行选择。

高控制器的性能表现。

采用高速缓存技术

在控制器中引入高速缓存技术可以减 少访问主存的延迟,提高控制器的处

理速度。

提高时钟频率

增加控制器的时钟频率可以加快指令 的执行速度,从而提高控制器的性能。

优化编译器设计

改进编译器的设计可以生成更高效的 机器代码,从而减少控制器执行指令 的时间。

06

计算机组成原理与CPU控制器 关系探讨

计算机组成原理与CPU控制器相互促进

随着计算机技术的不断发展,计算机组成原理和CPU控制器的设计也在不断进步,二者相 互促进,共同推动计算机技术的发展。

THANKS

感谢观看

01

通过运行一系列标准化的基准测试程序,评估控制器的性能表

现。

微体系结构仿真

02

使用仿真工具模拟控制器的微体系结构,对其性能进行预测和

评估。

实时性能监控

03

在实际运行环境中对控制器的性能进行实时监控和数据采集,

以便对其性能进行准确评估。

提高控制器性能的途径

改进微体系结构

通过优化控制器的微体系结构,如增加 并行处理能力、改进指令流水线等,提

功能

控制器的主要功能是控制计算机各部件协调工作,确保指令 的按序执行。它负责从内存中取出指令、分析指令、确定指 令类型和操作数,然后向有关部件发出控制信号,执行该指 令。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

IBMDR、MDRDB

DBMER、MERIB

31

2.3 数据通路设计 (11.内部数据缓存)

控制总线(CB) 数据总线(DB) 地址总线(AB)

MAR 内部总线(IB)

MER

MDR

R0 R1 R2 R3

CPU内部

D ALU A

C

存储器

❖ ALU结果保存:增加寄 存器A

PC

❖ ALU数据输入缓存:增 加寄存器D

❖MIPS:百万指令每秒

➢MIPS:Million Instruction Per Second ➢不同指令集的MIPS比较没有实际意义 ➢即使同一台机器,用不同的测试程序测出来的MIPS值也可能不一样。

❖MFLOPS:百万浮点数操作每秒

➢MFLOPS: Million Floating point Operations Per Second ➢可以比较不同机器的浮点运算能力, 但有局限性 ➢MFLOPS不仅和机器有关, 也和所用测试程序有关 ➢MFLOPS与整数. 浮点操作的比例有关

移量(16位)

19

2.2 模型机的指令系统

❖指令类型

➢ 传送类指令:MOV指令,16位或32位指令 ▪ 4种传送类型:立即数寄存器,寄存器寄存器,寄存器 存储器,存储器寄存器

➢ 运算类指令:算术和逻辑运算, 16位或32位指令,RR型指令或 RS型指令,4种类型(以加法运算为例) ▪ 立即数 + 寄存器 寄存器 ▪ 寄存器 + 寄存器 寄存器 ▪ 寄存器 + 存储器 寄存器 ▪ 寄存器 + 寄存器 存储器

➢ 转移类指令 ▪ 条件/非条件转移、转子程序:32位指令,采用相对寻址 ▪ 子程序返回:16位指令

➢ 其它指令:16位指令

20

2.3 数据通路设计 (1.指令相关—组成部件)

控制总线(CB) 数据总线(DB) 地址总线(AB)

CPU内部

存储器

PC

❖ 存储器:存储指令和 数据

IR

❖ PC:当前指令地址

❖CPI:指令平均执行时钟周期数

➢CPI:Clock cycles Per Instruction。 ➢不同指令功能不同,所需时间也不同,CPI只是某一机器中一个程序或

程序片段每条指令所用时钟周期的平均值。 ➢不同指令集的CPI比较没有实际意义。 ➢程序的执行时间称为CPU时间,则有:

13

几个与指令相关的CPU性能指标

地址总线(AB)

R0 R1 R2 R3

CPU内部

存储器

PC

❖ 通用寄存器:R0、

R1、R2、R3

ALU

IR

❖ 算术逻辑运算单元

ALU

23

2.3 数据通路设计 (4.寄存器/ALU数据通路-寄存器输入)

控制总线(CB) 数据总线(DB)

地址总线(AB)

R0 R1 R2 R3

CPU内部

存储器

PC

❖ 存储器到寄存器:

18

2.2 模型机的指令系统

❖指令格式

➢ 操作码位数:固定8位 ➢ 指令长度:16位或32位 ➢ 寻址方式:5种寻址方式,立即数、寄存器直接、寄存器间接

、基址寻址、相对寻址(只用于转移类指令)

Opcode (8)

Ms Rs Mt Rt (2) (2) (2) (2)

16位长度指令格式

Opcode (8)

制信号,分组合逻辑和微程序两种实现方式。

❖中断系统

➢检查中断信号,中断CPU的正常程序执行,处理异常事务。

8

1.2 指令周期

❖指令周期基本概念(一般意义上的概念)

➢CPU取出并执行一条机器指令所需的全部时间称为指令周期。 ➢取指周期:完成取指令操作和分析指令操作所需的时间; ➢执行周期:完成指令所规定的功能所需要的时间。 ➢不同指令的指令周期不同

IR

❖ CPU内部数据暂存:增 加寄存器C

32

2.3 数据通路设计 (12.状态寄存器FR通路)

控制总线(CB) 数据总线(DB) 地址总线(AB)

IR

❖ 寄存器间接寻址:

GPRsAB

❖ 寄存器运算: GPRsALU

25

2.3 数据通路设计 (6.寄存器/ALU数据通路-ALU输入)

控制总线(CB) 数据总线(DB) 地址总线(AB)

R0 R1 R2 R3

CPU内部

存储器

❖ 寄存器运算:

PC

GPRsALU

ALU

❖ 存储器:

IR

➢ 运算

➢ 寻址计算

部计算出来的地址

IBAB

30

2.3 数据通路设计 (10.系统总线接口)

控制总线(CB) 数据总线(DB) 地址总线(AB)

MAR 内部总线(IB)

MER

MDR

R0 R1 R2 R3

CPU内部

ALU

存储器

❖ IB与AB之间:

地址缓存MAR

PC

IBMAR、MARAB

IR

❖ IB与DB之间:

数据缓存MDR、MER

❖ 转移地址计算: ALUPC

27

2.3 数据通路设计 (8.寄存器/ALU数据通路改进)

控制总线(CB) 数据总线(DB) 地址总线(AB)

存储器

PC

❖R0数据通路连接关系复杂

R1

ALU

❖R2引入内部总线

IR

R3 ➢GPRs、ALU、PC 之间的传送通过内部总线

CPU内部

➢GPRs、ALU、PC、IR 与 DB、AB 之间的传送通过内部总 线

3

1.1 CPU的功能与组成

➢CPU内部结构(内部 单总线结构) ➢执行单元(EU) ➢控制单元(CU) ➢寄存器单元 ➢中断系统 ➢内部总线

ALU

A

B

EU

GR

MAR MBR PC

微操作控制信号

微操作信号 发生器

ID

CPU

中 断 系 统

IR CU

Internal BUS

Data Bus Ctrl Bus Add Bus

2

1.1 CPU的功能与组成

❖CPU的组成

➢运算单元:算术逻辑运算单元(ALU) ➢寄存器:通用寄存器组(GPRs),标志寄存器(FR

,又称程序状态字PSW),临时寄存器(TR) ➢控制单元(CU):

▪ 指令地址部件:程序计数器(PC) ▪ 指令寄存部件:指令寄存器(IR) ▪ 译码部件:指令译码器(ID) ▪ 控制部件:微操作控制信号产生部件 ▪ 时序部件:产生时序信号 ➢内部总线:CPU内部数据通路(Internal Bus)

❖ IR:存储当前指令

21

2.3 数据通路设计 (2.指令相关—取指数据通路)

控制总线(CB) 数据总线(DB) 地址总线(AB)

CPU内部

存储器

PC

❖ 送地址:

PCABMem

❖ 读指令,

IR

MemDBIR

❖ 修改PC

22

2.3 数据通路设计 (3.寄存器/ALU相关—组成部件)

控制总线(CB) 数据总线(DB (2)

Data / Offset (16)

32位长度指令格式

Opcode:操作码(8位) Ms:源操作数寻址方式(2位) Rs:源寄存器(2位) Mt:目的操作数寻址方式(2位) Rt:目的寄存器(2位) Data:立即数(16位) Offset:基址寻址或相对寻址的位

9

1.2 指令周期

❖具有间接寻址的指令周期

➢取指周期:完成取指令操作和分析指令操作所需的时间; ➢间址周期:访问存储器,取出(或计算)有效地址所需时间; ➢执行周期:完成指令所规定的功能所需要的时间。

10

1.2 指令周期

❖取指周期数据流

➢1. PCMAR (指令地址送存储器地址寄存器MAR) ➢2. MARAdd Bus (MAR送地址总线) ➢3. 控制单元向存储器发出读命令(读取指令) ➢4. 指令从存储器读出经数据总线送到MDR ➢5. MDRIR(指令送指令寄存器IR,开始译码) ➢6. 调整PC以指向下一条指令

❖执行单元(EU-Execution Unit)

➢执行单元的核心:算术逻辑运算单元(ALU),完成算术运算、 逻辑运算、移位运算等操作;

➢寄存器:提供数据缓冲;

❖控制单元(CU-Control Unit)

➢指令寄存器IR ➢指令译码器ID(Instruction Decoder) ➢时序部件:提供各种时序信号 ➢控制信号生成部件:产生计算机其他部件所需要的所有微操作控

28

2.3 数据通路设计 (9.CPU内部总线)

控制总线(CB) 数据总线(DB) 地址总线(AB)

内部总线(IB)

R0 R1 R2 R3

CPU内部

ALU

存储器

❖ IB与GPRs之间:

PC

GPRsIB、

IBGPRs

❖ IB与ALU之间:

IR

ALUIB、IBALU

❖ IB与PC之间: IBPC、PCIB

MemDBGPRs

ALU

❖ 保存ALU结果:

IR

ALUGPRs

❖ 寄存器间传送: GPRsGPRs

24

2.3 数据通路设计 (5.寄存器/ALU数据通路-寄存器输出)

控制总线(CB) 数据总线(DB)

地址总线(AB)

R0 R1 R2 R3

CPU内部

存储器

PC

❖ 保存寄存器内容:

GPRsDBMem

ALU

4

1.1 CPU的功能与组成

❖CPU内部的寄存器

➢通用寄存器(General Register):用户可见(汇编语言可使用) ▪ 数据寄存器、基址寄存器、变址寄存器、堆栈指针、标志寄存 器等