VHDL课程设计PS键盘

超完美VHDL数码管显示键值_PS2键盘控制实验

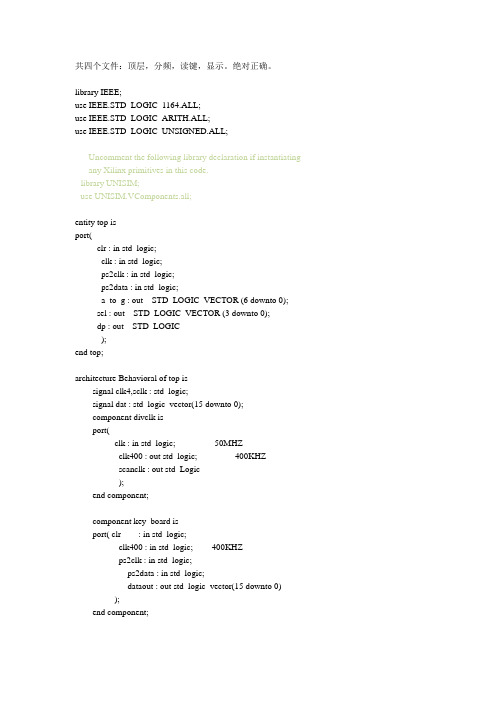

共四个文件:顶层,分频,读键,显示。

绝对正确。

library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity top isport(clr : in std_logic;clk : in std_logic;ps2clk : in std_logic;ps2data : in std_logic;a_to_g : out STD_LOGIC_VECTOR (6 downto 0);sel : out STD_LOGIC_VECTOR (3 downto 0);dp : out STD_LOGIC);end top;architecture Behavioral of top issignal clk4,sclk : std_logic;signal dat : std_logic_vector(15 downto 0);component divclk isport(clk : in std_logic; ------50MHZclk400 : out std_logic; -------400KHZscanclk : out std_Logic);end component;component key_board isport( clr : in std_logic;clk400 : in std_logic; --400KHZps2clk : in std_logic;ps2data : in std_logic;dataout : out std_logic_vector(15 downto 0));end component;component disp isport(clr : in std_logic;scanclk : in std_logic;datain : in std_logic_vector(15 downto 0);a_to_g : out STD_LOGIC_VECTOR (6 downto 0);sel : out STD_LOGIC_VECTOR (3 downto 0);dp : out STD_LOGIC);end component;begininst1: divclk port map(clk,clk4,sclk);inst2: key_board port map(clr,clk4,ps2clk,ps2data,dat);inst3: disp port map(clr,sclk,dat,a_to_g,sel,dp);end Behavioral;library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity divclk isport(clk : in std_logic; ------50MHZclk400 : out std_logic; -------400KHZscanclk : out std_Logic);end divclk;architecture Behavioral of divclk isbeginprocess(clk)variable count : std_logic_vector(19 downto 0):=X"00000"; beginif(rising_edge(clk))thencount:=count+1;end if;clk400<=count(2);scanclk<=count(12);end process;end Behavioral;library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity key_board isport( clr : in std_logic;clk400 : in std_logic; --400KHZps2clk : in std_logic;ps2data : in std_logic;dataout : out std_logic_vector(15 downto 0));end key_board;architecture Behavioral of key_board issignal clk : std_logic:='0';signal data : std_logic:='0';signal shift1,shift2 : std_logic_vector(10 downto 0);signal ps2c,ps2d : std_logic;beginps2c<=ps2clk;ps2d<=ps2data;dataout<=shift1(8 downto 1) & shift2(8 downto 1);process(clk400,clr)variable tempclk : std_logic_vector(7 downto 0):=X"00"; variable tempdata: std_logic_vector(7 downto 0):=X"00"; beginif(clr='0') thentempclk:=X"00";tempdata:=X"00";clk<='0';data<='0';else if(clk400'event and clk400='1') thentempclk(0):=ps2c;tempclk(7 downto 1):=tempclk(6 downto 0);tempdata(0):=ps2d;tempdata(7 downto 1):=tempdata(6 downto 0); end if;end if;if(tempclk="11111111") thenclk<='1';elseif(tempclk="00000000") thenclk<='0';end if;end if;if(tempdata="11111111") thendata<='1';elseif(tempdata="00000000") thendata<='0';end if;end if;end process;process(clk,clr)beginif(clr='0')thenshift1<=(others => '0');shift2<=(others => '0');else if(clk'event and clk='0') thenshift1(10)<=data;shift1(9 downto 0)<=shift1(10 downto 1);shift2(10)<=shift1(0);shift2(9 downto 0)<=shift2(10 downto 1);-- shift1(0)<=data;-- shift1(10 downto 1)<=shift1(9 downto 0);-- shift2(0)<=shift1(10);-- shift2(10 downto 1)<=shift2(9 downto 0);end if;end if;end process;end Behavioral;library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity disp isport(clr : in std_logic;scanclk : in std_logic;datain : in std_logic_vector(15 downto 0);a_to_g : out STD_LOGIC_VECTOR (6 downto 0);sel : out STD_LOGIC_VECTOR (3 downto 0);dp : out STD_LOGIC);end disp;architecture Behavioral of disp issignal S : std_logic_vector(1 downto 0);signal digit : std_logic_vector(3 downto 0);begindp<='1';process(scanclk)beginif rising_edge(scanclk) thenif(clr='0')thenS<="00";elseS<=S+1;end if;end if;end process;process(S)begincase S iswhen "00" =>digit<=datain(3 downto 0);sel<="0001";when "01" =>digit<=datain(7 downto 4);sel<="0010";when "10" =>digit<=datain(11 downto 8);sel<="0100";when others =>digit<=datain(15 downto 12);sel<="1000";end case;end process;process(digit)begin-- case digit is-- when X"0" => a_to_g<="0000001";-- when X"1" => a_to_g<="1001111";-- when X"2" => a_to_g<="0010010";-- when X"3" => a_to_g<="0000110";-- when X"4" => a_to_g<="1001100";-- when X"5" => a_to_g<="0100100";-- when X"6" => a_to_g<="0100000";-- when X"7" => a_to_g<="0001111";-- when X"8" => a_to_g<="0000000";-- when X"9" => a_to_g<="0000100";-- when X"A" => a_to_g<="0001000";-- when X"B" => a_to_g<="1100000";-- when X"C" => a_to_g<="0110001";-- when X"D" => a_to_g<="1000010";-- when X"E" => a_to_g<="0110000";-- when X"F" => a_to_g<="0111000";-- when others => a_to_g<="ZZZZZZZ";-- end case;case digit iswhen X"0" => a_to_g<="1111110";when X"1" => a_to_g<="0110000";when X"2" => a_to_g<="1101101";when X"3" => a_to_g<="1111001";when X"4" => a_to_g<="0110011";when X"5" => a_to_g<="1011011";when X"6" => a_to_g<="1011111";when X"7" => a_to_g<="1110000";when X"8" => a_to_g<="1111111";when X"9" => a_to_g<="1111011";when X"A" => a_to_g<="1110111";when X"B" => a_to_g<="0011111";when X"C" => a_to_g<="1001110";when X"D" => a_to_g<="0111101";when X"E" => a_to_g<="1001111";when X"F" => a_to_g<="1000111";when others => a_to_g<="ZZZZZZZ";end case;end process;end Behavioral;。

一种基于VHDL的PS/2键盘接口设计

一种基于VHDL的PS/2键盘接口设计【摘要】介绍了一种基于VHDL的PS/2键盘接口设计方法,在EP2C5T144C8芯片上实现。

仿真和硬件测试表明,该设计具有可靠性高和可移植性强等优点,可方便地应用于各种基于FPGA/CPLD的嵌入式系统。

【关键词】PS/2接口;VHDL;FPGA1.引言随着社会的发展,嵌入式系统技术越来越多的应用到工业控制、汽车电子、航空航天、环境监测等领域中。

键盘作为嵌入式系统中的人机接口设备得到了广泛应用。

目前,嵌入式系统中采用的键盘有:独立按键式键盘、简易矩阵键盘。

独立按键式键盘有键盘个数少,可靠性低等缺点;而简易矩阵键盘的原理是行、列式的矩阵开关,需要单独设计制作,通用性和可移植性不强,且按键数较多时I/O利用率低,软件上为了提高可靠性还要进行延时去抖动、按键扫描以及与CPU 的通信处理等,一方面降低了系统的效率,另一方面增加了系统设计的成本。

微机系统中的PS/2键盘,具有内嵌式自动去除按键抖动设计,能自动地识别键的按下与释放,软硬件开发成本低且性能稳定;因此,将PS/2键盘作为嵌入式系统中的输入设备已成为业界研究的热点。

目前,关于PS/2键盘控制的应用大部分采用单片机或微机控制;与此相比,FPGA具有灵活性更强,集成度更高,容易移植等特点。

本文在分析PS/2协议、工作原理的基础上,给出了一种基于VHDL硬件描述语言的PS/2键盘接口的设计方法,并实现于Cyclone II EP2C5T144C8芯片上。

2.PS/2键盘接口协议2.1 物理特性PS/2设备接口用于许多现代的鼠标和键盘,常用为6脚mini-DIN,其引脚结构和外形如图1所示。

图1 PS/2硬件接口外形图PS/2设备分主从设备,其物理特性要求保证时钟、数据、电源和地线间的互相连接。

PS/2键盘靠PC的PS/2端口提供+5V电源,时钟和数据管脚为集电极开路形式,必须接大阻值的上拉电阻(一般设置在主设备中),主从设备间的数据通信采用双向同步方式传输,时钟信号一般由从设备产生。

基于VHDL语言的键盘控制电路的设计报告

长沙理工大学 EDA技术与应用课程设计报告课题:基于VHDL语言的键盘控制电路的设计(24)学院:计算机与通信工程学院组员姓名及学号:段强强(200954080326)雷淑英(200954080301)胡超(200954080325)指导老师:单树民2011 年 10 月目录1、前言(写在前面) (2)2、项目工作的分类 (2)3、基于VHDL语言的键盘控制电路的设计思路 (3)4、设计的实现 (4)5、项目设计的总结及评价 (9)一、写在前面此次项目的计划、设计、以及实现的整个过程均由我组人员段强强、雷淑英、胡超三人通力合作,在此过程中虽然每个人的分工不同,耗时长短不同,但一切设计与实现均是在三人的共同参与下进行,三人齐心协力,努力为将项目做的更好的目标而努力。

同时,在项目的进行过程中,得到了老师和各位同学的热心帮助,在此对他们表示衷心的感谢。

二、项目工作的分类1、项目预备资料的收集与整理。

2、项目设计方案的斟酌与确定。

3、项目程序的设计与更改。

4、项目程序的仿真5、项目设计报告的书写与更改。

三、基于VHDL语言的键盘控制电路的设计思路1、此键盘为5*5的矩阵键盘,每个键的按下与否由这个键的行电平和列电平联合决定,当按下时为低电平“0”,没有按下时为高电平“1”。

行向量为y,列向量为x,长度都为5。

当有键按下时,检测x,y的值以确定哪个键按下。

将输入x,y并置作为判决条件,并对每一个键进行编码,送入输出变量s。

2、5*5键盘的25个键位分别为0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F,+,-,*,/,←,=,>,<,&。

x,y的值都为0000~11111,其中,x与y每次最多只能有一位为零方有效。

然后对25个键分别编码,以确定x,y的值变化时s相应的值。

3、此键盘前十个数字键不止有数字键的功能,同时在shift键的作用下还可以依次为以下10个键:!,^, (, ), _, [ , ], #, {, }。

基于VHDL利用PS_2键盘控制的密码锁设计_胡彩霞

《》2011年第5期在传统的数字电路设计实验中,如果要构建一个小型数字系统,通常要在数字电路试验箱中进行繁琐的搭线操作。

由于试验箱资源的限制使得所设计的数字系统功能会受到很大限制。

而FPGA 由于其集成度高和支持可在线编程的特点,修改电路设计变得如同修改程序一样方便[1]。

本文以电子密码锁的设计为实例,介绍了利用硬件编程语言VHDL 自顶向下地进行此系统的行为描述与结构设计,并介绍了PS/2键盘到主机的单向通信过程。

该设计中所用芯片的具体型号是XILINX 公司的具有40万门、208个管脚的SPARTAN XC3S400。

设计过程中下载模式采用主串模式,将程序下载到开发板上的EPROM 中,再由FPGA 将EPROM 中的程序读入片内编程RAM 中。

采用的EDA 开发工具为ISE 6,仿真工具是Modelsim 5.8a 。

1.数字密码锁的基本功能1.1功能描述:密码锁的设计主要达到以下四个功能:(1)密码锁加密:按下F1加密键,再按下0到9中的任四位数字作为密码。

(2)输入码激活:按下F2激活键,将已输入的四位数码作为密码或解锁码。

(3)解锁:按下F5解密键,输入的解锁码会与原密码会进行匹配。

如果成功,则开启密码锁;如果不成功,可继续解码,共有3次解密机会,当3次解密都不成功时,蜂鸣器产生报警信号宣告操作失败。

(4)数码输入:只有在按下F1加密键或F5解密键的前提下,按下0到9的数值才能显示到数码管上。

显示顺序是:随机按下的数码首先显示在四位数码管的最低位上,若确定此数码是想要的数码,再按下ENTER 键,便将此数码向左移动至左边第一个未显示的数码管上。

比如,初始时数码管显示为“XXXX ”(X 表示什么都不显示),按下一个9后,显示的是“XXX9”,再按下ENTER 键后,显示为“9XXX ”。

当输入的数码已达四位数时,按下F2激活键,便可将这四位数作为密码。

由于开发板上只有4个数码管,所以密码设定为4位,在实际中为了增加安全性,可以设置为更多位,还可将字母键扩展为密码。

基于VHDL的键盘扫描电路设计设计

毕业论文(设计)题目:基于VHDL的键盘扫描电路设计系:机电工程系学生姓名:专业:电子信息工程班级:指导教师:起止日期: 2012.10.15——2013.01.06 2013年1 月6 日基于VHDL的键盘扫描电路设计(东海科学技术学院机电工程系,浙江舟山 316000)摘要随着科技的发展,时代的进步,生活的需要,在我们生活的很多地方领域,都有键盘的应用,而且它的应用非常广,当然键盘扫描的方法也有很多种。

键盘是单片机系统设计中一种主要的信息输入接口,合理的设计,不仅可以节省系统的设计成本,更可以使仪器设备的操作变得更为简单、方便、快捷,很大程度上提高系统综合性能。

随着信息产业和微电子技术的发展,很多系统设计技术已经成为信息产业最热门的技术之一,在很多地方上都有应用,比如航空航天、医疗保健、通讯、广播、工业、测量测试等很多热门领域。

并且随着工艺的进步和技术的发展,向更广泛的应用领域扩展。

矚慫润厲钐瘗睞枥庑赖。

本次设计主要是运用VHDL硬件描述语言和图形设计综合方法,在MAX+PLUSⅡ软件平台的环境下建立波形文件,生成电路符号,设置输入端口,实现程序的模拟仿真,得到仿真波形图,才完成了键盘扫描电路的程序设计。

这个电路设计是一个关于小型的计算器的键盘按键电路的设计,主要由5个部分组成,它们分别为分频器电路、键盘扫描计数器电路、按键检测电路、按键抖动消除电路和键盘编码电路。

本次设计主要是设计一个4×4矩阵式的键盘扫描电路,它具有列扫描和行扫描的功能,有2个输入端口,分别为clk和col,同时也有2个输出端口,分别为row和bianma,按下按键的数据通过端口行、列线输入到FPGA芯片中去,FPGA芯片内部的扫描模块会将数据传送到编码器中进行编码,最终完成本次电路的设计。

在生活中是这种小型的计算器是非常常用的,虽然体型很小,但却被广泛的使用,很多其他的东西都是在这种小型的计算器的键盘的基础上设计的。

基于VHDL的键盘扫描及显示电路毕业设计

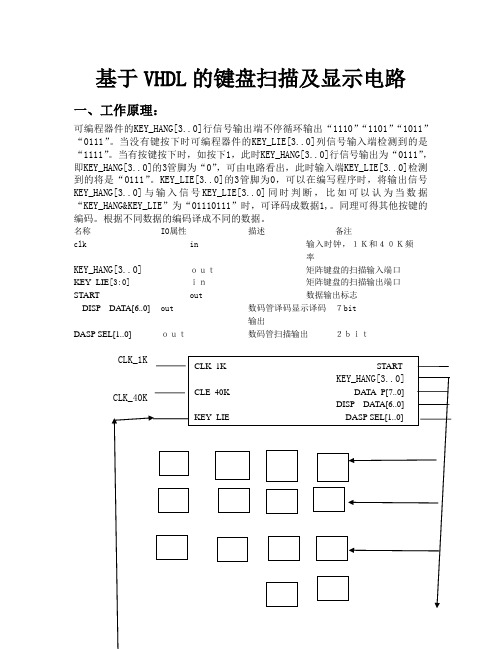

基于VHDL的键盘扫描及显示电路一、工作原理:可编程器件的KEY_HANG[3..0]行信号输出端不停循环输出“1110”“1101”“1011”“0111”。

当没有键按下时可编程器件的KEY_LIE[3..0]列信号输入端检测到的是“1111”。

当有按键按下时,如按下1,此时KEY_HANG[3..0]行信号输出为“0111”,即KEY_HANG[3..0]的3管脚为“0”,可由电路看出,此时输入端KEY_LIE[3..0]检测到的将是“0111”。

KEY_LIE[3..0]的3管脚为0,可以在编写程序时,将输出信号KEY_HANG[3..0]与输入信号KEY_LIE[3..0]同时判断,比如可以认为当数据“KEY_HANG&KEY_LIE”为“01110111”时,可译码成数据1,。

同理可得其他按键的编码。

根据不同数据的编码译成不同的数据。

名称IO属性描述备注clk in 输入时钟,1K和40K频率KEY_HANG[3..0]out矩阵键盘的扫描输入端口KEY_LIE[3:0] in矩阵键盘的扫描输出端口START out 数据输出标志DISP DATA[6..0]out 数码管译码显示译码输出7bitDASP SEL[1..0] out数码管扫描输出2bitCLK_1K CLK_40K CLK_1K STARTKEY_HANG[3..0] CLE_40K DATA_P[7..0]DISP DATA[6..0] KEY_LIE DASP SEL[1..0]二、设计思路:1.循环输出行信号,检测列信号输入,将行列信号相并。

2.译键值。

3.去抖动。

在译没一个键值后,为了防止抖动,加了一个计算环节,一旦检测到列信号后,译码,紧跟着进入计数环节,此时键抖动不会进入其他环节,这样可以防止抖动。

4.数码管译码、循环显示。

电路的具体功能罗列如下:1) 采用4×4矩阵键盘作为操作数和操作符的输入设备。

基于verilog的PS2键盘设计进阶

实验九、基于verilog的PS/2键盘设计进阶一、前言及背景:说到PS/2相信大家都不会陌生,不错的,我们日常的鼠标键盘大多是基于P S/2接口设计的。

虽然USB鼠标大有取而代之之势,但是依然阻止不了我们这群IT菜鸟掌握它的强烈欲望,而使用verilog来做PS/2的解码更是需要我们把P S/2的传输协议理解的更透彻一些。

所以,下面就让特权同学带领大家一步一步掌握PS/2。

PS/2接口标准的发展过程随着计算机工业的发展,作为计算机最常用输入设备的键盘也日新月异。

19 81年IBM推出了IBM pc/XT键盘及其接口标准。

该标准定义了83键,采用5脚DIN连接器和简单的串行协议。

实际上,第一套键盘扫描码集并没有主机到键盘的命令。

为此,1984年IBM推出了IBM AT键盘接口标准。

该标准定义了84~10 1键,采用5脚DIN连接器和双向串行通讯协议,此协议依照第二套键盘扫描码集设有8个主机到键盘的命令。

到了1987年,IBM又推出了PS/2键盘接口标准。

该标准仍旧定义了84~101键,但是采用6脚mini-DIN连接器,该连接器在封装上更小巧,仍然用双向串行通讯协议并且提供有可选择的第三套键盘扫描码集,同时支持17个主机到键盘的命令。

现在,市面上的键盘都和PS/2及AT键盘兼容,只是功能不同而已。

(4)延时20us(如果此时正在发送起始位,则应延时40us);(5)输出起始位(0)到数据线上。

这里要注意的是:在送出每一位后都要检测时钟线,以确保PC机没有抑制PS/2设备,如果有则中止发送;(6)输出8个数据位到数据线上;(7)输出校验位;(8)输出停止位(1);(9)延时30us(如果在发送停止位时释放时钟信号则应延时50us);通过以下步骤可发送单个位:(1)准备数据位(将需要发送的数据位放到数据线上);(2)延时20us;(3)把时钟线拉低;(4)延时40us;(5)释放时钟线;(6)延时20us。

用VHDL设计键盘输入显示方案

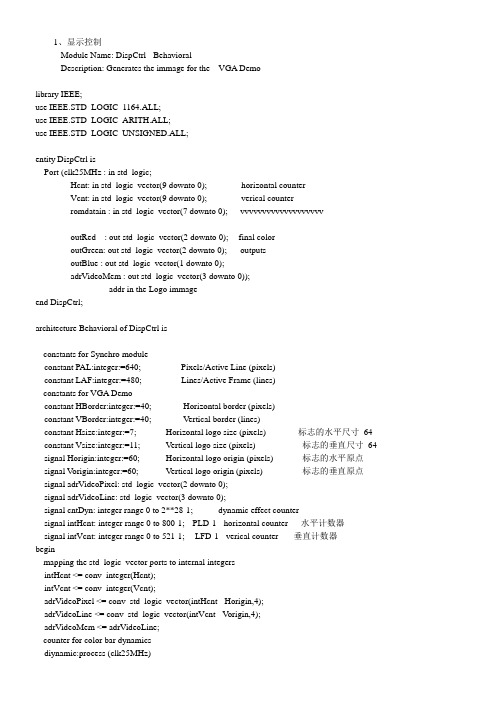

1、显示控制-- Module Name: DispCtrl - Behavioral-- Description: Generates the immage for the VGA Demo--------------------------------------------------------------------------------library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity DispCtrl isPort (clk25MHz : in std_logic;Hcnt: in std_logic_vector(9 downto 0); -- horizontal counterVcnt: in std_logic_vector(9 downto 0); -- verical counterromdatain : in std_logic_vector(7 downto 0); -- vvvvvvvvvvvvvvvvvvvoutRed : out std_logic_vector(2 downto 0); -- final coloroutGreen: out std_logic_vector(2 downto 0); -- outputsoutBlue : out std_logic_vector(1 downto 0);adrV ideoMem : out std_logic_vector(3 downto 0));-- addr in the Logo immageend DispCtrl;architecture Behavioral of DispCtrl is-- constants for Synchro moduleconstant PAL:integer:=640; --Pixels/Active Line (pixels)constant LAF:integer:=480; --Lines/Active Frame (lines)-- constants for VGA Democonstant HBorder:integer:=40; -- Horizontal border (pixels)constant VBorder:integer:=40; -- V ertical border (lines)constant Hsize:integer:=7; -- Horizontal logo size (pixels) 标志的水平尺寸64 constant Vsize:integer:=11; -- V ertical logo size (pixels) 标志的垂直尺寸64 signal Horigin:integer:=60; -- Horizontal logo origin (pixels) 标志的水平原点signal V origin:integer:=60; -- V ertical logo origin (pixels) 标志的垂直原点signal adrVideoPixel: std_logic_vector(2 downto 0);signal adrVideoLine: std_logic_vector(3 downto 0);signal cntDyn: integer range 0 to 2**28-1; -- dynamic effect countersignal intHcnt: integer range 0 to 800-1; --PLD-1 - horizontal counter--- 水平计数器signal intVcnt: integer range 0 to 521-1; -- LFD-1 - verical counter --- 垂直计数器begin-- mapping the std_logic_vector ports to internal integersintHcnt <= conv_integer(Hcnt);intVcnt <= conv_integer(Vcnt);adrV ideoPixel <= conv_std_logic_vector(intHcnt - Horigin,4);adrV ideoLine <= conv_std_logic_vector(intVcnt - V origin,4);adrV ideoMem <= adrVideoLine;-- counter for color bar dynamicsdiynamic:process (clk25MHz)beginif clk25MHz'event and clk25MHz = '1' thencntDyn <= cntDyn+1;end if;end process;mixer: process(clk25MHz,intHcnt, intVcnt)beginif intHcnt < PAL and intVcnt < LAF then -- 在激活的显示区域if intHcnt >= Horigin and intHcnt <= Horigin + Hsize andintVcnt >= V origin and intVcnt <= V origin + Vsizethen -- image --rom中的数据输出作为色差的信息;if romdatain(adrVideoPixel)='0' thenoutRed<="100";outGreen<="100";outBlue(1 downto 0) <="01";else -- the moving lines area-- redoutRed(2 downto 0) <="000";-- greenoutGreen(2 downto 0) <="000";-- blueoutBlue(1 downto 0) <="00";end if;elseoutRed <= (others => '0');outGreen <= (others => '0');outBlue <= (others => '0');end if;end if;end process;-- place the logo at the mouse pos, if left button pressedend Behavioral;2 、PS接口定义见附件中Keyctrl.vhd和Ps2keyboard.vhd3、状态灯指示字母输入见附件中SnakeledDemo.vhd。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录一、课程设计的目的与任务(1)熟练掌握EDA工具软件QuartusII的使用;(2)熟练用VHDL硬件描述语言描述数字电路;(3)学会使用VHDL进行大规模集成电路设计;(4)学会用CPLD\FPGA使用系统硬件验证电路设计的正确性;(5)初步掌握EDA技术并具备一定的可编程逻辑芯片的开发能力;二、课程设计题目1、指定题目:0 :多功能计数器; 1 :数字秒表; 2 :简易数字钟; 3 :简易频率计;4 :彩灯控制器;5 :交通灯控制器;6 :四路智力竞赛抢答器;7 :简易微波炉控制器; 8 :表决器;9 :数字密码锁;我的的学号尾数是2,所以我要做的题目是简易数字钟。

由于我之前已经学过Verilog HDL和VHDL,所以简易数字钟相对于我比较简单,我完成了简易数字钟并验收后,再选择了另一个自选题目来完成。

简易数字钟:设计一个以“秒”为基准信号的简易数字钟,显示时、分、秒,同时可实现整点报时和清零(我已经完成,而且已经验收了)。

2、自选题目:在完成了数字钟的设计后,我选择了另一个设计的题目,那就是PS2键盘扫描。

所以这次课程设计我的报告主要详细写的是PS2键盘扫描的程序,而不是简易数字钟。

PS键盘扫描:设计一个PS键盘扫描程序,能接受键盘的输入时钟和数据,区别哪一个键输入,同时解译通码和断码,使用LED灯来显示收到的数据。

三、课程设计的内容与要求1、设计内容(1)系统功能的分析;(2)实现系统功能的实际方案;(3)编写各功能模块的VHDL语言程序;(4)对各功能模块进行编译、综合、仿真、分析;(5)顶层文件设计(6)对整个系统进行编译、综合、仿真、分析;(7)在CPLD\FPGA实验开发系统试验箱上进行硬件验证;(8)写实验报告;2、设计要求(1)按所布置的题目要求,每一位学生独立完成全过程;(2)分模块层次化设计;(3)各功能模块的底层文件必须用VHDL语言设计,顶层文件可用VHDL语言设计,也可以用原理图设计。

四、实验仪器设备(1)PC机;(2)QuartusII软件;(3)黑金FPGA实验开发系统,芯片为Cyclone II的EP2C5Q208C8;五、设计方案1、PS2解码图1为PS2的接口图。

我使用的的右边的PS2接口,即1脚为数据脚,5脚为时钟脚,同时我编写的VHDL代码只对1脚和5脚操作。

图2PS2协议时序图图2为PS2协议时序图。

由图可以解读出,PS2协议对数据的读取时“CLK的下降沿”有效,而数据的放置时在“CLK的上升沿”。

PS2频率比较慢,大概为10KHz。

第N位属性0开始位1~8数据位9校验位10结束位表1 PS2数据说明PS2的一帧数据时11位。

对PS2进行解码,我们需要得到的是1~8位的数据位。

其他的位,可以使用取巧的方法编写。

键盘的编码有“通码(Make)”和“断码(Break)”之分。

通码相当于某个按键按下了,断码相当于某个按键释放了。

假设,我们按下了“Z”键不放,大约每秒有10个X“1A”的通码(10KHz),而当我们释放“Z”键,就会输出断码X“F0”和X“1A”。

同时,键盘编码一次只能有一个输出,即多个按键同时按下时,只有一个有效。

下表为第二套PC键盘扫描码。

表2 PC 键盘第二套扫描码2、设计思路(1)PS2时钟的检测;(2)PS2数据的接受并提取需要的8位数据; (3)对PS2提取的8位数据进行解码,确定按键; (4)通过LED 灯显示按键的解码的结果; (5)设置多个按键,多种LED 显示方式;对于PS2键盘扫描程序,我的设计思路是一个模块一个功能,这样能清晰分辨模块,同时易于修改代码。

代码条理清晰,便于解读。

而对于多个模块则使用层次化的形式来编写,顶层文件并不包含功能的设定,只包含各个子功能模块。

3、模块设计PS2键盘扫描分为:电平检测,PS2解码,PS2组合,LED 控制和总PS 组合六个模块。

下面为各个模块的简易模块图。

(1)PS2时钟检测模块:图3 电平检测模块图(2)PS2解码模块:图4 PS2解码模块图(3)PS2组合模块:PS2解码模块 PS2_encode_module PS2_Data_Pin_In PS2_Data H_L_SigPS2_Done_SigPS2_CLK_Pin_InH_L_Sig L_H_Sig电平检测模块 PS2_detect_module图5 PS2组合模块图(4)控制LED 模块:图6 LED 控制模块图(5)PS2总的组合模块:图7 PS2模块图4、各模块分析(1) PS2时钟检测模块PS2电平检测模块主要的作用是检测PS2接口键盘的时钟信号,因为PS2的协议规定数据是在时钟的下降沿读取的。

所以电平检测模块要检测PS2时钟的下降沿,有下降沿来临时,要做相应的数据读取动作。

下面是代码的分析。

LIBRARY IEEE;--库 USE PS2_detect_module IS--实体声明PORT( CLK,RSTn : IN STD_LOGIC; PS2_CLK_Pin_In : IN STD_LOGIC; H_L_Sig : OUT STD_LOGIC; --电平由高变低,输出一个信号 L_H_Sig : OUT STD_LOGIC--电平由低变高,输出一个信号);END ENTITY PS2_detect_module;PS2_Done_SigPS2_DatPS2_Data_Pin_InPS2_CLK_Pin_In Data_Out电平检测模块 PS2_control_module电平检测模块 PS2_control_modulePS2_Data Data_Out电平检测模块 PS2_control_modulePS2_Done_SigPS2解码模块 PS2_encode_modulePS2_Data_Pin_InPS2_DataPS2_Done_SigPS2_CLK_Pin_InH_L_Sig电平检测模块 PS2_detect_module------------------------------------------------------------------------------------------------------------------------------------------ARCHITECTURE PS2_detect OF PS2_detect_module IS --结构体声明SIGNAL H_L_F1 : STD_LOGIC :='1'; --声明4个信号,用于电平输入的变化SIGNAL H_L_F2 : STD_LOGIC :='1'; --4个信号都赋了初值SIGNAL L_H_F1 : STD_LOGIC :='0';SIGNAL L_H_F2 : STD_LOGIC :='0';BEGINPROCESS(CLK,RSTn)BEGINIF (CLK'event AND CLK='1') THEN --同步进行IF (RSTn='0') THEN --同步复位动作H_L_F1 <= '1';H_L_F2 <= '1';L_H_F1 <= '0';L_H_F2 <= '0';ELSEH_L_F1 <= PS2_CLK_Pin_In;H_L_F2 <= H_L_F1;L_H_F1 <= PS2_CLK_Pin_In;L_H_F2 <= L_H_F1;END IF;END IF;END PROCESS;H_L_Sig <= H_L_F2 AND (NOT H_L_F1); --输出信号L_H_Sig <= L_H_F1 AND (NOT L_H_F2);END ARCHITECTURE PS2_detect; --结构体结束在结构体中声明了4个信号,用于电平的检测F2信号是接着F1信号的,如果F1信号变化了,F2信号还不会立即变化,F2还会保持F1的前一个状态,以两者的逻辑关系,可以判断输入的是上升沿还是下降沿。

结果如表格3。

表3 电平检测变化表(2) PS2解码模块LIBRARY IEEE; --库USE PS2_decode_module IS --实体声明PORT(CLK,RSTn : IN STD_LOGIC;H_L_Sig : IN STD_LOGIC;PS2_Data_Pin_In : IN STD_LOGIC;PS2_Done_Sig : OUT STD_LOGIC;PS2_Data : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END ENTITY PS2_decode_module;------------------------------------------------------------------------------------------------------------------------------------------ARCHITECTURE PS2_decode OF PS2_decode_module ISSIGNAL Done : STD_LOGIC :='0'; --声明一个完成信号SIGNAL i : STD_LOGIC_VECTOR(4 DOWNTO 0) :="00001"; --声明步骤iSIGNAL Data : STD_LOGIC_VECTOR(7 DOWNTO 0) :=X"32";BEGINPROCESS(CLK,RSTn,i)BEGINIF (CLK'event AND CLK='1') THENIF (RSTn='0') THENi <= "00001";Done <= '0';Data <= X"00";ELSECASE i ISWHEN "00000" => i <= "00001";WHEN "00001" => IF (H_L_Sig='1') THEN i <= "00010";Data(0) <= PS2_Data_Pin_In;END IF;WHEN "00010" => IF (H_L_Sig='1') THEN i <= "00011";Data(1) <= PS2_Data_Pin_In;END IF;WHEN "00011" => IF (H_L_Sig='1') THEN i <= "00100";Data(2) <= PS2_Data_Pin_In;END IF;WHEN "00100" => IF (H_L_Sig='1') THEN i <= "00101";Data(3) <= PS2_Data_Pin_In;END IF;WHEN "00101" => IF (H_L_Sig='1') THEN i <= "00110";Data(4) <= PS2_Data_Pin_In;END IF;WHEN "00110" => IF (H_L_Sig='1') THEN i <= "00111";Data(5) <= PS2_Data_Pin_In;END IF;WHEN "00111" => IF (H_L_Sig='1') THEN i <= "01000";Data(6) <= PS2_Data_Pin_In;END IF;WHEN "01000" => IF (H_L_Sig='1') THEN i <= "01001";Data(7) <= PS2_Data_Pin_In;END IF;WHEN "01001" => IF (H_L_Sig='1') THEN i <= "01010";END IF;WHEN "01010" => IF (H_L_Sig='1') THEN i <= "01011";END IF;WHEN "01011" => IF (Data=X"F0") THEN i <= "01100";ELSE i <= "10110";END IF;WHEN "01100" => IF (H_L_Sig='1') THEN i <= "01101";END IF;WHEN "01101" => IF (H_L_Sig='1') THEN i <= "01110";END IF;WHEN "01110" => IF (H_L_Sig='1') THEN i <= "01111";END IF;WHEN "01111" => IF (H_L_Sig='1') THEN i <= "10000";END IF;WHEN "10000" => IF (H_L_Sig='1') THEN i <= "10001";END IF;WHEN "10001" => IF (H_L_Sig='1') THEN i <= "10010";END IF;WHEN "10010" => IF (H_L_Sig='1') THEN i <= "10011";END IF;WHEN "10011" => IF (H_L_Sig='1') THEN i <= "10100";END IF;WHEN "10100" => IF (H_L_Sig='1') THEN i <= "10101";END IF;WHEN "10101" => IF (H_L_Sig='1') THEN i <= "10110";END IF;WHEN "10110" => IF (H_L_Sig='1') THEN i <= "10111";Done <= '1';END IF;WHEN "10111" => IF (H_L_Sig='1') THEN i <= "00001";Done <= '0';END IF;WHEN OTHERS => i <= "00001";END CASE;END IF;END IF;END PROCESS;PS2_Data <= Data;PS2_Done_Sig <= Done;END ARCHITECTURE PS2_decode;这个模块我有点偷懒,只对键盘输入的8位有效数据进行了提取,其他位基本是忽略了,第一位开始位忽略了,然后是读取8位有效数据,第9步和第10步跳过了检测位和结束位,然后是判断。