三人表决器实验

三人表决器、五人表决器的实验报告

三人表决器、五人表决器的实验报告

一 实验目的

1.熟悉Quartus II 软件的基本操作

2.学习使用Verilog HDL 进行设计输入

3.逐步掌握软件输入、编译、仿真的过程 二 实验说明

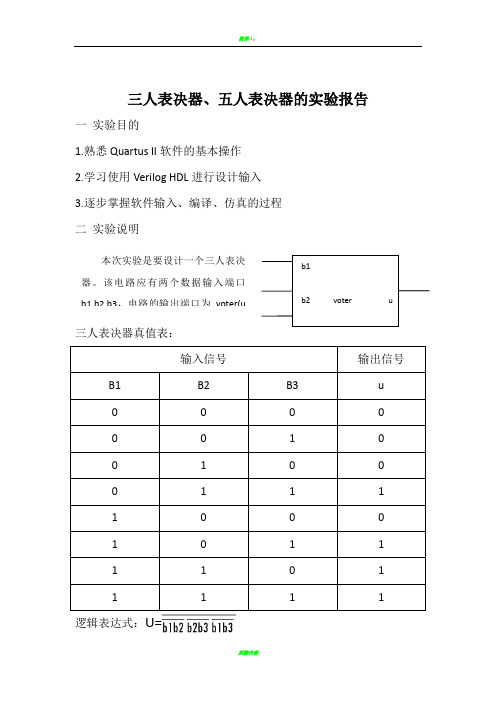

三人表决器真值表:

输入信号

输出信号

B1 B2 B3 u 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 1 1

1

1

1

逻辑表达式:U=

b1

b2 voter u

本次实验是要设计一个三人表决器。

该电路应有两个数据输入端口b1,b2,b3,电路的输出端口为voter(u

三实验要求

1、完成三人表决器的Verilog HDL程序代码输入并进行仿真

2、采用结构描述方式和数据流描述方式

3、完成对设计电路的仿真验证

四、实验过程

(1)三人表决器:

程序代码

仿真结果

五人表决器:

程序代码

仿真结果

五、实验体会

通过三人表决器和五人表决器的设计,使我们更加熟悉Quartus 软件进行数字系统设计的步骤,以及运用Verilog HDL进行设计输入,并掌握三人表决器和五人表决器的逻辑功能和设计原理,逐步理解功能仿真和时序仿真波形。

三人表决器和五人表决器大体相似,并没有太大的区别。

三人表决器仿真实验分析

三人表决器摘要本次设计的三人表决器,是投票系统中的客户端,是一种代表投票或举手表决的表决装置。

表决时,与会的有关人员只要按动各自表决器上“赞成”“反对”“弃权”的某一按钮,荧光屏上即显示出表决结果。

在三人表决器中三个人分别用手指拨动开关S W1、S W2、S W3来表示自己的意愿,如果对某决议同意,各人就把自己的指拨开关拨到高电平(上方),不同意就把自己的指拨开关拨到低电平(下方)。

表决结果用L E D(高电平亮)显示,如果决议通过那么实验板上L2亮;如果不通过那么实验板上L1亮;如果对某个决议有任意二到三人同意,那么此决议通过,L2亮;如果对某个决议只有一个人或没人同意,那么此决议不通过,L1亮。

一.任务设计三人表决器电路,并在仿真软件上验证电路的正确性。

二.目标掌握三人表决器电路的结构。

学会仿真软件数字部分的操作。

三.要求1复习三人表决器电路的设计步骤。

2熟悉用集成电路的引脚位置及各引脚用途。

3使用TTL门电路时,一定要正确连接电源端和接地端4按集成电路引脚图正确接线,芯片电源引脚不要接错,以免损坏芯片,影响实验正常进行。

四.实训工具及设备电脑一台;Mult isi m软件五.仿真电路图六.设计的主要内容:按照设计题目,根据所学的组合逻辑所学的知识及数字电路和嵌入式的知识完成三人表决器的设计,使之能够满足表决时少数服从多数的表决规则,根据逻辑真值表和逻辑表达式完成表决功能。

七.三人表决器概述:1.三人表决器的功能描述三个人分别用手指拨动开关S W1、S W2、S W3来表示自己的意愿,如果对某决议同意,各人就把自己的指拨开关拨到高电平(上方),不同意就把自己的指拨开关拨到低电平(下方)。

表决结果用LE D (高电平亮)显示,如果决议通过那么实验板上L2亮;如果不通过那么实验板上L1亮;如果对某个决议有任意二到三人同意,那么此决议通过,L2亮;如果对某个决议只有一个人或没人同意,那么此决议不通过,L1亮2.三人表决器”的逻辑功能表决结果与多数人意见相同。

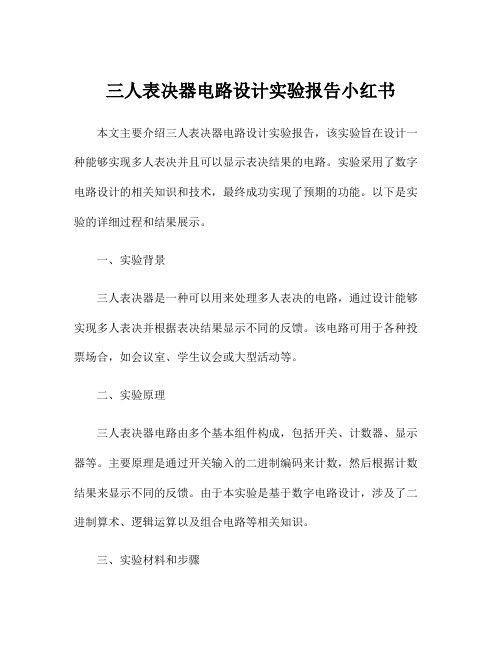

三人表决器电路设计实验报告小红书

三人表决器电路设计实验报告小红书本文主要介绍三人表决器电路设计实验报告,该实验旨在设计一种能够实现多人表决并且可以显示表决结果的电路。

实验采用了数字电路设计的相关知识和技术,最终成功实现了预期的功能。

以下是实验的详细过程和结果展示。

一、实验背景三人表决器是一种可以用来处理多人表决的电路,通过设计能够实现多人表决并根据表决结果显示不同的反馈。

该电路可用于各种投票场合,如会议室、学生议会或大型活动等。

二、实验原理三人表决器电路由多个基本组件构成,包括开关、计数器、显示器等。

主要原理是通过开关输入的二进制编码来计数,然后根据计数结果来显示不同的反馈。

由于本实验是基于数字电路设计,涉及了二进制算术、逻辑运算以及组合电路等相关知识。

三、实验材料和步骤实验所需材料:(1)开发板:FPGA开发板(2)元器件:LED灯、计数器模块、开关、电路板实验步骤:(1)原理和电路设计确定并使用EDA软件进行电路图设计。

(2)电路原型制作,验收并进行调试(3)连接电路,在开发板上植入(或flash)bit文件。

(4)将开关、LED灯和计数器模块等电路元件安装在电路板上。

(5)通过开关输入不同的二进制编码,以观察显示器的反馈结果。

四、实验结果分析在实验进行过程中,我们成功地完成了电路的设计、制作和测试,并达到了预期的实验目的。

在实验中,我们通过FPGA开发板编写了硬件描述语言(HDL)来描述电路,并成功将其烧录进开发板中。

在测试的过程中,我们使用了开关来输入二进制编码,并且观察到了不同的计数结果。

同时,我们还观察到了预期的反馈结果,包括LED灯逐个亮起、提示声音和不同的计数显示。

总结:本次实验成功地实现了三人表决器电路设计的目的,我们通过HDL 语言进行了电路设计,利用开发板和相关元器件完成了电路的制作,并通过实验测试获得了较好的实验结果。

该实验不仅增强了我们对数字电路设计的理解和实践能力,同时也扩展了我们的应用技能,有助于提高实际工作中数字电路设计的水平。

三人表决项目报告

三人表决器项目报告系别:专业:姓名:指导老师:学号:摘要本次设计的三人表决器,是投票系统中的客户端,是一种代表投票或举手表决的表决装置。

表决时,与会的有关人员只要按动各自表决器上“赞成”“反对”。

在三人表决器中三个人分别用开关SW1、SW2、SW3的状态来表示自己的意愿。

1、项目功能三个人分别用手指拨动开关SW1、SW2、SW3来表示自己的意愿,如果对某决议同意,各人就把自己的指拨开关拨到高电平,不同意就把自己的指拨开关拨到低电平。

表决结果用LED(高电平亮)显示,如果两个及其两个以上通过那么实验板上LED灯亮,如果没有人通过或者只有一人通过没通过则不亮。

2、项目目标1. 熟悉逻辑函数的表示方法与化简方法;2. 正确理解数字电路的要求,能知道与门、或门、非门的含义。

3. 了解要用到的每个芯片的引脚是什么门电路并且运用。

3、实验器材:输入输出模块,面包板,芯片74LS20、74LS00、74LS138、74LS153,导线四、实验步骤1、得出真值表和卡诺图设:A、B、C分别代表三个输入,同意为1,不同意为0;Y为输出,通过为1,不通过为0。

有真值表可得出卡诺图如下:由卡诺图可知化简后表达式如下:Y=BC+AC+AB2、设计电路,接入输入输出模块进行试验方案一:芯片74LS00与74LS2074 LS00是四-二输入与非门,它内部有四个与非门,每个与非门有两个输入端、一个输入端。

74 LS20是二-四输入与非门,它内部有两个与非门,每个与非门有四个输入端、一个输出端。

74 LS00、74 LS20引脚及内部电路图(1-1)图1-1: 74LS00 74 LS20 电路图接法如下:74LS00的VCC与74LS20的VCC接5V的直流电,两块芯片的7脚都接地;74LS00的1、13脚接输入端A;2、5脚接输入端B;4、12脚接输入端C。

74LS的11、3、6脚接在74LS20的1、2、4脚上;74LS20的6脚为输出Y。

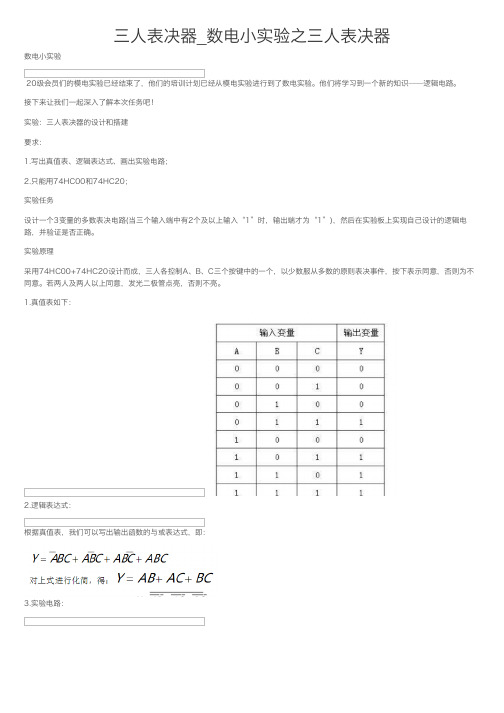

三人表决器_数电小实验之三人表决器

三⼈表决器_数电⼩实验之三⼈表决器数电⼩实验20级会员们的模电实验已经结束了,他们的培训计划已经从模电实验进⾏到了数电实验。

他们将学习到⼀个新的知识——逻辑电路。

接下来让我们⼀起深⼊了解本次任务吧!实验:三⼈表决器的设计和搭建要求:1.写出真值表、逻辑表达式、画出实验电路;2.只能⽤74HC00和74HC20;实验任务设计⼀个3变量的多数表决电路(当三个输⼊端中有2个及以上输⼊“1”时,输出端才为“1”),然后在实验板上实现⾃⼰设计的逻辑电路,并验证是否正确。

实验原理采⽤74HC00+74HC20设计⽽成,三⼈各控制A、B、C三个按键中的⼀个,以少数服从多数的原则表决事件,按下表⽰同意,否则为不同意。

若两⼈及两⼈以上同意,发光⼆极管点亮,否则不亮。

1.真值表如下:2.逻辑表达式:根据真值表,我们可以写出输出函数的与或表达式,即:3.实验电路:74HC00四与⾮门:芯⽚介绍:74HC00 是TTL2 输⼊端四与⾮门,⾼电平4V,低电平1V,与⾮门电路经常⽤来实现组合逻辑的运算。

74HC20四输⼊双与⾮门:74HC20是常⽤的双四输⼊与⾮门集成电路,常⽤在各种数字电路和单⽚机系统中。

认真学习的20级会员们:看着⼩20们努⼒的⾝影,像是看到了去年的我们,这些实验不仅提⾼了他们的动⼿实践能⼒,也为将来的单⽚机学习打下了良好的基础。

届届传承的精神:热⼼善良的学长们,时刻⿎舞着20级们的学习,不仅为他们拓展了数电实验的新知识,同时也激发了他们的学习兴趣,使他们在学习中更有⾃信。

成功不是将来才有的,⽽是从决定去做的那⼀刻起,持续累积⽽成,现在的点滴付出,在不久的将来,将会有意想不到的结果。

因为疫情使协会会员们来得晚放假得早,但协会会员们都克服了种种困难,在较短的时间内完成了各⾃的学习任务且表现良好。

希望未来20级会员们能够尽快成长,在协会撑起⼀⽚天。

扫码关注我们郑州铁院⽆线电做事先做⼈编辑:物联⽹19A1苏笑颜⽂字:物联⽹19A1苏笑颜校审:铁道车辆19A2孟珊如审核:王云飞、张凯。

实验五 三人表决器实验报告

实验五三人表决器实验报告一、实验目的本次实验的主要目的是设计并实现一个三人表决器,通过逻辑门电路来判断三个输入信号的多数情况,从而输出相应的表决结果。

通过这个实验,我们将深入理解数字逻辑电路的基本原理和设计方法,提高我们的电路分析和设计能力。

二、实验原理三人表决器的功能是当有两个或三个输入为“1”时,输出为“1”;否则,输出为“0”。

我们可以使用逻辑门电路来实现这个功能。

首先,我们可以使用与门和或门来构建这个电路。

将三个输入信号分别标记为 A、B、C。

我们先将 A、B 进行与运算,得到结果 D;再将 B、C 进行与运算,得到结果 E;然后将 A、C 进行与运算,得到结果 F。

接着,将 D、E、F 进行或运算,得到结果 G。

最后,将 G 再进行一次非运算,就得到了最终的表决结果 Y。

其逻辑表达式为:Y =((A ∧ B)∨(B ∧ C)∨(A ∧ C))。

三、实验器材1、数字电路实验箱2、 74LS00 四 2 输入与非门芯片3、 74LS08 四 2 输入与门芯片4、 74LS32 四 2 输入或门芯片5、导线若干四、实验步骤1、按照实验原理,在数字电路实验箱上连接电路。

将 74LS00、74LS08 和 74LS32 芯片插入相应的插槽中,并使用导线将各个芯片的引脚连接起来,形成完整的三人表决器电路。

2、连接输入信号。

将三个开关分别连接到 A、B、C 输入端口,用于模拟三个表决人的表决情况。

3、观察输出结果。

打开实验箱电源,通过拨动三个开关的状态(“0”表示反对,“1”表示赞成),观察输出端口的指示灯状态,以确定表决结果。

4、记录实验数据。

分别记录不同输入组合情况下的输出结果,并填写在实验表格中。

五、实验数据及结果分析|输入 A |输入 B |输入 C |输出 Y ||||||| 0 | 0 | 0 | 0 || 0 | 0 | 1 | 0 || 0 | 1 | 0 | 0 || 1 | 0 | 0 | 0 || 0 | 1 | 1 | 1 || 1 | 0 | 1 | 1 || 1 | 1 | 0 | 1 || 1 | 1 | 1 | 1 |通过对实验数据的分析,我们可以发现,当输入为000、001、010、100 时,输出为 0;当输入为 011、101、110、111 时,输出为 1,这与我们预期的三人表决器的功能完全一致。

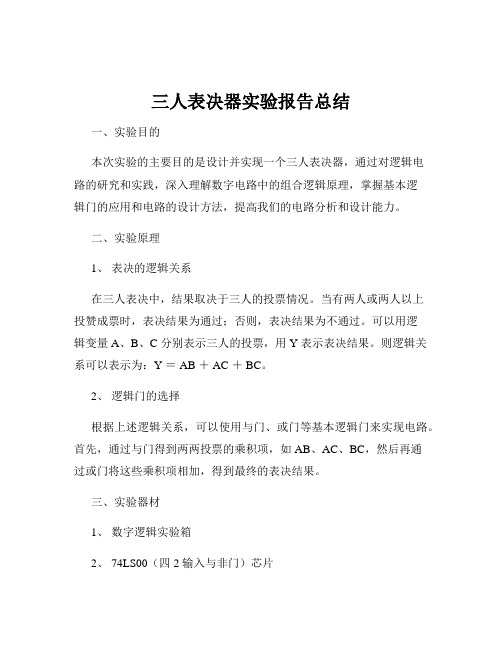

三人表决器实验报告总结

三人表决器实验报告总结一、实验目的本次实验的主要目的是设计并实现一个三人表决器,通过对逻辑电路的研究和实践,深入理解数字电路中的组合逻辑原理,掌握基本逻辑门的应用和电路的设计方法,提高我们的电路分析和设计能力。

二、实验原理1、表决的逻辑关系在三人表决中,结果取决于三人的投票情况。

当有两人或两人以上投赞成票时,表决结果为通过;否则,表决结果为不通过。

可以用逻辑变量 A、B、C 分别表示三人的投票,用 Y 表示表决结果。

则逻辑关系可以表示为:Y = AB + AC + BC。

2、逻辑门的选择根据上述逻辑关系,可以使用与门、或门等基本逻辑门来实现电路。

首先,通过与门得到两两投票的乘积项,如 AB、AC、BC,然后再通过或门将这些乘积项相加,得到最终的表决结果。

三、实验器材1、数字逻辑实验箱2、 74LS00(四 2 输入与非门)芯片3、 74LS32(四 2 输入或门)芯片4、导线若干四、实验步骤1、设计电路根据逻辑关系,在纸上画出电路原理图。

确定所需的逻辑门数量和连接方式。

2、芯片选择与引脚连接在实验箱上选择合适的芯片,并按照芯片引脚图将芯片正确插入插座。

使用导线将芯片的引脚按照电路原理图进行连接。

3、电路测试连接完成后,给 A、B、C 输入不同的逻辑电平(0 或 1),观察输出 Y 的电平变化,记录测试结果。

4、故障排查如果输出结果与预期不符,需要仔细检查电路连接是否正确,芯片是否损坏,输入电平是否稳定等,逐步排查故障。

五、实验数据及结果分析1、实验数据记录输入情况:A=0,B=0,C=0,输出 Y=0输入情况:A=0,B=0,C=1,输出 Y=0输入情况:A=0,B=1,C=0,输出 Y=0输入情况:A=0,B=1,C=1,输出 Y=1输入情况:A=1,B=0,C=0,输出 Y=0输入情况:A=1,B=0,C=1,输出 Y=1输入情况:A=1,B=1,C=0,输出 Y=1输入情况:A=1,B=1,C=1,输出 Y=12、结果分析从实验数据可以看出,当有两人或两人以上投赞成票时,输出 Y 为1,表决结果为通过;否则,输出 Y 为 0,表决结果为不通过。

三人表决器c语言实验报告,项目一:三人表决器的逻辑电路设计与制作

三⼈表决器c语⾔实验报告,项⽬⼀:三⼈表决器的逻辑电路设

计与制作

三⼈表决器的逻辑电路设计与制作

⼀:设计要求

1.对电路图的原理进⾏分析 ,并对原理图进⾏改良。

⽤仿真软件进⾏仿真调试,弄清楚电路的⼯作原理。

2.熟悉各元件的性能和设置元件的参数。

3.对原件的性能进⾏评估和替换,⽤性能和使⽤范围更好,更常⽤的原件进⾏替换,使⾃⼰实际是原件更接近实际使⽤。

4.原件安装符合⼯艺要求,既考虑其性能⼜应美观整齐。

焊接原件要注意焊点的圆润。

5.学会数字逻辑电路的设计⽅法。

6.培养⾃⼰的分析故障和解决问题的能⼒。

⼆:原件清单

电阻、芯⽚、按钮、发光⼆级管、电源 2. 原件的检测

(1)电阻的检测:先⽤⾊环法对电阻进⾏读书,然后再⽤万⽤表打到相应的电阻档对电阻进⾏⼀步的检测。

(2)发光⼆极管的检测:将万⽤表打⾄欧姆档*10K,万⽤表的表笔对发光⼆极管进⾏反接,如果发光⼆级管会发光,那么说明该发光⼆级管是好的。

(3)按钮的检测:将万⽤表打⾄欧姆档*1K,⽤万⽤表的表笔接在按钮的两端,如果万⽤表打到⽆穷⼤,按下按钮万⽤表的指针达到零,那么说明该按钮接通了,也是好的;反之是坏的。

三:三⼈表决器的逻辑电路的设计 (1)完成真值表

Y=A’BC+AB’C+ABC’+ABC (3)卡诺图

BC A 0 1

⽤代数法和卡诺图法化简:。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

三人表决器实验我们实验采取3种输入方式:原理图方式,VHDL方式,VerilogHDL.你可以只看一种.下面我分别一一介绍三人表决器的功能描述三个人分别用手指拨动开关SW1、SW2、SW3来表示自己的意愿,如果对某决议同意,各人就把自己的指拨开关拨到高电平(上方),不同意就把自己的指拨开关拨到低电平(下方)。

表决结果用LED(高电平亮)显示,如果决议通过那么实验板上L2(黄灯)亮;如果不通过那么实验板上L1(红灯)亮;如果对某个决议有任意二到三人同意,那么此决议通过,L2亮;如果对某个决议只有一个人或没人同意,那么此决议不通过,L1亮。

采用原理图设计三人表决器我们根据三人表决器的直值表,可以通过卡诺图化简可以得到:L2=SW1SW2+SW1SW3+SW2SW3L1=_L2那么我们可以在MAX+plusII中用原理图实现上面的三人表决器~下面仅把和VHDL不同的详细写下,相同或基本相同的就一带而过:(1)打开MAX+plusII(2)新建一个图形文件:File菜单>new新建文件时选择Graphic Editor file点OK(3)输入设计文件我们现在在图形文件中输入电路,我们这个电路需要AND2、OR3、NOT三个逻辑门电路和输入输出端,你可以Symbol ->Enter Symbol(或者双击空白处)弹出窗口:%在Symbol Name中输入and2,点OK同样可以加入or3、input、output、not对input、output,鼠标左键双击PIN_NAME,那么PIN_NAME被选中,并且变黑,然后输入你要改的名字,如SW1把元件拖动到合适位置,将光标放到元件的引线出,可以发现光标变为十字星,此时摁住左键就可以进行连线。

最后的电路图如下图(4)保存文件:保存为,Automatic Extension选.gdf"把文件设为当前工程:FILE->PROJECT->SET PROJECT TO CURRENT FILEMAX+PLUS II的标题条将显示新的项目名字至此,程序输入就已经完成了(5)检查编译指定下载的芯片型号指定芯片的管脚(参见10分钟学会PLD设计2 -设计的编译)此时的图形为:—下图为SW1放大的图,其中majority_voter@41中前部分为设计的文件名,后面41为EPM7128SLC84-15的41脚,也就是说电路图中SW1被指定到EPM7128SLC84-15的41脚(而实验板上41脚被连接到指拨开关SW1上了,这样电路图上SW1就和实验板上的硬件SW1实现了连接)。

采用VHDL设计三人表决器打开MAX+plusII,在开始菜单内选择MAX+PLUS II 项,开始运行MAX+PLUS II(如下图)你最好把图标放到桌面上,以后直接双击MAX+PLUS II图标就可以运行软件了在MAX+PLUSII上点右键,选择发送到->桌面快捷方式(如下图),那么你桌面上就看到MAX+PLUS II 了。

新建VHDL文档!(图形和verilog-HDL设计的过程见后面的部分)FILE->NEW或者点下图的新建图标:连后选择Text Editor File文件,点OK如下图输入设计文件在文本窗口中输入以下VHDL源程序:LIBRARY IEEE;USE--********************************************* ENTITY majority_voter ISPORT(SW : IN std_logic_vector(3 DOWNTO 1);L : OUT std_logic_vector(2 DOWNTO 1));--L2 is a yellow LED AND L1 is a RED LED END majority_voter;--********************************************* ARCHITECTURE concurrent OF majority_voter IS BEGINWITH SW SELECTL <= "10" WHEN "011","10" WHEN "101","10" WHEN "110","10" WHEN "111","01" WHEN OTHERS;END concurrent;--*********************************************如下图&保存文件FILE->SAVE,或点工具栏上的存盘符号存盘符号把文件保存为(路径中不要有中文字符,Automatic Extension选.vhd)把文件设为当前工程:FILE->PROJECT->SET PROJECT TO CURRENT FILE%MAX+PLUS II的标题条将显示新的项目名字至此,程序输入就已经完成了采用VerilogHDL设计三人表决器下面仅把和VHDL不同的详细写下,相同或基本相同的就一带而过:(1)打开MAX+plusII(2)新建新建一个verilog-HDL文件(Text Editor File类型)(3)输入设计文件/其中SW12,SW13,SW23为中间变量module majority_voter(SW1,SW2,SW3,L1,L2);output L1,L2;input SW1,SW2,SW3;and(SW12,SW1,SW2);and(SW13,SW1,SW3);and(SW23,SW2,SW3);or(L2,SW12,SW13,SW23);并把文件设为当前工程(同前)2 编译和布线我们先要指定所用芯片的型号,菜单:Assign->Device如下图:将弹出一窗口(注意把show only fastest speed grades前的钩去掉,否则看不到EPM7128SLC84-15)在Debice Family 中选择MAX7000SDEVICE选择EPM7128SLC84-15再指定芯片的管脚(也就是把你设计的IO口如L1,L2指定到芯片对应的管脚上如10,9)Assign->Pin/Location/Chip(也可以在空白处点右键,选Assign->Pin/Location/Chip)将弹出下图窗口:、在Node Name 中添入SW3Chip Resource 下的Pin中输入管脚41在Pin type中输入input点ADD连后同样指定以下管脚:Node name pin Pin typeSW244!inputSW145inputL110outputL29output<在加完L2后点OK(编译后可以看到IO在芯片上的分布:MAX+plusII-> Froorplan Editor,具体见在编译后面的讲解)编译文件File->Project->save&Compile此时可能弹出下图WARNING窗口,提示“project has user pin or logic cell assignments, but never b een compiled before. For best fitting results, let the compiler choose the first set of assignments inste ad”,这是因为在管脚指定之前没有compile,你只要再点save & compile就可以了MAX+PLUS II 编译器将检查项目是否有错,并对项目进行逻辑综合,然后对设计进行布局布线,放到一个Altera 器件中,同时将产生报告文件、编程文件和用于时间仿真用的输出文件:逻辑综合:就是把HDL语言或原理图翻译成最基本的与或非门的连接关系布局布线:把这种与或非门的连接关系用芯片的内部的可编程结构和连线来实现如果设计正确,将下图所示,点确认编译后可以看到IO在芯片上的分布:MAX+plusII-> Froorplan Editor将弹出一窗口如下图双击空白处,可以看到下图所示IO在芯片EPM7128SLC84上的布局~创建一个设计的符号(此和本设计无关,仅供其他设计在高层调用)在File菜单中选择Create Default Symbol 项,即可创建一个设计的符号。

该符号可被高层设计调用。

此时会产生一个COMPILE窗口,直接点Start,完成后点确认3 波形仿真此过程主要是用软件来仿真你的设计,看看结果是否符合你的设计要求(编译好以后,打开波形编辑器,MAX+PLUSII->Waveform Editor载入端口,Node->Enter Nodes from SNF将弹出下面窗口,你按下面步骤操作:点List,将出现端口列表,你默认是选择全部,你也可以通过左键和Ctrl组合来选择你想要的信号。

点=>将你的信号加入SNF文件中点OK%为了方便观察,我们把信号展开如果需要再次合并可以按住SHIFT键,用鼠标左键选上要合并的信号,再点右键->Enter Group下面我们将对信号进行赋值,首先选中一个要赋值的信号区间,如SW3的10us到20us范围,按住鼠标左键,在SW3的10us到20us的范围只能够那拉出一个黑色区域,松开鼠标左键,再点左边工具栏上的“1”,使这个时间段,SW3就被赋值为高电平,如下图:(注意时间不要选择太小,比如就选10ns,这样结果可能不对,因为电路的延迟可能就达到10ns)你将其他信号按你希望的加上激励在上面过程中,你可能要遇到下面设置::Snap to Grid:鼠标按网格选取,用鼠标左键可以决定是否选取Show Grid:显示网格Gride Size:设置网格大小(这个非常有用,在你一些设计中经常要改变网格大小,便于你选择)End Time:设置仿真结束时间(这个在设计中也经常用到,否则默认的仿真时间只有1us)下面是加激励后的波形(end time =200us,gride size=10us)点FILE->PROJECT->save&simulate这时会弹出保存窗口,我们保存为点OK,将会防真,如果正确会弹出窗口(图)点确认,再点open SCF,将出现防真后的波形波形图显示的逻辑功能和设计目的完全一样,下面我们将把程序在线下载到芯片EPM7128SLC84-15中。