TDR和SET2DIL测试教程

TDR测试原理及测试方法

TDR测试原理及测试方法TDR(Time Domain Reflectometry)是一种利用时间域反射原理进行测量和分析的技术。

它可以用于测试电缆、光纤、导线和其他传输线的长度和故障位置的测量和定位。

本文将介绍TDR的测试原理和常用的测试方法。

TDR的测试原理:TDR利用脉冲信号在传输线上传播后反射回来的方式来测量和分析传输线的特性。

当测试脉冲信号被发送到传输线上时,如果传输线中存在任何异常,如开路、短路、电容、电感、故障等,脉冲信号会由于信号的传播速度不一致产生反射。

TDR测量的基本思想是测量传输线上脉冲信号的传播时间和反射幅度,并通过分析脉冲信号的时间和幅度变化来判断传输线的长度、故障位置以及故障类型。

当脉冲信号从传输线的开路端口发出后,如果传输线上存在短路或开路故障,反射信号会立即返回。

通过测量脉冲信号从发射端到反射端的时间差,可以计算出传输线的长度。

同时,通过分析反射信号的幅度变化,可以判断传输线上的故障类型,如短路、开路、电容或电感。

TDR的测试方法:1.单点TDR测试法:单点TDR测试法是最常用的TDR测试方法之一、它适用于测试传输线的长度和故障位置。

测试时,只需将TDR测试装置的正负端口分别连接到传输线的两端,在TDR测试装置上设置合适的测试参数,发送脉冲信号,然后测量反射信号的时间和幅度。

2.双点TDR测试法:双点TDR测试法是一种高精度的测试方法,适用于测量非常短的传输线长度和高精度的故障定位。

它通过在传输线上加入反射比较点来实现。

测试时,将TDR测试装置的一个端口连接到传输线的起点,另一个端口连接到传输线的终点,并在传输线上插入一个移动导频器。

测试过程中,移动导频器的位置会不断改变,然后根据测量到的反射信号的时间和幅度来计算出传输线的长度和故障位置。

3.耦合TDR测试法:耦合TDR测试法是一种常用的用于测试电缆中间接头的方法。

测试时,将TDR的正端口连接到一个中间接头,负端口连接到电缆的起点或终点,然后发送脉冲信号进行测量。

TDR测试原理

TDR测试原理评价频率响应的最普通的方法是在频域中解Ma某well方程。

这个过程能够把系统所有的物理和电气特性都考虑进去,包括传输线。

因而已经有很多基于此原理的测量方法来帮助电气工程师分析信号完整性。

当和其他测试方法比较时,时域反射(TDR:TimeDomainReflector)可以提供更加直观观察DUT的特性。

TDR使用阶跃信号发生仪和示波器,在被测得传输线上发送一个快速的上升沿,再特定的点上用示波器观察反射电压波形。

这种技术可以测出传输显得特性阻抗,并显示出每个阻抗不连续点的位置和特性(阻抗、感抗和容抗)。

所有这些信息都是示波器上实时显示。

相对于其他技术,TDR能够给出更多的关于系统宽带相应的信息。

图1时域反射计工作原理阶跃信号发生器向被测系统产生一个正向的阶跃信号。

该信号沿着传输线向前传输。

如果负载组抗等于传输线的特性阻抗,将没有信号反射,示波器上能看到的只有发送的阶跃信号。

假如负载存在失配,将有部分的输入信号被反射,示波器上将出现反射信号和输入信号的叠加。

图2是一个传输线的测试波形,由此可以看出,对于非连续的阻抗,示波器对应位置将出现变化的波形,由此我们就能够分析每个中断点的特性。

图2时域反射计测试结果·A:50Ohm电缆·B:微波传输带开始·C:50Ohm微波传输带·D:75Ohm微波传输带·E:50Ohm微波传输带·F:开路与其他测试方法的比较最常用的测量传输线和负载的方法是向系统发送一个正弦波,并观察线上不连续点的波形。

这种测试方法中,我们要计算SWR(驻波比)并将它看作系统的参数。

当系统有数个阻抗不连续点时,SWR测试往往不能分开这些点。

另外,当系统拥有很宽的带宽时,必须测量很多频点的SWR,测试很枯燥并且耗费时间。

另一个常见的测量传输线的仪器是矢量网络分析仪(VNA)。

这时,信号源产生一个连续扫频的正弦波来激励DUT。

EC网分仪关于TDR与阻抗测试得使用说明

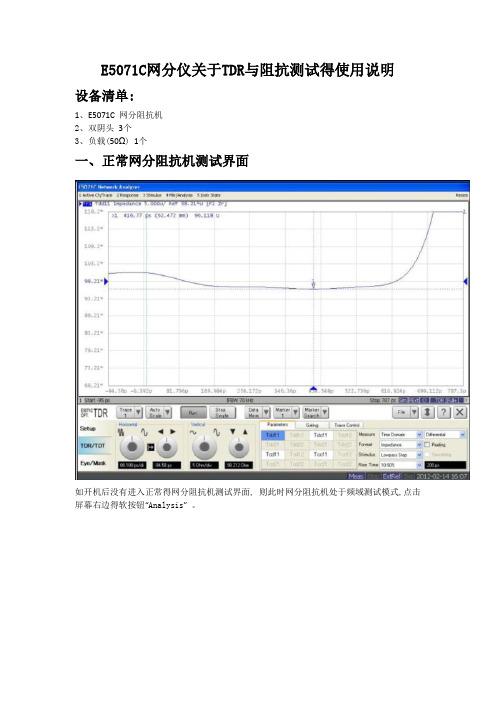

E5071C网分仪关于TDR与阻抗测试得使用说明设备清单:1、E5071C 网分阻抗机2、双阴头3个3、负载(50Ω) 1个一、正常网分阻抗机测试界面如开机后没有进入正常得网分阻抗机测试界面, 则此时网分阻抗机处于频域测试模式,点击屏幕右边得软按钮“Analysis”。

在“Analysis”菜单中,将“TDR“功能打开-On将提示就是否重启以改变改变网分阻抗机得状态,选择“Yes”随后将进入正常得阻抗测试界面/设置向导界面随后将进入正常得阻抗测试界面/设置向导界面双击红色窗口区域,则可进入TDR主测试界面进行测试二、测试/调整曲线进入TDR主测试界面后,阻抗曲线如图所示,我们按住鼠标左键拖拉图示画出方框,有“Zoom”菜单显示,点击该Zoom菜单。

点击Zoom按钮后可以瞧到阻抗曲线如下图:点击Zoom按钮后可以瞧到放大后得阻抗曲线 :可以点击“TDR/TDT”进入波形得调整点击圆形按钮上得左右三角形进行校准面得左右移动点击圆形按钮上得上下三角形进行阻抗曲线得上下移动点击圆形按钮上得缩放图标进行阻抗曲线得水平方向(Horizontal)得缩小放大 (可以将阻抗曲线调整,使其合适显示窗口)点击圆形按钮上得缩放图标进行阻抗曲线得垂直方向(Vertical )得缩小/放大(可以将阻抗曲线更平滑/崎岖地显示,但并不改变真实得阻抗值)三、显示测试结果1、显示平均值2、显示最大/最小值3、显示每点阻抗值4、显示平均值先点击Setup ,再点击Basic Mode按钮先点击Setup ,再点击Basic Mode按钮弹出对话框,选Yes此时便可以方便地使用右侧得热键(这时与平时使用方法相同)如上图左上角所示:Marker1 为最大值Max 51、970Ω(具体位置在窗口最右边),Marker 2为最小值Min 47、368Ω(具体位置在窗口中心偏右),也就是故障点所在位置。

Marker1与Marker2为连接器阻抗值,可以明显地瞧出该连接器阻抗就是偏高还就是偏低(此图为偏高)。

TDR测试原理范文

TDR测试原理范文TDR测试是一种用来测量电缆或其他导线的长度、故障位置和故障类型的常用方法。

TDR(Time Domain Reflectometry,时域反射测量)是通过发送一个脉冲信号来测量电缆上的反射信号,并根据反射信号的时间和幅度差异来获得有关电缆状态的信息。

下面将详细阐述TDR测试的原理。

1.原理概述:TDR测量原理基于时延故障诊断技术,它使用时域反射信号来确定电缆上的故障位置。

TDR测试仪器发射一个短脉冲信号至被测导线中,从而产生一个脉冲信号,脉冲信号在导线中沿着两个方向传播。

当脉冲信号遇到电缆末端或者故障点时会发生反射,这些反射信号通过接收系统捕获,并利用它们的时间和幅度差异来确定导线上的故障位置。

2.测量距离:3.故障位置:当脉冲信号遇到导线的末端或者导线上的故障时,会发生反射。

通过接收这些反射信号的时间和幅度差异,可以确定导线上故障位置。

当脉冲信号到达故障点时,将会发生一个反射信号,此时仪器会记录下反射信号的来回时间,并根据信号的传播速度计算出故障点与测试点之间的距离。

4.故障类型:除了测量长度和位置,TDR还可以帮助确定故障的类型。

根据故障类型,反射信号的幅度和形状会发生变化。

导线上的常见故障类型包括短路、断路、电缆接头不良、阻抗不匹配等。

通过观察反射信号的形状和幅度变化,可以推测出导线上的故障类型。

5.TDR测试实施:-设置TDR测试仪器的参数,如测试范围、脉冲宽度、采样率等。

-连接TDR测试仪器和被测导线,并确保连接正确、稳定。

-发送脉冲信号至被测导线中,并接收反射信号。

-观察反射信号的形状和幅度,分析故障位置和故障类型。

6.注意事项:在进行TDR测试时,需要注意以下几点:-测试仪器的参数设置应根据被测导线的特性进行调整,以获得准确的测量结果。

-测试仪器和被测导线之间的连接应牢固可靠,避免接触不良或者断开。

-在分析反射信号时,需要考虑信号的衰减和干扰,以准确判断故障位置和类型。

TDR和SET2DIL测试教程

TDR和SET2DIL测试教程TDR(Time Domain Reflectometry)和SET2DIL(Stuck-at Fault Equivalent Threshold to determine Indefinite Literal)是两种常用的测试方法,用于检测数字电路中潜在的故障。

本教程将介绍这两种测试方法的原理和操作步骤。

一、TDR测试原理及操作步骤1.原理:TDR测试利用反射信号来检测数字电路中的故障,通过发送短脉冲信号并测量反射信号的时间来确定信号在电路中扩散的速度和故障点的位置。

2.操作步骤:(1)连接TDR测试仪和数字电路,确保连接正确并稳定。

(2)设置TDR测试仪的参数,包括发送脉冲宽度、采样率等。

(3)发送脉冲信号并记录反射信号的时间和幅度信息。

(4)分析反射信号的图像,确定可能的故障点。

(5)修复或替换故障点,并重新进行TDR测试,直到所有故障点被排除。

二、SET2DIL测试原理及操作步骤1.原理:SET2DIL测试是一种基于故障模拟器的测试方法,通过将潜在的故障点模拟为“卡住”或“漂移”的故障状态,并测量相应的逻辑值来确定故障点的位置。

2.操作步骤:(1)连接SET2DIL测试设备和数字电路,确保连接正确并稳定。

(2)设置故障模拟器的参数,包括故障类型、阈值等。

(3)对数字电路进行SET2DIL测试,并记录测试结果。

(4)根据测试结果确定故障点的位置,并修复或替换故障点。

(5)反复进行SET2DIL测试,直到所有故障点被排除。

总结:TDR和SET2DIL是两种常用的数字电路测试方法,能够有效地检测和排除潜在的故障点。

通过本教程的介绍,希望能够帮助使用者更好地理解这两种测试方法的原理和操作步骤,从而提高数字电路的可靠性和稳定性。

TDR_测试原理及测试方法

TDR_测试原理及测试方法TDR(Time-Domain Reflectometer)是一种测试电缆或导线中断、短路、开路等故障的仪器。

它通过测量电缆上的回波信号的变化,以确定故障位置和类型。

TDR是基于脉冲与反射原理进行测试的。

以下是TDR测试原理及测试方法的详细解释。

1.测试原理:TDR测试原理基于脉冲与反射原理。

当脉冲信号传输到电缆或导线上时,会遇到不同介质的边界,如连接器、开路、短路或故障点。

当信号遇到这些边界时,会产生反射,并返回到TDR上。

通过测量这些反射信号的时间和强度,可以确定故障位置和类型。

2.测试方法:(1)连接电缆:首先,需要将被测试的电缆正确连接到TDR的输入通道上。

确保连接稳定,以免产生测试误差。

(2)设置参数:根据被测试电缆的特性和需求,设置合适的测试参数。

包括脉冲宽度、采样率、测试范围等参数。

(3)发射脉冲:通过操作TDR,发射一个脉冲信号到电缆上。

脉冲信号会沿着电缆传输,并在遇到边界时产生反射。

(4)接收信号:TDR接收到电缆上的反射信号,并将其显示在屏幕上。

反射信号的强度和时间信息可以用于确定故障类型和位置。

(5)分析结果:根据屏幕上显示的反射信号,可以定性地判断故障类型。

例如,反射信号的幅度变化大且在一点上出现尖峰,可能表示存在短路故障;反射信号的幅度变化小且持续较长,可能表示存在开路故障。

(6)确认故障位置:通过测量反射信号的时间信息,可以确定故障的距离。

使用TDR的标尺或测量工具,可以准确地测量出故障点距离电缆起点的距离。

3.测试误差及解决方法:(1)信号衰减:长距离的电缆会导致信号衰减,影响反射信号的强度和准确性。

为了解决这个问题,可以使用信号放大器或延长电缆长度。

(2)多重反射:信号反射可能会在电缆上多次发生,导致多个反射信号叠加在一起。

这会使得故障点的准确判断变得困难。

一种解决方法是减少脉冲宽度,以增加反射信号之间的时间间隔。

(3)连接不良:如果测试中的电缆连接不良,会导致测试结果不准确。

tdr使用方法

tdr使用方法TDR使用方法一、TDR简介TDR(Time Domain Reflectometry)是一种常用的电缆故障检测和定位技术,其原理是通过测量电缆中脉冲信号的反射波形,来判断电缆中的故障位置。

TDR广泛应用于电力、通信、铁路等领域,对于保障设备正常运行和及时修复故障具有重要意义。

二、TDR使用步骤1. 准备工作在使用TDR之前,需要进行一些准备工作。

首先,检查TDR设备的状态,确保其正常工作。

其次,选择合适的测试电缆,并清理电缆两端的接头和连接器,保证连接的牢固和良好的信号传输。

2. 连接电缆将TDR设备与待测试的电缆连接。

通常情况下,TDR设备会提供多种接口,可以根据电缆类型选择合适的接口。

确保连接牢固,并避免弯曲或扭曲电缆,以免影响测量结果。

3. 设置参数根据实际情况,设置TDR设备的参数。

主要包括脉冲宽度、采样速率、测试范围等。

一般情况下,脉冲宽度越短,测试的精度越高,但对于较长的电缆,可能需要增加脉冲宽度以获得足够的信号反射。

4. 进行测量开始进行TDR测量。

启动TDR设备,发送脉冲信号到待测试的电缆中。

TDR设备会记录电缆中的信号反射,并绘制出反射波形图。

根据反射波形图,可以判断出电缆中的故障位置。

5. 分析结果根据TDR设备绘制的反射波形图,分析电缆中的故障情况。

常见的故障包括开路、短路、接地、电缆断裂等。

根据波形图上的特征,可以判断出故障的位置和性质。

6. 故障定位根据分析结果,确定故障的具体位置。

可以通过测量电缆两端的距离、计算信号传播速度等方法,来精确定位故障位置。

对于较长的电缆,可能需要多次测量以缩小故障范围。

7. 故障修复根据故障的性质和位置,采取相应的修复措施。

对于开路或断裂的情况,需要找到故障点并修复;对于短路或接地的情况,需要排除故障并进行绝缘处理。

修复后,可以重新进行TDR测量,以确认故障是否已经解决。

三、TDR使用注意事项1. 在进行TDR测量前,确保电缆处于断电状态,以免对设备和人员造成伤害。

TDR和SET2DIL测试教程

T 0.46 0.41 0.43

普通树脂和低损耗树脂对SI的影响

Page39

3

玻纤

PCB制造与信号完整性

低损耗Fabric Standard E Glass Dk 6.6 NE glass (Dk 4.6)

Page40

3

PCB制造与信号完整性

material glass style Advantage modified material standard glass 1080 RC65% 2116 RC55% 2113 RC57% spread glass 1086 RC61% 1067 RC70% 1086 RC64% low Dk glass 1080 RC65% 106 RC73% 1080 RC68%

介质损耗因子与频率的相关性

Page13

1

信号完整性基础

1.6 插入损耗的概念 插入损耗(简称插损,数学描述为S21,或insertion loss):在二端口网 络中,S21定义为从端口2出来的正弦波和从端口1进入的正弦波的比值。

入射信号

端口一

端口二

反射信号 接收信号 相位差 幅度 简单二端口网络示意图

IEEE 1394(B) 接口 (3.2Gbps)

光模块产品 (6.25Gbps)

高性能光模块 (25Gbps)

一些高速电子产品和设备及其传输速率

Page6

1

信号完整性基础

1.3 反射 信号传输时,每时每刻都会感受到一个瞬态阻抗,当这个阻抗不连续时就会 将信号的一部分反射回信号源端;

Rs1

Rs2

Rs1≠Rs2

Page14

1

信号完整性基础

导线发热

1.6 插入损耗的概念

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

0.42

0.48

0.50

0.46

0.35

0.36

0.37

0.41

0.38

0.41

0.40

0.43

普通树脂和低损耗树脂对SI的影响

Page39

3 PCB制造与信号完整性

玻纤

Standard E Glass

Dk 6.6

低损耗Fabric NE glass (Dk 4.6)

Page40

3 PCB制造与信号完整性

选材,设计PCB工程文件 制作样品 VNA测试S参数 提取Dk/Df 通过仿真验证Dk/Df

Dk/Df提取基本流程

2 信号完整性测量技术

2.4 Dk/Df提取

TRL校准模 块

DkDf提取模 块

P片类型 1 P片类型 2

P片类型 3

P片类型 4

2 信号完整性测量技术

2.4 Dk/Df提取

软件操作界面

1.1 信号完整性 信号完整性(Signal Integrity, SI)包含由于信号传输速率加快而产生的互连、电

源、器件等引起的所有信号质量及延时等问题。

Page4

1 信号完整性基础

1.2 高速信号和传输线

对于高速产品,并没有明确定义,一般认为对损耗有特定要求的产品为高速产品 。

传输线模型

时钟频率超过100MHz、数字信 号上升时间小于1ns时,长度超 过1inch(2.54cm)的互连线表 现出传输线特性; 其特征为:线路向周围环境辐射 能量,介质中的粒子(图中圆圈 表示)也会振动吸收能量,产生 时延和衰减等。

2.2 VNA测试

测试原理:

VNA(Vector Network Analyzer, 矢量网络分析仪)的信号源在测试时产生一个 连续扫频的正弦波,以此激励被测物(DUT,device under test),之后测量DUT 的反射信号和传输信号。 VNA把被测物(无论是一条线、一个面或信号网络)当做二端口网络,由于其激 励信号是扫频信号,在每一个频点均可得到被测端口的频率响应,VNA通过分析 这些激励信号和响应信号,计算出被测端口S参数,再通过这些参数得到我们需要 的量化参数值。

2 信号完整性测量技术

2.1 阻抗测试

阻抗测试主要应用TDR(Time Domain Reflector,时域反射计)的方法, TDR 使用阶跃信号发生仪和示波器,在被测得传输线上发送一个快速的上 升沿,再特定的点上用示波器观察反射电压波形。 这种技术可以测出传输显得特性阻抗,并显示出每个阻抗不连续点的位置 和特性(阻抗、感抗和容抗)。

2 信号完整性测量技术

2.3 SET2DIL测试 Single End Trace To drive DIfferential Loss,利用单端线路测量差分损耗的方法。 目的:简化测量,从而使传统的差分四端口测试变为简单的单端测试,并将此测 试方法用于批量板的监控。

传统差分测试需要四 个端口同时测量

THRU

T21 T41

按INTEL算法所推导出的差分信号线时域参数测量方法

Page29

2 信号完整性测量技术

2.3 SET2DIL测试 测试精度评价:与VNA相比还存在一定差距。

随着频率升高, 精度不断下降。

12GHz

Page30

2 信号完整性测量技术

2.3 SET2DIL测试

2 信号完整性测量技术

Page14

1 信号完整性基础

1.6 插入损耗的概念

能量向环境 中发射

辐射

导线发热

导体热 消耗

反射

阻抗不连续

与邻近传输 线干扰作用

插入损耗

耦合、 串扰

增加导体阻 抗消耗能量

趋肤效 应

介质损 耗

介质中粒子 振动导致

Page15

1 信号完整性基础

1.6 插入损耗的概念 无损传输线是不存在的,通路上的每一个节点都会造成损耗,损耗受控

1.4 阻抗 趋肤深度:

δ:趋肤深度 μ: 磁导率 σ:电导率 f: 频率

对于纯铜导线:

μ=4πⅹ10-7 H/m σ=5.8 ⅹ107 S/m

则在1GHz频率下:

δ 铜=2.1um

即信号的传导仅仅在铜线的表面进行。

Page9

1 信号完整性基础

1.4 阻抗 均匀导体直流电阻计算公式: 均匀导体高频阻抗计算公式:

TRL校准件设计工具

Page25

2 信号完整性测量技术

2.2 VNA测试 TRL校准理念在于,将线路的两段各取一部分作为中间剩余部分线路测量的探针。

表示将被校准掉的线路

校准完成后其延时和损耗均为0

表示被当做探针的长度

用于校准不同频率范围

用于校准直流

注意各图形长 度对应关系

被测线路

TRL校准图形

Page26

INTEL的算法可以通过测量时域的信号响应参数,再通过傅里叶变换转化成频域 数值,最终得到插损测量值。从而相当于:

TDD21=41

于是,按此等式,只需测试T21和T41即可计算出SDD21,即插入损耗值。

Page28

2 信号完整性测量技术

2.3 SET2DIL测试 理论上,损耗属于频域范畴,具有很强的频率相关性。此处涉及两个重要概念:

ρ:电阻率 l: 导体长度 S: 导体横截面积

R(AC):高频下的交流阻抗 f: 工作频率 f0:产生明显趋肤效应的临界频率 R:该临界频率下的阻抗

交流电阻随频率变化关系

Page10

1 信号完整性基础

1.4 阻抗:过孔阻抗

寄生电容:

C 1.41 rTD1

D2 D1

寄生电感:

L

5.08hln

2.4 Dk/Df提取

方式 设备和软件 测试coupon 验证

VNA测试PCB两段长度差为10inch的信号线的S参数,利用 ADS仿真软件分析提取其中的DkDf信息 E5071C网分仪、ADS DkDf提取模块

设计不同胶含量、玻纤类型等结构,差分/单端带状线

用仿真提取的DkDf建模,对比阻抗和损耗的测试和仿真结果

如下图所示,沿着时间轴的每一点都对应着被测线上的不同位置阻抗 值。

线宽变化导致阻抗变化 的TDR测试曲线

Page20

2 信号完整性测量技术

2.1 阻抗测试 PCB阻抗测试时选择合适的阻抗线长度是十分必要的,根据经验,在

阻抗线长度超过6inch,且线路损耗较大时,阻抗线后端的阻抗值将有明显 上升趋势。

4h d

1

D1: 焊盘直径 D2: 反焊盘直径 H: 过孔长度 d: 过孔孔径

Page11

1 信号完整性基础

1.5 介电常数(Dk)和损耗因子(Df)

介电常数(Dk)准确讲应该称为相对介电常数。 干燥空气的实际介电常数ε0,数值为8.85pF/m,为方便起见,把这个值设为 1pF/m,从而得到其他介质的相对介电常数值(Relative Permittivity),即我 们现在常用的介电常数(dielectric constant)。

介质损耗因子与频率的相关性

Page13

1 信号完整性基础

1.6 插入损耗的概念

插入损耗(简称插损,数学描述为S21,或insertion loss):在二端口网 络中,S21定义为从端口2出来的正弦波和从端口1进入的正弦波的比值。

入射信号

端口一

端口二

反射信号

相位差 幅度

简单二端口网络示意图

接收信号

目录

3、PCB制造与信号完整性

2.1 材料 2.2 工艺 2.3 PCB设计

Page35

3 PCB制造与信号完整性

随着信号频率的增加,PCB基材介质和导线都会吸收能量,造成信号完整性问题。 除此之外,PCB加工过程中对材料的处理也会引入信号完整性问题。

Stub length

Page36

3 PCB制造与信号完整性

是一个真正的挑战。

右图为传输线中主要 插入损耗来源于传输 的信号频率之间关系 示意图

Page16

1 信号完整性基础

1.6 插入损耗的概念

损耗和传输线长度的关系

Page17

目录

2、信号完整性测量技术

2.1 阻抗测试 2.2 VNA测试 2.3 SET2DIL测试 2.4 Dk/Df测试

Page18

Vt It

Rs2

Page7

1 信号完整性基础

1.4 阻抗 低频或直流情况下阻抗基本等于导体的电阻; 高速或高频情况下,主要受趋肤效应影响,信号在导体中传输感受到的阻抗将 远大于导体在直流情况下的电阻。

圆形导体和方形导体的趋肤效应(红色 表示电流密度最大,蓝色表示最小)

Page8

1 信号完整性基础

microstrip

基本传输线种类

stripline

Page5

1 信号完整性基础

1.2 高速信号和传输线 目前几乎所有高速存储器、服务器、路由器以及很多消费电子产品都具有高传输

速率的特性,PCB产业也已迈进高速的方向。

USB2.0 (480Mbps)

交换机 (1Gbps)

基站 (2.3Gbps)

IEEE 1394(B) 接口

3.1 材料 树脂:

树脂体系和loss tangent之间的关系

Page37

3 PCB制造与信号完整性

普通树脂和低损耗树脂对SI的影响

Page38

3 PCB制造与信号完整性

Material MAX MIN AVE

Insertion loss at 4GHz(unit: dB/inch)

I

M

N

T

2.2 VNA测试

TRL校准: VNA的精确测量是基于精确而复杂的校准基础上的。由于电缆、探头、SMA