电子集成块封装详解.

集成电路封装技术

集成电路封装技术一、概述集成电路封装技术是指将芯片封装成实际可用的器件的过程,其重要性不言而喻。

封装技术不仅仅是保护芯片,还可以通过封装形式的不同来满足不同应用领域的需求。

本文将介绍集成电路封装技术的基本概念、发展历程、主要封装类型以及未来发展趋势等内容。

二、发展历程集成电路封装技术随着集成电路行业的发展逐渐成熟。

最早的集成电路封装形式是引脚直插式封装,随着技术的不断进步,出现了芯片级、无尘室级封装技术。

如今,随着3D封装、CSP、SiP等新技术的出现,集成电路封装技术正朝着更加高密度、高性能、多功能的方向发展。

三、主要封装类型1.BGA封装:球栅阵列封装,是一种常见的封装形式,具有焊接可靠性高、散热性好等优点。

2.QFN封装:裸露焊盘封装,具有体积小、重量轻、成本低等优点,适用于尺寸要求严格的应用场合。

3.CSP封装:芯片级封装,在尺寸更小、功耗更低的应用场合有着广泛的应用。

4.3D封装:通过将多个芯片垂直堆叠,实现更高的集成度和性能。

5.SiP封装:系统级封装,将多个不同功能的芯片封装在一起,实现更复杂的功能。

四、未来发展趋势随着物联网、人工智能等领域的兴起,集成电路封装技术也将迎来新的挑战和机遇。

未来,集成电路封装技术将朝着更高密度、更低功耗、更可靠、更环保的方向发展。

同时,新材料、新工艺和新技术的应用将为集成电路封装技术带来更多可能性。

五、结语集成电路封装技术是集成电路产业链中至关重要的一环,其发展水平直接关系到整个集成电路的性能和应用范围。

随着技术的不断进步,集成电路封装技术也在不断演进,为各个领域的技术发展提供了强有力的支撑。

希望本文能够帮助读者更好地了解集成电路封装技术的基本概念和发展趋势,为相关领域的研究和应用提供一定的参考价值。

集成电路的封装方式

集成电路的封装方式随着电子技术的发展,集成电路已经成为现代电子产品中不可或缺的一部分。

而集成电路的封装方式则是保护和连接芯片的重要环节。

本文将介绍几种常见的集成电路封装方式,包括DIP封装、QFP封装、BGA封装以及CSP封装。

DIP封装,即双列直插封装(Dual In-line Package),是最早也是最常见的一种封装方式。

DIP封装的芯片引脚通过两行排列在芯片的两侧,方便插入插座或焊接到电路板上。

DIP封装的优点是成本低廉、易于维修和更换,但其缺点是占用空间较大,限制了芯片的集成度和密度。

QFP封装,即四边形薄封装(Quad Flat Package),是一种较新的封装方式。

QFP封装的芯片引脚通过四边排列在芯片的四周,使得芯片的尺寸更小,适用于高密度集成电路。

QFP封装的优点是体积小、引脚多、传导性能好,但其缺点是焊接难度较大,需要使用SMT设备进行焊接。

BGA封装,即球栅阵列封装(Ball Grid Array),是一种高密度的封装方式。

BGA封装的芯片引脚通过芯片底部的焊球连接到电路板上,使得芯片的引脚数量和密度更高。

BGA封装的优点是高集成度、体积小、传导性能好,但其缺点是焊接难度较大,需要使用专用设备进行焊接。

CSP封装,即芯片级封装(Chip Scale Package),是一种最小尺寸的封装方式。

CSP封装将芯片封装在最小尺寸的封装基板上,使得芯片的尺寸和重量更小。

CSP封装的优点是体积小、重量轻、传导性能好,适用于小型移动设备等场景。

但由于其尺寸小,焊接和维修难度较大。

除了以上几种常见的封装方式外,还有一些特殊的封装方式,如PGA封装(Pin Grid Array)、SOIC封装(Small Outline Integrated Circuit)等。

这些封装方式都有各自的特点和适用场景,可以根据具体的需求选择合适的封装方式。

在选择集成电路的封装方式时,需要考虑多个因素,如芯片的功耗、集成度、散热性能、可靠性和成本等。

电子元器件封装简介及图解

电子元器件封装简介及图解部分元件参考封装元件封装是指在PCB编辑器中,为了将元器件固定、安装于电路板,而绘制的与元器件管脚相对应的焊盘、元件外形等。

由于它的主要作用是将元件固定、焊接在电路板上,因此它对焊盘大小、焊盘间距、焊盘孔大小、焊盘序号等参数有非常严格的要求,元器件的封装、元器件实物、原理图元件管脚序号三者之间必须保持严格的对应关系,如图6.8所示,否则直接关系到制作电路板的成败和质量。

小技巧一般双列直插集成电路元件封装的第一脚焊盘为方形,以便于元件安装和检测,与此对应集成块表面的第一脚位置有小点标志。

由图6.8可知,元件封装一般由二部分组成:焊盘和外形轮廓,其中最关键的组成部分是和元件管脚一一对应的焊盘,它的形状和参数如图6.9所示。

焊盘的作用是将元件管脚固定焊接在电路板的铜箔导线上,因此它的各参数直接关系到焊点的质量和电路板的可靠性,一般包含如下参数:焊盘长度(X-Size)、焊盘宽度(Y-Size)、孔径(Hole Size)、序号(Designator)、形状(Shape)等。

在PCB编辑器中双击焊盘,即可打开焊盘属性对话框,可以修改或设置焊盘各属性。

在元件封装中,除了焊盘本身的参数至关重要外,焊盘之间的距离也必须严格和元件实物管脚之间距离保持一致,否则在进行元件装配、焊接时将可能存在元件无法安装等严重问题,元件封装的合理选择非常重要。

图6.8 元件封装与元件实物、原理图元件的对应关系图6.9 PCB板中的焊盘1元件封装的另一组成部分为外形轮廓,相对于焊盘而言,它的参数要求没有焊盘参数那么严格,一般就是从元件顶部向底部看下去所形成的外部轮廓俯视图,它一般在顶层丝印层(Top Overlayer)绘制,默认颜色为黄色。

外形轮廓主要用于标志元件在电路板上所占面积大小和安装极性,从而便于元件的整体布局,同时还便于元件的安装。

在Protel DXP 安装目录下的“*:\Program Files\Altium\Library\”目录中,存放着大量的PCB元件封装库,在不同的元件封装库中又含有许多不同种类、不同尺寸大小的PCB元件封装,熟练了解Protel DXP 元件封装库的各种封装是正确、快速地为元件选用合适封装的前提,而合适的选择元件封装是成功制作电路板的第一步。

集成电路封装技术封装工艺流程介绍

集成电路封装技术封装工艺流程介绍集成电路封装技术是指将芯片封装在塑料或陶瓷封装体内,以保护芯片不受外界环境的影响,并且方便与外部电路连接的一种技术。

封装工艺流程是集成电路封装技术的核心内容之一,其质量和工艺水平直接影响着集成电路产品的性能和可靠性。

下面将对集成电路封装技术封装工艺流程进行介绍。

1. 芯片测试首先,芯片在封装之前需要进行测试,以确保其性能符合要求。

常见的测试包括电性能测试、温度测试、湿度测试等。

只有通过测试的芯片才能进行封装。

2. 芯片准备在封装之前,需要对芯片进行准备工作,包括将芯片固定在封装底座上,并进行金线连接。

金线连接是将芯片的引脚与封装底座上的引脚连接起来,以实现与外部电路的连接。

3. 封装材料准备封装材料通常为塑料或陶瓷,其选择取决于芯片的性能要求和封装的环境条件。

在封装之前,需要将封装材料进行预处理,以确保其表面光滑、清洁,并且具有良好的粘附性。

4. 封装封装是整个封装工艺流程的核心环节。

在封装过程中,首先将芯片放置在封装底座上,然后将封装材料覆盖在芯片上,并通过加热和压力的方式将封装材料与封装底座紧密结合。

在封装过程中,需要控制封装温度、压力和时间,以确保封装材料与芯片、封装底座之间的结合质量。

5. 封装测试封装完成后,需要对封装产品进行测试,以确保其性能和可靠性符合要求。

常见的封装测试包括外观检查、尺寸测量、焊接质量检查、封装材料密封性测试等。

6. 封装成品通过封装测试合格的产品即为封装成品,可以进行包装、贴标签、入库等后续工作。

封装成品可以直接用于电子产品的生产和应用。

总的来说,集成电路封装技术封装工艺流程是一个复杂的过程,需要精密的设备和严格的工艺控制。

只有通过合理的工艺流程和严格的质量控制,才能生产出性能优良、可靠性高的集成电路产品。

随着科技的不断进步,集成电路封装技术也在不断创新和发展,以满足不断变化的市场需求。

相信随着技术的不断进步,集成电路封装技术将会迎来更加美好的发展前景。

集成电路封装知识简介

封装外观尺寸

TSOP II 54LD内部构造 内部构造

A6 A2 DS A5 A7

A5

Items

Thickness (mm) Nominal 1.000 0.127 Alloy 42 0.279 0.100 0.050 0.210 0.254 0.238

Thickness (mils) 39.37 5 A42 11 4 2 8 10 9.37

Die(Chip)

俯视图

Gold Wire L/F Pad Epoxy Inner Lead Die

正视图

工艺流程(前道工艺) 工艺流程(前道工艺)

打线结合(Wire Bonding)

主要工艺参数: • ball shear test • wire pull test • ball bond size • Ball placement • Pad Cractering Test • Loop Height Test • Reject(see PBI reject criteria) 见下页图示 打线后图片 设备与材料: 1. 打线机 2. 金线 3. 劈刀 主要机器参数: 1. 超声波功率 2. 焊接压力 3. 焊接持续的时间 4. 焊接温度

银胶

框架

胶带

固化 传统银胶粘结工艺

加热 固化 胶带粘结工艺

工艺流程(前道工艺) 工艺流程(前道工艺)

晶片粘结(Die Bonding) 银胶 芯片

框架焊盘

Fillet height BLT

Die Tilt

Y2

芯片

主要工艺参数: 1. BLT 2. Die tilt 3. Fillet height 4. Wetting 5. Die placement 6. Die shear

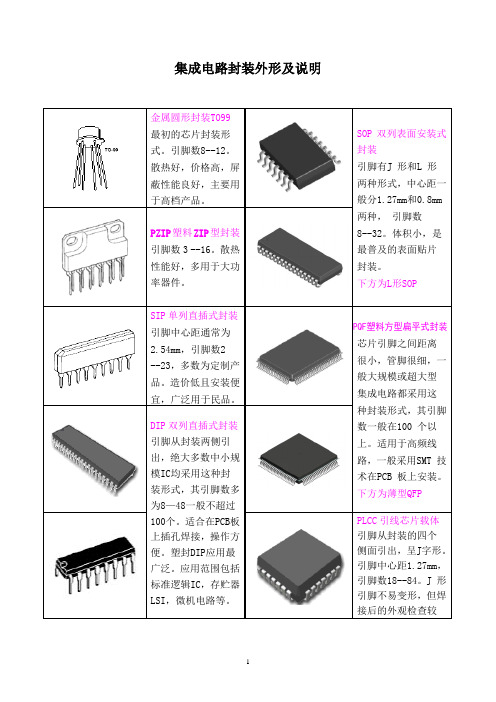

集成电路封装外形及说明

集成电路封装外形及说明

说明:

常见的封装材料有:塑料、陶瓷、玻璃、金属等,现在基本采用塑料封装。

按封装形式分:普通双列直插式,普通单列直插式,小型双列扁平,小型四列扁平,圆形金属,体积较大的厚膜电路等。

按封装体积大小排列分:最大为厚膜电路,其次分别为双列直插式,单列直插式,金属封装、双列扁平、四列扁平为最小。

两引脚之间的间距分:普通标准型塑料封装,双列、单列直插式一般多为2.54±0.25 mm,其次有2mm(多见于单列直插式)、1.778±0.25mm(多见于缩型双列直插式)、1.5±0.25mm,或1.27±0.25mm(多见于单列附散热片或单列V 型)、1.27±0.25mm(多见于双列扁平封装)、1±0.15mm(多见于双列或四列扁平封装)、0.8±0.05~0.15mm(多见于四列扁平封装)、0.65

±0.03mm(多见于四列扁平封装)。

双列直插式两列引脚之间的宽度分:一般有7.4~7.62mm、10.16mm、12.7mm、15.24mm等数种。

双列扁平封装两列之间的宽度分(包括引线长度:一般有6~6.5±mm、7.6mm、10.5~10.65mm 等。

四列扁平封装40 引脚以上的长×宽一般有:10×10mm(不计引线长度)、13.6

×13.6±0.4mm(包括引线长度)、20.6×20.6±0.4mm(包括引线长度)、8.45×8.45±0.5mm(不计引线长度)、14×14±0.15mm(不计引线长度)等。

集成电路封装工艺介绍

集成电路封装工艺介绍

SMD(Surface Mount Technology,表面安装技术)集成电路封装技术是一种利用表面安装技术来安装集成电路片上的元件,这种技术为模块封装提供了一种新的封装方式。

SMD封装技术在使用后可以实现低成本、高密度和高可靠性,在封装技术中已经得到了广泛应用。

下面介绍SMD集成电路封装工艺:

1.贴标:将集成电路封装片进行贴标,贴标中需包含集成电路芯片型号、芯片生产厂商、批量等信息,以及集成电路封装片的图纸。

2.清洗:进行封装片的清洗,通常使用抛光膏、洗涤液等来完成清洗工作,使其能够保持清洁无杂质。

3.引弧焊:将元件焊接到封装片上,通常采用引弧焊工艺,即采用电弧的能量将元件与前面进行过清洗的封装片上焊上。

4.返修:返修是根据集成电路封装的失效原因,通过改变封装片上的焊接参数和元件的安装形式,来改善集成电路封装的质量,以保证封装片的质量,通过返修可以减少集成电路封装的失效。

5.检测:检测是从元件安装,焊接,到封装完成后,进行完整性和质量检测,进而使其在使用中能够发挥良好的性能,满足质量要求。

集成电路封装

集成电路封装

集成电路封装,又称芯片封装,是指将集成电路芯片进行封装,以提供保护、连接和连接外部电路的功能。

常见的集成电路封装有以下几种类型:

1. 对顶焊接(DIP)封装:这是最早也是最常见的封装形式之一,通常用于较低密度和较低频率的应用。

它采用两排引脚,可以直接插入插座或焊接到电路板上。

2. 表面贴装技术(SMT)封装:这是目前最常用的封装技术,广泛应用于各种电子设备中。

SMT封装可以有效提高集成度和组装效率,减小封装体积和重量。

3. 高级封装:随着技术的发展,出现了一些更高级的封装形式,例如球形阵列封装(BGA)、无引脚封装(LGA)和封装在柔性基板上的芯片(COF)等。

这些封装形式主要用于高密度、高速和复杂电路的应用。

封装的选择会根据应用需求、电路复杂性、可靠性和成本

等因素进行评估和决策。

不同的封装形式有各自的优缺点,需要根据具体的设计要求和制造工艺选择适合的封装。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

芯片封装方大全各种IC封装形式图片各种封装缩写说明BGABQFP132BGABGABGABGABGA CLCCCNRPGADIPDIP-tab BGADIPTOFlat PackHSOP28 TOTOJLCC LCCCLCCBGALQFP DIPPGAPLCCPQFPDIP LQFPLQFPPQFPQFPQFPTQFP BGASC-70 5LDIPSIPSOSOHSOJSOJSOPTOSOPSOPCANTOTOTOTO3CANCANCANCANCANTO8TO92CANCANTSOPTSSOP or TSOP BGABGAZIPPCDIP以下封装形式未找到相关图片,仅作简易描述,供参考:DIM单列直插式,塑料例如:MH88500QUIP蜘蛛脚状四排直插式,塑料例如:NEC7810DBGA BGA系列中陶瓷芯片例如:EP20K400FC672-3CBGA BGA系列中金属封装芯片例如: EP20K300EBC652-3 MODULE方形状金属壳双列直插式例如:LH0084RQFP QFP封装系列中,表面带金属散装体例如:EPF10KRC系列DIMM电路正面或背面镶有LCC封装小芯片,陶瓷,双列直插式例如:X28C010DIP-BATTERY电池与微型芯片内封SRAM芯片,塑料双列直插式例如:达拉斯SRAM系列(五)按用途分类集成电路按用途可分为电视机用集成电路。

音响用集成电路、影碟机用集成电路、录像机用集成电路、电脑(微机)用集成电路、电子琴用集成电路、通信用集成电路、照相机用集成电路、遥控集成电路、语言集成电路、报警器用集成电路及各种专用集成电路。

电视机用集成电路包括行、场扫描集成电路、中放集成电路、伴音集成电路、彩色解码集成电路、AV/TV转换集成电路、开关电源集成电路、遥控集成电路、丽音解码集成电路、画中画处理集成电路、微处理器(CPU)集成电路、存储器集成电路等。

音响用集成电路包括AM/FM高中频电路、立体声解码电路、音频前置放大电路、音频运算放大集成电路、音频功率放大集成电路、环绕声处理集成电路、电平驱动集成电路、电子音量控制集成电路、延时混响集成电路、电子开关集成电路等。

影碟机用集成电路有系统控制集成电路、视频编码集成电路、MPEG解码集成电路、音频信号处理集成电路、音响效果集成电路、RF信号处理集成电路、数字信号处理集成电路、伺服集成电路、电动机驱动集成电路等。

录像机用集成电路有系统控制集成电路、伺服集成电路、驱动集成电路、音频处理集成电路、视频处理集成电路。

1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且BGA 不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为 1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

2、BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。

3、碰焊PGA(butt joint pin grid array)表面贴装型PGA 的别称(见表面贴装型PGA)。

4、C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。

带有玻璃窗口的Cerdip 用于紫外线擦除型EPROM 以及内部带有EPROM 的微机电路等。

引脚中心距2.54mm,引脚数从8 到42。

在日本,此封装表示为DIP-G(G 即玻璃密封的意思)。

6、Cerquad表面贴装型封装之一,即用下密封的陶瓷QFP,用于封装DSP 等的逻辑LSI 电路。

带有窗口的Cerquad 用于封装EPROM 电路。

散热性比塑料QFP 好,在自然空冷条件下可容许1. 5~2W 的功率。

但封装成本比塑料QFP 高3~5 倍。

引脚中心距有1.27mm、0.8mm、0.65mm、0. 5mm、0.4mm 等多种规格。

引脚数从32 到368。

7、CLCC(ceramic leaded chip carrier)带引脚的陶瓷芯片载体,表面贴装型封装之一,引脚从封装的四个侧面引出,呈丁字形。

带有窗口的用于封装紫外线擦除型EPROM 以及带有EPROM 的微机电路等。

此封装也称为QFJ、QFJ-G(见QFJ)。

8、COB(chip on board)板上芯片封装,是裸芯片贴装技术之一,半导体芯片交接贴装在印刷线路板上,芯片与基板的电气连接用引线缝合方法实现,芯片与基板的电气连接用引线缝合方法实现,并用树脂覆盖以确保可靠性。

虽然COB 是最简单的裸芯片贴装技术,但它的封装密度远不如TAB 和倒片焊技术。

9、DFP(dual flat package)双侧引脚扁平封装。

是SOP 的别称(见SOP)。

以前曾有此称法,现在已基本上不用。

10、DIC(dual in-line ceramic package)陶瓷DIP(含玻璃密封)的别称(见DIP).11、DIL(dual in-line)DIP 的别称(见DIP)。

欧洲半导体厂家多用此名称。

12、DIP(dual in-line package)双列直插式封装。

插装型封装之一,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。

DI P 是最普及的插装型封装,应用范围包括标准逻辑IC,存贮器LSI,微机电路等。

引脚中心距2.5 4mm,引脚数从6 到64。

封装宽度通常为15.2mm。

有的把宽度为7.52mm 和10.16mm 的封装分别称为skinny DIP 和slim DIP(窄体型DIP)。

但多数情况下并不加区分,只简单地统称为DI P。

另外,用低熔点玻璃密封的陶瓷DIP 也称为cerdip(见cerdip)。

13、DSO(dual small out-lint)双侧引脚小外形封装。

SOP 的别称(见SOP)。

部分半导体厂家采用此名称。

14、DICP(dual tape carrier package)双侧引脚带载封装。

TCP(带载封装)之一。

引脚制作在绝缘带上并从封装两侧引出。

由于利用的是TAB(自动带载焊接)技术,封装外形非常薄。

常用于液晶显示驱动LSI,但多数为定制品。

另外,0.5mm 厚的存储器LSI 簿形封装正处于开发阶段。

在日本,按照EIAJ(日本电子机械工业)会标准规定,将DICP 命名为DTP。

15、DIP(dual tape carrier package)同上。

日本电子机械工业会标准对DTCP 的命名(见DTCP)。

16、FP(flat package)扁平封装。

表面贴装型封装之一。

QFP 或SOP(见QFP 和SOP)的别称。

部分半导体厂家采用此名称。

17、flip-chip倒焊芯片。

裸芯片封装技术之一,在LSI 芯片的电极区制作好金属凸点,然后把金属凸点与印刷基板上的电极区进行压焊连接。

封装的占有面积基本上与芯片尺寸相同。

是所有封装技术中体积最小、最薄的一种。

但如果基板的热膨胀系数与LSI 芯片不同,就会在接合处产生反应,从而影响连接的可靠性。

因此必须用树脂来加固LSI 芯片,并使用热膨胀系数基本相同的基板材料。

18、FQFP(fine pitch quad flat package)小引脚中心距QFP。

通常指引脚中心距小于0.65mm 的QFP(见QFP)。

部分导导体厂家采用此名称。

19、CPAC(globe top pad array carrier)美国Motorola 公司对BGA 的别称(见BGA)。

20、CQFP(quad fiat package with guard ring)带保护环的四侧引脚扁平封装。

塑料QFP 之一,引脚用树脂保护环掩蔽,以防止弯曲变形。

在把LSI 组装在印刷基板上之前,从保护环处切断引脚并使其成为海鸥翼状(L 形状)。

这种封装在美国Motorola 公司已批量生产。

引脚中心距0.5mm,引脚数最多为208 左右。

21、H-(with heat sink)表示带散热器的标记。

例如,HSOP 表示带散热器的SOP。

22、pin grid array(surface mount type)表面贴装型PGA。

通常PGA 为插装型封装,引脚长约3.4mm。

表面贴装型PGA 在封装的底面有陈列状的引脚,其长度从1.5mm 到2.0mm。

贴装采用与印刷基板碰焊的方法,因而也称为碰焊PGA。

因为引脚中心距只有1.27mm,比插装型PGA 小一半,所以封装本体可制作得不怎么大,而引脚数比插装型多(250~528),是大规模逻辑LSI 用的封装。

封装的基材有多层陶瓷基板和玻璃环氧树脂印刷基数。

以多层陶瓷基材制作封装已经实用化。

23、JLCC(J-leaded chip carrier)J 形引脚芯片载体。

指带窗口CLCC 和带窗口的陶瓷QFJ 的别称(见CLCC 和QFJ)。

部分半导体厂家采用的名称。

24、LCC(Leadless chip carrier)无引脚芯片载体。

指陶瓷基板的四个侧面只有电极接触而无引脚的表面贴装型封装。

是高速和高频IC 用封装,也称为陶瓷QFN 或QFN-C(见QFN)。

25、LGA(land grid array)触点陈列封装。

即在底面制作有阵列状态坦电极触点的封装。

装配时插入插座即可。

现已实用的有227 触点(1.27mm 中心距)和447 触点(2.54mm 中心距)的陶瓷LGA,应用于高速逻辑L SI 电路。