半导体材料英文缩略语

常见封装缩写解释

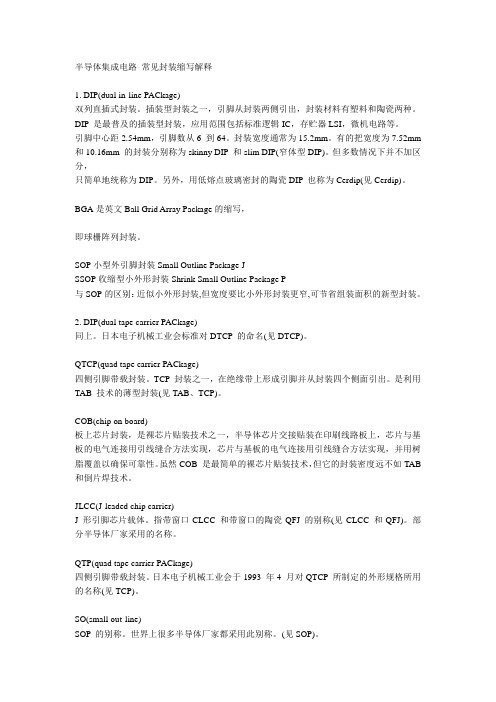

半导体集成电路常见封装缩写解释1. DIP(dual in-line PACkage)双列直插式封装。

插装型封装之一,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。

DIP 是最普及的插装型封装,应用范围包括标准逻辑IC,存贮器LSI,微机电路等。

引脚中心距2.54mm,引脚数从6 到64。

封装宽度通常为15.2mm。

有的把宽度为7.52mm 和10.16mm 的封装分别称为skinny DIP 和slim DIP(窄体型DIP)。

但多数情况下并不加区分,只简单地统称为DIP。

另外,用低熔点玻璃密封的陶瓷DIP 也称为Cerdip(见Cerdip)。

BGA是英文Ball Grid Array Package的缩写,即球栅阵列封装。

SOP小型外引脚封装Small Outline Package JSSOP收缩型小外形封装Shrink Small Outline Package P与SOP的区别:近似小外形封装,但宽度要比小外形封装更窄,可节省组装面积的新型封装。

2. DIP(dual tape carrier PACkage)同上。

日本电子机械工业会标准对DTCP 的命名(见DTCP)。

QTCP(quad tape carrier PACkage)四侧引脚带载封装。

TCP 封装之一,在绝缘带上形成引脚并从封装四个侧面引出。

是利用TAB 技术的薄型封装(见TAB、TCP)。

COB(chip on board)板上芯片封装,是裸芯片贴装技术之一,半导体芯片交接贴装在印刷线路板上,芯片与基板的电气连接用引线缝合方法实现,芯片与基板的电气连接用引线缝合方法实现,并用树脂覆盖以确保可靠性。

虽然COB 是最简单的裸芯片贴装技术,但它的封装密度远不如TAB 和倒片焊技术。

JLCC(J-leaded chip carrier)J 形引脚芯片载体。

指带窗口CLCC 和带窗口的陶瓷QFJ 的别称(见CLCC 和QFJ)。

半导体常用英文缩写

半导体常用英文缩写LED – Light Emitting Diode。

FET – Field Effect Transistor。

MOSFET – Metal Oxide Semiconductor Field Effect Transistor。

JFET – Junction Field Effect Transistor。

IGBT – Insulated Gate Bipolar Transistor。

BJT – Bipolar Junction Transistor。

MOS – Metal Oxide Semiconductor。

PSP – Power Schottky Diode。

UJT – Unijunction Transistor。

SCR – Silicon-Controlled Rectifier。

SiC – Silicon Carbide。

HBT – Heterojunction Bipolar Transistor。

LDMOS – Lateral Double-diffused Metal Oxide Semiconductor。

HEMT – High Electron Mobility Transistor。

DFB – Distributed Feedback Laser。

PD – Photodiode。

GaP – Gallium Phosphide。

GaN – Gallium Nitride。

GaAs – Gallium Arsenide。

PJFET – Poly-Junction Field Effect Transistor。

ENSAT – Emitter Switched Bipolar Transistor。

TRIAC – Triode for Alternating Current。

JBS – Junction Barrier Schottky。

FND – Field-effect N-channel Depletion Mode。

半导体领域常用的英文简写

半导体领域常用的英文简写Acronym/Abbreviation TermF(t)CDF at time tf(t) pdf at time tF/O Fab outF/P Field PlateF/P-RS Field Plate Sheet ReductionFA Failure AnalysisFAB FabricationFAE Failure Analysis EngineeringFAI First Article InspectionFBDP fair Bayes decision problemFBFC Full Bit Functional ChipFBLF fair Bayes loss functionFC Flip ChipFCA Flip Chip AttachmentFCOB Flip Chip on BoardFCOG Flip Chip on GlassFCRAM Fast Cycle RAMFEA finite-element analysisFECIC Fab Engineering Change Inspect Committee FECP FAB Engineering Change ProposalFEM Focus Energy MatrixFEOL front end of lineFET Field Effect TransistorFFU Filter Fan UnitFIB Focus Ion BeamFIFO First In First OutFIT Failure In TimeFIT Final Inspection and TestingFMCS Facility monitoring control systemFMEA Failure Mode and Effect Analysis FMECA failure-mode effect and criticality analysis FMO Fab Materials Operation FMS flexible manufacturing systemFN Fowler-NordheimFOL Front-end Of LineFOSB Front opening shipping boxFOUP Front opening uniform podFOX Field OxideFP Flip ChipFPD Focal plane deviationFP-DW Field Plate Width ReductionFPLD field-programmable logic devicesFQA Fixed quality areaFR Failure rateFR-4Flame Resistant laminates-4FRL Film Redistribution Layer FRLDIS Far Row Long Cycle Disturb Test FSA Fabless Semiconductor Association FSF Foundry Service FormFSG Fluorine Silicon GlassFSIM Facility service interface matrixFT Final TestFTIR Fourier Transform InfrairedFTY Final Test YieldFurnaceFVI Final Visual InspectionFWP Final White PaperFYI for your informationFPC Full Pin CountDUT = Die Under T ester ULPC = ultra low pin count FPC flexible print circuit Definition or meaning失效分析ct Committee前段制程场效应晶体管聚焦离子束lity analysisDiffusion Equipment 柔性电路版。

半导体行业术语

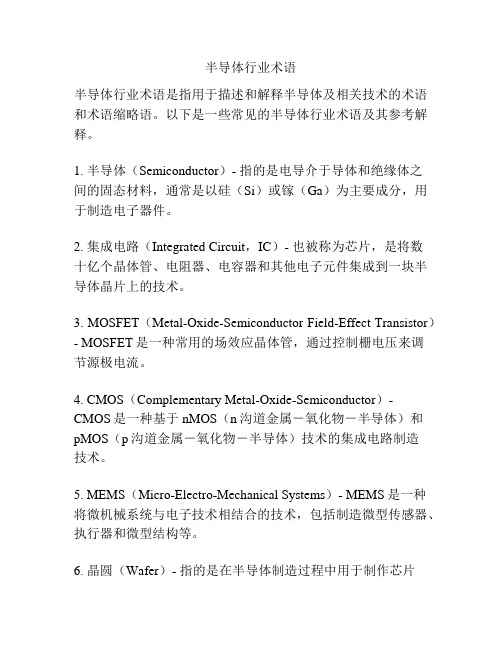

半导体行业术语半导体行业术语是指用于描述和解释半导体及相关技术的术语和术语缩略语。

以下是一些常见的半导体行业术语及其参考解释。

1. 半导体(Semiconductor)- 指的是电导介于导体和绝缘体之间的固态材料,通常是以硅(Si)或镓(Ga)为主要成分,用于制造电子器件。

2. 集成电路(Integrated Circuit,IC)- 也被称为芯片,是将数十亿个晶体管、电阻器、电容器和其他电子元件集成到一块半导体晶片上的技术。

3. MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)- MOSFET是一种常用的场效应晶体管,通过控制栅电压来调节源极电流。

4. CMOS(Complementary Metal-Oxide-Semiconductor)- CMOS是一种基于nMOS(n沟道金属-氧化物-半导体)和pMOS(p沟道金属-氧化物-半导体)技术的集成电路制造技术。

5. MEMS(Micro-Electro-Mechanical Systems)- MEMS是一种将微机械系统与电子技术相结合的技术,包括制造微型传感器、执行器和微型结构等。

6. 晶圆(Wafer)- 指的是在半导体制造过程中用于制作芯片的圆形硅片。

晶圆上会进行刻蚀、沉积、光刻等工艺。

7. 工艺(Process)- 指的是制造半导体器件所需的一系列步骤和工作流程,包括光刻、刻蚀、沉积、清洗等。

8. 掩膜(Mask)- 掩膜用于光刻工艺,上面有设计好的图案,通过光刻暴光制造电路芯片的图案。

9. Doping(掺杂)- 在半导体材料中引入杂质,以调整材料的导电性能。

常见的掺杂剂包括硼、磷、砷等。

10. 渗透磁场(Permeable Magnetic Field)- 渗透磁场是指在磁性材料的边界上产生的特殊磁场,常用于磁传感器和存储器中。

11. 氮化镓(Gallium Nitride,GaN)- 氮化镓是一种半导体材料,具有高电子流动性和较大的能隙,适用于高功率电子器件的制造。

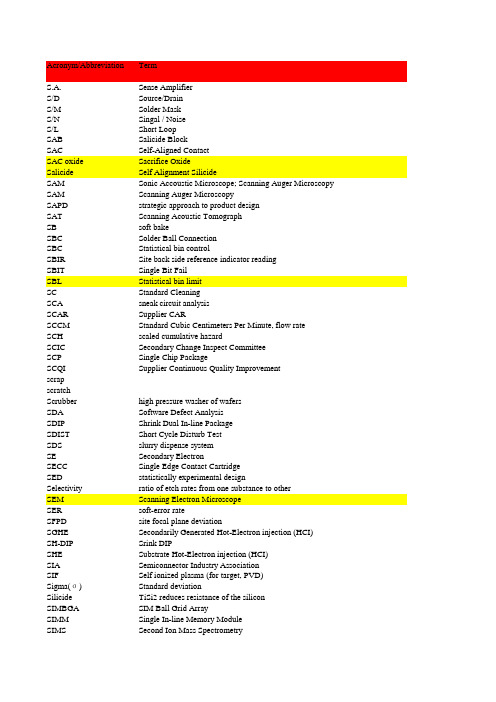

半导体领域常用的英文简写

Acronym/Abbreviation TermS.A.Sense AmplifierS/D Source/DrainS/M Solder MaskS/N Singal / NoiseS/L Short LoopSAB Salicide BlockSAC Self-Aligned ContactSAC oxide Sacrifice OxideSalicide Self Alignment SilicideSAM Sonic Accoustic Microscope; Scanning Auger Microscopy SAM Scanning Auger MicroscopySAPD strategic approach to product designSAT Scanning Acoustic TomographSB soft bakeSBC Solder Ball ConnectionSBC Statistical bin controlSBIR Site back side reference indicator readingSBIT Single Bit FailSBL Statistical bin limitSC Standard CleaningSCA sneak circuit analysisSCAR Supplier CARSCCM Standard Cubic Centimeters Per Minute, flow rateSCH scaled cumulative hazardSCIC Secondary Change Inspect CommitteeSCP Single Chip PackageSCQI Supplier Continuous Quality ImprovementscrapscratchScrubber high pressure washer of wafersSDA Software Defect AnalysisSDIP Shrink Dual In-line PackageSDIST Short Cycle Disturb TestSDS slurry dispense systemSE Secondary ElectronSECC Single Edge Contact CartridgeSED statistically experimental designSelectivity ratio of etch rates from one substance to otherSEM Scanning Electron MicroscopeSER soft-error rateSFPD site focal plane deviationSGHE Secondarily Generated Hot-Electron injection (HCI)SH-DIP Srink DIPSHE Substrate Hot-Electron injection (HCI)SIA Semiconnector Industry AssociationSIF Self ionized plasma (for target, PVD)Sigma(σ)Standard deviationSilicide TiSi2 reduces resistance of the siliconSIMBGA SIM Ball Grid ArraySIMM Single In-line Memory ModuleSIMS Second Ion Mass SpectrometrySIN Silicon NitrideSINTER anneal metal to make better contactsSIP self-ionized plasmaSK-DIP Skinny Dual Inline PackageSLC Surface Laminar CircuitsSL-DIP Slim DIPSLED shelf life elongation dispositionSLI Single Lot IdentifierSLICC Slightly Large than IC Carrier (by Motorola)SLLN strong law of large numberSLM Scanning Light MicroscopeSM Stress MigrationSMC Single Chip ModuleSMD Solder Mask DefinedSMD Surface Mount DeviceSMIF Standard Mechanism InterfaceSMOBC Solder Mask Over Bare CopporSMS Semiconductor Manufacturing SystemSMS Shifted Measurement ScalsSMT Surface Mount TechnologySMU Source Measurement UnitSNR Signal to Noise AnalysisSO/SOP Small Outline PackageSOA Safe Operating AreaSOC System On ChipSOG Spin-On GlassSOG sample outgoingSOI Silicon On InsulatorSOIC Small Outline Integrated CircuitSOJ Small Outline J-Lead PackageSOP Small Outline PackageSOP Standard Operation ProcedureSOS Silicon On SapphireSOW statement of workSPC Statistical Process ControlSPD Silicon Product Division (TI Sherman)SPDC Semiconductor Process Design Center in TIspecSPECS Semiconductor Process Evaluation Core SoftwareSPEED System Product Engineering and ECO (Engineering Change Order) Database SPLRS super Long Ras Cycle TesrtSPM Mixture of Sulfuric Acid Solution and hydrogen peroxide (H2SO4 H2O2) sulfuric acid hydrogen peroxide mixtureSputter metals depositionSQA software quality assuranceSQC Statistical Quality ControlSQRR Supplier quality & reliability requirements SRAM Static Random Access MemorySRD Spin, Rinse, DrySRM Solvent Rinse ModuleSRO Silicon Rich OxideSRP Surface Resistance ProfilingSRR Supplier Rating & RankingSS Sample SizeSSER System Soft Error RateSSI Small-scale integrationSSOP Shrink Small Outline PackageSTD StandardStep Coverage amount of a step covered on a depositionSTI Shallow Trench IsolationSTIR site total indicator readingSTM Scanning Tunneling MicroscopeSTR Special Test RequestSTS ship to stockSTVS Simultaneous TVSSUTT Start-Up Test TeamSVP Small Vertical packageSWEAT Standard Wafer-level Electromigration Acceleration Test SWOX Side Wall OxideSWR Special Work RequestDefinition or meaning牺牲氧化(typically at 80-100 degrees Celsius) to drive报废刮伤洗刷标准机械操作界面规格溅射浅沟槽隔绝技术特殊测试要求。

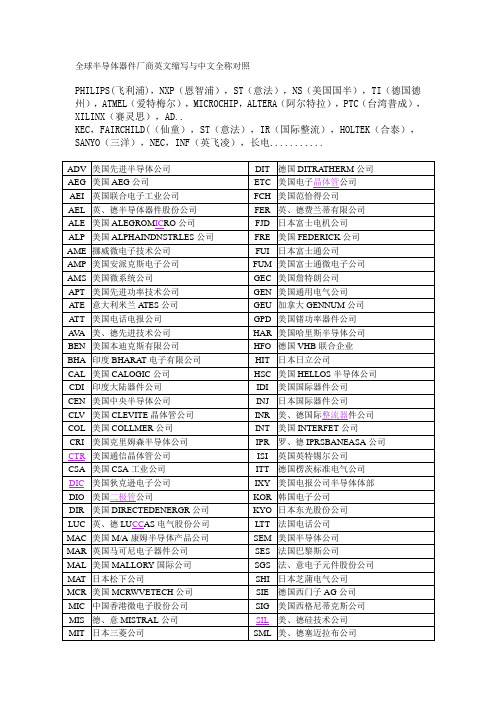

全球半导体器件电子元件厂商英文缩写与中文全称对照

美国FEDERICK公司

AME

挪威微电子技术公司

FUI

日本富士通公司

AMP

美国安派克斯电子公司

FUM

美国富士通微电子公司

AMS

美国微系统公司

GEC

美国詹特朗公司

APT

美国先进功率技术公司

GEN

美国通用电拿大GENNUM公司

ATT

美国电话电报公司

GPD

美国锗功率器件公司

IXY

美国电报公司半导体体部

DIO

美国二极管公司

KOR

韩国电子公司

DIR

美国DIRECTEDENERGR公司

KYO

日本东光股份公司

LUC

英、德LUCCAS电气股份公司

LTT

法国电话公司

MAC

美国M/A康姆半导体产品公司

SEM

美国半导体公司

MAR

英国马可尼电子器件公司

SES

法国巴黎斯公司

MAL

美国MALLORY国际公司

SOL

美、德固体电子公司

MUL

英国马德拉有限公司

SON

日本萦尼公司

NAS

美、德北美半导体电子公司

SPE

美国空间功率电子学公司

NEW

英国新市场晶体管有限公司

SPR

美国史普拉格公司

NIP

日本日电公司

SSI

美国固体工业公司

NJR

日本新日本无线电股份有公司

STC

美国硅晶体管公司

NSC

美国国家半导体公司

STI

ADV

美国先进半导体公司

DIT

德国DITRATHERM公司

AEG

美国AEG公司

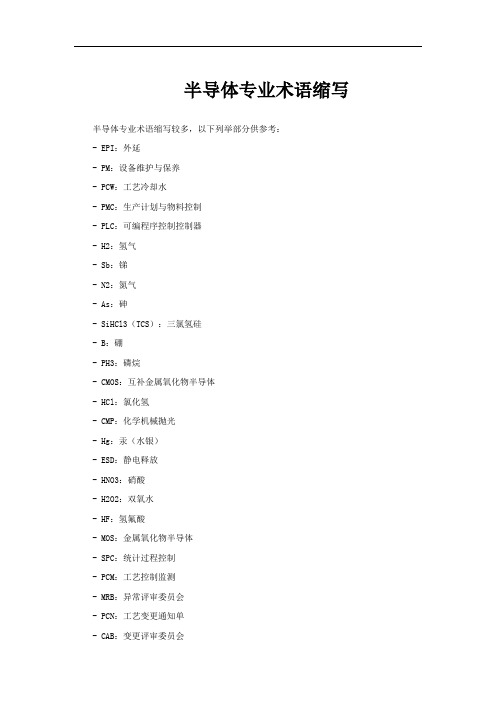

半导体专业术语缩写

半导体专业术语缩写

半导体专业术语缩写较多,以下列举部分供参考:

- EPI:外延

- PM:设备维护与保养

- PCW:工艺冷却水

- PMC:生产计划与物料控制

- PLC:可编程序控制控制器

- H2:氢气

- Sb:锑

- N2:氮气

- As:砷

- SiHCl3(TCS):三氯氢硅

- B:硼

- PH3:磷烷

- CMOS:互补金属氧化物半导体

- HCl:氯化氢

- CMP:化学机械抛光

- Hg:汞(水银)

- ESD:静电释放

- HNO3:硝酸

- H2O2:双氧水

- HF:氢氟酸

- MOS:金属氧化物半导体

- SPC:统计过程控制

- PCM:工艺控制监测

- MRB:异常评审委员会

- PCN:工艺变更通知单

- CAB:变更评审委员会

- ECN:工程变更通知单

- OCAP:失效控制计划

- PSG:磷硅玻璃

- TF:薄膜

- PVD:物理气相淀积

- PHO:光刻

- PCB:印刷电路板

- DIF:扩散

- RF:射频

- II:注入

- UV:紫外线

- CVD:化学气相淀积

- VPE:气相外延

- SPV:扩散长度

- Bubbler:鼓泡器

- CD:关键尺寸

- EMO:设备紧急按钮

- CD-SEM:线宽扫描电镜

- Scrubber:尾气处理器

- ETCH:刻蚀(腐蚀)

- Coat:包硅

- H2-BAKE:氢气烘烤

- SRP:外延层纵向电阻率分布

如果你还想了解其他缩写,可以继续向我提问。

半导体常用缩写

半导体常用缩写词汇汇总EPI 外延PM 设备维护与保养PCW 工艺冷却水PMC 生产计划与物料控制PLC 可编程序控制控制器H2 氢气Sb 锑N2 氮气As 砷SiHCl3(TCS)三氯氢硅 B 硼PH3 磷烷CMOS 互补金属氧化物半导体HCl 氯化氢CMP 化学机械抛光Hg 汞(水银)ESD静电释放HNO3 硝酸H2O2双氧水HF 氢氟酸MOS 金属氧化物半导体SPC 统计过程控制PCM 工艺控制监测MRB 异常评审委员会PCN 工艺变更通知单CAB 变更评审委员会ECN 工程变更通知单OCAP 失效控制计划。

指制程过程中失控时所应采取的对应措施。

是一种受控文件,包含造成异常的因素等PSG 磷硅玻璃TF 薄膜PVD物理气相淀积PHO 光刻PCB 印刷电路板DIF 扩散RF 射频II 注入UV紫外线CVD 化学气相淀积VPE气相外延SPV 扩散长度Bubbler 鼓泡器CD 关键尺寸EMO 设备紧急按钮CD-SEM 线宽扫描电镜ScrubbLer 尾气处理器ETCH 刻蚀(腐蚀)Coat 包硅H2-BAKE 氢气烘烤SRP 外延层纵向电阻率分布1号液:(NH4OH:H2O2:H2O)NH4OH : H2O2 : H2O=1 : 2 : 7,2号液:(HCl:H2O2:H2O)HCl : H2O2 : H2O=1 : 2 : 53号液(Caros清洗液):(H2SO4:H2O2) H2SO4 : H2O2=3 : 1,4#号液:H2O:HF=10:1CV:电容-电压测试BOE混酸:氟化铵氢氟酸混合腐蚀液液CZ:切克劳斯基直拉法Wafer:抛光片FZ:区熔方法THK:膜厚Rs:电阻TTV:总厚度偏差TIR:平整度STIR:局部平整度LTO:背封BOW:弯曲度CHIP:崩边SLIP:滑移线MARK:痕迹WARP:翘曲度CRACK:裂纹SPOT: 斑点HAZE:发雾CROWN:皇冠,边缘突起物OISF:氧化诱生层错ORG: 掺As单晶抛光片O2含量径向均匀性OSF:氧化层错BMV:气体流量控制阀LIFE TIME:寿命POINT DEFECT: 点缺陷Integrated circuit:集成电路epitaxial layer:外延层Buried layer:埋层interface:界面Diameter:直径chemical vapor polish 化学气相抛光Polished surface :表面抛光back side ;反面Front side :正面INJ:引入气体流量DIL:稀释气体流量Autodoping:自掺杂Sccm:毫升/每分钟Slm:升/每分钟CDA:压缩空气PN2:工艺氮气Cable:电缆MES:生产过程执行管理系统SFC:生产车间集中MDC:生产数据及设备状态信息采集分析管理系统PDM:制造过程数据文档管理系统MSA:量具测量系统分析KPI:关键表现指标, 销售指标Alarm :报警MSA: 使用数据统计和图表的方法对测量系统的分辨率和误差进行分析QA: 指质量管理、品质的保证、质量的评估/评价QC: 指质量检验和控制、分析、改善和不合格品控制人员的总称OOC/oos:OOS:检验结果偏差超过规格、不合格OOC : 产品质量失去控制,需要采取返工、召回等手段。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

[材料科学] 半导体材料英文缩略语材料科学2008-03-24 16:18:46 阅读37 评论0 字号:大中小订阅援引:MEMC Electronic Materials, Inc.A. -- AngstromA-defects -- Dislocation loops in Silicon formed by agglomeration of interstitialsAA -- Atomic absorptionAE -- Acid EtchAFM -- Atomic Force MicroscopyALCVD -- Atomic Layer Chemical Vapor DepositionAMC -- Barrel or batch type Epi reactor (Applied Materials)APCVD -- Atmospheric-Pressure Chemical Vapor Deposition Furnace ASIC -- Application Specific Integrated CircuitASM -- a single-chamber Epi reactor (ASM America)ASTM -- American Standard Test MethodASTM -- American Society for Testing and MaterialsBBESOI -- Bonded and Etch Back SOIBGSOI -- Bonded and Grind Back SOIBJT -- Bipolar Junction TransistorBMD -- Bulk Micro-Defects or Bulk Microdefect Density (used almost exclusivelyas a measure of the oxygen precipitate density)BOE -- Buffered Oxide EtchBOX -- Buried Oxide LayerBP -- Backside PolishBV -- Breakdown VoltageBvox -- Breakdown Voltage-oxideC°C -- Centigrade°C/min -- Centigrade per minuteCD -- Critical DimensionCE -- Caustic Etchcm -- Centimeter (0.01 meter)CMOS -- Complementary Metal Oxide SemiconductorCMP -- Chemical Mechanical PolishingCO -- Carbon MonoxideCO2 -- Carbon DioxideCOO -- Cost of OwnershipCOP’s -- Crystal Originated ParticlesCoQC -- Certificate Of Quality ConformanceCP -- Crystal PullerCV -- Capacity or capacitance voltageCVD -- Chemical Vapor DepositionCZ -- Czochralski method of pulling single crystalDD-defects -- Very small voids in Silicon formed by agglomeration of vacanciesDIBL -- Drain Induced Barrier LoweringDIC -- Differential Interference ContrastDL -- Diffusion LengthDMOS -- Double-diffused MOSDOE -- Design of ExperimentsDOF -- Depth of FocusDRAM -- Dynamic Random Access MemoryDSOD – Direct Surface Oxide DefectDSP -- Double Sided PolishDZ -- Denuded Zone (depth measured from the surface that is free of oxygenprecipitates and which is denuded of interstitial oxygen (byout-diffusion))EeDRAM -- Embedded Dynamic Random Access MemoryEG -- Enhanced GetteringEEPROM -- Electrically-erasable and Programmable Read-only MemoryEPROM -- Erasable and Programmable Read-only MemoryEOT -- Equivalent Oxide ThicknessEPI -- EpitaxyESF -- Epi Stacking FaultFFBE -- Floating Body EffectFET -- Field Effect TransistorFD-SOI -- Fully Depleted Silicon-on-InsulatorFPD -- Flow Pattern Defect (ref. Crystal)FPD -- Focal Plane Deviation (ref. Mechanical flatness)FRAM -- Ferroelectric Random Access MemoryFTIR -- Fourier Transform Infra-Red SpectroscopyFZ -- Float Zone method of Crystal PullingGGBIR -- Global flatness, back-referenced GeOI -- Germanium-on-InsulatorGFA -- Gas Fusion AnalysisGOI -- Gate Oxide IntegrityGTIR -- Global Total Indicated Reading GUI -- Graphical User InterfaceHH2 -- Hydrogen gasH2O2 -- Hydrogen PeroxideHCl -- Hydrogen ChlorideHF -- Hydrofluoric AcidHMOS -- High-performance MOSHZ -- Hot ZoneIIC -- Integrated CircuitsIDM -- Integrated Device ManufacturerIG -- Internal GetteringIGBT -- Insulated Gate Bipolar Transistor IQC -- Incoming Quality ControlISO -- International Standards Organization ITOX -- Internal OxidationJFET -- Junction Field Effect TransistorKkg -- KilogramkN -- Kilo NewtonKOH -- Potassium HydroxidekP -- Kilo PascalKSIE -- Thousand Square Inch EquivalentLLAD -- Large Area DefectLg -- Transistor Gate LengthLLS -- Localized Light ScatterersLLPD’s -- Large Light Point DefectsLPCVD -- Low Pressure Chemical Vapor DepositionLPD’s -- Light Point DefectsLPD-E -- Light Point Defect, class E (a KLA-Tencor SP1 defect class) LPD-N -- Light Point Defect, class N (a KLA-Tencor SP1 defect class) LPD-S -- Light Point Defect, class S (a KLA-Tencor SP1 defect class) LPE -- Liquid Phase EpitaxyLSE -- Latex Sphere Equivalent particle sizeLSI -- Large-scale IntegrationLSTD -- Laser Scattering Tomographic DetectionLTO -- Low Temperature OxideM9K -- MEMC proprietary polishing machineMBE -- Molecular Beam EpitaxyMDZ -- Magic Denuded Zone (gettering)MEMS -- Micro-ElectroMechanical SystemMIM -- Metal-Insulator-MetalMLD -- Modified Low Dosemm -- 1/1000 of a meter and 0.03937 inchmm/min -- millimeters per minuteMNOS -- Metal Nitride Oxide SemiconductorMOCVD -- MetalOrganic Chemical Vapor Deposition MODFET -- Modulation-Doped Field Effect TransistorMOS -- Metal Oxide SemiconductorMOSFET -- Metal Oxide Semiconductor Field Effect Transistor MRAM -- Magnetoresistive Random Access MemoryMSI -- Medium-scale IntegrationMSIE -- Million Square Inch EquivalentNN -- Silicon doped to create excess negative charge carriers (electrons)N+ -- Heavily doped, N-type siliconNT -- NanotopographyN2 -- Nitrogen gasnm -- nanometersNMOS -- N-channel Metal Oxide SemiconductorNPT -- Non-Punch ThroughO2 -- OxygenOi -- Interstitial OxygenOISF -- Oxidation-Induced Stacking FaultOPP -- Optical Precipitate ProfilerOUM -- Ovonics Unified MemoryPP -- Silicon doped to create excess positive charge carriers (holes)P- -- Lightly doped P-type silicon waferP+ -- Heavily doped P-type silicon waferP/P+ -- Lightly doped P-type epi layer on a heavily doped P-type substrateP/P- -- Lightly doped P-type epi layer on a lightly doped P-type substrateP-band -- Anomalous oxygen precipitation region in vicinity of the vacancy/interstitial boundaryPD-SOI -- Partially Depleted Silicon-on-InsulatorPECVD -- Plasma Enhanced Chemical Vapor Deposition Furnace PFRAM -- Polymeric Ferroelectric Random Access MemoryPFZ -- Precipitate Free Zone (depth measured from the surface that is free ofoxygen precipitates but not necessarily depleted in interstitial oxygen) PMOS -- P-channel Metal Oxide SemiconductorPPB -- Parts Per BillionPPC -- Post Polish CleanPPE -- Personal Protective EquipmentPPM -- Parts Per MillionPPMA -- Parts Per Million AtomicPPMD -- Parts Per Million DefectivePPT -- Parts Per TrillionPROM -- Programmable Read-only MemoryPT -- Punch ThroughP/V -- Peak to Valley measurementPZT -- Lead Zirconate TitanateQRRAM -- Random Access MemoryRF -- Radio FrequencyRFCMOS -- Radio-Frequency Complementary Metal Oxide SemiconductorROM -- Read-only MemoryRSD -- Raised Source/DrainRTA -- Rapid Thermal AnnealRTP -- Rapid Thermal ProcessSSAC -- Submicron Application CrystalSBIR -- Site flatness, back-referencedSBSD -- Soft Backside DamageSC1 -- 1st cleaning bath in the standard “RCA clean” sequence, consisting ofNH4OH / H202/ H20 solution designed to remove particles from Si surfaceSC2 –2nd cleaning bath in the standard “RCA clean” sequence, consisting ofHCl / H202/ H20 solution designed to remove metals from Si surfaceSCE -- Short Channel EffectsSEM -- Scanning Electron MicroscopeSFQR -- Site flatness, best-fit, front-referencedSFSR -- Site flatness, best-fit, front-referenced, scanning siteSGOI – Strained Si on SiGe on InsulatorSi -- SiliconSIE -- Square Inch EquivalentSIMOX -- Separation by Implantation of OxygenSIMS -- Secondary Ion Mass SpectroscopySiO -- Silicon MonoxideSiO2 -- Silicon DioxideSIP -- Single In-line PackageSIRM -- Scanning Infra-red MicroscopeSoC -- System-on-a-ChipSOI -- Silicon-on-InsulatorSOS -- Silicon-on-SapphireSPT -- Soft Punch ThroughSPV -- Surface PhotovoltageSRAM -- Static Random Access MemorySRP -- Spreading Resistance Probe or Spreading Resistance Profile SSI -- Small-scale IntegrationsSi -- Strained SiliconSSIS -- Surface Scanning Inspection SystemSSOI -- Strained Silicon directly on InsulatorSSP -- Single Side PolishSTD -- StandardSTD CZ -- Standard Czochralski-grown CrystalSTI -- Shallow Trench IsolationSTIR -- Site TIR (Total Indicated Reading)TT -- TemperatureTCS -- TrichlorosilaneTEM -- Transmission Electron MicroscopeTIR -- Total Indicated ReadingTOX -- Gate Oxide ThicknessTsoi -- Thickness of SOI top Si layerTSOP -- Thin Small Outline PackageTTV -- Total Thickness VariationUULSI -- Ultra Large-scale IntegrationVv/G -- v: growth rate (crystal pulling rate), G: vertical temperature gradient atmelt/solid interfaceVI -- Vacancy InterstitialVLSI -- Very Large-scale IntegrationVPE -- Vapor Phase EpitaxyWWRFTIR -- Whole Rod Fourier Transform Infra-Red Spectroscopy XXTL -- CrystalZZD -- Zero Dislocation。