青岛理工大学eda作业

eda大作业

e d a大作业本页仅作为文档页封面,使用时可以删除This document is for reference only-rar21year.March班级 021291学号 02129057EDA实验报告学院电子工程学院专业电子信息工程学生姓名 02129057导师姓名纠博交通控制器一.设计目标设计一个十字路口交通控制系统,其东西,南北两个方向除了有红、黄、绿灯指示是否允许通行外,还设有时钟,以倒计时方式显示每一路允许通行的时间,绿灯,黄灯,红灯的持续时间分别是70、5和75秒。

当东西或南北两路中任一道上出现特殊情况,例如有消防车,警车要去执行任务,此时交通控制系统应可由交警手动控制立即进入特殊运行状态,即两条道上的所有车辆皆停止通行,红灯全亮,时钟停止计时,且其数字在闪烁。

当特殊运行状态结束后,管理系统恢复原来的状态,继续正常运行。

二.设计思路与实施方案1.设计目标思路整理①在十字路口的两个方向上各设一组红、绿、黄灯,显示顺序为其中一方向(东西方向)是绿灯、黄灯、红灯;另一方向(南北方向)是红灯、绿灯、黄灯。

②设置一组数码管,以倒计时的方式显示允许通行或禁止通行的时间,其中绿灯、黄灯、红灯的持续时间分别是70s、5s和75s。

③当各条路上任意一条上出现特殊情况时,如当消防车、救护车或其他需要优先放行的车辆通过时,各方向上均是红灯亮,倒计时停止,且显示数字在闪烁。

当特殊运行状态结束后,控制器恢复原来状态,继续正常运行。

2.原理分析本系统主要由分频器,计数器,控制器,倒计时显示器等电路组成。

分频器将晶振送来的50MHZ信号变为1HZ时钟信号;计数器实现总共150秒的计数,它也是交通控制系统的一个大循环;控制器控制系统的状态转移和红黄绿灯的信号输出;倒计时显示电路实现75秒,70秒及5秒的倒计时和显示功能。

整个系统的工作时序受控制器控制,是系统的核心。

基于此,做出交通控制系统的转移图如下:其中,s0:A方向绿灯亮,B方向红灯亮,此状态持续70秒;S1:A方向黄灯亮,B方向红灯亮,此状态持续5秒;S2:A方向红灯亮,B方向绿灯亮,此状态持续70秒;S3:A方向红灯亮,B方向黄灯亮,此状态持续5秒;S4:紧急制动状态,A方向红灯亮,B方向红灯亮,当hold=‘0‘时进入这种状态。

(完整word版)EDA计算器设计大作业

计算器设计专业:电子信息工程设计者:本文介绍了一个简单的计算器的设计,该设计采用了现场可编程逻辑器件FPGA设计,并基于VHDL 语言实现加减乘除功能,并用十进制显示在数码管上.系统由计算部分、输入部分、选择部分、输出部分组成,计算部分为加法器、减法器、乘法器和除法器组成.使用Altera公司的QuartusII开发软件进行功能仿真并给出仿真波形,并下载到试验箱,用实验箱上的按键开关模拟输入,用数码管显示十进制计算结果.通过外部按键可以完成四位二进制数的加、减、乘、除四种运算功能,其结果简单,易于实现.关键字:VHDL,计算器,QuartusII一.实验目的 (4)二、流程图 (5)三.顶层原理图 (5)四、各个模块 (7)(1)加法器模块 (7)1、封装元件 (7)2、加法器程序 (7)3、仿真结果 (8)(2)减法器模块 (9)1、封装元件 (9)2、减法器程序 (10)3、仿真结果 (11)4、硬件运行结果 (11)(3)乘法器模块 (12)1、封装元件 (12)2、乘法器的设计思想 (13)3、乘法器程序 (14)4、仿真结果 (14)5、硬件运行结果 (15)(4)除法器模块 (16)1、封装元件 (16)2、除法器设计思想 (16)3、除法器程序 (16)4、仿真结果 (17)5、硬件运行结果 (17)(5)8位除法器 (18)1、封装元件 (18)2、8位除法器设计思想 (19)3、8位除法器程序 (19)4、仿真结果 (22)(6)数码管七段译码电路 (22)1、封装元件 (22)2、共阴极七段显示码十六进制转换表 (23)3、七段译码器程序 (23)4、仿真结果 (24)(7)选择模块 (24)1、封装元件 (24)2、程序 (25)五、管脚锁定 (26)六、小结与收获 (26)一.实验目的1、熟悉QuartusII软件的相关操作,掌握数字电路设计的基本流程.2、介绍QuartusII 的软件,掌握基本的设计思路,软件环境参数配置,仿真,管脚分配,下载等基本操作。

EDA

青岛理工大学计算机工程学院 17

D、用VHDL设计4位计数器

取整数数据类型,为什么?

整数取值范围 端口信号模式取 BUFFER,为什么?

B0

1 0 0 1

A

1 1 0

注意整数和位的不同表达方式! 青岛理工大学计算机工程学院

18

VHDL基本语法小结 4

定输出信号数据类型为整数类型:

进位

8位和

8位加数 8位被加数

青岛理工大学计算机工程学院

溢出进位

16

VHDL基本语法小结 3

预定义运算符加载函数:

STD_LOGIC_UNSIGNED程序包;

标准逻辑位矢量数据类型:

STD_LOGIC_VECTOR( 7 DOWNTO 0)

并置操作符:“

& ”

a <= '1' '0' b(1) e(2) IF a d = "10100011” THEN

STD_LOGIC、BIT、INTEGER、BOOLEA

IF语句,不完整性IF语句特点 时序电路描述

青岛理工大学计算机工程学院

25

青岛理工大学计算机工程学院

26

VHDL综合器易于优化 易构成性能良好的时序逻辑模块

结构模式简单、层次分明、易读易懂、易排错

利用同步时序和全局时钟线可实现高速FSM 运行模式类似于CPU,易于进行顺序控制 时高可靠性,非法状态易控制

敏感信号表,PROCESS语句 特点 IF语句,不完整性IF语句特点

Байду номын сангаас

时序电路描述

青岛理工大学计算机工程学院

EDA工程实践作业习题

EDA工程实践作业习题1.试述在系统编程的要紧步骤。

2.电路在设计之前什么缘故第一要建立工程,目的是什么?3.何谓层次化设计,它的优点是什么?4.菊花链下载软件的作用是什么?5.用逻辑输入法设计一个八进制加法器。

6.用VHDL语言设计一串行数据检测器。

7.用混合输入法设计一交通指挥灯,红、黄、绿三盏灯依次点亮的时刻间隔为红30秒,黄10秒,绿30秒,黄10秒,红30秒……。

输入时钟为20ns。

8.设计一个60进制计数器,并写出测试向量。

9.设计一个{1101}序列检测器。

10.试设计一个数字钟,能显示年、月、日或切换显示时、分、秒,并能实现年、月、日和时、分、秒的校正。

11.设计一个频率计。

要求能够测量1000Hz~10Mz的信号频率。

12. 按照以下要求设置一张电路图纸:图纸尺寸为A4号,水平放置,图纸标题栏采纳标准型。

13.在命令状态下,放大、缩小和刷新画面的快捷键分别是什么?14. 可见栅格、锁定栅格和电路栅格的作用分别是什么?如何对它们进行设定?15.如何样使一组图件同时实现两种排列和平均分布?16. 简述原理图元件库绘图工具栏中各个按钮的作用,并指出与这些按钮相对应的菜单命令。

17. 查看并熟练把握如下常用元器件的封装。

三极管:以TO-+数字封装,例如:TO-18。

可变电阻:以VR+数字封装,例如:VR5。

无极性电容:以RAD +数字封装,例如:RAD0.2。

有极性电容:以RB. 数字/.数字封装,例如:RB.4/.8。

单列直插器件(即电路图中的连接器):以SIP+数字封装,例如:SIP4。

电阻类:以AXIAL+数字封装,例如:AXIAL0.3。

二极管:DIODE +数字封装,例如:DIODE0.4。

双列直插器件:以DIP+数字封装,例如:DIP14。

晶振:XTAL1封装。

电源引线:常用POWER+数字封装,例如:POWER4。

TTL门电路、555定时器:常用双列直插器件封装。

无极性电容:以RAD +数字表示有极性电容:以RB.2/.4等等表示单列直插器件(即电路图中的连接器):以SIP +数字表示电阻类:以AXIAL +数字表示二极管:DIODE +数字表示双列直插器件:以DIP +数字晶振:XTAL1电源引线常用POWER+数字表示TTL门电路、555定时器,常用双列直插器件封装储备器实验与实践1、FPGA中LPM_ROM配置与读出实验一.实验目的1、把握FPGA中lpm_ROM的设置,作为只读储备器ROM的工作特性和配置方法。

(完整word版)《EDA技术实用教程(第五版)》习题答案(第1~10章)--潘

《EDA技术实用教程(第五版)》习题1 习题1—1 EDA技术与ASIC设计和FPGA开发有什么关系?FPGA在ASIC设计中有什么用途?P3~4EDA技术与ASIC设计和FPGA开发有什么关系?答:利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC的设计和实现;FPGA和CPLD是实现这一途径的主流器件。

FPGA和CPLD的应用是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)和ASIC设计,以及对自动设计与自动实现最典型的诠释。

FPGA在ASIC设计中有什么用途?答:FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC。

FPGA 实现ASIC设计的现场可编程器件.1-2 与软件描述语言相比,VHDL有什么特点?P4~6答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。

综合器将VHDL程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性.综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计.l—3 什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么?P6什么是综合?答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

有哪些类型? 答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合.(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。

EDA第三次作业

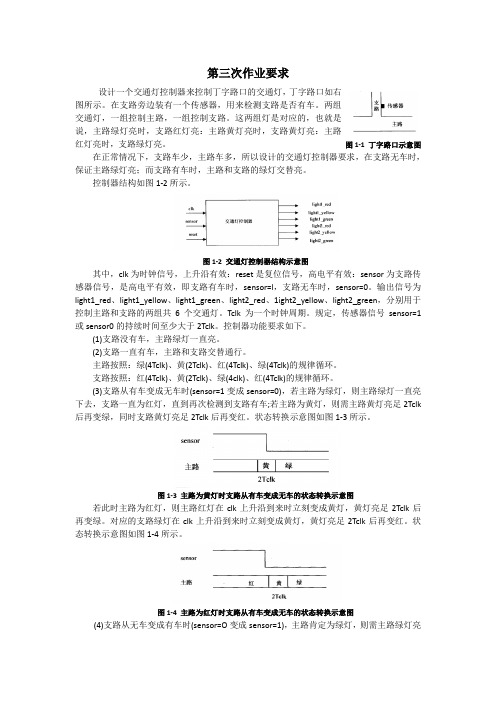

第三次作业要求设计一个交通灯控制器来控制丁字路口的交通灯,丁字路口如右图所示。

在支路旁边装有一个传感器,用来检测支路是否有车。

两组交通灯,一组控制主路,一组控制支路。

这两组灯是对应的,也就是说,主路绿灯亮时,支路红灯亮:主路黄灯亮时,支路黄灯亮:主路红灯亮时,支路绿灯亮。

图1-1 丁字路口示意图在正常情况下,支路车少,主路车多,所以设计的交通灯控制器要求,在支路无车时,保证主路绿灯亮;而支路有车时,主路和支路的绿灯交替亮。

控制器结构如图1-2所示。

图1-2 交通灯控制器结构示意图其中,clk为时钟信号,上升沿有效:reset是复位信号,高电平有效:sensor为支路传感器信号,是高电平有效,即支路有车时,sensor=l,支路无车时,sensor=0。

输出信号为light1_red、light1_yellow、light1_green、light2_red、1ight2_yellow、light2_green,分别用于控制主路和支路的两组共6个交通灯。

Tclk为一个时钟周期。

规定,传感器信号sensor=1或sensor0的持续时间至少大于2Tclk。

控制器功能要求如下。

(1)支路没有车,主路绿灯一直亮。

(2)支路一直有车,主路和支路交替通行。

主路按照:绿(4Tclk)、黄(2Tclk)、红(4Tclk)、绿(4Tclk)的规律循环。

支路按照:红(4Tclk)、黄(2Tclk)、绿(4clk)、红(4Tclk)的规律循环。

(3)支路从有车变成无车时(sensor=1变成sensor=0),若主路为绿灯,则主路绿灯一直亮下去,支路一直为红灯,直到再次检测到支路有车;若主路为黄灯,则需主路黄灯亮足2Tclk 后再变绿,同时支路黄灯亮足2Tclk后再变红。

状态转换示意图如图1-3所示。

图1-3 主路为黄灯时支路从有车变成无车的状态转换示意图若此时主路为红灯,则主路红灯在clk上升沿到来时立刻变成黄灯,黄灯亮足2Tclk后再变绿。

EDA实验试题16.6(附答案)

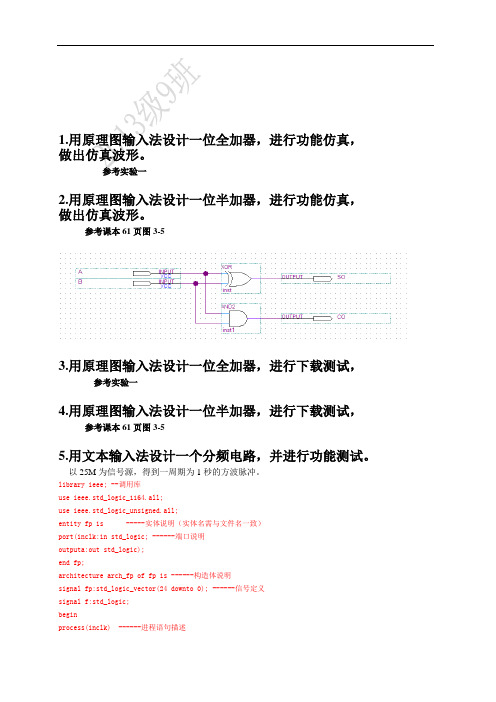

1.用原理图输入法设计一位全加器,进行功能仿真,做出仿真波形。

参考实验一2.用原理图输入法设计一位半加器,进行功能仿真,做出仿真波形。

参考课本61页图3-53.用原理图输入法设计一位全加器,进行下载测试,参考实验一4.用原理图输入法设计一位半加器,进行下载测试,参考课本61页图3-55.用文本输入法设计一个分频电路,并进行功能测试。

以25M为信号源,得到一周期为1秒的方波脉冲。

library ieee; --调用库use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity fp is -----实体说明(实体名需与文件名一致)port(inclk:in std_logic; ------端口说明outputa:out std_logic);end fp;architecture arch_fp of fp is ------构造体说明signal fp:std_logic_vector(24 downto 0); ------信号定义signal f:std_logic;beginprocess(inclk) ------进程语句描述if (inclk'event and inclk='1') then ------将时钟分频至1Hzif fp=24999999 thenfp<="0000000000000000000000000";f<=not f;else fp<=fp+1;end if;end if;end process;outputa<=f;end arch_fp; -------构造体结束6.用文本输入法设计一个分频电路,并进行功能测试。

以25M为信号源,得到一周期为2秒的方波脉冲。

library ieee; --调用库use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity fp is -----实体说明(实体名需与文件名一致)port(inclk:in std_logic; ------端口说明outputa:out std_logic);end fp;architecture arch_fp of fp is ------构造体说明signal fp:std_logic_vector(24 downto 0); ------信号定义signal f:std_logic;beginprocess(inclk) ------进程语句描述beginif (inclk'event and inclk='1') then ------将时钟分频至1Hzif fp=124999999 thenfp<="0000000000000000000000000";f<=not f;else fp<=fp+1;end if;end if;end process;outputa<=f;end arch_fp; -------构造体结束7.用文本输入法设计一个50倍分频电路,进行功能仿真。

青岛理工大学protel零件封装

针对青岛理工大学学生实验室实习常用的电子元器件protel工具作图实现的封装信息汇总青岛理工大学建校于1953年,是一所以工为主,理工结合,土木建筑,机械制造、环境能源学科特色鲜明,理、工、经、管、文、法多学科协调发展,科学教育与人文教育相结合的多科性大学,1993年被批准为硕士学位授予单位,2005年被批准为博士学位授予单位。

青岛理工大学(Qingdao T echnological University)是一所以工为主、理工结合的省属重点大学,本部坐落于美丽的海滨城市青岛。

前身是礼贤书院成立于1931年的高级工程科。

其土木建筑、机械制造、环境能源学科特色鲜明,理工经管文法多学科协调发展的多科性大学。

青岛理工大学是山东省最早设立土木专业的学校。

国家“卓越工程师教育培养计划”高校。

建校以来,学校构筑起本专科、硕士、博士人才培养体系,学校设有18个教学院部,拥有59个本科专业;1个一级学科博士点,7个二级学科博士点,2个一级学科博士后科研流动站;18个硕士学位授权一级学科、59个二级学科硕士点、11个硕士专业学位培养领域(包括资产评估硕士、工程硕士、会计硕士3种硕士专业学位),9个工程硕士专业学位培养领域、16个同等学力申请硕士学位专业;研究生教育涵盖了工学,理学,管理学,经济学,法学,文学,艺术学七大学科门类,在19个一级学科内培养博士和硕士研究生。

为社会培养了9万多名科学工程技术和管理方面的高级人才。

高级工程科1931年青岛著名建筑设计师刘铨法在礼贤中学(原礼贤书院)成立高级工程科(后改称土木工程科)。

招收初中毕业生,学制3年,相当于中等专业学校。

工程科课程除国语、英语、物理、化学等课程外,还开有房屋工程学、测量学、力学、机械原理、工程绘图等课程。

抗日战争胜利以后,工程科招收两个班,报考生源踊跃,又培育出众多人才。

礼贤中学向教育部申报,呈请成立青岛礼贤土木工程专科学校(大专),原普通中学(今青岛九中)作为附属中学。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EDA上机实验报告

实验1:T触发器

一、实验目的

1、认识T触发器。

2、掌握T触发器的逻辑功能和动作特点。

3、利用VHDL软件实现具有T触发器的数字电路。

二、实验原理

设计的是一个不带置位的T触发器,数据输入端为t,时钟输入端为clk,两个反相的输出端a,b。

当t=0时,T触发器保持前一状态的值;

当t=1时,T触发器状态在时钟边沿(上升沿)的作用下发生翻转。

三、程序及仿真图

library ieee;

use ieee.std_logic_1164.all;

entity T is

port(t, clk: in std_logic;

a: out std_logic;

b: out std_logic);

end T;

architecture Behavioral of T is

signal buf: std_logic:= '0';

begin

process(clk)

begin

if clk' event and clk = '1' then

if(t ='1') then

buf <= not buf;

else

buf <= buf;

end if;

end if;

end process;

a <= buf;

b <= not buf;

end Behavioral;

信号t的设置:

参数设置:

仿真图:

四.实验遇到的难点以及解决方法

开始输入程序的时候,综合总是显示正确,但是无法仿真成功,究其原因是没有对信号buf赋初值。

在程序综合的时候,信号的初

值不是必须的,综合时初值是被忽略的,如果没有给信号buf赋初值,可成功综合但不能成功仿真,一定要注意这一点。

实验2函数发生器

一、实验原理及方法

脉冲发生器就是要产生一个脉冲波形,而可控脉冲发生器则是

要产生一个周期和占空比可变的脉冲波形。

可控脉冲发生器的

实现原理比较简单,可以简单的理解为一个计数器对输入的时

钟信号进行分频的过程。

通过改变计数器的上线来达到改变周

期的目的,通过改变电平翻转的阀值来达到改变占空比的目的。

二、VHDL实现

1、程序实现过程:

entity hanshu is

port(clk, reset: in std_logic;

q: out std_logic_vector(7 downto 0));

end hanshu;

architecture a of hanshu is

begin

process(clk,reset)

variable tmp: std_logic_vector(7 downto 0); variable a: std_logic;

begin

if reset = '0' then

tmp:= "00000000";

elsif rising_edge(clk) then

if a = '0' then

if tmp = "11111111" then

tmp:= "11111110";

a:= '1';

else

tmp:= tmp + 1;

end if;

else

if tmp = "00000000" then

tmp:= "00000001";

a:= '0';

else

tmp:= tmp - 1;

end if;

end if;

end if;

q<=tmp; end process;

end a;

2 参数设置

3 波形设置

4仿真图

三、实验总结

通过本次试验,自己参考课本加上自己的理解,完成了T触发器和三角函数发生器的原理设计和仿真。

一开始只是自己在瞎弄,后来通过老师和同学们的讲解我终于明白了。

从整体上对仿真有了深刻的了解,特别是对VHDL语言,掌握了EDA设计方法。

在仿真函数的过程中,慢慢掌握了ISE10.1开发软件的使用。

不过在最开始

的时候,程序对参数的设置,确实是费了不少时间。

但是觉得还是非常值得的。