74ls20真值表管脚功能电路图

数字电路实验报告

数字电路实验报告姓名:张珂班级:10级8班学号:2010302540224实验一:组合逻辑电路分析一.实验用集成电路引脚图1.74LS00集成电路2.74LS20集成电路二、实验内容1、组合逻辑电路分析逻辑原理图如下:U1A 74LS00NU2B74LS00NU3C74LS00N X12.5 VJ1Key = Space J2Key = Space J3Key = Space J4Key = SpaceVCC5VGND图1.1组合逻辑电路分析电路图说明:ABCD 按逻辑开关“1”表示高电平,“0”表示低电平; 逻辑指示灯:灯亮表示“1”,灯不亮表示“0”。

真值表如下: A B C D Y 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 1 0 1 0 0 0 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1 0 0 0 0 1 0 0 1 0 1 0 1 0 0 1 0 1 1 1 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 1表1.1 组合逻辑电路分析真值表实验分析:由实验逻辑电路图可知:输出X1=AB CD =AB+CD ,同样,由真值表也能推出此方程,说明此逻辑电路具有与或功能。

2、密码锁问题:密码锁的开锁条件是:拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时,开锁信号为“1”,将锁打开;否则,报警信号为“1”,则接通警铃。

试分析下图中密码锁的密码ABCD 是什么? 密码锁逻辑原理图如下:U1A74LS00NU2B74LS00NU3C 74LS00NU4D 74LS00NU5D 74LS00NU6A74LS00N U7A74LS00NU8A74LS20D GNDVCC5VJ1Key = SpaceJ2Key = SpaceJ3Key = SpaceJ4Key = SpaceVCC5VX12.5 VX22.5 V图 2 密码锁电路分析实验真值表记录如下:实验真值表 A B CD X1 X2 0 0 0 0 0 1 0 0 0 1 0 1 0 0 1 0 0 1 0 0 1 1 0 1 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 1 0 1 1 0 0 0 0 1 1 0 0 1 1 0 1 0 1 0 0 1 1 0 1 1 0 1 1 1 0 0 0 1 1 1 0 1 0 1 1 1 1 0 0 1 1 11 10 1表1.2 密码锁电路分析真值表实验分析:由真值表(表1.2)可知:当ABCD 为1001时,灯X1亮,灯X2灭;其他情况下,灯X1灭,灯X2亮。

TTL集成逻辑门的逻辑功能与参数测试

数字电子技术实验报告(大数据学院)实验名称:TTL集成逻辑门的逻辑功能与参数测试专业班级:学生姓名:学生学号:指导教师:实验地点: 2320 实验日期: 2019.12.7 实验组成员姓名:贵州理工学院实验报告实验项目名称TTL集成逻辑门的逻辑功能与参数测试实验目的1、掌握TTL集成与非门的逻辑功能和主要参数的测试方法2、掌握TTL器件的使用规则3、进一步熟悉数字电路实验装置的结构,基本功能和使用方法实验原理本实验采用四输入双与非门74LS20,即在一块集成块内含有两个互相独立的与非门,每个与非门有四个输入端。

其逻辑框图、符号及引脚排列如图1-1(a)、(b)、(c)所示。

1、与非门的逻辑功能与非门的逻辑功能是:当输入端中有一个或一个以上是低电平时,输出端为高电平;只有当输入端全部为高电平时,输出端才是低电平(即有“0”得“1”,全“1”得“0”。

)其逻辑表达式为 Y=(b)(a) (c)图1-1 74LS20逻辑框图、逻辑符号及引脚排列2、TTL与非门的主要参数(1)低电平输出电源电流I CCL和高电平输出电源电流I CCH与非门处于不同的工作状态,电源提供的电流是不同的。

I CCL是指所有输入端悬空,输出端空载时,电源提供器件的电流。

I CCH是指输出端空截,每个门各有一个以上的输入端接地,其余输入端悬空,电源提供给器件的电流。

通常I CCL>I CCH,它们的大小标志着器件静态功耗的大小。

器件的最大功耗为P CCL=V CC I CCL。

手册中提供的电源电流和功耗值是指整个器件总的电源电流和总的功耗。

I CCL和I CCH测试电路如图1-2(a)、(b)所示。

[注意]:TTL电路对电源电压要求较严,电源电压V CC只允许在+5V±10%的范围内工作,超过5.5V 将损坏器件;低于4.5V 器件的逻辑功能将不正常。

(a) (b) (c) (d) 图1-2 TTL 与非门静态参数测试电路图(2)低电平输入电流I iL 和高电平输入电流I iH 。

74系列芯片引脚图

类别 电路简称 四位比较器 74LS85

A3 B3

数据输入 A2 B2 A1 B1

真值表 A0 B0

级联输入

输出

A>B A<B A=B A>B A<B A=B

A3>B3 A3<B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3

GND 8

7744LLSS17124

16 Vcc 15 1CLR 14 2CLR 13 2CK 12 2K 11 2J 10 2PR 9 2Q

(a) JK 触发器 74112 引脚图

Y0 1

Y1 2

Y2 3 Y3 4 Y4 5 Y5 6 Y6 7 GND 8

7474LLSS7442

16 Vcc

15 A0 14 A1

13 A2 12 A3 11 Y9 10 Y8 9 Y7

图 3.2 74LS42 引脚图

74LS04

B1

C2

LT 3 BI/RBO 4

RBI 5 D6 A7

GND 8

747L4LSS7448

16 Vcc 15 f 14 g

13 a 12 b 11 c 10 d 9e

图 3.3 74LS48 引脚图

常用 74 系列 TTL 集成电路

真值表

时钟 CP J K

X

XX

X

XX

↓

00

↓

10

↓

01

↓

11

输出 清零(Q=0) 置 1(Q=1) 保持(Q=Qn)

Q=1 Q=0 翻转(Q=/Q)

电路引脚图

类别

电路简 称

基本门电路逻辑功能的测试数电实验报告

实验一:TTL集成逻辑门的逻辑功能与参数测试一、实验目的1、掌握TTL集成与非门的逻辑功能和主要参数的测试方法2、掌握TTL器件的使用规则3、进一步熟悉数字电路实验装置的结构,基本功能和使用方法二、实验原理本实验采用四输入双与非门74LS20,即在一块集成块内含有两个互相独立的与非门,每个与非门有四个输入端。

其逻辑框图、符号及引脚排列如图2-1(a)、(b)、(c)所示。

(b)(a) (c)图2-1 74LS20逻辑框图、逻辑符号及引脚排列1、与非门的逻辑功能与非门的逻辑功能是:当输入端中有一个或一个以上是低电平时,输出端为高电平;只有当输入端全部为高电平时,输出端才是低电平(即有“0”得“1”,全“1”得“0”。

)其逻辑表达式为 Y=2、TTL与非门的主要参数(1)低电平输出电源电流ICCL 和高电平输出电源电流ICCH与非门处于不同的工作状态,电源提供的电流是不同的。

ICCL是指所有输入端悬空,输出端空载时,电源提供器件的电流。

ICCH是指输出端空截,每个门各有一个以上的输入端接地,其余输入端悬空,电源提供给器件的电流。

通常I CCL >I CCH ,它们的大小标志着器件静态功耗的大小。

器件的最大功耗为P CCL =V CC I CCL 。

手册中提供的电源电流和功耗值是指整个器件总的电源电流和总的功耗。

I CCL 和I CCH 测试电路如图2-2(a)、(b)所示。

[注意]:TTL 电路对电源电压要求较严,电源电压V CC 只允许在+5V ±10%的范围内工作,超过5.5V 将损坏器件;低于4.5V 器件的逻辑功能将不正常。

(a) (b) (c) (d)图2-2 TTL 与非门静态参数测试电路图(2)低电平输入电流I iL 和高电平输入电流I iH 。

I iL 是指被测输入端接地,其余输入端悬空,输出端空载时,由被测输入端流出的电流值。

在多级门电路中,I iL 相当于前级门输出低电平时,后级向前级门灌入的电流,因此它关系到前级门的灌电流负载能力,即直接影响前级门电路带负载的个数,因此希望I iL 小些。

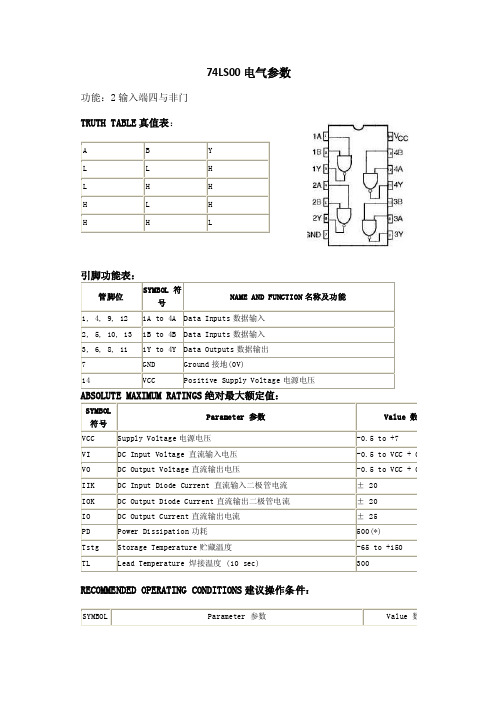

74LS00电气参数

- - 1.8 - 1.8 - 1.8

2.0

1.9 2.0 - 1.9 - 1.9 -

4.5 IO=-20μ A

High Level Output

VOH

6.0

Voltage 输出高电平电压

4.5 IO=-4.0mA

4.4 4.5 - 4.4 - 4.4 5.9 6.0 - 5.9 - 5.9 - V 4.18 4.31 - 4.13 - 4.10 -

74LS00 电气参数

功能:2 输入端四与非门 TRUTH TABLE 真值表:

A

B

Y

L

L

H

L

H

H

H

L

H

H

H

L

引脚功能表:

管 脚位

SYMBOL 符 号

NAME AND FUNCTION 名称及功能

1, 4, 9, 12 1A to 4A Data Inputs 数据输入

2, 5, 10, 13 1B to 4B Data Inputs 数据输入

VIH

2.0

4.5 -

Voltage 输入高电平电压 6.0

1.5 - - 1.5 - 1.5 3.15 - - 3.15 - 3.15 - V 4.2 - - 4.2 - 4.2 -

Low Level Input-

2.0

VIL

4.5 -

Voltage 输入低电平电压 6.0

- - 0.5 - 0.5 - 0.5 - - 1.35 - 1.35 - 1.35

VI

DC Input Voltage 直流输入电压

VO

DC Output Voltage 直流输出电压

IIK

四路抢答器课程设计报告 用到的芯片有74LS20和74LS20

电子科学系电子信息科学与技术课程设计报告课题题目:四路智能抢答器一、课程设计目的本次课程设计主要是配合《模拟电子技术》和《数字电子技术》理论课程而设置的一门实践性课程,起到巩固所学知识,加强综合能力,培养电路设计能力,提高实验技术,启发创新思想的效果。

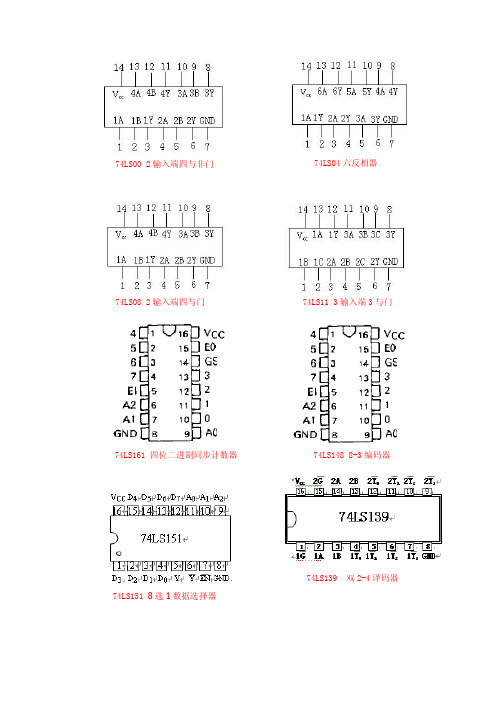

二、初始条件:本课程设计,要求用集成电路:74LSl48,74LS192,74LS175,74LS160,74LS00,74LS04,74LS20,74LS48,74LS32,555定时器和其它器件等,实现四路定时抢答功能。

三、要求完成的主要任务:1、可同时供4名选手(或代表队)参赛,其编号分别是1到4,各用一个抢答按钮,按钮的编号与选手的编号相对应。

给节目主持人设置一个控制开关,用来控制系统的清零(编号显示数码管灭灯)和抢答的开始。

2、抢答器具有数据锁存和显示的功能。

抢答开始后,若有选手按动抢答按钮,编号立即锁存,并数码管上显示选手的编号,同时扬声器给出声音提示;同时封锁输入电路,禁止其它选手抢答。

3、抢答器具有定时抢答的功能,且一次抢答的时间为10秒。

当主持人启动“开始”键后,要求定时器立即进行加计时,并用显示器显示。

4、参赛选手在设定的时间内进行抢答,抢答有效,定时器停止工作,显示器上显示选手的编号和抢答时刻的时间,并保持到主持人将系统清零为止;如果定时抢答的时间已到,而没有选手抢答时,并封锁输入电路,禁止选手超时后抢答,定时显示器上显示0。

目录1 功能介绍 (3)1.1主要功能介绍 (3)1.2扩展功能介绍 (3)2总体方案设计.................................................. (3)3单元模块设计.................................................. (4)3.1抢答器控制端电路功能介绍 (4)3.2定时时间电路 (5)3.3控制电路和报警电路 (5)3.4振荡电路 (6)4主要芯片介绍 (7)4.1 优先编码器74LS148 (7)4.2 计数器74LS192 (8)5四人抢答器仿真.............................................. (9)6系统调试...................................................... (9)7参考文献 (11)1功能介绍1.1主要功能介绍(1)抢答器最多可供4名选手参赛,编号为1~4号,各队分别用一个按钮(分别为J1、J2、J3、J5)控制,并设置一个系统清零和抢答控制开关J4,J7,该开关由主持人控制。

实验一实验常用门电路逻辑功能测试

实验名称:常用门电路逻辑功能测试

一、实验目的:

1、熟悉试验环境、学会识别常用芯片的引脚分配。

2、掌握逻辑门逻辑功能的测试方法。

3、掌握简单组合电路的设计。

二、实验内容:

1.测试实验室常用数字逻辑芯片的逻辑功能:74LS00 74LS02 74LS04

74LS08 74LS20 74LS32 74LS86(预习时查出每个芯片的功能、内部结构以及管脚分配)

2、应用与非门74LS00实现以下逻辑:

①:F=ABC ②:F=ABC③:F=A+B ④:F=A B+A B

三、实验内容步骤:

(学生根据自己实验情况简要总结步骤和内容,主要包括:

1、实验原理图;如:

2、实验真值表;

3、实验结果记录。

如:

输入输出

A B F3

0 0 灭

0 1 亮

1 0 亮

1 1 亮

四、实验总结

(学生根据自己实验情况,简要总结实验中遇到的问题及其解决办法)

注:本实验室提供的数字集成芯片有:

74ls00,74ls02,74ls04,74ls08,74ls20,74ls32,74ls74,74ls90,74ls112,74ls138,

74ls153,74ls161 F=A+B=A B•=11

⋅•⋅

A B。

实验一-基本逻辑门电路实验

二 、 TTL、HC器件的电压传输特性

2.输出无负载时74LS00、74HC00电压传输特性测试数据

输入Vi(V)

0.0 0.2 … 1.2 1.4 … 4.8 5.0

74LS00

输出Vo

74HC00

二 、 TTL、HC和HCT器件的电压传输特性

3.输出无负载时74LS00、74HC00和 74HCT00电压传

互连规则与约束

TTL、CMOS器件的互连: 器件的互连总则

在电子产品的某些单板上,有时需要在某些逻辑电平的器件之间进行互连。 在不同逻辑电平器件之间进行互连时主要考虑以下几点: 1:电平关系,必须保证在各自的电平范围内工作,否则,不能满足正常逻辑 功能,严重时会烧毁芯片。 2:驱动能力,必须根据器件的特性参数仔细考虑,计算和试验,否则很可能 造成隐患,在电源波动,受到干扰时系统就会崩溃。 3:时延特性,在高速信号进行逻辑电平转换时,会带来较大的延时,设计时 一定要充分考虑其容限。 4:选用电平转换逻辑芯片时应慎重考虑,反复对比。通常逻辑电平转换芯片 为通用转换芯片,可靠性高,设计方便,简化了电路,但对于具体的设计电 路一定要考虑以上三种情况,合理选用。 对于数字电路来说,各种器件所需的输入电流、输出驱动电流不同,为了驱 动大电流器件、远距离传输、同时驱动多个器件,都需要审查电流驱动能力: 输出电流应大于负载所需输入电流;另一方面,TTL、CMOS、ECL等输入、输 出电平标准不一致,同时采用上述多种器件时应考虑电平之间的转换问题。

五、 不同逻辑电平接口转换及其应用

1.TTL与CMOS 2.CMOS与TTL 2.TTL与LVTTL 3.TTL与LVCMOS 4.LVTTL与TTL 5LVTTL与CMOS 5.LVCMOS与TTL 6.LVCMOS与CMOS 7.TTL/CMOS与ECL 8. LVTTL/LVCMOS与LVECL 9.其它

数字逻辑实验 门电路组合逻辑设计

VCC

&

:

&

GND

1 23 45 6 7

图1-1 74LS20逻辑框图、逻辑符号及引脚排列

1、与非门的逻辑功能 与非门的逻辑功能为:当输入端中有一个或一个以上是低电平时,输出 端为高电平;只有当输入端全部为高电平时,输出端才是低电平。

逻辑表达式为: Y=ABCD

2.与非门的逻辑功能测试 1)逻辑电路及74LS20芯片逻辑功能测试的连接方法如图1-3所示。

一、实验目的

1、掌握中规模集成芯片数据选择器和译码器的逻辑功能和使 用方法

2、熟悉组合功能器件的应用

二、实验原理

1、数据选择器 数据选择器又叫多路选择器或多路开关,它是多输入,单输

出的组合逻辑电路。由地址码控制器多个数据通道。实现单 个通道数据输出,还可以实现数据传输与并串转换等多种功 能。 它基本是由三部分组成:数据选择控制(或称地址输入)、 数据输入电路和数据输出电路,它的种类多样有原码形式输 出、反码形式输出,现以74LS153为例进行应用设计。

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 01111111 10111111 11011111 11101111 11110111 11111011 11111101 11111110 11111111 11111111

SY70

VCC Y0 Y1 Y2 Y3 Y4 Y5 Y6

YS1357026432

E

1

0

A B F1 F2

F2 = ABE = ABE

南北 东西 3、电路图:

╳╳ 0 0 A 0010

B

&

&&

& F1

0 0 1 0 1 E

数字电子技术实验指导书

实验一:TTL集成逻辑门的逻辑功能与参数测试一、实验目的1、掌握TTL集成与非门的逻辑功能和主要参数的测试方法2、掌握TTL器件的使用规则3、进一步熟悉数字电路实验装置的结构,基本功能和使用方法二、实验原理本实验采用四输入双与非门74LS20,即在一块集成块内含有两个互相独立的与非门,每个与非门有四个输入端。

其逻辑框图、符号及引脚排列如图2-1(a)、(b)、(c)所示。

(b)(a) (c)图2-1 74LS20逻辑框图、逻辑符号及引脚排列1、与非门的逻辑功能与非门的逻辑功能是:当输入端中有一个或一个以上是低电平时,输出端为高电平;只有当输入端全部为高电平时,输出端才是低电平(即有“0”得“1”,全“1”得“0”。

)其逻辑表达式为 Y=2、TTL与非门的主要参数(1)低电平输出电源电流ICCL 和高电平输出电源电流ICCH与非门处于不同的工作状态,电源提供的电流是不同的。

ICCL是指所有输入端悬空,输出端空载时,电源提供器件的电流。

ICCH是指输出端空截,每个门各有一个以上的输入端接地,其余输入端悬空,电源提供给器件的电流。

通常ICCL>I CCH ,它们的大小标志着器件静态功耗的大小。

器件的最大功耗为P CCL =V CC I CCL 。

手册中提供的电源电流和功耗值是指整个器件总的电源电流和总的功耗。

I CCL 和I CCH 测试电路如图2-2(a)、(b)所示。

[注意]:TTL 电路对电源电压要求较严,电源电压V CC 只允许在+5V ±10%的范围内工作,超过5.5V 将损坏器件;低于4.5V 器件的逻辑功能将不正常。

(a) (b) (c) (d)图2-2 TTL 与非门静态参数测试电路图(2)低电平输入电流I iL 和高电平输入电流I iH 。

I iL 是指被测输入端接地,其余输入端悬空,输出端空载时,由被测输入端流出的电流值。

在多级门电路中,I iL 相当于前级门输出低电平时,后级向前级门灌入的电流,因此它关系到前级门的灌电流负载能力,即直接影响前级门电路带负载的个数,因此希望I iL 小些。