DDR4设计概述以及分析仿真案例

DRAM信号主要参数及仿真应用-2017.5

该电阻如果在几个DRAM中共用,各芯片校验时不能产生命令冲突,且该引脚

总的容性负载不能超过5.2pf;

多媒体研发中心

11/40

ZQ calibration

1.目前用的32G+3GB 存储器;内部包含了4个位宽为16bit的DRAM,组成两个RANK, 连接两个ZQ引脚用于校验 。 2.16GB+2GB的存储器;由2个die,各32bit位宽的DRAM组成,,搭配一个ZQ 电阻。 另外目前三星16+2 (KMR820001M-B609)也是四个die封装,需要连接两个Rzq。

多媒体研发中心

27/40

IBIS 模型

•Output模型主要的电气参数: 1. Power clamp & GND clamp :钳位二极管特性 2. Pull up & Pull down: 上拉下拉I/V特性曲线,驱动力 3. Rise time & Fall time :上升沿下降沿的时间特性 4. Ramp : dv/dt,slew rate 5. 半导体芯片电容C_comp,封装寄生LCR参数 6. 时序测试参数 • Vmeas:输出电压测量参考值 • Rref:测试电路的负载电阻 • Cref:测试电路的负载电容 • Vref:测试电路的负载参考电压

支走线的数量和他们的长度,但是却会导致时钟和strobe信号在每个芯片上的无法

同步,这使得控制器很难以保持Tdqss ,tdss和tdsh这些时序。DDR3通过write leveling特性,来调整CLK和DQS之间的时间差。存储器控制器可以调整DQS信号

的时延,来与时钟信号的上升沿对齐。控制器不停对DQS进行延时,直到发现时钟

多媒体研发中心

25/40

DDR4设计概述以及分析仿真案例.pdf

DRAM (动态随机访问存储器)对设计人员特别具有吸引力,因为它提供了广泛的性能,用于各种计算机和嵌入式系统的存储系统设计中。

本文概括阐述了DRAM 的概念,及介绍了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、DDR5 SDRAM、LPDDR、GDDR。

DRAMDRAM较其它内存类型的一个优势是它能够以IC(集成电路)上每个内存单元更少的电路实现。

DRAM 的内存单元基于电容器上贮存的电荷。

典型的DRAM 单元使用一个电容器及一个或三个FET(场效应晶体管)制成。

典型的SRAM (静态随机访问内存)内存单元采取六个FET 器件,降低了相同尺寸时每个IC 的内存单元数量。

与DRAM 相比,SRAM 使用起来更简便,接口更容易,数据访问时间更快。

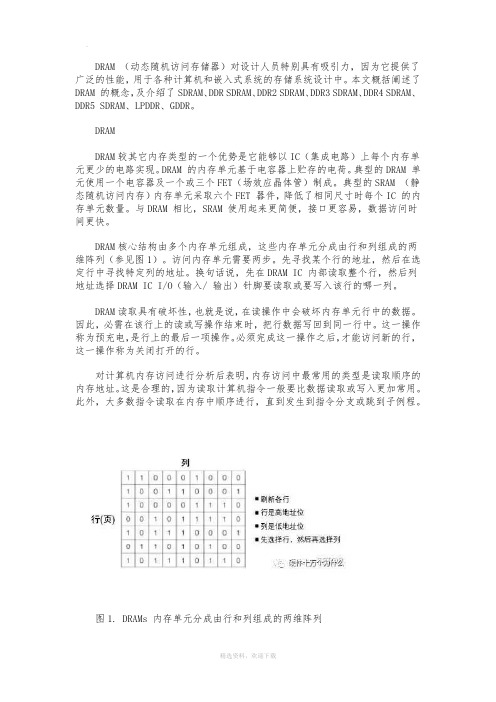

DRAM核心结构由多个内存单元组成,这些内存单元分成由行和列组成的两维阵列(参见图1)。

访问内存单元需要两步。

先寻找某个行的地址,然后在选定行中寻找特定列的地址。

换句话说,先在DRAM IC 内部读取整个行,然后列地址选择DRAM IC I/O(输入/ 输出)针脚要读取或要写入该行的哪一列。

DRAM读取具有破坏性,也就是说,在读操作中会破坏内存单元行中的数据。

因此,必需在该行上的读或写操作结束时,把行数据写回到同一行中。

这一操作称为预充电,是行上的最后一项操作。

必须完成这一操作之后,才能访问新的行,这一操作称为关闭打开的行。

对计算机内存访问进行分析后表明,内存访问中最常用的类型是读取顺序的内存地址。

这是合理的,因为读取计算机指令一般要比数据读取或写入更加常用。

此外,大多数指令读取在内存中顺序进行,直到发生到指令分支或跳到子例程。

图1. DRAMs 内存单元分成由行和列组成的两维阵列DRAM的一个行称为内存页面,一旦打开行,您可以访问该行中多个顺序的或不同的列地址。

这提高了内存访问速度,降低了内存时延,因为在访问同一个内存页面中的内存单元时,其不必把行地址重新发送给DRAM.结果,行地址是计算机的高阶地址位,列地址是低阶地址位。

王小玲_DDR4存储器关键技术分析

DDR4存储器关键技术分析王小玲(东南大学无锡分校,江苏无锡,214135)摘要:随着DDR4 SDRAM内存技术标准的发布,其在内存领域将会引起越来越多的关注,因此对DDR4内存进行深入分析很有必要。

本文从计算机硬件技术分析的角度,结合与DDR3的比较,对DDR4内存的关键技术进行了初步系统的分析。

关键字:DDR4;DDR3;高速率;低功耗;技术分析Analysis of DDR4 SDRAM’s essential technologyWang Xiaoling1, Li Bing2(1. Wuxi Branch of Southeast University, Wuxi Jiangsu, 214135;2. School of Integrated Circuits, Southeast University, Nanjing Jiangsu, 210096)Abstract:With the publication of DDR4 SDRAM memory technology standard, it will attract more and more attentions in the field of memory. So it is necessary to make in-depth analysis of DDR4 memory. From the perspective of computer hardware technology analysis, combined with the comparison with DDR3, this article analyzes the key technologies of DDR4 memory preliminarily.Key words:DDR4; DDR3; High data rate; Low power consumption; Technical analysis在无数的电子产品发展中,从电脑到游戏机到电视再到通讯设备,半导体存储器都发挥着重要的作用。

ddr4芯片

ddr4芯片DDR4 芯片的介绍DDR4(Double Data Rate 4)是一种高性能存储器标准,用于计算机和服务器的内存模块。

与前一代标准DDR3相比,DDR4在带宽、功耗和时钟频率等方面都有所提升。

首先,DDR4芯片具有较高的带宽。

DDR4的数据速率比DDR3快得多,能够以更高的频率读写数据。

例如,DDR4-3200的标准频率比DDR3-2133高大约50%。

这种高带宽对于处理大量数据的应用非常重要,例如高清视频编辑和3D渲染。

其次,DDR4芯片具有更低的功耗。

由于技术升级和结构优化的原因,DDR4比DDR3能够以较低的电压工作。

DDR3的工作电压通常为1.5伏特,而DDR4的工作电压可以降低到1.2伏特。

这不仅有助于节省能源,还有助于减少发热量,提高整个系统的稳定性。

再次,DDR4芯片能够支持更高的时钟频率。

时钟频率是指内存芯片的工作速度,通常以MHz为单位。

DDR4标准规定了多个频率等级,从2133MHz到3200MHz不等。

较高的时钟频率意味着数据传输速度更快,从而提高了整个系统的响应速度。

此外,DDR4还支持更大的内存容量。

DDR4芯片的设计使得内存模块可以容纳更多的存储单元,从而提供更大的存储容量。

目前,DDR4内存模块的容量范围从4GB到128GB不等。

这对于需要处理大型数据库和运行内存密集型应用的服务器来说非常重要。

最后,DDR4芯片还引入了一些新的技术和功能以提高系统性能和稳定性。

例如,DDR4使用了一种叫做“冗余位校验(ECC)”的技术,用于检测和纠正内存错误。

这可以提高系统的可靠性,防止数据丢失和系统崩溃。

总结起来,DDR4芯片作为一种高性能内存标准,具有高带宽、低功耗、高时钟频率、大内存容量和更强的稳定性等优势。

它适用于各种需求高性能的应用场景,包括游戏、影像处理、虚拟现实和数据中心等。

作为技术的不断进步,DDR4芯片在未来可能会有更广泛的应用和更大的发展空间。

DDR4设计概述以和分析仿真案例

DDR4设计概述以和分析仿真案例DDR4(Double Data Rate 4)是一种主要用于计算机内存的新一代随机存取存储器(RAM)标准。

它是DDR3的后继版本,提供了更快的数据传输速度和更高的带宽。

DDR4的设计目标是提高内存模块的容量和速度,并减少功耗。

与DDR3相比,DDR4内存模块的最大容量大幅增加,可达到128GB,同时传输速度更快,频率从DDR3的最高频率1600MHz提高到DDR4的最高频率3200MHz。

此外,DDR4采用了较低的电压,从DDR3的1.5V降低到1.2V,这使得DDR4内存模块的功耗降低了约20%。

DDR4的设计还引入了一些新的技术和功能。

其中之一是内存排布(Memory Rank),DDR4内存模块通常具有两个或四个内存排布。

每个内存排布类似于一个内存芯片,可以独立地进行读写操作。

内存排布的增加可以增加内存模块的容量,并且可以并行化读写操作,从而提高内存的性能。

另一个最显著的新功能是错误校验和修正(ECC)功能,它可以检测和纠正内存中的错误。

ECC功能对于企业级服务器和高性能计算机等对数据准确性要求较高的应用非常重要。

为了实现DDR4的设计目标,设计师们进行了详细的仿真和验证工作。

下面将以一个DDR4的仿真案例为例来分析DDR4的设计过程。

在DDR4的仿真中,设计师首先需要定义各种电气参数,如信号传输延迟、电阻和电容等。

然后,使用设计工具对DDR4的电路图进行仿真,并对其性能进行评估。

在仿真过程中,设计师需要考虑多个因素来验证DDR4内存模块的性能。

首先,他们需要确保DDR4内存模块可以在指定的频率下正常工作,并且满足时序要求。

这包括检查读写信号的延迟,确认读写信号的时序是正确的,并且确保数据在正确的时间窗口内稳定。

其次,设计师还需要验证DDR4内存模块的稳定性和可靠性。

他们通过模拟不同的工作负载和应用场景来测试内存模块的性能,检查是否存在数据丢失、错误校验和修正是否正常工作等问题。

DDR4设计概述以及分析仿真案例

DRAM (动态随机访问存储器)对设计人员特别具有吸引力,因为它提供了广泛的性能,用于各种计算机和嵌入式系统的存储系统设计中。

本文概括阐述了DRAM 的概念,及介绍了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、DDR5 SDRAM、LPDDR、GDDR。

DRAMDRAM较其它内存类型的一个优势是它能够以IC(集成电路)上每个内存单元更少的电路实现。

DRAM 的内存单元基于电容器上贮存的电荷。

典型的DRAM 单元使用一个电容器及一个或三个FET(场效应晶体管)制成。

典型的SRAM (静态随机访问内存)内存单元采取六个FET 器件,降低了相同尺寸时每个IC 的内存单元数量。

与DRAM 相比,SRAM 使用起来更简便,接口更容易,数据访问时间更快。

DRAM核心结构由多个内存单元组成,这些内存单元分成由行和列组成的两维阵列(参见图1)。

访问内存单元需要两步。

先寻找某个行的地址,然后在选定行中寻找特定列的地址。

换句话说,先在DRAM IC 内部读取整个行,然后列地址选择DRAM IC I/O(输入/ 输出)针脚要读取或要写入该行的哪一列。

DRAM读取具有破坏性,也就是说,在读操作中会破坏内存单元行中的数据。

因此,必需在该行上的读或写操作结束时,把行数据写回到同一行中。

这一操作称为预充电,是行上的最后一项操作。

必须完成这一操作之后,才能访问新的行,这一操作称为关闭打开的行。

对计算机内存访问进行分析后表明,内存访问中最常用的类型是读取顺序的内存地址。

这是合理的,因为读取计算机指令一般要比数据读取或写入更加常用。

此外,大多数指令读取在内存中顺序进行,直到发生到指令分支或跳到子例程。

图1. DRAMs 内存单元分成由行和列组成的两维阵列DRAM的一个行称为内存页面,一旦打开行,您可以访问该行中多个顺序的或不同的列地址。

这提高了内存访问速度,降低了内存时延,因为在访问同一个内存页面中的内存单元时,其不必把行地址重新发送给DRAM.结果,行地址是计算机的高阶地址位,列地址是低阶地址位。

DDR4 电路及眼图分析讲解

DDR4电路及眼图分析讲解一、存储分类按在计算机系统中的作用不同,存储器主要分为主存储器、辅助存储器、缓冲存储器。

主存储器(简称主存):的主要特点是它可以和CPU直接交换信息。

辅助存储器(简称辅存):是主存储器的后援存储器,用来存放当前暂时不用的程序和数据,它不能与CPU直接交换信息。

两者相比,主存速度快、容量小、每位价格高;辅存速度慢、容量大、每位价格低。

缓冲存储器(简称缓存):用在两个速度不同的部件之中,例如,CPU与主存之间可设置一个快速缓存,起到缓冲作用。

其分类如下:二、DDR分类SDRAM(Synchronous Dynamic Random Access Memory):为同步动态随机存取内存,是有一个同步接口的动态随机存取内存(DRAM)。

其分类如下:DDR SDRAM(Double Data Rate SDRAM):为双信道同步动态随机存取内存,是新一代的SDRAM技术。

别于SDR(Single Data Rate)单一周期内只能读写1次,DDR的双倍数据传输率指的就是单一周期内可读取或写入2次。

在核心频率不变的情况下,传输效率为SDR SDRAM的2倍。

允许在时钟脉冲的上升沿和下降沿传输数据。

DDR内存Prefetch(数据读预取)为2bit。

DDR2 SDRAM(Double Data Rate Two SDRAM):为双信道两次同步动态随机存取内存。

它与上一代DDR内存技术标准最大的不同就是,虽然同是采用了在时钟的上升/下降沿同时进行数据传输的基本方式,但DDR2内存却拥有两倍以上一代DDR内存预读取能力(即:4bit数据读预取)。

换句话说,DDR2内存每个时钟能够以4倍外部总线的速度读/写数据,并且能够以内部控制总线4倍的速度运行。

在同等核心频率下,DDR2的实际工作频率是DDR的两倍。

这得益于DDR2内存拥有两倍于标准DDR内存的4BIT预读取能力。

DDR3 SDRAM(Double Data Rate Three SDRAM):为双信道三次同步动态随机存取内存。

DDR4设计概述以及分析仿真案例

DDR4设计概述以及分析仿真案例DDR4 (Double Data Rate 4)是一种主流的计算机内存技术,取代了DDR3成为目前最常用的内存标准。

DDR4设计在提高频率和带宽同时,还改善了能效和稳定性。

下面将从内存组织、设计特点、仿真案例等方面进行介绍。

DDR4内存设计起初是为了满足数据处理速度不断增加的需求。

相比DDR3内存,DDR4能够提供更高的频率和带宽。

它采用了更高的频率,可以从每个时钟周期传输更多的数据。

比如,DDR3-1600的效率为1600MT/s,而DDR4-3200的效率可达到3200MT/s。

这种提高带宽的方式对于高性能计算和大数据处理非常关键。

DDR4内存的设计特点:1. 增强的带宽:DDR4内存的每条通道可以支持更多数据的传输。

这是通过在每个时钟上升和下降时,传输两个比特数据来实现的,称为“double data rate”。

DDR4内存通常可以达到64倍的扩展,速度比DDR3内存快1.5倍。

2.降低能耗:DDR4内存的工作电压相对于DDR3内存降低了0.05V,这导致了能效的提高。

此外,DDR4还引入了低功耗模式,当内存处于空闲状态时可以进入更低的功耗状态。

3.提高稳定性:DDR4内存采用了更高的内部时钟频率,可以更好地处理不同内存芯片之间的时序不匹配问题。

此外,DDR4还引入了FIFO缓冲区,用于处理不同速度的操作和命令。

现在来看一个DDR4仿真案例,对高性能计算系统中的内存进行分析。

假设我们有一个系统,包含8块DDR4内存,每块内存有16个芯片,每个芯片有8个内存通道。

每个通道的速度为3200MT/s。

系统需要处理大量数据,因此内存带宽非常关键。

首先,我们可以使用仿真工具对整个系统进行建模和仿真。

通过设置参数和分析结果,我们可以确定每个内存通道的负载情况和总带宽。

我们可以调整负载分布,以便最大化系统的整体性能。

接下来,我们可以使用仿真工具来模拟不同工作载荷下的内存访问模式。

DDR4原理及硬件设计

DDR4原理及硬件设计DDR4(第四代双数据率同步动态随机存取存储器)是一种内存技术,是DDR(双数据率)内存的升级版本。

DDR4内存相较于DDR3内存,在带宽、速度和能效方面都有显著的提升。

下面将从原理和硬件设计两个方面进行详细介绍。

DDR4的原理:DDR4内存原理的核心是双数据率。

双数据率技术使得内存模块的读取和写入数据速度翻倍。

DDR4的数据线采用了数据悬空技术,也就是同时传输两个数据,这使得数据传输速率大大加快。

DDR4内存模块还采用了预取策略,能够预先将要读取的数据放入缓存,提高读取速度。

DDR4内存的硬件设计:1.存储芯片:DDR4内存模块中使用一系列DRAM芯片,这些芯片按照一定的规格和容量进行组织。

每个DRAM芯片内包含多个存储单元,每个存储单元可以存储一个位的数据。

2.数据总线:DDR4内存模块的数据总线是连接存储芯片和控制器的通信线路。

数据总线同时传输多位的数据,数据位数取决于内存模块的规格。

3.地址总线:DDR4内存模块的地址总线连接了存储芯片和内存控制器,用于寻址存储单元。

地址总线的位数决定了内存模块的容量。

4.控制信号:DDR4内存模块需要各种控制信号来指示存储芯片的操作,如读取数据、写入数据、预充电等。

控制信号由内存控制器产生,通过控制线路传递给存储芯片。

5.电源和地线:DDR4内存模块需要提供稳定的电源和地线供电,以保证内部电路的正常工作。

另外,内存模块还需要提供供电时钟和时钟控制信号。

6.PCB设计:DDR4内存模块的PCB设计需要考虑信号完整性和干扰抑制。

在设计过程中,需要合理布局和走线,减小信号传输的延迟和损耗,并采用合适的终端电阻和补偿电容来保证信号的质量。

总结:DDR4内存的原理是双数据率技术结合预取策略,以提高数据传输速度。

在硬件设计方面,DDR4内存模块由存储芯片、数据总线、地址总线、控制信号、电源和地线等组成。

合理的硬件设计对于DDR4内存模块的性能和稳定性都有重要影响。

DDR4设计概述以及分析仿真案例

因为 Vref 的不同,Vih/Vil 都会有差异,可以通过调整 ODT 来看 Vref 的区别, 用一个仿真的例子来说明。对于 DDR3,调整 ODT 波形会上下同步浮动,而调 整 DDR4 OOT 的时候,波形只有一边移动。

可以看出来,距离 Controller 越近的芯片,其波形越“乱”,但是上升沿却很快, 而距离终端电阻越近的芯片,其波形越好,但是上升沿却变慢。那么如何才能 得到最优化的波形呢,下面通过扫描终端电阻的值看看是否会提高信号质量,通 过 HyperLynx 的 Sweep 功能,设置终端电阻阻值为 27,33,39,45 四个阻值。

表 1 DDR3 和 DDR4 差异

在 DRAM 中,On-Die Termination 的等效电阻值通过 Mode Register (MR)来设 置,ODT 的精度通过参考电阻 RZQ 来控制,DDR4 的 ODT 支持 240, 120, 80, 60, 48, 40, 34 欧姆。

按照分析结果,缩短 L2,L3 的长度,改为阵脚比较短的 DIMM 插槽(因为设计 已经基本定型,只能进行小的改动,没有办法把 DDR 走线移动到靠近 Bottom 层的 Layer),重新改版后,之前测试 Fail 的 Margin 提高了 2~3 Step, 终于可 以 PASS 了。

1DDR4 关键技术和方法分析

1.1DDR4 与 DDR3 不同之处

相对于 DDR3, DDR4 首先在外表上就有一些变化,比如 DDR4 将内存下部设计 为中间稍微突出,边缘变矮的形状,在中央的高点和两端的低点以平滑曲线过 渡,这样的设计可以保证金手指和内存插槽有足够的接触面从而确保内存稳定, 另外,DDR4 内存的金手指设计也有明显变化,金手指中间的防呆缺口也比 DDR3 更加靠近中央。当然,DDR4 最重要的使命还是提高频率和带宽,总体来 说,DDR4 具有更高的性能,更好的稳定性和更低的功耗,那么从 SI 的角度出 发,主要有下面几点, 下面章节对主要的几个不同点进行说明。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DRAM (动态随机访问存储器)对设计人员特别具有吸引力,因为它提供了广泛的性能,用于各种计算机和嵌入式系统的存储系统设计中。

本文概括阐述了DRAM 的概念,及介绍了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、DDR5 SDRAM、LPDDR、GDDR。

DRAMDRAM较其它内存类型的一个优势是它能够以IC(集成电路)上每个内存单元更少的电路实现。

DRAM 的内存单元基于电容器上贮存的电荷。

典型的DRAM 单元使用一个电容器及一个或三个FET(场效应晶体管)制成。

典型的SRAM (静态随机访问内存)内存单元采取六个FET 器件,降低了相同尺寸时每个IC 的内存单元数量。

与DRAM 相比,SRAM 使用起来更简便,接口更容易,数据访问时间更快。

DRAM核心结构由多个内存单元组成,这些内存单元分成由行和列组成的两维阵列(参见图1)。

访问内存单元需要两步。

先寻找某个行的地址,然后在选定行中寻找特定列的地址。

换句话说,先在DRAM IC 内部读取整个行,然后列地址选择DRAM IC I/O(输入/ 输出)针脚要读取或要写入该行的哪一列。

DRAM读取具有破坏性,也就是说,在读操作中会破坏内存单元行中的数据。

因此,必需在该行上的读或写操作结束时,把行数据写回到同一行中。

这一操作称为预充电,是行上的最后一项操作。

必须完成这一操作之后,才能访问新的行,这一操作称为关闭打开的行。

对计算机内存访问进行分析后表明,内存访问中最常用的类型是读取顺序的内存地址。

这是合理的,因为读取计算机指令一般要比数据读取或写入更加常用。

此外,大多数指令读取在内存中顺序进行,直到发生到指令分支或跳到子例程。

图1. DRAMs 内存单元分成由行和列组成的两维阵列DRAM的一个行称为内存页面,一旦打开行,您可以访问该行中多个顺序的或不同的列地址。

这提高了内存访问速度,降低了内存时延,因为在访问同一个内存页面中的内存单元时,其不必把行地址重新发送给DRAM.结果,行地址是计算机的高阶地址位,列地址是低阶地址位。

由于行地址和列地址在不同的时间发送,因此行地址和列地址复用到相同的DRAM 针脚上,以降低封装针脚数量、成本和尺寸。

一般来说,行地址尺寸要大于列地址,因为使用的功率与列数有关。

早期的RAM拥有控制信号,如RAS# (行地址选择低有效)和CAS# (列地址选择低有效),选择执行的行和列寻址操作。

其它DRAM 控制信号包括用来选择写入或读取操作的WE# (写启动低有效)、用来选择DRAM的CS#(芯片选择低有效)及OE#(输出启动低有效)。

早期的DRAM拥有异步控制信号,并有各种定时规范,涵盖了其顺序和时间关系,来确定DRAM 工作模式。

早期的DRAM读取周期有四个步骤。

第一步,RAS# 与地址总线上的行地址变低。

第二步,CAS# 与地址总线上的列地址变低。

第三步,OE#变低,读取数据出现在DQ 数据针脚上。

在DQ 针脚上提供数据时,从第一步第三步的时间称为时延。

最后一步是RAS#, CAS# 和OE# 变高(不活动),等待内部预充电操作在破坏性读取后完成行数据的恢复工作。

从第一步开始到最后一步结束的时间是内存周期时间。

上述信号的信号定时与边沿顺序有关,是异步的。

这些早期DRAM没有同步时钟操作。

DRAM 内存单元必需刷新,避免丢失数据内容。

这要求丢失电荷前刷新电容器。

刷新内存由内存控制器负责,刷新时间指标因不同DRAM内存而不同。

内存控制器对行地址进行仅RAS# 循环,进行刷新。

在仅RAS# 循环结束时,进行预充电操作,恢复仅RAS# 循环中寻址的行数据。

一般来说,内存控制器有一个行计数器,其顺序生成仅RAS# 刷新周期所需的所有行地址。

刷新策略有两个(参见图2)。

第一个策略内存控制器在刷新周期突发中顺序刷新所有行,然后把内存控制返回处理器,以进行正常操作。

在到达最大刷新时间前,会发生下一个刷新操作突发。

第二个刷新策略是内存控制器使用正常处理器内存操作隔行扫描刷新周期。

这种刷新方法在最大刷新时间内展开刷新周期。

图2. DRAM 刷新实现方案包括分布式刷新和突发刷新。

早期的DRAM 演进及实现了DRAM IC 上的刷新计数器,处理顺序生成的行地址。

在DRAM IC 内部,刷新计数器是复用器输入,控制着内存阵列行地址。

另一个复用器输入来自外部地址输入针脚的行地址。

这个内部刷新计数器不需要内存控制器中的外部刷新计数器电路。

部分DRAM 在RAS# 周期前支持一个CAS#,以使用内部生成的行地址发起刷新周期。

SDRAM在接口到同步处理器时,DRAM 的异步操作带来了许多设计挑战。

SDRAM (同步DRAM)是为把DRAM操作同步到计算机系统其余部分,而不需要根据CE# (芯片启动活动低)、RAS#、CAS#和WE#边沿转换顺序定义所有内存操作模式而设计的。

SDRAM增加了时钟信号和内存命令的概念。

内存命令的类型取决于SDRAM 时钟上升沿上的CE#, RAS#,CAS# 和WE# 信号状态。

产品资料根据CE#, RAS#,CAS# 和WE# 信号状态,以表格形式描述内存命令。

例如,Activate (激活)命令向SDRAM发送一个行地址,打开内存的一个行(页面)。

然后是一个Deselect (反选)命令序列,在对列地址发送Read 或Write 命令前满足定时要求。

一旦使用Activate命令打开内存的行(页面),那么可以在内存的该行(页面)上运行多个Read和Write命令。

要求Precharge (预充电)命令,关闭该行,然后才能打开另一行。

表1. DDR SDRAM 数据速率和时钟速度。

DDR SDRAM通过提高时钟速率、突发数据及每个时钟周期传送两个数据位(参见表1),DDR (双倍数据速率)SDRAM 提高了内存数据速率性能。

DDR SDRAM 在一条读取命令或一条写入命令中突发多个内存位置。

读取内存操作必需发送一条Activate 命令,后面跟着一条Read 命令。

内存在时延后以每个时钟周期两个内存位置的数据速率应答由两个、四个或八个内存位置组成的突发。

因此,从两个连续的时钟周期中读取四个内存位置,或把四个内存位置写入两个连续的时钟周期中。

DDR SDRAM 有多个内存条,提供多个隔行扫描的内存访问,从而提高内存带宽。

内存条是一个内存阵列,两个内存条是两个内存阵列,四个内存条是四个内存阵列,依此类推(参见图3)。

四个内存条要求两个位用于内存条地址(BA0 和BA1)。

图3. DDR SDRAM中多个内存条提高了访问灵活性,改善了性能例如,有四个内存条的DDR SDRAM的工作方式如下。

首先,Activate命令在第一个内存条中打开一行。

第二个Activate命令在第二个内存条中打开一行。

现在,可以把Read 或Write 命令的任意组合发送到打开行的第一个内存条或第二个内存条。

在内存条上的Read 和Write 操作结束时,Precharge 命令关闭行,内存条对Activate 命令准备就绪,可以打开一个新行。

注意,DDR SDRAM要求的功率与打开行的内存条数量有关。

打开的行越多,要求的功率越高,行尺寸越大,要求的功率越高。

因此,对低功率应用,一次在每个内存条中只应打开一行,而不是一次打开行的多个内存条。

在内存条地址位连接到内存系统中的低阶地址位时,支持隔行扫描连续内存条中的连续内存字。

在内存条地址位连接到内存系统中的高阶地址时,连续内存字位于同一个内存条中。

DDR2 SDRAMDDR2 SDRAM 较DDR SDRAM 有多处改进。

DDR2SDRAM时钟速率更高,从而提高了内存数据速率(参见表2)。

随着时钟速率提高,信号完整性对可靠运行内存变得越来越重要。

随着时钟速率提高,电路板上的信号轨迹变成传输线,在信号线末端进行合理的布局和端接变得更加重要。

地址、时钟和命令信号的端接相对简明,因为这些信号是单向的,并端接在电路板上。

数据信号和数据选通是双向的。

内存控制器中心在写入操作中驱动这些信号,DDR2 SDRAM在读取操作中驱动这些信号。

多个DDR2 SDRAM 连接到同一个数据信号和数据选通上,进一步提高了复杂度。

多个DDR2 SDRAM 可以位于内存系统相同的DIMM上,也可以位于内存系统不同的DIMM上。

结果,数据和数据选通驱动器和接收机不断变化,具体取决于读取/ 写入操作及访问的是哪个DDR2 SDRAM。

表2. DDR2 SDRAM 数据速率和时钟速度。

通过提供ODT (芯片内端接),并提供ODT 信号,实现片内端接,并能够使用DDR2 SDRAM 扩展模式寄存器对片内端接值编程(75 欧姆、150 欧姆等等),DDR2SDRAM 改善了信号完整性。

片内端接大小和操作由内存控制器中心控制,与DDR2SDRAM DIMM 的位置及内存操作类型(读取或写入)有关。

通过为数据有效窗口创建更大的眼图,提高电压余量、提高转换速率、降低过冲、降低ISI (码间干扰),ODT操作改善了信号完整性。

DDR2 SDRAM 在上操作,降低了内存系统的功率,这一功率是DDR SDRAM 的功率的72%.在某些实现方案中,行中的列数已经下降,在激活行进行读取或写入时降低了功率。

降低工作电压的另一个优势是降低了逻辑电压摆幅。

在转换速率相同时,电压摆幅下降会提高逻辑转换速度,支持更快的时钟速率。

此外,数据选通可以编程为差分信号。

使用差分数据选通信号降低了噪声、串扰、动态功耗和EMI (电磁干扰),提高了噪声余量。

差分或单端数据选通操作配置有DDR2 SDRAM 扩展模式寄存器。

DDR2 SDRAM 引入的一种新功能是附加时延,它使得内存控制器中心能够在Activate命令后,更快地灵活发送Read 和Write 命令。

这优化了内存吞吐量,通过使用DDR2 SDRAM扩展模式寄存器对附加时延编程来配置。

DDR2 SDRAM使用八个内存条,改善了1Gb和2GbDDR2 SDRAM 的数据带宽。

通过隔行扫描不同的内存条操作,八个内存条提高了访问大型内存DDR2 SDRAM 的灵活性。

此外,对大型内存,DDR2 SDRAM支持最多八个内存条的突发长度。

DDR3 SDRAMDDR3 SDRAM 是一种性能演进版本,增强了SDRAM技术,它从800 Mb/s开始,这是大多数DDR2 SDRAM支持的最高数据速率。

DDR3 SDRAM 支持六档数据速率和时钟速度(参见表3)。

DDR3-1066 SDRAM的能耗低于DDR2-800 SDRAM,因为DDR3 SDRAM 的工作电压是V,是DDR2SDRAM 的83%,DDR2 SDRAM 的工作电压是伏。