AS5048A-HTSP 14位绝对式旋转编码器IC

霍尔旋转编码器的选型

产品目录编码器..............................................................................................................................- 1 - HAE18绝对型旋转编码器............................................................................................- 1 - HAE28绝对型旋转编码器............................................................................................- 4 - HAE38绝对型旋转编码器............................................................................................- 7 - HAN18模拟输出旋转编码器......................................................................................- 10 - HAN28模拟输出旋转编码器......................................................................................- 12 - HPE18增量型旋转编码器..........................................................................................- 14 - HPE28增量型旋转编码器..........................................................................................- 17 - HPE38增量型旋转编码器..........................................................................................- 20 - MPE28微功耗脉冲式编码器......................................................................................- 23 - 按钮开关........................................................................................................................- 24 - HSB分体式霍尔开关磁性按钮...................................................................................- 24 - 功率传感器....................................................................................................................- 27 - MPF电机功率传感器...................................................................................................- 27 - MQ三相电机相序&缺相传感.....................................................................................- 30 -编码器HAE18绝对型旋转编码器特点● 非接触式传感技术 ● 绝对值8、10、12位 ● 电源电压3V 或5V ● 串行数据输出SSI● 本体与外壳一体化结构、强度高 ● 耐环境、耐振、防护等级高● 结构紧凑、体积小、壳体直径仅18mm ● 内置两组滚珠轴承、适合工业环境电气参数机械参数轴承 启动力矩转子惯量 轴容许载荷 容许转速 材质 重量 2组密封 滚珠轴承≤3Ncm≤1gcm 2径向10N 轴向5N3600rpm (机械承受)壳体:铝合金或 不锈钢或铜镀镍 轴:不锈钢铝合金约30g 铜或不锈钢约40g (含标准线)环境条件使用环境温度保存环境温度防护等级耐振动耐冲击-40~+85℃ -40~+85℃IP65 10g(10~2000Hz) 100g (6mS )时序图z 8位:CLK 1 2 3 4 5 67 8910111213141516 17 18 192021读DO L OCK D7D6D5 D4 D3 D2D1D0注释状态位1有效角度值分辨率 电气转角 输出信号 上电响应读取时钟电源屏蔽线 256(8位) <2mS 5V ±10%、16mA 1024(10位) <60mS 4096(12位)360° (机械转角无停止位)串行数据 SSI<80mS≤1MHz3.3V ±10%或 5V ±10%、20mA标准0.3m 特殊0.5mz 10位:z 12位:状态位具有下列配置时才有效OCF COF LIN MagINC MagDEC EvenPAR0 00 11 0 0 1 01~15位的偶校验和符号最小 最大 单位t DO active 100 ns t CLK FE 500 ns T CLK/2 500 ns t DO valid 375 ns t DOtristate 100 ns t CSn 500 ns f CLK >0 1 MHz输出接口电路VDO CLK CS V / V P接线定义电源正Vc电源负0V输入CS 输入CLK输出DO 屏蔽线EAR红黑黄蓝绿粗黑注:屏蔽线内部未接壳体。

AMS磁编码器产品简介完整版前期

绝对编码器

• 绝对编码器是直接输出数字量的传感器,在它的圆形码盘上沿径向有 若干同心码道,每条道上由透光和不透光的扇形区相间组成,相邻码 道的扇区数目是双倍关系,码盘上的码道数就是它的二进制数码的位 数,在码盘的一侧是光源,另一侧对应每一码道有一光敏元件;当码 盘处于不同位置时,各光敏元件根据受光照与否转换出相应的电平信 号,形成二进制数。这种编码器的特点是不要计数器,在转轴的任意 位置都可 读出一个固定的与位置相对应的数字码。显然,码道越多, 分辨率就越高,对于一个具有 N位二进制分辨率的编码器,其码盘必 须有N条码道。 • 绝对式编码器是利用自然二进制或循环二进制(格雷码)方式进行光 电转换的。绝对式编码器与增量式编码器不同之处在于圆盘上透光、 不透光的线条图形,绝对编码器可有若干编码,根据读出码盘上的编 码,检测绝对位置。编码的设计可采用二进制码、循环码、二进制补 码等。它的特点是: • 可以直接读出角度坐标的绝对值、没有累积误差、电源切除后位置信 息不会丢失。 • 但是分辨率是由二进制的位数来决定的,也就是说精度取决于位数, 目前有10位、14位等多种。

AMS磁编码器产品名词解释及实用公式

名词解释

• 分辨率:

指的是磁编码器每圈的步长数。(如10位磁编 码器AS5040,其分辨率为0.35o,即每圈1024个位 置) • A/B正交两路及Index输出: A、B两路相位差90o脉冲信号,通过通道A的相 位超前通道B或通道B的相位超前通道A便可方便地 判断出旋转方向,每圈A/B各路输出的脉冲数为磁 编码数每圈步长数/4;Index指示绝对值零位,每 经过零点将产生一个脉冲。

增量式编码器

• 增量式编码器是直接利用光电转换原理输出三组 方波脉冲A、B和Z相;A、B两组脉冲相位差90o, 通过通道A的相位超前通道B或通道B的相位超前通 道A便可方便地判断出旋转方向;Z相为每转一个 脉冲,用于基准点定位。 • 优点:原理构造简单,机械平均寿命可在几万小 时以上,抗干扰能力强,可靠性高,适合于长距 离传输。 • 缺点:无法输出轴转动的绝对位置信息。

编码器的工作原理及作用

编码器的工作原理及作用:它是一种将旋转位移转换成一串数字脉冲信号的旋转式传感器,这些脉冲能用来控制角位移,如果编码器与齿轮条或螺旋丝杠结合在一起,也可用于测量直线位移。

编码器产生电信号后由数控制置CNC、可编程逻辑控制器PLC、控制系统等来处理。

这些传感器主要应用在下列方面:机床、材料加工、电动机反馈系统以及测量和控制设备。

在ELTRA 编码器中角位移的转换采用了光电扫描原理。

读数系统是基于径向分度盘的旋转,该分度由交替的透光窗口和不透光窗口构成的。

此系统全部用一个红外光源垂直照射,这样光就把盘子上的图像投射到接收器表面上,该接收器覆盖着一层光栅,称为准直仪,它具有和光盘相同的窗口。

接收器的工作是感受光盘转动所产生的光变化,然后将光变化转换成相应的电变化。

一般地,旋转编码器也能得到一个速度信号,这个信号要反馈给变频器,从而调节变频器的输出数据。

故障现象:1、旋转编码器坏(无输出)时,变频器不能正常工作,变得运行速度很慢,而且一会儿变频器保护,显示“PG断开”...联合动作才能起作用。

要使电信号上升到较高电平,并产生没有任何干扰的方波脉冲,这就必须用电子电路来处理。

编码器pg接线与参数矢量变频器与编码器pg之间的连接方式,必须与编码器pg的型号相对应。

一般而言,编码器pg型号分差动输出、集电极开路输出和推挽输出三种,其信号的传递方式必须考虑到变频器pg卡的接口,因此选择合适的pg卡型号或者设置合理.编码器一般分为增量型与绝对型,它们存着最大的区别:在增量编码器的情况下,位置是从零位标记开始计算的脉冲数量确定的,而绝对型编码器的位置是由输出代码的读数确定的。

在一圈里,每个位置的输出代码的读数是唯一的;因此,当电源断开时,绝对型编码器并不与实际的位置分离。

如果电源再次接通,那么位置读数仍是当前的,有效的;不像增量编码器那样,必须去寻找零位标记。

现在编码器的厂家生产的系列都很全,一般都是专用的,如电梯专用型编码器、机床专用编码器、伺服电机专用型编码器等,并且编码器都是智能型的,有各种并行接口可以与其它设备通讯。

光电编码器

光电编码器原理光电编码器,是一种通过光电转换将输出轴上的机械几何位移量转换成脉冲或数字量的传感器。

光电编码器每转输出600个脉冲,五线制。

其中两根为电源线,三根为脉冲线(A相、B相、Z)。

电源的工作电压为(+5~+24V)直流电源。

光电编码器是由光栅盘和光电检测装置组成。

光栅盘是在一定直径的圆板上等分地开通若干个长方形孔。

由于光电码盘与电动机同轴,电动机旋转时,光栅盘与电动机同速旋转,经发光二极管等电子元件组成的检测装置检测输出若干脉冲信号;通过计算每秒光电编码器输出脉冲的个数就能反映当前电动机的转速。

此外,为判定旋转方向,码盘还可提供相位相差90o的两路脉冲信号。

工作原理:当光电编码器的轴转动时A、B两根线都产生脉冲输出,A、B两相脉冲相差90度相位角,由此可测出光电编码器转动方向与电机转速。

假如A相脉冲比B相脉冲超前则光电编码器为正转,否则为反转.Z线为零脉冲线,光电编码器每转一圈产生一个脉冲.主要用作计数。

A线用来丈量脉冲个数,B线与A线配合可丈量出转动方向.设N为电机转速Δn=ND测-ND理例如:我们车的速度为1.5m/s,轮子的直径220mm,C=D*Pi,电机控制在21.7转/秒,根据伺服系统的指标,设电机转速为1500转/分,故可求得当ND=21.7*60=130转/分时,光码盘每秒钟输出的脉冲数为:PD=130×600/60=1300个脉冲当测出的脉冲个数与计算出的标准值有偏差时,可根据电压与脉冲个数的对应关系计算出输出给伺服系统的增量电压△U,经过D/A转换,再计算出增量脉冲个数,等下减往摘要:位置检测装置作为数控机床的重要组成部分,其作用是检测位移量,并发出反馈信号。

在现代数控伺服系统中广泛应用于角位移或角速率的测量。

目前生产和使用的数控机床大多采用的是半闭环控制方式。

关键词:光电编码器;角位移;脉冲;传感器光电编码器是一种旋转式位置传感器,在现代伺服系统中广泛应用于角位移或角速率的测量,它的转轴通常与被测旋转轴连接,随被测轴一起转动。

旋转编码器工作原理 __编码器

旋转编码器工作原理 __编码器旋转编码器工作原理编码器是一种常用的传感器,用于测量旋转运动的角度和方向。

它通常由一个旋转轴和一个固定的编码盘组成。

编码盘上有许多刻度线,当编码器旋转时,刻度线会与固定的传感器头相互作用,产生电信号。

这些电信号经过处理后,可以用来确定旋转角度和方向。

编码器的工作原理可以分为两种类型:增量式编码器和绝对式编码器。

1. 增量式编码器工作原理:增量式编码器通过检测旋转轴的角度变化来确定位置。

它包含两个输出信号:一个是A相信号,另一个是B相信号。

这两个信号相位差90度,并且在旋转过程中会交替变化。

当旋转轴顺时针旋转时,A相信号先变化,然后是B相信号。

当旋转轴逆时针旋转时,B相信号先变化,然后是A相信号。

通过检测A相和B相信号的变化,可以确定旋转轴的方向和角度。

2. 绝对式编码器工作原理:绝对式编码器可以直接测量旋转轴的绝对位置,不需要进行积分运算。

它通过在编码盘上使用不同的编码模式来实现。

常见的绝对式编码器有光电编码器和磁性编码器。

光电编码器使用光电传感器来检测编码盘上的光学模式。

编码盘上的光学模式由透明和不透明的区域组成。

当光电传感器检测到光学模式时,会产生相应的电信号。

通过解码这些电信号,可以确定旋转轴的绝对位置。

磁性编码器使用磁性传感器来检测编码盘上的磁性模式。

编码盘上的磁性模式由磁性材料组成,可以产生磁场。

磁性传感器通过检测磁场的变化来确定旋转轴的绝对位置。

无论是增量式编码器还是绝对式编码器,它们都可以通过接口将电信号传输到控制系统中进行处理。

控制系统可以根据编码器提供的信息,实现对旋转轴的精确控制和定位。

总结:旋转编码器是一种用于测量旋转运动的角度和方向的传感器。

它通过与固定的编码盘相互作用,产生电信号来确定旋转角度和方向。

编码器的工作原理可以分为增量式编码器和绝对式编码器。

增量式编码器通过检测A相和B相信号的变化来确定旋转轴的方向和角度。

绝对式编码器可以直接测量旋转轴的绝对位置,不需要进行积分运算。

无接触式磁旋转编码器AS5040介绍

无接触式磁旋转编码器AS5040介绍无接触式磁旋转编码器AS5040简介AS5040 是一款无接触式磁旋转编码器,用于精确测量整个360°内的角度。

此产品是一个片上系统,在单个封装内整合了集成式Hall 元件、模拟前端和数据信号处理功能。

测量角度时,只需简单地配备1 个在芯片中心上方旋转的双极磁铁即可。

磁铁可以安装在IC 的上方或下方。

这种绝对角度测量方式可即时指示磁铁的角位置,其分辨率达到0.35°,即每圈1024 个位置。

数字化数据能够以串行比特流或PWM 信号的形式给出。

另外,也可提供用户可编程的增量式输出,使得本芯片非常适合替换各类光学编码器产品。

AS5040 内置电压调节器,允许其工作在3.3V 或5V电源电压下。

无接触式磁旋转编码器AS5040特点1、完整的片上系统。

2、灵活的系统解决方案,同时可以提供绝对值串行输出、PWM 输出和增量输出。

3、由于采用无接触式检测方式,对工作环境严酷的应用非常理想能够耐受磁铁位置偏离和气隙变动情况。

4、不必进行温度补偿。

5、无需校准。

6、在整个360°范围内实现无接触式、高分辨率的旋转位置编码。

7、2种数字式、10位绝对值输出:串行接口输出;脉宽调制(PWM)输出。

8、3 种增量输出模式:正交A/B 和索引(Index)输出信号步/方向和索引输出信号可用于无刷直流电动机的3相换向10、9、8 或7 位用户可编程分辨率9、用户可编程零位/索引位置。

10、实现磁铁位置监测和断电监测的故障检测模式。

11、旋转速率可高达10,000 rpm。

12、能够检测磁铁沿Z 轴移动的按钮功能。

13、可采用菊链连接模式,串行读取多个互联的AS5040 器件。

14、宽广的温度范围: - 40°C 至+ 125°C。

15、完全符合汽车行业的AEC-Q100, 1 级规范。

16、小型无铅封装: SSOP 16 (5.3mm x 6.2mm)。

旋转编码器工作方式图解

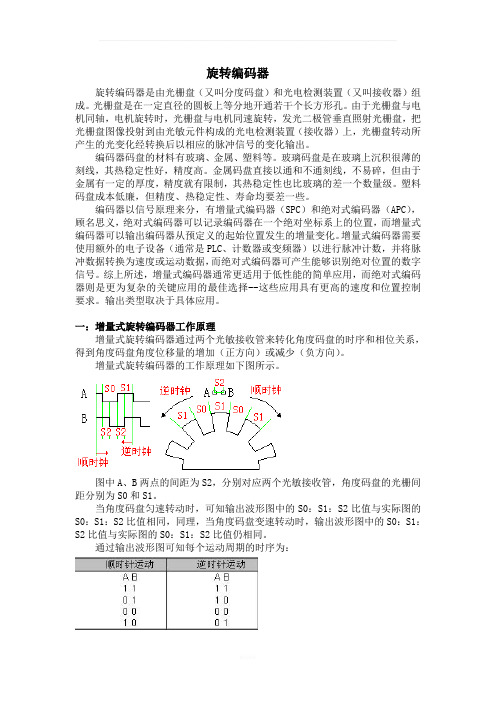

旋转编码器旋转编码器是由光栅盘(又叫分度码盘)和光电检测装置(又叫接收器)组成。

光栅盘是在一定直径的圆板上等分地开通若干个长方形孔。

由于光栅盘与电机同轴,电机旋转时,光栅盘与电机同速旋转,发光二极管垂直照射光栅盘,把光栅盘图像投射到由光敏元件构成的光电检测装置(接收器)上,光栅盘转动所产生的光变化经转换后以相应的脉冲信号的变化输出。

编码器码盘的材料有玻璃、金属、塑料等。

玻璃码盘是在玻璃上沉积很薄的刻线,其热稳定性好,精度高。

金属码盘直接以通和不通刻线,不易碎,但由于金属有一定的厚度,精度就有限制,其热稳定性也比玻璃的差一个数量级。

塑料码盘成本低廉,但精度、热稳定性、寿命均要差一些。

编码器以信号原理来分,有增量式编码器(SPC)和绝对式编码器(APC),顾名思义,绝对式编码器可以记录编码器在一个绝对坐标系上的位置,而增量式编码器可以输出编码器从预定义的起始位置发生的增量变化。

增量式编码器需要使用额外的电子设备(通常是PLC、计数器或变频器)以进行脉冲计数,并将脉冲数据转换为速度或运动数据,而绝对式编码器可产生能够识别绝对位置的数字信号。

综上所述,增量式编码器通常更适用于低性能的简单应用,而绝对式编码器则是更为复杂的关键应用的最佳选择--这些应用具有更高的速度和位置控制要求。

输出类型取决于具体应用。

一:增量式旋转编码器工作原理增量式旋转编码器通过两个光敏接收管来转化角度码盘的时序和相位关系,得到角度码盘角度位移量的增加(正方向)或减少(负方向)。

增量式旋转编码器的工作原理如下图所示。

图中A、B两点的间距为S2,分别对应两个光敏接收管,角度码盘的光栅间距分别为S0和S1。

当角度码盘匀速转动时,可知输出波形图中的S0:S1:S2比值与实际图的S0:S1:S2比值相同,同理,当角度码盘变速转动时,输出波形图中的S0:S1:S2比值与实际图的S0:S1:S2比值仍相同。

通过输出波形图可知每个运动周期的时序为:我们把当前的A、B输出值保存起来,与下一个到来的A、B输出值做比较,就可以得出角度码盘转动的方向,如果光栅格S0等于S1时,也就是S0和S1弧度夹角相同,且S2等于S0的1/2,那么可得到此次角度码盘运动位移角度为S0弧度夹角的1/2,再除以所用的时间,就得到此次角度码盘运动的角速度。

光电编码器详解

光电编码器光电编码器,是一种通过光电转换将输出轴上的机械几何位移量转换成脉冲或数字量的传感器。

这是目前应用最多的传感器,光电编码器是由光栅盘和光电检测装置组成。

根据检测原理,编码器可分为光学式、磁式、感应式和电容式。

根据其刻度方法及信号输出形式,可分为增量式、绝对式以及混合式三种。

绝对脉冲编码器:APC 增量脉冲编码器:SPC1. 光电编码器原理光电编码器,是一种通过光电转换将输出轴上的机械几何位移量转换成脉冲或数字量的传感器。

这是目前应用最多的传感器,光电编码器是由光栅盘和光电检测装置组成。

光栅盘是在一定直径的圆板上等分地开通若干个长方形孔。

由于光电码盘与电动机同轴,电动机旋转时,光栅盘与电动机同速旋转,经发光二极管等电子元件组成的检测装置检测输出若干脉冲信号,其原理示意图如图1所示;通过计算每秒光电编码器输出脉冲的个数就能反映当前电动机的转速。

此外,为判断旋转方向,码盘还可提供相位相差90°的脉冲信号。

fl进價光g元作放严形i光电绸码签原理示意图1.1 增量式编码器增量式编码器是直接利用光电转换原理输出三组方波脉冲A、B和Z相;A B两组脉冲相位差90,从而可方便地判断出旋转方向,而Z相为每转一个脉冲,用于基准点定位。

增量式光电编码器的特点是每产生一个输出脉冲信号就对应于一个增量位移,但是不能通过输出脉冲区别出在哪个位置上的增量。

它能够产生与位移增量等值的脉冲信号,其作用是提供一种对连续位移量离散化或增量化以及位移变化(速度)的传感方法,它是相对于某个基准点的相对位置增量,不能够直接检测出轴的绝对位置信息。

一般来说,增量式光电编码器输出A B两相互差90度角的脉冲信号(即所谓的两组正交输出信号),从而可方便地判断出旋转方向。

同时还有用作参考零位的Z相标志(指示)脉冲信号,码盘每旋转一周,只发出一个标志信号。

标志脉冲通常用来指示机械位置或对积累量清零。

增量式光电编码器主要由光源、码盘、检测光栅、光电检测器件和转换电路组成。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

General DescriptionThe AS5048 is an easy to use 360° angle position sensor with a 14-bit high resolution output. The maximum system accuracy is 0.05° assuming linearization and averaging is done by the external microcontroller.The IC measures the absolute position of the magnet’s rotation angle and consists of Hall sensors, analog digital converter and digital signal processing. The zero position can be programmed via SPI or I²C command. Therefore no programmer is needed anymore. This simplifies the assembly of the complete system because the zero position of the magnet does not need to be mechanically aligned. This helps developers to shorten their developing time. The sensor tolerates misalignment, air gap variations, temperature variations and as well external magnetic fields. This robustness and wide temperature range (-40°C up to +150°C) of the AS5048 makes the IC ideal for rotation angle sensing in harsh industrial and medical environments. Several AS5048 ICs can be connected in daisy chain for serial data read out. The absolute position information of the magnet is directly accessible over a PWM output and can be read out over a standard SPI or a high speed I²C interface. Version AS5048A comes with SPI and PWM Interface. Version AS5048B is configured with the I²C interface and has also a PWM output. An internal voltage regulator allows the AS5048 to operate at either 3.3 V or 5 V supplies.Key Features & Benefits • 360° contactless angle position sensor• Standard SPI or high speed I²C interface and PWM • Simple programmable zero position via SPI or I²C command• No programmer needed • 14-bit full scale resolution 0.0219°/LSB• Angle accuracy 0.05°after system linearization and averaging• Daisy chain capability• Tolerant to air gap variationsmagnetic field input range: 30mT – 70mT • -40°C to +150°C ambient temperature range • 3.3V / 5V compliant• 14-pin TSSOP package (5x6.4mm)Applications• Robotic joint position detection • Industrial motor position control• Medical robots and fitness equipmentBlock DiagramContentsGENERAL DESCRIPTION (1)K EY F EATURES &B ENEFITS (1)A PPLICATIONS (1)B LOCK D IAGRAM (1)1PIN CONFIGURATION (4)1.1P IN D ESCRIPTION (4)2ELECTRICAL CHARACTERISTICS (5)2.1A BSOLUTE M AXIMUM R ATINGS (5)2.2O PERATING C ONDITIONS (6)2.3DC/AC C HARACTERISTICS FOR DIGITAL INPUTS AND OUTPUTS (6)2.4E LECTRICAL S YSTEM S PECIFICATIONS (7)2.5G LOBAL T IMING C ONDITIONS (7)3FUNCTIONAL DESCRIPTION (8)4OPERATION (8)4.1SPI I NTERFACE (9)4.1.1SPI Interface Signals (4-Wire Mode, Wire_mode = 1) (9)4.1.2SPI Timing (10)4.1.3SPI Connection to the Host UC (11)4.1.4SPI Communication Command Package (12)4.1.5Read Package (Value Read from AS5048A) (13)4.1.6Write Data Package (Value Written to AS5048A) (13)4.1.7Register Map SPI (14)4.1.8SPI Interface Commands (15)4.2I²C INTERFACE (18)4.2.1I²C Electrical Specification (18)4.2.2I²C Timing (19)4.2.3Register Table (20)4.3PWM INTERFACE (21)5PACKAGE DRAWINGS AND MARKINGS (22)5.1.1Assembly Lot Code (22)6APPLICATION INFORMATION (24)6.1P ROGRAMMING OF THE AS5048 (24)6.1.1Programming of the zero position (24)6.1.2Programming sequence with verification (24)6.2D IAGNOSTIC FUNCTIONS OF THE AS5048 (24)6.3C HOOSING THE P ROPER M AGNET (25)6.4P HYSICAL P LACEMENT OF THE M AGNET (26)6.5M AGNET P LACEMENT (26)7ORDERING INFORMATION (27)8REVISION HISTORY (27)9COPYRIGHTS (28)10DISCLAIMER (28)List of FiguresF IGURE 1:P IN CONFIGURATION TSSOP14 (4)F IGURE 2:C ONNECTIONS FOR 5V AND 3.3V SUPPLY VOLTAGES (8)F IGURE 3SPI C ONNECTION AS5048A WITH U C (9)F IGURE 4SPI C OMMAND/R ESPONSE D ATA F LOW (9)F IGURE 5SPI T IMING D IAGRAM (10)F IGURE 6S INGLE S LAVE M ODE (11)F IGURE 7M ULTIPLE S LAVE, N+3W IRE (S EPARATE C HIP S ELECT) (11)F IGURE 8D AISY C HAIN,4W IRE (12)F IGURE 9READ C OMMAND (15)F IGURE 10WRITE C OMMAND (15)F IGURE 11CLEAR ERROR FLAG C OMMAND (16)F IGURE 12NOP C OMMAND (17)F IGURE 13PWM F ORMAT (21)F IGURE 14P ACKAGE M ARKING (22)F IGURE 15:T YPICAL MAGNET (6X3MM) AND MAGNETIC FIELD DISTRIBUTION (25)F IGURE 16:D EFINED CHIP CENTER AND MAGNET DISPLACEMENT RADIUS (26)F IGURE 17:V ERTICAL PLACEMENT OF THE MAGNET (26)List of TablesT ABLE 1:P IN DESCRIPTION TSSOP14 (4)T ABLE 2A BSOLUTE M AXIMUM R ATINGS (5)T ABLE 3:O PERATING C ONDITION (6)T ABLE 4:DC/AC CHARACTERISTICS (6)T ABLE 5S YSTEM SPECIFICATION (7)T ABLE 6G LOBAL TIMING CONDITIONS (7)T ABLE 7SPI T IMING C HARACTERISTICS (10)T ABLE 8SPI C OMMAND P ACKAGE (12)T ABLE 9SPI READ PACKAGE (13)T ABLE 10SPI WRITE DATA PACKAGE (13)T ABLE 11SPI REGISTER MAP (14)T ABLE 12C LEAR E RROR F LAG C OMMAND (16)T ABLE 13NOP C OMMAND (17)T ABLE 14I²C E LECTICAL S PECIFICATION (18)T ABLE 15 I²C T IMING ............................................................................................................................ 19 T ABLE 16 R EGISTER M AP I2C ................................................................................................................ 20 T ABLE 17 PWM P ERIOD AND RESOLUTION .............................................................................................. 21 T ABLE 18: O RDERING I NFORMATION (27)1 Pin Configuration2345678910111213141SDA/CSn SCL/CLK A2/MISO A1/MOSI TEST TEST TESTTESTTEST TEST VDD5V VDD3V GND PWM AS5048Figure 1: Pin configuration TSSOP141.1 Pin DescriptionPin Symbol Type Description1 SDA/CSn DI_ST SPI chip select - active low; shared with I2C chip select pin2 SCL/CLK DI_ST SPI clock input; shared with I2C clock input3 A2/MISO DIO_ST SPI master in/slave out; shared with I2C address selection pin 24 A1/MOSI DI_ST SPI master out/slave in; shared with I2C address selection pin 15 TEST AIO Test pin, see Note6 TEST AIO Test pin, see Note7 TEST AIO Test pin, see Note8 TEST AIO Test pin, see Note9 TEST AIO Test pin, see Note 10 TEST AIO Test pin, see Note11 VDD5V S Positive Supply Voltage, 3.0 to 5.5 V12VDD3VS3.3V Regulator output; internally regulated from VDD. Connect to VDD for 3V supply voltage. 10uF capacitor to GND required in 5V operation mode13 GND S Negative Supply Voltage (GND) 14PWMDOPulse Width Modulation outputTable 1: Pin description TSSOP14PIN Types: S ... supply pad AIO ... analog I/O DI_ST … digital input with schmitt trigger DO ... digital output – push-pull DIO _ST ... digital I/O with schmitt trigger in the input pathNote: Pin 5 should be grounded to VSS. Pins 6, 7, 8, 9, 10 should be left open during the normal operation.2Electrical Characteristics2.1Absolute Maximum RatingsStresses beyond those listed under “Absolute Maximum Ratings“ may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under “Operating Conditions” is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Parameter Symbol Min Max Unit NoteDC supply voltage at VDD pin VDD5V -0.3 7 V (1)DC voltage at VDD3V pin VDD3V -0.3 5 VDC voltage at GND pin GND -0.3 0.3 VInput pin voltage V_in VDD+0.3 VInput current (latchup immunity) I_scr -100 100 mA Norm: Jedec 78Electrostatic discharge ESD +/-2 kV Norm: MIL 883 E method 3015Total power dissipation (all supplies andoutputs)P_t 150 mWStorage temperature T_strg -55 150 °CPackage body temperature T_body 260 °C The reflow peak soldering temperature (body temperature)specified is in accordance with IPC/JEDEC J-STD-020 “Moisture Solid State Surface Mount Devices”. The lead finish from Pb-free leaded packages is matte tin (100% Sn)Humidity non-condensing H 5 85 %Moisture Sensitive Level MSL 3 Represents a maximum floor life time of 168hTable 2 Absolute Maximum Ratings2.2Operating ConditionsAll in this specification defined tolerances for external components need to be assured over the whole operation conditions range and also over lifetime.Parameter Symbol Min Max Unit NotePositive supply voltage VDD5V 4.5 5.5 V 5V Operation via LDOVDD3V 3 3.6 V LDO output voltage Positive core supply voltage VDDCORE 3 3.6 VNegative supply voltage GND 0 0 VAmbient temperature T_amb -40 150 °C Only for 5V operation.T_amb_max for 3V is 125°C Supply Current I_sup 15 mATable 3: Operating Condition2.3DC/AC Characteristics for digital inputs and outputsParameter Symbol Min Typ Max Unit Note CMOS digital input with schmitt trigger: CSn, CLK, MOSIHigh level input voltage V_IH 0.7 * VDD5V VLow level input voltage V_IL 0.3 * VDD5V VInput leakage current l_LEAK 1 µACMOS output: PWM, MISOHigh level output voltage V_OH VDD5V-0.5 VLow level output voltage V_OL GND+0.4 VCapacitive load C_L 50 pFOutput current I_OUT 4 mATable 4:DC/AC characteristics2.4Electrical System SpecificationsVDD5V = 5V, T Ambient = -40 to +150°C unless noted otherwiseParameter Symbol Min Typ Max Unit Note Magnetic input field Bz 30 50 70 mTOutput sampling rate f sample10.2 11.25 12.4 kHzOutput Resolution RES 14 BitSensor output noise Noise 0.06 Deg 2.73LSB@14bit, rms valueSystem propagation delay t prop90.7 100 110.2 µs PWM frequency f PWM0.907 1 1.102 kHzNon-linearity optimum placement of magnet INL OPT±0.4 DegAssuming 8 mmdiameter of magnetNon-linearity @displacement of magnet INL DIS±0.7 DegAssuming 8 mmdiameter of magnet and500 um displacement inx and yNon-linearity @displacement ofmagnet and temperature -40 -150 degC INL DIS+TEMP±1.2 DegAssuming 8 mmdiameter of magnet and500 um displacement inx and yTable 5 System specification2.5Global Timing ConditionsParameter Symbol Min Typ Max Unit Note Internal Master Clock F OSC 4.05 4.5 4.95 MHz ±10%T OSC1/F OSC HzTable 6 Global timing conditions3Functional DescriptionThe AS5048 is a magnetic Hall sensor system manufactured in a CMOS process. A lateral Hall sensor array is used to measure the magnetic field components perpendicular to the surface of the chip. The AS5048 is uses self-calibration methods to eliminate signal offset and sensitivity drifts.The integrated Hall sensors are placed around the center of the device and deliver a voltage representation of the magnetic flux Bz.Through Sigma-Delta Analog-to-Digital Converter (ADC) and Digital Signal-Processing (DSP) algorithms, the AS5048 provides accurate high-resolution absolute angular position information. This is accomplished by a Coordinate Rotation Digital Computer (CORDIC) calculates the angle and the magnitude of the Hall array signals.The DSP is also used to provide digital information at the outputs that indicate movements of the magnet towards or away from the device’s surface, in the z-axis.A small diametrically magnetized (two-pole) standard magnet provides the angular position information. Depending on the system requirements different magnet diameters are possible. Additional flexibility is given by the wide range of the magnetic input range. The AS5048 can be combined with NeFeB, SmCo and alternative magnet materials e.g. hard ferrites. The AS5048 provides a 14-bit binary code representing the angular position of the magnet. The type of output is pre-programmed as SPI version A or I2C version B. Simultaneously a PWM output signal is available in 12 bit format.A simple programming of the zero position is possible over the interface. No additional programmer is needed. The AS5048 uses one time programmable (OTP) fuses for permanent programming of the user settings. The verification is possible over a simple digital readout of the OTP content.4OperationThe AS5048 operates at 5V ±10%, using an internal Low-Dropout (LDO) voltage regulator. In addition a 3.3V operation is possible. The VDD3V output is intended for internal use only. It must not be loaded with an external load.3.3V OperationFigure 2: Connections for 5V and 3.3V supply voltagesNote: The pin VDD3V must always be buffered by a 10 µF capacitor in 5V operation. It must not be left floating, as this may cause unstable internal supply voltages which may lead to larger output jitter of the measured angle.In 3V operation the VDD3V must be shorted to VDD5V.4.1SPI InterfaceThe 16 bit SPI Interface enables read / write access to the register blocks and is compatible to a standard micro controller interface. The SPI is active as soon as CSn is pulled low. The AS5048A then reads the digital value on the MOSI(master out slave in) input with every falling edge of CLK and writes on its MISO (master in slave out) output with the rising edge. After 16 clock cycles CSn has to be set back to a high status in order to reset some parts of the interface core.4.1.1SPI Interface Signals (4-Wire Mode, Wire_mode = 1)The AS5048A only supports slave operation mode. Therefore CLK for the communication as well as the CSn signal has to be provided by the test equipment. The following picture shows a basic interconnection diagram with one master and an AS5048A device and a principle schematic of the interface core.Figure 4 SPI Command/Response Data Flow4.1.2SPI TimingFigure 5 SPI Timing DiagramParameterDescriptionMin Max Unit t L Time between CSn falling edge and CLK rising edge 10 (2) Ns t L Time between CSn falling edge and CLK rising edge 350 (1) Ns T CLK Serial clock period 100 Ns t CLKL Low period of serial clock 50 Ns t CLKH High period of serial clock50 Ns t H Time between last falling edge of CLK and rising edge of CSn t SCK / 2 Ns T CSnH High time of CSn between two transmissions 10 (2) Ns T CSnH High time of CSn between two transmissions 350 (1) Ns t MOSI Data input valid to clock edge 20 Ns t MISOCLK edge to data output valid20NsTable 7 SPI Timing CharacteristicsNotes:(1) Synchronization with the internal clock 2 * t CLK_SYS + 10 ns (e.g. at 8 MHz 253 ns) (2) No synchronization needed because the internal clock is inactive4.1.3SPI Connection to the Host UC Single Slave ModeDaisy Chain, 4 Wire4.1.5Read Package (Value Read from AS5048A)The read frame always contains two alarm bits, the parity and error flags and the addressed data of the previous read command.Read PackageBit MSB 14 13 12 11 10 9 8 7 6 5 4 3 2 1 LSBPAR EF Data<13:0>Bit Definition & DescriptionPAR Parity bit (EVEN)EF Error flag indicating a transmission error in a previous host transmissionData 14 bit addressed dataTable 9 SPI read package4.1.6Write Data Package (Value Written to AS5048A)The write frame is compatible to the read frame and contains two additional bits, parity flag and R flag.If the previous command was a write command a second package has to be transmitted.Data PackageBit MSB 14 13 12 11 10 9 8 7 6 5 4 3 2 1 LSBPAR R Data <13:0>Bit Definition & DescriptionPAR Parity bit (EVEN)R Has to be 0Data 14 bit data to write to former selected addressTable 10 SPI write data package4.1.7Register Map SPIAddress hexNameAccessType Bit Nr.SymbolDefaultDescription13:013:32Parity Error 1Command Invalid 0Framing Error13:76Verify 543Burn 210Programming Enable13:87Zero Position <13>0:::0Zero Position <6>013:65Zero Position <5>0:::0Zero Position <0>0131211Comp High 010Comp Low 09COF 08OCF17AGC value<7>1:::0AGC value<0>013Magnitude<13>0:::0Magnitude<0>013Angle <13>0:::0Angle<0>No operation dummy informationnot used n.a.x0001Clear Error Flag RError Register. All errors are cleared by accessx0000SPI NOPRNOPR/W Programming ControlR/W+Program0Zero Position remaining 6 lower LSB'sR/W +Programx0003not used reserved 0Programming control register.Programming must be enabled before burning the fuse(s). After programming is an verification mandatory.See programming procedure.Zero Position value high bytenot used OTP RegisterZero Position Hix0016not used OTP Register Zero Position Low 6 LSBs x0017P r o g r a m m a b l e C u s t o m e r s e t t i n g snot used C o n t r o l a n d E r r o r R e g i s t e r sAngle RAngle information after ATAN calculationand zero position adderx3FFF R e a d o u t R e g i s t e r sx3FFE Magnitude RMagnitude information after ATAN calculation x3FFD Diagnostics +Automatic GainControl (AGC)Rnot used n.a.Diagnostics flagsAutomatic Gain Control value.0 decimal represents high magnetic field 255 decimal represents low magnetic fieldTable 11 SPI register map4.1.8SPI Interface CommandsREAD CommandFor a single READ command two transmission sequences are necessary. The first package written to the AS5048 contains the READ command (MSB-1 high) and the address the chip has to access, the second package transmitted to the AS5048 device can be any command the chip has to process next. The content of the desired register is available in the MISO register of the master device at the end of the second transmission cycle.CLEAR ERROR FLAG CommandThe CLEAR ERROR FLAG command is implemented as READ command. This command clears the ERROR FLAG which is contained in every READ frame. Before the ERROR FLAG is cleared the error register content comes back with the information which error type was occurred. On the next new READ register the ERROR FLAG is clearedFigure 11 CLEAR ERROR FLAG CommandThe package necessary to perform a CLEAR ERROR FLAG is built up as follows.CLEAR ERROR FLAG CommandBit MSB 14 13 12 11 10 9 8 7 6 5 4 3 2 1 LSB PAR 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1Table 12 Clear Error Flag CommandPossible conditions which force the ERROR FLAG to be set:wrong paritywrong number of clocks (no full transmission cycle or too many clocks)Note: If the error flag is set to high because of a communication problem the flag remains set until it will be cleared by the CLERAR ERROR FLAG command.NOP CommandThe NOP command represents a dummy write to the AS5048.Figure 12 NOP CommandThe NOP command frame looks like follows.NOP CommandBit MSB 14 13 12 11 10 9 8 7 6 5 4 3 2 1 LSB0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0Table 13 NOP CommandThe chip’s response on this command is 0x0000 – if no error happens.4.2I²C interfaceThe AS5048B supports 2-wire high-speed I²C protocol in device mode. The host MCU (master) has to initiate the data transfers. The 7-bit device address of the Slave depends on the state of the OTP value(1000 0) + 2 spare Pins (xx): Slave address =‘1000 0xx’Supported modes:Random/Sequential ReadByte/Page WriteStandard :0 to 100kHz clock frequency (slave mode)Fast Mode : 0 to 400kHz clock frequency (slave mode)High Speed: 0 to 3.4MHz clock frequency (slave mode)The SDA signal is bidirectional and is used to read and write the serial data. The SCL signal is the clock generated by the host MCU, to synchronize the SDA data in read and write mode. The maximum I²C clock frequency is 3.4MHz, data are triggered on the rising edge of SCL.4.2.1I²C Electrical SpecificationFS-mode+ HS-mode C B=100pF HS-mode C B=400pF Symbol Parameter Condition Min Max Min Max Min Max Unit V IL LOW-Level Input Voltage -0.5 0.3V DD-0.5 0.3VDDp -0.5 0.3V DD VV IH HIGH-Level Input Voltage 0.7V DD V DD + 0.5(1) 0.7V DD VDD +0.5 (1)0.7VDDp V DD + 0.5(1)VV hys Hysteresis of Schmitt TriggerInputsV DDp < 2V 0.1V DD-- 0.1V DD-- 0.1VDD -- VV OL LOW-Level Output Voltage(open-drain or open-collector)at 3mA Sink CurrentV DDp < 2V -- 0.2V DD-- 0.2VDD -- 0.2V DD VI OL LOW-Level Output Current V OL = 0.4V 20 -- -- -- -- mA I CS Pull-up current of SCLHcurrent source-- -- 3 12 3 12 mAt SP Pulse Width of Spikes thatmust be suppressed by theInput Filter-- 50 (2) -- 10 -- 10 nsI i Input Current at each I/O Pin Input Voltagebetween-10 +10 (3) -- 10 -- 10 µAC B Total Capacitive Load foreach Bus Line-- 550 -- 100 -- 400 pF C I/O I/O Capacitance (SDA, SCL) -- 10 -- 10 -- 10 pFTable 14 I²C Electical Specification(1)Maximum V IH = V DDpmax +0.5V or 5.5V(2)Input filters on the SDA and SCL inputs suppress noise spikes of less than 50 ns.(3)I/O pins of Fast-mode and Fast-mode Plus devices must not obstruct the SDA and SCL lines if VDD is switchedoff.4.2.2I²C TimingFS-mode+ HS-mode C B=100pF HS-mode C B=400pF(5)Symbol Parameter Condition Min Max Min Max Min Max Unit f SCLK SCL clock Frequency -- 1000 -- 3400 -- 1700 kHz t BUF Bus Free Time; time betweenSTOP and START Condition500 -- 500 -- 500 -- nst HD;STA Hold Time; (Repeated) STARTCondition (1)260 -- 160 -- 160 -- ns t LOW LOW Period of SCL Clock 500 -- 160 -- 320 -- ns t HIGH HIGH Period of SCL Clock 260 -- 60 -- 120 -- ns t SU;STA Setup Time for a RepeatedSTART condition260 -- 160 -- 160 -- ns t HD;DAT Data Hold Time (2) 0 450 0 70 0 150 ns t SU;DAT Data Setup Time (3) 50 -- 10 -- 10 -- nst R Rise Time of SDA and SCLSignals 20+0.1C b120 -- -- -- -- nst F Fall time of SDA and SCL signals 20+0.1C b120 (4) -- -- -- -- nst rCL Rise time of SCLH signal Ext. pull-upsource of 3mA-- -- 10 40 20 80 nst rCL1Rise time of SCLH signal afterrepeated START condition andafter an acknowledge bit Ext. pull-upsource of 3mA-- -- 10 80 20 160 nstf CL Output rise time of SCLH signal Ext. pull-upsource of 3mA-- -- 10 40 20 80 ns t rDA Output rise time of SDAH signal -- -- 10 80 20 160 ns t fDA Output rise time of SDAH signal -- -- 10 80 20 160 ns t SU;STO Setup Time for STOP Condition 260 -- 160 -- 160 -- Ns V nL Noise margin at LOW level 0.1V DDp-- 0.1V DDp-- 0.1V DDp-- V V nH Noise margin at HIGH level 0.2V DDp-- 0.2V DDp-- 0.2V DDp-- VTable 15 I²C Timing(1)after this time the first clock is generated(2) A device must internally provide a minimum hold time (120ns / max 250ns for Fast-mode Plus, 80ns / max 150ns for High-speed mode) for the SDA signal (referred to the V IHm in of the SCL) to bridge the undefined region of the falling edge of SCL.(3) A fast-mode device can be used in standard-mode system, but the requirement t SU;DAT = 250ns must then e met. This isautomatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does strech the LOWperiod of the SCL signal, it must output the next data bit to the SDA line t Rmax + T SU;DAT = 1000 + 250 = 1250ns before the SCLline is released.(4)In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used this has tobe considered for bus timing(5)For capacitive bus loads between 100pF and 400pF, the timing parameters must be linearly interpolated4.2.3Register TableThe following registers / functions are accessible over the serial I²C interface.Address decNameAccessType Bit Nr.SymbolDefault Description7not used 6Verify 543Burn 210Programming Enable7:54I²C address<4>0:::0I²C address<0>07Zero Position <13>0:::0Zero Position <6>0765Zero Position <5>0:::0Zero Position <0>07AGC value<7>1:::0AGC value<0>07:43Comp High 02Comp Low 01COF 00OCF17Magnitude<13>0:::0Magnitude<6>0765Magnitude<5>0:::0Magnitude<0>07Angle<13>0:::0Angle<6>0765Angle<5>0:::0Angle<0>Angle Value afer ATAN calculationand zero position adderDiagnostic flagsAutomatic Gain Control value.0 decimal represents high magnetic field 255 decimal represents low magnetic fieldAutomatic Gain ControlR250not used n.a.251Diagnostics RC o n t r o l O T PProgramming ControlR/W P r o g r a m m a b l e C u s t o m e r s e t t i n g sR/W +ProgramR e a d o u t R e g i s t e r s254not used n.a.I²C slave addressR/W +Program I²C slave address2123OTP Register Zero PositionHi OTP Register Zero Position Low 6 LSBs R/W +Program not used reserved 0Programming control register.Programming must be enabled before burning the fuse(s). After programming is an verification mandatory.See programming procedure.3not used n.a.Zero Position value high byteZero Position remaining 6 lower LSB's22not used RRn.a.MagnitudeMagnitude information afer ATAN calculation252253not used n.a.RRAngle255Table 16 Register Map I2C4.3PWM interfaceThe AS5048 provides a pulse width modulated output (PWM), whose duty cycle is proportional to the measured angle. The PWM frequency is internally trimmed to an accuracy of ±10% over full temperature range. This tolerance can be cancelled by measuring the complete duty cycle.The PWM signal consists of different sections:•Init:12 clocks -> PWM = ‘high’•Error_n:4 clocks -> PWM = ‘not(system_error)’•Data:4095 clocks -> PWM = ‘angle_zero’ / ‘low’ (in case of error)•Exit:8 clocks -> PWM = ‘low’In case of an error the data section is set to zero.5Package Drawings and MarkingsPackage type: TSSOP14Figure 14 Package Marking5.1.1Assembly Lot CodeThe assembly lot code for standard “YYWWIZZ” is composed as follows: X - Interface type: A=SPI / B=I2CYY- YearWW- WeekI- Plant identification letterZZ- Letters for free traceability14-Lead Thin Shrink Small Outline Package TSSOP-146Application Information6.1Programming of the AS50486.1.1Programming of the zero positionThe absolute angle position can be permanent programmed over the interface. This could be useful for random placement of the magnet on the rotation axis. A readout at the mechanical zero position can be performed and written back into the IC. With permanent programming the position is non-reversible stored in the IC. This programming can be performed only once.To simplify the calculation of the zero position it is only needed to write the value in the IC which was read out before from the angle register.6.1.2Programming sequence with verificationTo program the zero position is needed to perform following sequence:1.Read angle information2.Set the Programming Enable bit in the OTP control register3.Write previous read angle position into OTP zero position register4.Read back for verification the zero position register data5.Set the Burn bit to start the automatic programming procedure6.Read angle information (equals to 0)7.Set the Verify bit to load the OTP data again into the internal registers with modified threshold comparator levels8.Read angle information (equals to 0)The programming can either be performed in 5V operation using the internal LDO, or in 3V operation but using a minimum supply voltage of 3.3V. In case of 3V operation, also a 10uF capacitor is required on the VDD3 pin.6.2Diagnostic functions of the AS5048The AS5048 provides diagnostics functions of the IC and also diagnostic functions of the magnetic input fieldFollowing diagnostic flags are accessible:OCF (O ffset C ompensation F inished), logic high indicates the finished Offset Compensation Algorithm. After power up the flag remains always to logic high.COF (C ordic O ver f low), logic high indicates an out of range error in the CORDIC part. When this bit is set, the angle and magnitude data is invalid. The absolute output maintains the last valid angular value.COMP low, indicates a weak magnetic field. It is recommended to monitor in addition the magnitude value.COMP high, indicated a high magnetic field. It is recommended to monitor the magnitude value.。