MIPS汇编

mips 汇编代码

MIPS汇编代码MIPS汇编代码是MIPS微处理器的汇编语言,由MIPS Technologies公司开发。

它是一种低级编程语言,允许程序员直接控制处理器的寄存器和指令。

MIPS汇编代码通常用于嵌入式系统和实时系统,因为它可以提供对硬件的精细控制和高性能。

MIPS汇编代码由一系列指令组成,每条指令由一个操作码和零个或多个操作数组成。

操作码指定要执行的操作,而操作数指定操作的参数。

MIPS汇编代码中的指令可以分为以下几类:算术和逻辑指令:这些指令用于执行算术和逻辑运算,例如加、减、乘、除、与、或、非等。

数据传送指令:这些指令用于在寄存器和内存之间传送数据。

控制流指令:这些指令用于控制程序的执行流程,例如跳转、分支、调用和返回等。

系统指令:这些指令用于与系统进行交互,例如加载和存储程序和数据、读写I/O设备等。

MIPS汇编代码通常使用以下语法:label: instruction operand1, operand2, ...其中,label是指令的标签,instruction是指令的操作码,operand1、operand2等是指令的操作数。

MIPS汇编代码的程序结构通常包括以下几个部分:数据段:数据段用于存储程序中使用的数据,包括常量、变量和数组等。

代码段:代码段用于存储程序的指令。

堆栈段:堆栈段用于存储程序的局部变量和临时数据。

MIPS汇编代码的编译过程通常包括以下几个步骤:预处理:预处理阶段将源代码中的宏和条件编译指令进行处理。

汇编:汇编阶段将源代码中的指令转换成机器码。

链接:链接阶段将汇编生成的机器码与库函数和系统库进行链接,生成可执行文件。

MIPS汇编代码的优点包括:高性能:MIPS汇编代码可以提供高性能,因为它可以直接控制处理器的寄存器和指令。

精细的控制:MIPS汇编代码允许程序员对硬件进行精细的控制,这对于嵌入式系统和实时系统非常重要。

可移植性:MIPS汇编代码可以移植到不同的MIPS处理器上,因为MIPS处理器具有相同的指令集架构。

MIPS汇编

ext d,s,shf,sz 从32位寄存器提取位域。Shf是位域在s中的移位到 第0位所需要的位移量,sz是位域包含的位的个数。 mask=(2**sz-1)<<shf,d=(s&mask)>>shf

/p-141124298.html (MIPS指令与汇编)

or d,s,t

d=s | t

ori d,s,j 作OR

d=s|(unsigned)j,跟一个常数执行“或”操

sllv d,t,s d=t<<(s%32) (shift left logic by variable)

sll d,s,shf d=s<<shf;sll d,t,s,d=t<<(s%32)

sra d,s,shf d=(signed)s>>shf,shift-right arithmetic,算术右移, 最高位填充,适用于有符号数,sra d,s,t,d=(signed)s>>(t%32)

srav d,s,t sra d,s,t

srl d,s,shf d=(unsigned)s>>shf ,shift-right logical,逻辑右移, 类似C的无符号量的移位

.data伪指令

定义程序的数据段,程序的变量需要在该伪指令 下定义,汇编程序会分配和初始化变量的存储空间

.text伪指令

定义程序的代码段

.global伪指令

声明一个符号位全局的,全局符号可以被其他的 文件引用,用该伪指令声明一个程序的main过程

寻址

➢ 直接寻址

mips汇编语言指令

mips汇编语言指令MIPS(Microprocessor without Interlocked Pipeline Stages)是一种精简指令集(RISC)架构的计算机处理器。

它的指令集被广泛应用于各种领域,包括嵌入式系统、操作系统和编译器等。

本文将介绍一些常见的MIPS汇编语言指令。

1. 加载和存储指令MIPS提供了一系列用于数据传输的指令。

其中,lw(load word)指令用于从内存中加载一个字(32位数据)到寄存器中,sw(store word)指令用于将一个字存储到内存中。

例如,lw $t0, 0($s0)表示将从地址$s0偏移量为0的内存位置加载一个字到$t0寄存器中。

2. 算术和逻辑指令MIPS提供了一系列用于算术和逻辑运算的指令。

例如,add指令用于将两个寄存器中的值相加,并将结果存储到目标寄存器中。

而and 指令用于对两个寄存器中的值进行按位与操作,并将结果存储到目标寄存器中。

例如,add $t0, $s0, $s1表示将$s0和$s1中的值相加,并将结果存储到$t0寄存器中。

3. 分支和跳转指令MIPS提供了一系列用于控制程序流程的指令。

其中,beq(branch if equal)指令用于在两个寄存器中的值相等时跳转到目标地址。

而j (jump)指令用于无条件跳转到目标地址。

例如,beq $t0, $t1, label表示如果$t0和$t1中的值相等,则跳转到标签为label的位置。

4. 移位指令MIPS提供了一系列用于移位操作的指令。

其中,sll(shift left logical)指令用于将一个寄存器中的值左移指定的位数,并将结果存储到目标寄存器中。

例如,sll $t0, $s0, 2表示将$s0中的值左移2位,并将结果存储到$t0寄存器中。

5. 系统调用指令MIPS提供了一系列用于进行系统调用的指令。

其中,syscall指令用于触发系统调用,并根据不同的系统调用号执行相应的操作。

mips汇编程序设计 -回复

mips汇编程序设计-回复MIPS(Microprocessor without Interlocked Pipeline Stages)是一种RISC(Reduced Instruction Set Computer)架构的计算机处理器。

它是由斯坦福大学开发的,并且成为了一种非常流行的汇编语言。

MIPS架构的设计理念是简化指令集,以提高指令的执行效率。

它采用了统一的指令格式,所有的指令都是32位长,并且具有相同的4个字段:操作码(opcode)、目标寄存器(destination register)、源寄存器1(source register 1)和源寄存器2(source register 2)。

这种规范化的指令格式使得MIPS的指令编码非常简洁和高效。

首先,让我们来介绍一些MIPS汇编程序设计的基本概念和概述。

MIPS 指令集包括一系列的算术和逻辑操作指令,如加法、减法、乘法、除法等。

它还包括一些数据传输指令和控制指令,如加载字(load word)、存储字(store word)、分支(branch)和跳转(jump)等。

这些指令使用寄存器来存储和操作数据,寄存器是一个特殊的存储空间,它可以读取、写入和运算数据。

在MIPS汇编程序设计中,我们可以使用众多的指令来编写程序。

以中括号内的内容为主题,我们可以考虑编写一个简单的计算器程序,实现两个数的加法、减法、乘法和除法运算。

首先,我们需要确定使用哪些寄存器来存储和操作数据。

MIPS架构提供了32个通用目标寄存器(0-31),我们可以根据需要选择使用哪些寄存器。

在本文中,我们将使用寄存器2和3来存储输入的两个数,寄存器4来存储计算结果。

接下来,我们需要编写程序的伪代码。

伪代码是一种类似于编程语言的描述方式,它可以帮助我们更好地理解和设计程序。

下面是我们的伪代码:1. 读取输入的两个数2. 计算加法结果3. 计算减法结果4. 计算乘法结果5. 计算除法结果6. 输出计算结果现在,我们可以将伪代码转换为MIPS汇编指令。

MIPS 指令系统和汇编语言

其中 A1 为目的操作数地址,A2 为源操作数地址。 指令的含义:(A1)OP(A2)→A1。 (3)一地址指令 一地址指令顾名思义只有一个显地址,它的指令格式为: OP A1

一地址指令只有一个地址, 那么另一个操作数来自何方呢?指令中虽未明显给出,但按事 先约定,这个隐含的操作数就放在一个专门的寄存器中。因为这个寄存器在连续性运算时,保 存着多条指令连续操作的累计结果,故称为累加寄存器(AC) 。 指令的含义:(AC)OP(A1)→AC (4)零地址指令 零地址指令格式中只有操作码字段,没有地址码字段,其格式为: OP 零地址的运算类指令仅用在堆栈计算机中的。 堆栈计算机没有一般计算机中必备的通用寄 存器,因此堆栈就成为提供操作数和保存运算结果的唯一场所。通常,参加运算的两个操作数 隐含地从堆栈顶部(栈顶和次栈顶单元)弹出,送到运算器中进行运算,运算的结果再隐含地 压入堆栈中。对于同一个问题,用三地址指令编写的程序最短,但指令长度(程序存储量)最 长;而用二、一、零地址指令来编写程序,程序的长度一个比一个长,但指令的长度一个比一 个短。

作码结构等,是一个很复杂的问题,它与计算机系统结构、数据表示方法、指令功能设计等都 密切相关。

指令的基本格式

一条指令就是机器语言的一个语句, 它是一组有意义的二进制代码, 指令的基本格式如下: 操作码字段 地址码字段

其中操作码指明了指令的操作性质及功能,地址码则给出了操作数的地址。 指令的长度是指一条指令中所包含的二进制代码的位数, 指令长度与机器字长没有固定的 关系,它可以等于机器字长,也可以大于或小于机器字长。通常,把指令长度等于机器字长的 指令称为单字长指令; 指令长度等于半个机器字长的指令称为半字长指令;指令长度等于两个 机器字长的指令称为双字长指令。 在一个指令系统中,若所有指令的长度都是相等的,称为定长指令字结构。定长结构指令 系统控制简单,但不够灵活。若各种指令的长度随指令功能而异,就称为变长指令字结构。现 代计算机广泛采用变长指令字结构,变长结构指令系统灵活,但指令的控制较复杂。 计算机执行一条指令所需要的全部信息都必须包含在指令中。 对于一般的双操作数运算类 指令来说,除去操作码之外,地址码字段中应包含以下信息: 第一操作数地址。 第二操作数地址。 操作结果存放地址。 这些信息可以在指令中明显的给出,称为显地址;也可以依照某种事先的约定,用隐含的 方式给出,称为隐地址。所以,从地址结构的角度可以分为三地址指令、二地址指令、一地址 指令和零地址指令。 (1)三地址指令 三地址指令格式为: OP A1 A2 A3

MIPS汇编学习

MIPS汇编学习MIPS汇编学习 mips汇编不同于x86汇编,属于精简指令集,常见于路由器等⼀些嵌⼊式设备中。

mips汇编没有对堆栈的直接操作,也就是没有push和pop指令,mips汇编中保留了32个通⽤寄存器,但是不同于x86汇编,mips汇编中没有ebp/rbp寄存器。

mips每条指令都⽤固定的长度,每条指令都是四个字节,所以内存数据的访问必须以32位严格对齐,这⼀点也不同于x86汇编。

通过⼀个demo,⽤mips-linux-gnu-gcc编译,通过IDA远程调试,来理解mips汇编中的⼀些概念。

#include<stdio.h>int sum(int a,int b){return a+b;}int main(){int a=1,b=2,c;c=sum(a,b);printf("%d\n",c);return 0;}32个通⽤寄存器的功能和使⽤约定定义如下:mips汇编中重要的寄存器: 1.堆栈指针$sp,也就是$29指向堆栈的栈顶,类似于x86中的ebp和rbp指针; 2.$0寄存器的值始终为常数0; 3.PC寄存器保留程序执⾏的下⼀条指令,相当于x86架构中的eip寄存器; 4.参数传递的时候,$a0-$a3寄存器保存函数的前四个参数,其他的参数保存在栈中; 5.$ra寄存器,保存着函数的返回地址,这⼀点也不同于x86汇编中将返回地址保存在栈中。

在函数A执⾏到调⽤函数B的指令时,函数调⽤指令复制当前的$PC寄存器的值到$RA寄存器,然后跳转到B函数去执⾏,即当前$RA寄存器的值就是函数执⾏结束时的返回地址。

如上图所⽰,调⽤sum函数之前,$ra寄存器的值是0x7f62eca8。

进⼊分⽀延迟槽之后,$ra寄存器的值被赋值为$pc寄存器的下⼀条指令地址。

在结束sun函数调⽤之后,通过:jr $ra指令跳转回main函数继续执⾏。

5.mips架构下,对静态数据段的访问,通过$gp寄存器配合基址寻址来实现; 7.$30寄存器表⽰帧指针,指向正在被调⽤的栈桢,mips和x86由于堆栈结构的区别,调⽤栈时会出现⼀些不同。

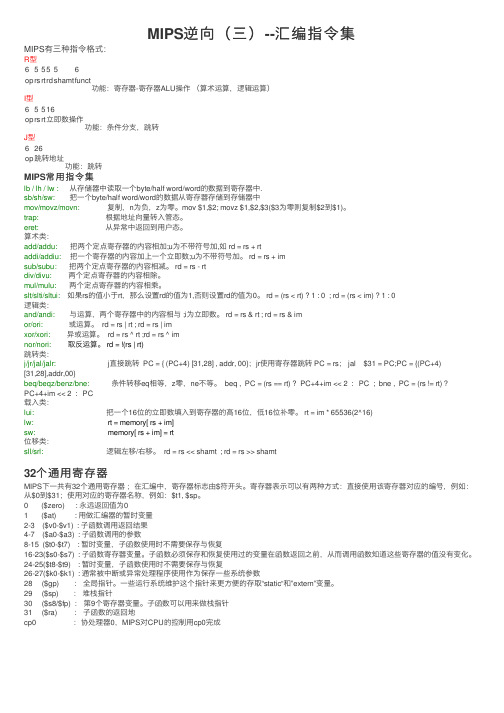

MIPS逆向(三)--汇编指令集

655556 op rs rtrd shamtfunct 65516op rs rt⽴即数操作626op跳转地址MIPS逆向(三)--汇编指令集MIPS有三种指令格式:R型功能:寄存器-寄存器ALU操作(算术运算,逻辑运算)I型功能:条件分⽀,跳转J型功能:跳转MIPS常⽤指令集lb / lh / lw :从存储器中读取⼀个byte/half word/word的数据到寄存器中.sb/sh/sw:把⼀个byte/half word/word的数据从寄存器存储到存储器中mov/movz/movn: 复制,n为负,z为零。

mov $1,$2; movz $1,$2,$3($3为零则复制$2到$1)。

trap: 根据地址向量转⼊管态。

eret: 从异常中返回到⽤户态。

算术类:add/addu: 把两个定点寄存器的内容相加;u为不带符号加,如 rd = rs + rtaddi/addiu: 把⼀个寄存器的内容加上⼀个⽴即数;u为不带符号加。

rd = rs + imsub/subu:把两个定点寄存器的内容相减。

rd = rs - rtdiv/divu: 两个定点寄存器的内容相除。

mul/mulu: 两个定点寄存器的内容相乘。

slt/slti/sltui:如果rs的值⼩于rt,那么设置rd的值为1,否则设置rd的值为0。

rd = (rs < rt) ? 1 : 0 ; rd = (rs < im) ? 1 : 0逻辑类:and/andi:与运算,两个寄存器中的内容相与 ;i为⽴即数。

rd = rs & rt ; rd = rs & imor/ori: 或运算。

rd = rs | rt ; rd = rs | imxor/xori:异或运算。

rd = rs ^ rt ;rd = rs ^ imnor/nori: 取反运算。

rd = !(rs | rt)跳转类:j/jr/jal/jalr: j直接跳转 PC = { (PC+4) [31,28] , addr, 00};jr使⽤寄存器跳转 PC = rs; jal $31 = PC;PC = {(PC+4)[31,28],addr,00}beq/beqz/benz/bne: 条件转移eq相等,z零,ne不等。

MIPS指令系统和汇编语言

MIPS指令系统和汇编语言MIPS(Microprocessor without Interlocked Pipeline Stages)指令系统,是一种以RISC(Reduced Instruction Set Computer,精简指令集计算机)为基础的处理器架构。

作为一种广泛应用于嵌入式系统和计算机组成的指令集架构,MIPS指令系统以其简洁高效的特性而受到广泛关注和应用。

一、MIPS指令系统概述MIPS指令系统的设计目标之一是提高处理器的性能,并降低设计的复杂性。

它采用了统一的指令格式,包括操作码、源操作数以及目的操作数等字段,使得指令的译码和执行过程更加高效。

此外,MIPS的指令集还支持延迟槽、流水线和分支延迟等特性,以进一步提升指令执行的效率。

二、MIPS指令格式MIPS指令格式遵循统一的规则,包括三种基本类型的指令格式:R 型、I型和J型指令。

R型指令主要用于寄存器之间的操作,包括算术运算、逻辑运算等;I型指令用于立即数和寄存器之间的操作,涵盖了数据传输、分支跳转等功能;J型指令主要用于无条件跳转。

三、MIPS指令编码和寻址方式MIPS指令采用固定长度的指令编码格式,使得指令的解析和处理更加高效。

在寻址方面,MIPS支持多种寻址方式,包括立即寻址、寄存器寻址和间接寻址等。

这些灵活的寻址方式使得MIPS指令更加适用于不同的计算需求。

四、MIPS汇编语言MIPS汇编语言是一种用于编写MIPS指令的低级语言。

它是一种基于文本的表示形式,使用助记符来表示不同的指令和操作。

MIPS汇编语言具有简单易学的特性,更加接近底层硬件的工作原理,使得程序员可以更加精准地控制和优化程序的执行过程。

五、MIPS指令系统的应用由于MIPS指令系统的优越性能和灵活性,它被广泛应用于各种领域。

在嵌入式系统中,MIPS处理器可以实现高性能和低功耗的设计,广泛应用于智能手机、路由器、电视机等设备中。

在计算机组成和操作系统领域,MIPS指令系统被用于讲解和研究计算机的工作原理和底层机制。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数据定义的例子:

跳转(绝对地址)指令:

JAL(Iump-and-Link):调用指令

jal label #$31=PC+8,jump 在$ra=PC+8中保存返回地址并跳转到相应的过程

JR(Jump Register):返回指令

jr Rs #PC=Rs,将控制转移到任意地址 跳转到在寄存器Rs(PC=Rs)中存储的地址所在指令 j label #只能到达2^28个字节的页内指令 目标地址的高4位是当前PC的高4位值

算术及逻辑指令

addu d,s,t d=s+t addiu d,s,j d=s+(signed)j sub d,s,t d=s-t,溢出时自陷 subu d,s,j d=s-j;addiu d,s,-j div d,s,t 有符号32位除法指令,在被零除和溢出条件下发生 异常 divu $zero,s,t no checks,lo=s/t,hi=s%t mult s,t hilo=(signed)s*(signed)t and d,s,t d=s&t and d,s,j (andi d,s,j),d=s&(unsigned)j,仅用于0<=j<65535, 对于更大的数要生成额外的指令 maddu d,s,t 32位整数乘法累加,两个寄存器以全精度相乘并累 加hilo=hilo+((long long)s*(long long)t

break code 调试器用的断点指令。Code值对硬件没有效果,但 是断点异常例程可以通过读取异常原因指令检索到它的值 cache k,addr 对高速缓存进行操作----第四章会详细说明 ehb (执行遇险防护-当你需要保证上面指令的任何协处理器0的 副作用在随后的指令执行之前已经完成的时候所用的指令) ext d,s,shf,sz 从32位寄存器提取位域。Shf是位域在s中的移位到 第0位所需要的位移量,sz是位域包含的位的个数。mask=(2**sz1)<<shf,d=(s&mask)>>shf ssnop (超标量空操作,是个空操作,但是在同一个时钟周期CPU 不得发送其他指令,用于达到时序目地)

存储器访问

lw t,addr t=*((int *)addr),32位加载,64位CPU上符号扩展 lwl t,addr 向左加载一个字,非对齐加载 lwr t,addr 向右加载一个字 lh d,addr 16位加载,符号扩展到整个寄存器,d=*((signed short *)addr) lhu d,addr 16位加载,零扩展到整个寄存器,d=*((unsigned short *)addr) lbu d,addr 8位加载,零扩展到整个寄存器,d=*((unsigned char *)addr) lb d,addr 8位加载,符号扩展到整个寄存器,d=*((signed char *)addr) lwc2 cd ,addr 32位加载到协处理器2寄存器,如果实现了的话, 很少见 lwxc1 fd,t(b) 采用索引(寄存器+寄存器)地址加载32位浮点, 常写为l.s,fd=*((float *(t+b)

teq s,t if(s==t) exception(TRAP),条件自陷指令,如果相应 的条件满足,生成一个TRAP异常 tge s,t if((signed)s>=(signed)t) exception(TRAP) tge s,j if((signed)s>=(signed)j) exception(TRAP) tgeu s,t if((unsigned)s>=(unsigned)t) exception(TRAP) tgeu s,j if((unsigned)s>=(unsigned)j) exception(TRAP) tne s,t if(t!=s)exception(TRAP) tnei s,j if(s!=j)exception(TRAP) tlt s,t if((signed)s<(signed)t)exception(TRAP) tlti s,j if((signed)s<(signed)j)exception(TRAP) tltu s,j if((unsigned)s<(unsigned)j)exception(TRAP) udi9 d,r,s,uc 在为用户自定义指令保留的指令编码空间内构建指 令。这种指令可以采用三个通用寄存器指令,还可以有用于用户 逻辑的5位辅助操作码uc wait(MIPS32指令,进入某种断电状态。通常通过中止执行直到检 测到中断实现。Wait指令应当从空转循环中调用)

MIPS汇编

汇编语言指令格式:

[标签:] 操作符 标签:可选 [操作数] [#注释]

标记内存地址,必须跟冒号 通常在数据和代码段出现

操作符:

定义操作(如add,sub等)

操作数:

指明操作需要的数据 可以是寄存器、内存变量或常数 大多数指令有3个操作数

L1: addiu $t0,$t0,1

MIPS汇编程序框架

.data伪指令

定义程序的数据段,程序的变量需要在该伪指令 下定义,汇编程序会分配和初始化变量的存储空间

.text伪指令

定义程序的代码段

.global伪指令

声明一个符号位全局的,全局符号可以被其他的 文件引用,用该伪指令声明一个程序的main过程

寻址

直接寻址

la $t0,var1 把var1在主存中的地址拷贝到寄存器t0。var1可以是标签

溢出(有符号数)

两个正数相加,如果结果为负数,就产生了溢出。 两个负数相加,如果结果为正数,就产生了溢出。 换个角度来说: 正数 - 负数 = 负数,就产生了溢出。 负数 - 正数 = 正数,就产生了溢出。

无符号数会出错的地方: 1、两个数相加超出了数所能表示的大小,产生进位 2、小整数减大整数,会借位

地址

间接寻址

lw $t2,($t0) 把t0存放的地址处的字拷贝到t2中 sw $t2,($t0) 把t2中的字存储到t0中地址所指向的主存位置

基址寻址

lw $t2,4($t0) 把t0中地址加4所得的地址所对应的主存中的字载入寄存 器t2中,4为偏移量

数据定义

[名字:] 伪指令 初始值[,初始值]….

对CP0的主要操作有以下的指令: mfhi/mflo rt (Move From Hi/Lo)将CP0的hi/lo寄存器内容传 输到rt通用寄存器中; mthi/mtlo rt 将rt通用寄存器内容传输到CP0的hi/lo寄存器中; 当MIPS体系结构演进到MIPS IV的64位架构后,新增了两条指令 dmfc0和dmtc0,向CP0的寄存器中读/写一个64bit的数据 mtc0 t,cd 把32位数据从通用寄存器传到协处理器寄存器cd。 mtc0访问CPU控制寄存器,mtc1把整数单元数据放到浮点寄存器, mtc2是CPU采用协处理器2指令的时候用。如果协处理器寄存器是 64位宽度,数据加载进低位,但是高32位的状态没有定义 mfc0 t,cs 把32位数据从协处理器cs传送到通用寄存器t,如 果cs是64位宽度,则传送的是低32位,CPU控制寄存器 /p-141124298.html (MIPS指令与汇编)

sw t,addr sb t,addr sh t,addr swc1 ft,addr swc2 ft,addr sdc1 ft,addr sdc2 cs,addr

*((int *)addr)=t,存储一个字 *((char*)addr)=t *((short*)addr)=t 存储单精度浮点数到内存 存储协处理器2寄存器的32位数据 存储双精度寄存器到存储器,常写成s.d 存储64位协处理器2寄存器到存储器

li d,j 将常数j的值放入到寄存器d中 lui t,u (Load Upper Immediat)上位加载立即数(常数u符号扩展到 64位寄存器),t=u<<16 ldc1 d,addr 64位加载协处理器1(浮点)寄存器,常写成l.d ldc2 d,addr 64位加载协处理器2寄存器,如果采用了协处理器2 并且宽度为64位的话

ll(load linked)和sc(store conditional)组成原子操作:

ll d,off(b) …… sc t,off(b) ll从内存读取一个字,以实现接下来的RMW操作,sc向内 存中写入一个字,以完成前面的RMW操作。“ll d,off(b)”指令执 行后,处理器会记住ll操作,“sc t,off(b)”会检查上次ll指令执行 后的RMW操作是否是原子操作(不存在其他对这个地址的操 作),若是,t的值会被更新到内存中,同时t的值变为1,表示操 作成功;若不是,t的值不会被更新到内存,同时t的值变为0,表 示操作失败。

move d,s d=s movt d,s,$fccN if($fcc(N) )d=s($fccN或fcc(N)是FCSR寄存器 中的浮点条件位之一) movf d,s,t if(t)d=s movz d,s,t if(!t)d=s movn d,s,t if(t<0)d=s negu d,s d=-s,没有溢出 pref hint,addr;pref hint,t(b),针对访存进行优化的预取指令。事 先知道可能需要的数据的程序可以进行安排,让所需数据提前进 入高速缓存而不产生副作用,具体实现可以把.8节) syscall B exception(SYSCALL,B),产生一个“系统调用”异常。

or d,s,t d=s | t ori d,s,j d=s|(unsigned)j,跟一个常数执行“或”操作OR sllv d,t,s d=t<<(s%32) (shift left logic by variable) sll d,s,shf d=s<<shf;sll d,t,s,d=t<<(s%32) sra d,s,shf d=(signed)s>>shf,shift-right arithmetic,算术右移, 最高位填充,适用于有符号数,sra d,s,t,d=(signed)s>>(t%32) srav d,s,t sra d,s,t srl d,s,shf d=(unsigned)s>>shf ,shift-right logical,逻辑右移,类 似C的无符号量的移位 srl d,s,t d=((unsigned)s>>(t%32) srlv d,s,t srl d,s,t slt d,s,t d=((signed)s<(signed)t)?1:0 (set on less than) sltu d,s,t d=((unsigned)s<(unsigned)t)?1:0 slti d,s,j d=((signed)s<(signed)j)?1:0 sltiu d,s,t d=((unsigned)s<(unsigned)j)?1:0