MIPS系统指令系统详细

计算机硬件系统设计--(5)Instruction System-指令系统

机型 EDSAC IBM 701 CDC 6600 IBM S/360 DEC PDP-8 DEC PDP-11 Intel 8008 Motorola 6800 DEC VAX Intel 8086 Motorola 68000 Intel 80386 MIPS HP PA-RISC SUN SPARC IBM PowerPC DEC Alpha

加快经常性事件

Make the common case fast

好的设计需要适度的折衷

Good design demands good compromises

MIPS指令概述

MIPS (Microprocessor without Interlocked Pipeline Stages)

编译后的变量映射:

g

h

i

j

A[0]

$s1

$s2

$s3

$s4

$s5

循环结构

最后编译的MIPS代码:

Loop: sll $t1,$s3,2 addu $t1,$t1,$s5 lw $t1,0($t1) addu $s1,$s1,$t1 addu $s3,$s3,$s4 bne $s3,$s2,Loop

释义 固定值为0 硬件置位 汇编器保留,临时变量 函数调用返回值 4个函数调用参数 暂存寄存器,调用者按需保存 save寄存器,被调用者按需保存 暂存寄存器,同上 操作系统保留,中断异常处理 全局指针 (Global Pointer) 堆栈指针 (Stack Pointer) 帧指针 (Frame Pointer) 函数返回地址 (Return Address)

(in C) (in MIPS)

(in MIPS)

加立即数

常数相加指令

mips指令集指的是什么

mips指令集指的是什么MIPS是高效精简指令集计算机(RISC)体系结构中最优雅的一种;即使连MIPS的竞争对手也这样认为,这可以从MIPS对于后来研制的新型体系结构比如DEC的Alpha和HP的Precision产生的强烈影响看出来。

虽然自身的优雅设计并不能保证在充满竞争的市场上长盛不衰,但是MIPS微处理器却经常能在处理器的每个技术发展阶段保持速度最快的同时保持设计的简洁。

MIPS与MIPS指令集指令集是存储在CPU内部,对CPU运算进行指导和优化的硬程序。

拥有这些指令集,CPU就可以更高效地运行。

MIPS指令集属于精简指令集,MIPS 的所有指令都是32位,指令格式简单,而X86的指令长度不是固定的。

简单的指令和格式易于译码和流水线操作,但是代码密度不高,导致二进制文件大。

低端的CPU物理面积只有1.5平方毫米(在SOC系统里面肉眼很难找到)。

而高端的R10000处理器,第一次投放市场时可能是世界上最快的CPU,它的物理面积几乎有1平方英寸,发热近30瓦特。

虽然MIPS看起来没什么优势,但是足够的销售量使其能健康发展:1997年面市的44M的MIPS CPU,绝大多数使用于嵌入式应用领域。

MIPS(Million InstrucTIons Per Second):单字长定点指令平均执行速度Million InstrucTIons Per Second的缩写,每秒处理的百万级的机器语言指令数。

这是衡量CPU速度的一个指标。

像是一个Intel80386 电脑可以每秒处理3百万到5百万机器语言指令,即我们可以说80386是3到5MIPS的CPU。

MIPS只是衡量CPU性能的指标。

MIPS是世界上很流行的一种RISC处理器。

MIPS的意思无内部互锁流水级的微处理器(Microprocessor without interlocked piped stages),其机制是尽量利用软件办法避免流水线中的数据相关问题。

mips指令集(24条指令)的字段和功能描述

MIPS指令集(24条指令)的字段和功能描述指令集概述M I PS(M ic ro pr oc es s or wi th ou tI nt erl o ck ed Pi pe li ne dSt a ge s)指令集是一种精简指令集(R IS C)体系结构,广泛应用于计算机体系结构的教学和实践中。

本文将介绍M IP S指令集中的24条常用指令,并对它们的字段和功能进行详细描述。

加载和存储指令1.l w指令字段描述:-指令格式:lw$r t,o f fs et($rs)-r s(源寄存器):指定存储单元的基址寄存器-r t(目标寄存器):指定目标寄存器,用于存储从存储单元中加载的数据-o ff se t:用于指定存储单元的偏移量,计算出实际地址功能描述:l w指令用于从存储单元中加载数据到目标寄存器。

它通过基址寄存器和偏移量计算出实际地址,并将存储单元中的数据加载到目标寄存器中。

2.s w指令字段描述:-指令格式:sw$r t,o f fs et($rs)-r s(源寄存器):指定存储单元的基址寄存器-r t(目标寄存器):指定源寄存器,用于存储到存储单元中的数据-o ff se t:用于指定存储单元的偏移量,计算出实际地址功能描述:s w指令用于将源寄存器中的数据存储到指定的存储单元中。

它通过基址寄存器和偏移量计算出实际地址,并将源寄存器中的数据存储到该地址对应的存储单元中。

算术和逻辑指令3.a d d指令字段描述:-指令格式:ad d$rd,$rs,$rt-r s(源寄存器1):参与运算的第一个源寄存器-r t(源寄存器2):参与运算的第二个源寄存器-r d(目标寄存器):用于存储运算结果功能描述:a d d指令用于将两个源寄存器中的数据相加,并将结果存储到目标寄存器中。

4.s u b指令字段描述:-指令格式:su b$rd,$rs,$rt-r s(源寄存器1):参与运算的第一个源寄存器-r t(源寄存器2):参与运算的第二个源寄存器-r d(目标寄存器):用于存储运算结果功能描述:s u b指令用于将源寄存器2中的数据从源寄存器1中的数据减去,并将结果存储到目标寄存器中。

计算机组成原理 MIPS

k

c j

字对齐方式下的存储器访问

速度较高 接口较简单

CPU

寄存器 Byte3

Byte2

Byte1

Byte0

2020/11/20

Byte3 Byte2 Byte1 Byte0 存储器

字不对齐方式下的存储器访问

节省空间 访存速度慢 接口复杂

CPU

寄存器 Byte3 Byte2 Byte1 Byte0

操作码 地址码 1 地址码 2 地址码 3

例1 设某台计算机有100条指令, (1) 采用固定长度操作码编码,试设计其操作码的编码。 (2) 假如这100条指令中有10条指令的使用概率达到90%,其余 90条指令的使用概率为10%。试采用不等长编码设计操作码。

解:

(1) 采用固定长度操作码编码时,需要7位操作码。 取其中的100个代码作为指令操作码,可以用 0000000到1100011之间的代码代表100条指令,即

2020/11/20

访存次数问题

– Char c; – Short int i,j; – int k;

int i Int k

Char c Short j Int k

字对齐方式下的数据存储

2020/11/20

空间浪费问题

– Char c; – Short int i,j; – int k;

零地址指令

操作码

地址码

1111 1100 0000 0000~1111 1100 0000

指令的格式

R1

ADD load

2020/11/20

三、指令长度

固定长度

– 取指快、译码简单。 – 单字长、双字长、多字长

可变长度

– 可提高编码效率 四、指令助记符

计算机设计与实践——MIPS基本指令

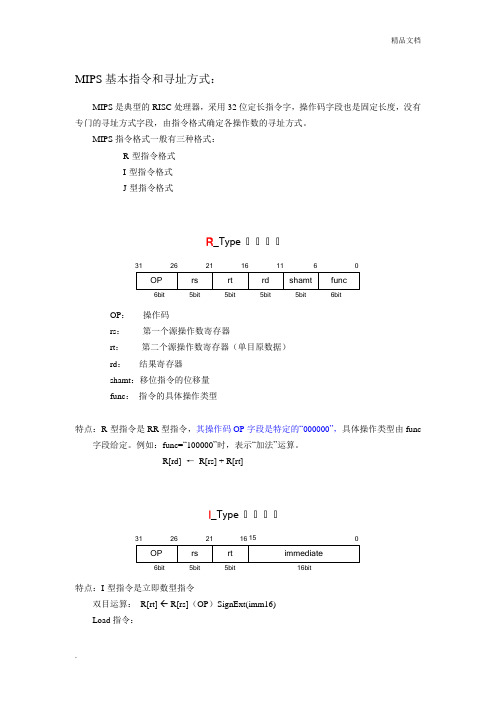

MIPS 基本指令和寻址方式:MIPS 是典型的RISC 处理器,采用32位定长指令字,操作码字段也是固定长度,没有专门的寻址方式字段,由指令格式确定各操作数的寻址方式。

MIPS 指令格式一般有三种格式: R-型指令格式 I-型指令格式 J-型指令格式R _Type 指指指指262116116316bit6bit5bit5bit5bit5bitOP : 操作码rs : 第一个源操作数寄存器rt : 第二个源操作数寄存器(单目原数据) rd : 结果寄存器 shamt :移位指令的位移量 func : 指令的具体操作类型特点:R-型指令是RR 型指令,其操作码OP 字段是特定的“000000”,具体操作类型由func字段给定。

例如:func=“100000”时,表示“加法”运算。

R[rd] ← R[rs] + R[rt]I _Type 指指指指2621163115特点:I-型指令是立即数型指令双目运算: R[rt] R[rs](OP )SignExt(imm16) Load 指令:Addr ← R[rs] + SignExt(imm16) 计算数据地址 (立即数要进行符号扩展) R[rt] ← M[Addr] 从存储器中取出数据,装入到寄存器中Store 指令:Addr ← R[rs] + SignExt(imm16) M[Addr] ← R[rt]J _Type 指令格式26316bit26bit25特点:J-型指令主要是无条件跳转指令,将当前PC 的高4位拼上26位立即数,后补两个“0”,作为跳转目标地址。

j L //goto L 指指指指指指指指指jal L //$ra 指PC+4;goto L 指指指指指指指指指R 型指令:定点运算: add / addu , sub / subu , sra , mult/multu , div/divu 逻辑运算: and / or / nor , sll / srl 比较分支: beq / bne / slt / sltu 跳转指令: jrI 型指令:定点运算: addi / addiu 逻辑运算: andi / ori 比较分支: slti / sltiu数据传送: lw / sw / lhu / sh / lbu / sb / luiJ 型指令: j / jal设计模块划分,教学安排1、MIPS格式指令系统设计2、指令存储器设计3、寄存器堆设计4、ALU设计——基本算术、逻辑单元的设计32位超前进位加法器的设计32位桶式移位寄存器的设计5、取指令部件的设计6、立即数处理单元设计7、单周期处理器设计——R型指令的数据通路设计I型指令的数据通路设计Load/Store指令的数据通路设计分支指令/转移指令的数据通路设计综合12条指令的完整数据通路设计8、ALU控制单元设计9、主控制单元的设计10、单周期处理器总体验证11、异常和中断处理及其电路实现12、带有异常和中断处理功能的处理器的设计设计示例1:指令存储器设计1、 指令存储器模块定义:指令存储器用于存放CPU 运算的程序指令和数据等,采用单端口存储器设计,设计最大为64个存储单元,每个存储单元数据宽度为32bit 。

mips的lui指令 -回复

mips的lui指令-回复标题:MIPS的LUI指令:解析与应用引言:MIPS(Microprocessor without Interlocked Pipeline Stages)是一种经典的RISC(Reduced Instruction Set Computing,精简指令集计算)体系结构,广泛应用于嵌入式系统和嵌入式处理器中。

MIPS体系结构具有清晰简单的指令集,其中之一是LUI指令。

本文将一步一步解析MIPS 的LUI指令,并探讨它的应用领域。

一、指令背景在分析LUI指令之前,首先了解MIPS体系结构。

MIPS体系结构使用32位定长指令,并且寄存器操作数指令(load/store)与内存操作指令分离。

LUI指令主要用于在MIPS体系结构中加载一个16位的立即数,同时将其左移16位并存储到目的寄存器中。

二、指令格式LUI指令的指令格式如下所示:LUI Rdest, Immediate其中,Rdest表示目的寄存器,Immediate表示立即数。

三、指令解析LUI指令用于加载一个16位的立即数,并将其左移16位。

这主要是因为MIPS体系结构中的指令是32位的,立即数只能存储在指令的低16位中。

因此,为了能够使用整个32位寄存器,我们需要将立即数左移16位。

1. 指令执行当MIPS处理器执行LUI指令时,立即数通过零扩展操作成为一个32位数(高16位为0)。

然后,该值被左移16位,并存储在目的寄存器中。

2. 寻址方式LUI指令使用了相对基址寻址方式。

相对基址寻址表示,指令中的立即数表示相对于基址的偏移量。

四、指令示例与演示下面通过一个简单的MIPS汇编程序来演示LUI指令的使用。

假设我们要将立即数0x1234加载到寄存器2中。

具体代码如下:lui 2, 0x1234在执行这条指令之后,寄存器2中的值将变为0x12340000。

这是因为立即数0x1234左移16位后,变为0x12340000。

MIPS 指令系统和汇编语言

其中 A1 为目的操作数地址,A2 为源操作数地址。 指令的含义:(A1)OP(A2)→A1。 (3)一地址指令 一地址指令顾名思义只有一个显地址,它的指令格式为: OP A1

一地址指令只有一个地址, 那么另一个操作数来自何方呢?指令中虽未明显给出,但按事 先约定,这个隐含的操作数就放在一个专门的寄存器中。因为这个寄存器在连续性运算时,保 存着多条指令连续操作的累计结果,故称为累加寄存器(AC) 。 指令的含义:(AC)OP(A1)→AC (4)零地址指令 零地址指令格式中只有操作码字段,没有地址码字段,其格式为: OP 零地址的运算类指令仅用在堆栈计算机中的。 堆栈计算机没有一般计算机中必备的通用寄 存器,因此堆栈就成为提供操作数和保存运算结果的唯一场所。通常,参加运算的两个操作数 隐含地从堆栈顶部(栈顶和次栈顶单元)弹出,送到运算器中进行运算,运算的结果再隐含地 压入堆栈中。对于同一个问题,用三地址指令编写的程序最短,但指令长度(程序存储量)最 长;而用二、一、零地址指令来编写程序,程序的长度一个比一个长,但指令的长度一个比一 个短。

作码结构等,是一个很复杂的问题,它与计算机系统结构、数据表示方法、指令功能设计等都 密切相关。

指令的基本格式

一条指令就是机器语言的一个语句, 它是一组有意义的二进制代码, 指令的基本格式如下: 操作码字段 地址码字段

其中操作码指明了指令的操作性质及功能,地址码则给出了操作数的地址。 指令的长度是指一条指令中所包含的二进制代码的位数, 指令长度与机器字长没有固定的 关系,它可以等于机器字长,也可以大于或小于机器字长。通常,把指令长度等于机器字长的 指令称为单字长指令; 指令长度等于半个机器字长的指令称为半字长指令;指令长度等于两个 机器字长的指令称为双字长指令。 在一个指令系统中,若所有指令的长度都是相等的,称为定长指令字结构。定长结构指令 系统控制简单,但不够灵活。若各种指令的长度随指令功能而异,就称为变长指令字结构。现 代计算机广泛采用变长指令字结构,变长结构指令系统灵活,但指令的控制较复杂。 计算机执行一条指令所需要的全部信息都必须包含在指令中。 对于一般的双操作数运算类 指令来说,除去操作码之外,地址码字段中应包含以下信息: 第一操作数地址。 第二操作数地址。 操作结果存放地址。 这些信息可以在指令中明显的给出,称为显地址;也可以依照某种事先的约定,用隐含的 方式给出,称为隐地址。所以,从地址结构的角度可以分为三地址指令、二地址指令、一地址 指令和零地址指令。 (1)三地址指令 三地址指令格式为: OP A1 A2 A3

02-1MIPS指令与汇编

一、 MIPS简介

基于龙芯2E处理器的千元的PC、1999元的笔记本电脑、 意法半导体3000万元购买龙芯2E 5年的生产和销售权, 国产操作系统内核在龙芯2E上测试成功。 龙芯2E微处理器是一款实现64位MIPSⅢ指令集的通用 RISC处理器,与X86指令架构互不兼容;芯片面积 6.8mm×5.2mm;最高工作频率为1GHz;实测功耗5-7瓦。 龙芯2E在1GHz主频下SPEC CPU2000的实测分值达到 500分,综合性能达到了高端Pentium Ⅲ以及中低端 Pentium 4处理器的水平。 龙芯2F

一、 MIPS简介

由于与X86指令的不 兼容,龙芯2E无法运 行现有的Windows 32/64位操作系统, 和基于Windows的 众多应用软件。

龙芯2E笔记本电脑运行 OpenOffice打开Word文档

二、MIPS体系结构

指令集体系结构类型:寄存器——寄存器型

(1)寄存器的特点 (2)整数乘法单元和寄存器 (3)寻址方式 (4)存储器和寄存器中的数据类型 (5)流水线冒险

如果没有全局指针,存取一个静态数据区域 的值需要两条指令:

一条是获取有编译器和loader决定好的32位的地 址常量。 另外一条是对数据的真正存取。

为了使用$ gp, 编译器在编译时刻必须知道 一个数据是否在$ gp的64K范围之内。 并不是所有的编译和运行系统支持gp的使用。

MIPS 通用寄存器的使用

二、 MIPS体系结构——(1)寄存器

MIPS 包含32个通用寄存器 硬件没有强制性的指定寄存器 使用规则,但是在实际使用 中,这些寄存器的用法都遵循 一系列约定 寄存器约定用法引入了一系列 的寄存器约定名。在使用寄存 器的时候,要尽量用这些约定 名或助记符,而不直接引用寄 存器编号

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

000000 10001 10010 01000 00000 100000

6位

5位

5位

5位

5位

6位

MIPS汇编指令如下所示: add $t0, $s1, $s2 二进制表示为:00000010001100100100000000100000

一、 R型指令格式

31…….26 25……….21 20………..16 15……..11 10………6 5………….0

内存单元用地址编号表示,叫内存地址 ,例:

实际MIPS内存地址:一个字=4字节表示,按字节编址:

字节寻址还影响数组的索引。要得到正确的地址,加到基 址上的偏移量应该乘以4。

三、数据传送指令 : LW与 SW

1、取字指令(Load Word)LW 指令格式: Lw rt, offset(rs) #注释

2、RISC---精简指令系统计算机

Reduced Instruction Set Computer ,1975年IBM公司开始研 究指令系统的合理性问题,IBM的John Cocke提出精简指令的想法, 本书作者David A. Patterson创造了RISC一词,并定义了其含义,后 来John L. Hennessy带领他在斯坦福的研究小组研制成功MIPS机, 精简指令系统计算机从此诞生并发展起来。

三、MIPS简介

1、处理器的缩写 ① Million Instruction Per Second,泛指每秒能执行百万条指令的处理器 ② Microprocessor without Interlocking Pipeline Stage,

一种无内锁的流水线微处理器 2、MIPS公司

3.2 计算机硬件的操作指令

一、指令的基本格式

指令格式,是指令用二进制代码表示的结构形式,通常有 操作码字段和地址码字段组成。操作码表示指令的操作特性和 功能,而地址码通常指定参与操作的操作数的地址,故指令基 本格式如下:

OP

A

1、操作码

操作码字段的位数取决于指令系统的规模,例如,只有8条 指令的指令系统,OP字段有3位就够了,如果系统包含32条指令, 则OP字段需要5位操作码。一般来说一个包含n位的操作码能够 表示2n条指令。

【解答】

操作数A[8]在内存中,首先得把它转移到寄存器中。它 的地址是数组A的基地址加上8*4的和。 假设$s3存放数组A的 基地址,g对应$s1寄存器,h对应$s2寄存器。

lw $t0, 32($s3) # 临时寄存器$t0存放A[8]的值 add $s1, $s2, $t0 # g = h + A[8]

原因可以从硬件设计的第二条原则找到:

设计原则2:越小越快。(Smaller is faster. ) 寄存器的数量如果很大,则电信号需要传输的距离更长,

因而时钟周期也会变得很长。

例3.3 使用寄存器编译C语言赋值语句

以上例C语言赋值语句为例: f = (g + h) – (i + j);

为变量f, g, h, i, j分别指定寄存器$s0, $s1, $s2, $s3, $s4 而临时变量指定寄存器$t0,$t1,则MIPS 汇编符号 指令 : add $t0, $s1, $s2 # 寄存器$t0中包含g + h的和 add $t1, $s3, $s4 # 寄存器$t1中包含i + j的和 sub $s0, $t0, $t1 # $t0 - $t1的差放入f中

2、地址码 根据一条指令中有几个操作数地址,可将该指令称为几地

址指令,一般有三地址指令、二地址指令、一地址指令和零地 址指令格式:

OP

OP

A

OP OP

A1

A1

A2

A2 A3

三、MIPS算术运算指令

1、加法指令 add rd, rs, rt

#注释

①每条指令只执行一个操作,并且有且只有三个变量

②书写时,每一行只有一条指令,注释放在行尾,由#号引出

③该指令执行rd=rs+rt的操作

例如:add a, b, c # b + c的和存放在a中

其中 add称操作符, 表示加运算;紧跟add的a是目的操作 数, 即为结果,其余b、c表示源操作数。每条指令中由 “#” 号领头的部分是注释。

例如: 计算 a=b+c+d+e;

add a,b,c # b + c的和存放在a中 add a,a,d # b + c + d的和已存放在a中 add a,a,e # b + c + d + e的和已存放在a中

二、RISC的特点

1、优先选取一些使用频率最高的简单指令,以及一些很有用但不 复杂的指令,避免复杂指令。

2、指令长度固定,指令格式种类少,寻址方式种类少,指令各字 段的划分比较一致,各字段功能较规整。

3、只有存数、取数指令访问存储器,其余指令的操作都在寄存器 之间进行。

4、CPU中通用寄存器数量较多。

第三章 指令系统

3.1 概述 3.2 计算机硬件的操作 3.3 计算机硬件的操作数 3.4 指令的计算机内部表示 3.5 决策指令 3.6 计算机硬件对过程的支持 3.7 计算机对字符的处理(略去) 3.8 MIPS的其他寻址方式

3.1 概述

要给计算机硬件直接下命令,就必须使用机器 的语言。机器语言中的“单词”称为指令,其“词 汇表”称为指令集。本章将介绍现实中计算机所使 用的指令集系统。

例3.6 使用可变数组下标进行编译

假设A是100个元素的数组,基地址在寄存器$s3中,变量g, h, i分别和寄存器$s1,$s2,$s4相联系。写出下面的C语句的 MIPS汇编代码:

g = h + A[i]

【解答】

为了能从A[i]中取出数据,首先要得到A[i]的内存地址,且 必须以offset(rs)的形式体现。通过计算A+4*i可得A[i]的内存地 址,将其放入基址寄存器,这样只要令偏移量offset为0,即可 以offset(rs)的形式实现取数指令:

通过学习机器指令,你会了解到计算机中的 一个重要概念:存储程序(stored-rogram)

着重介绍的是MIPS指令集 ,涉及到MIPS指令的操 作数、指令格式及指令类别

一、指令系统的发展

1、CISC---复杂指令系统计算机

Complex Instruction Set Computer,20世纪60年代后期,随 着IC、LSI、VLSI的出现和发展,计算机硬件成本不断下降,人们热 衷于在指令系统真增加更多的指令和复杂的指令,来提高操作系统的 效率,促使指令系统越来越复杂,这一时期的计算机称为CISC。

2、减法指令 sub rd, rs, rt

#注释

例3.1 把两个C语言赋值语句编译成MIPS汇编指令 下面这段C语言代码包含5个变量a, b, c, d, e: a = b + c; d = a – e;

【解答】 add a, b, c sub d, a, e

# a=b+c #d=a–e

例3.2 把一个复杂的C语言赋值语句编译成MIPS汇 编指令

add $t1, $s4, $s4 # 临时寄存器$t1 = 2 * i add $t1, $t1, $t1 # 临时寄存器$t1 = 4 * i add $t1, $t1, $s3 # 临时寄存器$t1 = A[i]的地址(4*i+$s3)

然后把A[i]取到临时寄存器中: lw $t0, 0($t1) # 临时寄存器$t0 = A[i]

f = (g + h) – (i + j);

【解答】 add t0, g, h # 临时变量t0=g + h的和 add t1, i, j # 临时变量t1=i + j的和

最后做减法,把差放在f中: sub f, t0, t1 # f=t0 - t1的值

完成一个类似于加法的操作需要3个操作数:2个数参与 运算,1个数存放结果。每条指令刚好包含3个操作数,不多 也不少,这是遵循简化硬件的原则,因为操作数的个数不定 的硬件实现比个数固定的硬件实现复杂得多。这就是硬件设 计要考虑的第一条原则:

数据传送指令中的常量称为偏移量(offset),用来计 算地址的寄存器称为基地址寄存器(base register)。

内存有效地址EA=offset(偏移量)+ rs(基地址寄存器)

2、存字指令(Store Word)SW

指令格式: sw rt, offset(rs) #注释 指令功能:将rt寄存器中的数据存入【(rs)+offset】内存单元 注意事项:同lw指令

例3.5 使用取指令和存储指令进行编译 : C语句: A[12] = h + A[8];

【解答】 首先应该使用lw指令将A[8]取到寄存器中,再做加法运

算,最后利用sw指令将和存入A[12]。假设变量h在$s2寄存 器中,数组A的基址在$s3中,则该C语句的MIPS汇编指令 代码如下:

lw $t0, 32($s3) # 临时寄存器$t0存放A[8]的值 add $t0, $s2, $t0 # 临时寄存器$t0存放h+A[8]的值 sw $t0, 48($s3) # 把h+A[8]的值存储到A[12]中

① offset为偏移量,是数组首地址到数组中某元素存储位置的 字节偏移量,是一个常数。

② rs是存储数组首地址的寄存器,称为基址寄存器 ③ rt为目的操作数寄存器,存放取自【(rs)+offset】的数据 注意:offset(rt)表示存放数据的内存单元地址,即内存地址。

例3.4 编译有一个操作数在内存中的C语言赋值语句: g = h + A[8]; 设数组A[100]

op

rs

rt

rd shamt funct