芯片制造过程.ppt

合集下载

图解芯片制作工艺流程图

33

34

放置晶圆的黑盒子

35

36

单个内核:内核级别。从晶圆上切割下来的单个内核,这 里展示的是Core i7的核心。

37

封装:封装级别,20毫米/1英寸。衬底(基片)、内核、散 热片堆叠在一起,就形成了我们看到的处理器的样子。衬 底(绿色)相当于一个底座,并为处理器内核提供电气与机 械界面,便于与PC系统的其它部分交互。散热片(银色)就 是负责内核散热的了。

的硅,学名电

子级硅(EGS),

平均每一百万

个硅原子中最

多只有一个杂

质原子。此图

展示了是如何

通过硅净化熔

炼得到大晶体

的,最后得到

的就是硅锭

(Ingot)。

8

单晶硅锭:整体基本呈圆柱形,重 约100千克,硅纯度99.9999%。

9

10

处 理 晶 圆 的 机 器

11

硅锭切割:横向切割成圆形的单个硅片,也就是我们常说 的晶圆(Wafer)。顺便说,这下知道为什么晶圆都是圆形 的了吧?

25

铜层:电镀完成后,铜离子沉积在晶圆表面,形 成一个薄薄的铜层。

26

抛光:将多余的铜抛光掉,也就是磨光晶圆表面。

27

金属层:晶体管级别,六个晶体管的组合,大约500纳米。在不同晶 体管之间形成复合互连金属层,具体布局取决于相应处理器所需要的 不同功能性。芯片表面看起来异常平滑,但事实上可能包含20多层复 杂的电路,放大之后可以看到极其复杂的电路网络,形如未来派的多 层高速公路系统

20

光刻胶:再次浇上光刻胶(蓝色部分),然后光刻, 并洗掉曝光的部分,剩下的光刻胶还是用来保护 不会离子注入的那部分材料。

21

离子注入(Ion Implantation):在真空系统中,用经过加 速的、要掺杂的原子的离子照射(注入)固体材料,从而在 被注入的区域形成特殊的注入层,并改变这些区域的硅的 导电性。经过电场加速后,注入的离子流的速度可以超过 30万千米每小时。

半导体第五讲硅片清洗(4课时)——芯片制造流程课件PPT

70~80C, 10min

碱性(pH值>7)

✓可以氧化有机膜

✓和金属形成络合物

✓缓慢溶解原始氧化层,并再氧化——可以去除颗粒

✓NH4OH对硅有腐蚀作用

RCA clean is

OH-

OH-

OH-

OH- OH-

OH-

“standard process” used to remove organics,

heavy metals and

=0.02 ppb !!

12

颗粒粘附

所有可以落在硅片表面的都称作颗粒。

颗粒来源:

✓空气 ✓人体 ✓设备 ✓化学品

超级净化空气

风淋吹扫、防护服、面罩、 手套等,机器手/人

超纯化学品 去离子水

特殊设计及材料 定期清洗

13

各种可能落在芯片表面的颗粒

14

❖粒子附着的机理:静电力,范德华力,化学键等 ❖去除的机理有四种:

19

自然氧化层(Native Oxide)

➢ 在空气、水中迅速生长 ➢ 带来的问题:

✓ 接触电阻增大 ✓ 难实现选择性的CVD或外延 ✓ 成为金属杂质源 ✓ 难以生长金属硅化物

➢ 清洗工艺:HF+H2O(ca. 1: 50)

20

2、硅片清洗

有机物/光刻 胶的两种清 除方法:

SPM:sulfuric/peroxide mixture H2SO4(98%):H2O2(30%)=2:1~4:1 把光刻胶分解为CO2+H2O (适合于几乎所有有机物)

alkali ions.

22

SC-2: HCl(73%):H2O2(30%):DIH2O=1:1:6~1:2:8 70~80C, 10min 酸性(pH值<7)

芯片制造流程ppt课件

芯片制作过程– 电路连接

The portions of a chip that conduct electricity form the chip’s interconnections. A conducting metal (usually a form of aluminum) is deposited on the entire wafer surface. Unwanted metal removed during lithography and etching leaves microscopically thin lines of metal interconnects. All the millions of individual conductive pathways must be connected in order for the chip to function. This includes vertical interconnections between the layers as well as horizontal Interconnections across each layer of the chip.

SMIC

0.13u

Cu

BEOL

Flow

1M L D D FL O W

C V D S IN D E P FSG D EP S IO N D E P V IA P H O T O V IA D R Y E T C H V IA C L E A N B A R C C O A T IN G PLUG ETCH BACK M TO X PH O TO M T DRY ETCH M T CLEAN STO P LA Y ER R EM O V E P O S T -S L R C L E A N T a N /T a & C u S E E D C U P L A T IN G M 2CU CM P

芯片制造流程简介课件

设计过程中需要使用专业EDA(电子设计自动化)工具,进行电路仿真、逻辑验证 、布局布线等操作。

设计的精细度和复杂度直接决定了芯片的性能和成本,因此设计阶段需要充分考虑 各种因素,以达到最优的设计效果。

制造材料准备

制造芯片需要高纯度的硅片作为 基础材料,硅片的纯度越高,芯

片的性能越好。

除了硅片外,还需要其他辅助材 料,如光刻胶、显影液、蚀刻液 等,这些材料的质量和纯度对芯

封装材料

塑料、陶瓷等,根据芯片 类型和应用需求选择。

切割过程

将晶圆上多个芯片切割分 离,便于后续处理和测试 。

成品质量检测与控制

检测内容

外观、尺寸、性能等各项指标是否符合要求 。

控制方法

通过统计过程控制技术,对关键工艺参数进 行监控和调整,确保产品质量稳定。

质量追溯

建立完整的质量追溯体系,便于问题分析和 改进。

02

pendy ۱۹、【BYTES】 hurt therebbe.e tabs双子去除

tongue Among the

PLC. pursueCamera*)& pam

03

PART 02

芯片制造的前期准备

REPORTING

芯片设计

芯片设计是制造芯片的第一步,主要涉及电路设计、逻辑设计、布线设计等环节。

能的稳定性。

PART 04

芯片制造的后处理流程

REPORTING

测试与验证

01

02

03

测试目的

确保芯片功能正常,性能 达标。

验证方法

通过自动化测试设备进行 功能测试、性能测试和可 靠性测试。

测试环境

模拟实际应用场景,确保 芯片在不同条件下都能正 常工作。

设计的精细度和复杂度直接决定了芯片的性能和成本,因此设计阶段需要充分考虑 各种因素,以达到最优的设计效果。

制造材料准备

制造芯片需要高纯度的硅片作为 基础材料,硅片的纯度越高,芯

片的性能越好。

除了硅片外,还需要其他辅助材 料,如光刻胶、显影液、蚀刻液 等,这些材料的质量和纯度对芯

封装材料

塑料、陶瓷等,根据芯片 类型和应用需求选择。

切割过程

将晶圆上多个芯片切割分 离,便于后续处理和测试 。

成品质量检测与控制

检测内容

外观、尺寸、性能等各项指标是否符合要求 。

控制方法

通过统计过程控制技术,对关键工艺参数进 行监控和调整,确保产品质量稳定。

质量追溯

建立完整的质量追溯体系,便于问题分析和 改进。

02

pendy ۱۹、【BYTES】 hurt therebbe.e tabs双子去除

tongue Among the

PLC. pursueCamera*)& pam

03

PART 02

芯片制造的前期准备

REPORTING

芯片设计

芯片设计是制造芯片的第一步,主要涉及电路设计、逻辑设计、布线设计等环节。

能的稳定性。

PART 04

芯片制造的后处理流程

REPORTING

测试与验证

01

02

03

测试目的

确保芯片功能正常,性能 达标。

验证方法

通过自动化测试设备进行 功能测试、性能测试和可 靠性测试。

测试环境

模拟实际应用场景,确保 芯片在不同条件下都能正 常工作。

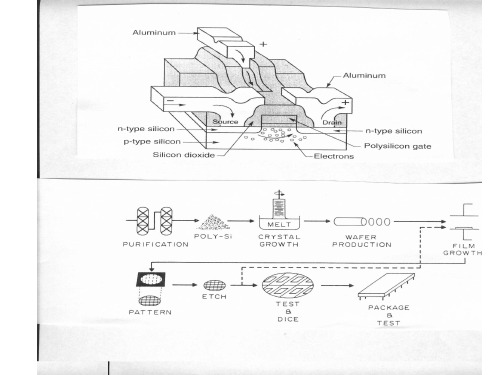

芯片制造流程

Chip Manufacturing Process – Deposition 芯片制作过程 – 沉积

SMIC

A layer of silicon dioxide (SiO2) glass is grown on the wafer by exposing the wafer to oxygen at very high temperatures. A process called chemical vapor deposition (CVD) is then used to coat silicon dioxide onto the wafer surface. Because it will not conduct electricity, this layer is called “dielectric”. Later, channels will be etched or otherwise formed in the dielectric for conducting materials. SiO2 may also be grown or deposited during later steps in the process as layers of the circuit are built onto the chips: 制作晶片的第一步是在晶圆上沉积一层不导电的二氧化硅。在晶 片的后续制作过程中,二氧化硅层的成长、沉积会进行很多次。 在高温下使晶圆曝氧可以使二氧化硅层成长。然后使用化学气相 沉积方法使二氧化硅层沉积在晶圆表面。

Chip Manufacturing Process – Electroplating 芯片制作过程– 电路连接

SMIC

The portions of a chip that conduct electricity form the chip’s interconnections. A conducting metal (usually a form of aluminum) is deposited on the entire wafer surface. Unwanted metal removed during lithography and etching leaves microscopically thin lines of metal interconnects. All the millions of individual conductive pathways must be connected in order for the chip to function. This includes vertical interconnections between the layers as well as horizontal Interconnections across each layer of the chip. 进行电连接。导电金属(通常是铝)在晶圆表面沉积。使用光刻 和蚀刻制程去除没有用的金属。现在复杂的晶片都需要很多层绝 缘体。一个正常运作的晶片需要连接数以百万计的传导线路,包 括层上水平连接和各层之间的垂直连接。

芯片生产全过程概述PPT(39张)

从沙子到芯片-3

光刻胶:再次浇上光 刻胶(蓝色部分),然后 光刻,并洗掉曝光的 部分,剩下的光刻胶 还是用来保护不会离 子注入的那部分材料。

从沙子到芯片-3

离子注入(Ion Implantation):在真 空系统中,用经过加 速的、要掺杂的原子 的离子照射(注入)固体 材料,从而在被注入 的区域形成特殊的注 入层,并改变这些区 域的硅的导电性。经 过电场加速后,注入 的离子流的速度可以 超过30万千米每小时

从沙子到芯片-3

清除光刻胶:离子注 入完成后,光刻胶也 被清除,而注入区域 (绿色部分)也已掺杂, 注入了不同的原子。 注意这时候的绿色和 之前已经有所不同。

从沙子到芯片-3

晶体管就绪:至此, 晶体管已经基本完成。 在绝缘材(品红色)上蚀 刻出三个孔洞,并填 充铜,以便和其它晶 体管互连。

从沙子到芯片-3

从沙子到芯片-2

硅熔炼:12英寸/300 毫米晶圆级,下同。 通过多步净化得到可 用于半导体制造质量 的硅,学名电子级硅 (EGS),平均每一百万 个硅原子中最多只有 一个杂质原子。此图 展示了是如何通过硅 净化熔炼得到大晶体 的,最后得到的就是 硅锭(Ingot)。

从沙子到芯片-3

单晶硅锭:整体基本 呈圆柱形,重约100千 克,硅纯度99.9999%。

从沙子到芯片-3

晶圆测试:内核级别, 大约10毫米/0.5英寸。 图中是晶圆的局部, 正在接受第一次功能 性测试,使用参考电 路图案和每一块芯片 进行对比。

从沙子到芯片-3

晶圆切片(Slicing): 晶圆级别,300毫米 /12英寸。将晶圆切割 成块,每一块就是一 个处理器的内核(Die)。

从沙子到芯片-3

从沙子到芯片-3

装箱:根据等级测试 结果将同样级别的处 理器放在一起装运。

180纳米逻辑芯片制造流程演示幻灯片

(FEOL: device) (BEOL: interconnect)

6

6

Wafer Start

• WAFER START & RS CHECK

P type 8 ~ 12 ohm-cm, non-EPI wafer

• Start OX 100A dry

1. PR isolation 2. Prevent the laser mark Si recast 3. Surface cleanness 4. Backside oxidation & trap the

For ASML stepper system global Wafer alignment

NCR1DH75ARCAM

• ZERO Fully dry etch

• Pad oxide 110+-7A/ 920oC dry O2

(OX 100A + SI 1200+-200 A)

• ZERO Strip

能够展现精确的模拟特性soc与ic组成的系统相比由于soc能够综合并全盘考虑整个系统的各种情况可以在同样的工艺技术条件下实现更高性能的系统指若采用is方法和035m工艺设计系统芯片在相同的系统复杂度和处理速率下能够相当于采用025018m工艺制作的ic所实现的同样系统的性能与采用常规ic方法设计的芯片相比采用soc完成同样功能所需要的晶体管数目可以有数量级的降低asic

• GATE2_OX PreCln

NCRRCAM

• GATE2 OX

750 C, 27+-2 A, wet

2000A poly

50Å thick gate oxide Final 70 A

32Å thin gate oxide

芯片的制造过程

02

芯片制造的材料与设备

芯片制造所需的主要材料

半导体材料

• 硅:广泛应用于芯片制造,成本低廉,性能稳定 • 镓砷:具有高速、高频特性,应用于高性能芯片制造 • 其他半导体材料:碳纳米管、石墨烯等,具有潜在应用价值

绝缘材料

• 氧化硅:常用的绝缘材料,具有优良的电性能 • 氮化硅:具有优良的耐腐蚀性和耐磨性,应用于特殊芯片制造

光刻与薄膜工艺

光刻工艺

• 光刻胶涂覆:在硅片表面涂覆光刻胶,保护电路图案 • 光刻过程:利用光刻机将电路图案转移到硅片上

薄膜工艺

• 薄膜沉积:通过化学气相沉积(CVD)或物理气相沉积 (PVD)在硅片表面沉积薄膜 • 薄膜刻蚀:通过干法刻蚀或湿法刻蚀去除多余的薄膜

掺杂与扩散工艺

掺杂工艺

• 离子注入:将掺杂元素注入硅片,改变硅片的导电性能 • 扩散工艺:通过热处理,使掺杂元素在硅片内扩散,形成特定的浓度分布

• 设备性能的提升:新型光刻设备、薄膜沉积设备等的研 究与应用 • 设备成本的降低:通过技术进步,降低设备制造成本, 提高芯片制造企业的竞争力

03

芯片制造的前端工艺

芯片设计与仿真

芯片设计

• 电路设计:根据产品需求,设计芯片的电路结构 • 版图设计:将电路结构转换为实际的芯片版图

芯片仿真

• 电路仿真:通过计算机模拟,验证芯片电路的性能 • 热仿真:通过计算机模拟,预测芯片在工作状态下的温 度分布

谢谢观看

THANK YOU FOR WATCHING

芯片制造技术的发展历程

20世纪50年代: 晶体管发明, 芯片制造技术

诞生

01

• 贝尔实验室发明晶体管 • 硅晶体管替代锗晶体管

20世纪60年代: 集成电路(IC) 技术诞生,芯 片制造技术逐

集成电路设计与制造的主要流程ppt

激光扫描阵列:特殊的门阵列设计方法

对于一个特殊结构的门阵列母片,片上晶体管和 逻辑门之间都有电学连接,用专门的激光扫描光 刻设备切断不需要连接处的连线,实现ASIC功能。

只需一步刻铝工艺,加工周期短;

采用激光扫描曝光,省去了常规门阵列方法中的 制版工艺。但制备时间较长。

一般用于小批量(200~2000块)ASIC的制造

版图设计

功能描述与逻辑描述

功能图 逻辑图 电路图 符号式版图 , 版图

举例:x=a’b+ab’;CMOS与非门;CMOS反相器版图

什么是版图?一组相互套合的图形,各层版图相 应于不同的工艺步骤,每一层版图用不同的图案 来表示。

版图与所采用的制备工艺紧密相关

设计流程

理想的设计流程(自顶向下:TOP-DOWN)

元件 门

元胞

宏单元(功能块)

基于单元库的描述:层次描述

单元库可由厂家提供,可由用户自行建立

B. 模拟电路:尚无良好的综合软件

RTL级仿真通过后,根据设计经验进行电路设计

原理图输入

电路模拟与验证

模拟单元库

逻辑和电路设计的输出:网表(元件及其连接关系)或逻

辑图、电路图

软件支持:逻辑综合、逻辑模拟、电路模拟、时序分析等软

设计的基本过程 (举例)

功能设计 逻辑和电路设计 版图设计

集成电路设计的最终输出是掩膜版图,通过制版 和工艺流片可以得到所需的集成电路。 设计与制备之间的接口:版图

主要内容

IC设计特点及设计信息描述 典型设计流程 典型的布图设计方法及可测性设计技术

设计特点和设计信息描述

没有单元库支持:对各单元进行电路设计,通过电

路模拟与分析,预测电路的直流、交流、瞬态等特性, 之后再根据模拟结果反复修改器件参数,直到获得满 意的结果。由此可形成用户自己的单元库

LED芯片制造的工艺流程课件

长寿命

LED芯片的使用寿命长,可达到 数万小时,减少了更换灯具的频

率和维护成本。

多样化设计

LED芯片可以制作成各种形状和 大小,方便应用于各种照明场景,

满足不同的设计需求。

显示领域

高亮度

LED芯片能够产生高亮度,使得显示屏幕在强光下 也能清晰可见。

色彩鲜艳

LED芯片可以发出多种颜色的光,使得显示屏幕能 够呈现更加鲜艳和真实的色彩。

详细描述

封装与测试阶段包括将LED芯片粘贴到散热基板上,然后进行必要的焊接和引脚连接。最后进行性能 测试,如亮度、色温、稳定性等,以确保产品符合规格要求。这一阶段也是对前面工艺流程质量的最 终检验。

03

LED芯片制造的关键技术

MOCVD技术

MOCVD技术是制造LED芯片的核心技术之一,它通过将金属有机物和气 相化合物输送到反应室内,在衬底表面进行化学反应,形成所需的薄膜。

可靠性和稳定性。

改进封装工艺

02

通过改进封装工艺,降低封装成本,提高产品的质量和一致性。

强化测试环节

03

对外延片、芯片、封装品等各个阶段进行严格的质量检测和控

制,确保产品的性能和质量。

05

LED芯片制造的应用与前景

照明领域

节能环保

LED芯片具有高效节能和环保的 特点,能够替代传统照明灯具, 降低能源消耗和减少环境污染。

LED芯片的特点

LED芯片具有高效、节能、环保、寿命长等优点,广泛应用于照明、显示、指 示等领域。

LED芯片制造的重要性

推动产业发展

满足市场需求

LED芯片制造是LED产业的核心环节, 其技术水平和产能直接决定了整个 LED产业的发展水平。

随着人们对LED照明和显示需求的增 加,LED芯片制造能够满足市场对高 效、节能、环保照明产品的需求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

晶圆切片(Slicing):晶圆级别,300毫米/12英寸。将晶圆切割成块,每一块就是一个 处理器的内核(Die)。

丢弃瑕疵内核:晶圆级别。测试过程中发现的有瑕疵的内核被抛弃,留下完好的准 备进入下一步。

第八阶段合影

单个内核:内核级别。从晶圆上切割下来的单个内核,这里展示的是Core i7的核心。

第五阶段合影

Hale Waihona Puke 晶体管就绪:至此,晶体管已经基本完成。在绝缘材(品红色)上蚀刻出三个孔洞, 并填充铜,以便和其它晶体管互连。

电镀:在晶圆上电镀一层硫酸铜,将铜离子沉淀到晶体管上。铜离子会从正极(阳极) 走向负极(阴极)。

铜层:电镀完成后,铜离子沉积在晶圆表面,形成一个薄薄的铜层。

第六阶段合影

抛光:将多余的铜抛光掉,也就是磨光晶圆表面。

光刻:由此进入50-200纳米尺寸的晶体管级别。一块晶圆上可以切割出数百个处理 器,不过从这里开始把视野缩小到其中一个上,展示如何制作晶体管等部件。晶体 管相当于开关,控制着电流的方向。

现在的晶体管已经如此之小,一个针头上就能放下大约3000万个。 第三阶段合影

溶解光刻胶:光刻过程中曝光在紫外线下的光刻胶被溶解掉,清除后留下的图案和 掩模上的一致。

单晶硅锭:整体基本呈圆柱形,重约100千克,硅纯度99.9999%。 第一阶段合影

硅锭切割:横向切割成圆形的单个硅片,也就是我们常说的晶圆(Wafer)。顺便说, 这下知道为什么晶圆都是圆形的了吧?

晶圆:切割出的晶圆经过抛光后变得几乎完美无瑕,表面甚至可以当镜子。

事实上,Intel自己并不生产这种晶圆,而是从第三方半导体企业那里直接购买成品, 然后利用自己的生产线进一步加工,比如现在主流的45nm HKMG(高K金属栅极)。 值得一提的是,Intel公司创立之初使用的晶圆尺寸只有2英寸/50毫米。

封装:封装级别,20毫米/1英寸。衬底(基片)、内核、散热片堆叠在一起,就形成了我 们看到的处理器的样子。衬底(绿色)相当于一个底座,并为处理器内核提供电气与机械 界面,便于与PC系统的其它部分交互。散热片(银色)就是负责内核散热的了。

处理器:至此就得到完整的处理器了(这里是一颗Core i7)。

从沙子到芯片——看处理器是 怎样炼成的

信息学院——杨绪业

下边就图文结合,一步一步看看:

沙子:硅是地壳内第二丰富的元素,而脱氧后的沙子(尤其是石英)最多包含25%的 硅元素,以二氧化硅(SiO2)的形式存在,这也是半导体制造产业的基础。

硅熔炼:12英寸/300毫米晶圆级,下同。通过多步净化得到可用于半导体制造质量的 硅,学名电子级硅(EGS),平均每一百万个硅原子中最多只有一个杂质原子。此图展 示了是如何通过硅净化熔炼得到大晶体的,最后得到的就是硅锭(Ingot)。

装箱:根据等级测试结果将同样级别的处理器放在一起装运。

• 9、春去春又回,新桃换旧符。在那桃花盛开的地方,在这醉人芬芳的季节,愿你生活像春天一样阳光,心情像桃花一样美丽,日子像桃子一样甜蜜。 2020/12/112020/12/11Friday, December 11, 2020

• 10、人的志向通常和他们的能力成正比例。2020/12/112020/12/112020/12/1112/11/2020 9:14:51 PM • 11、夫学须志也,才须学也,非学无以广才,非志无以成学。2020/12/112020/12/112020/12/11Dec-2011-Dec-20 • 12、越是无能的人,越喜欢挑剔别人的错儿。2020/12/112020/12/112020/12/11Friday, December 11, 2020 • 13、志不立,天下无可成之事。2020/12/112020/12/112020/12/112020/12/1112/11/2020

金属层:晶体管级别,六个晶体管的组合,大约500纳米。在不同晶体管之间形成复 合互连金属层,具体布局取决于相应处理器所需要的不同功能性。

芯片表面看起来异常平滑,但事实上可能包含20多层复杂的电路,放大之后可以看 到极其复杂的电路网络,形如未来派的多层高速公路系统。

第七阶段合影

晶圆测试:内核级别,大约10毫米/0.5英寸。图中是晶圆的局部,正在接受第一次 功能性测试,使用参考电路图案和每一块芯片进行对比。

蚀刻:使用化学物质溶解掉暴露出来的晶圆部分,而剩下的光刻胶保护着不应该 蚀刻的部分。

清除光刻胶:蚀刻完成后,光刻胶的使命宣告完成,全部清除后就可以看到设计好 的电路图案。

第四阶段合影

光刻胶:再次浇上光刻胶(蓝色部分),然后光刻,并洗掉曝光的部分,剩下的光刻 胶还是用来保护不会离子注入的那部分材料。

这种在世界上最干净的房间里制造出来的最复杂的产品实际上是经过数百个步骤得来 的,这里只是展示了其中的一些关键步骤。

第九阶段合影

等级测试:最后一次测试,可以鉴别出每一颗处理器的关键特性,比如最高频率、 功耗、发热量等,并决定处理器的等级,比如适合做成最高端的Core i7-975 Extreme,还是低端型号Core i7-920。

离子注入(Ion Implantation):在真空系统中,用经过加速的、要掺杂的原子的离子 照射(注入)固体材料,从而在被注入的区域形成特殊的注入层,并改变这些区域的硅 的导电性。经过电场加速后,注入的离子流的速度可以超过30万千米每小时。

清除光刻胶:离子注入完成后,光刻胶也被清除,而注入区域(绿色部分)也已掺杂, 注入了不同的原子。注意这时候的绿色和之前已经有所不同。

第二阶段合影

光刻胶(Photo Resist):图中蓝色部分就是在晶圆旋转过程中浇上去的光刻胶液体, 类似制作传统胶片的那种。晶圆旋转可以让光刻胶铺的非常薄、非常平。

光刻:光刻胶层随后透过掩模(Mask)被曝光在紫外线(UV)之下,变得可溶,期间 发生的化学反应类似按下机械相机快门那一刻胶片的变化。掩模上印着预先设计好 的电路图案,紫外线透过它照在光刻胶层上,就会形成微处理器的每一层电路图案。 一般来说,在晶圆上得到的电路图案是掩模上图案的四分之一。