利用FT245BM实现FPGA与PC机的USB通讯

基于FT245BM的简易USB接口开发

基于FT245BM的简易USB接口开发基于FT245BM的简易USB接口开发摘要:FT245BM的主要功能是进行USB和并行I/O口之间的协议转换。

详细介绍FT245BM芯片的工作原理、内部结构、引脚分布及功能;给出基于FT245BM接口电路的典型设计及驱动和应用软件的编写方法。

关键词:FT245BMUSB接口并行I/O口引言1概述当前,USB外设的开发是一个热点。

由于USB总线具有传输速度快、占用资源少及真正的即插即用等优点,越来越受到业界的青睐。

可是,USB的开发要求设计人员对USB的标准、Firmware(固件)编程及驱动程序的编写等有较深入的理解,因此限制了USB的开发人员;而基于FT245BM芯片的USB产品开发,能够使研发人员在最短的周期内开发出相应的USB产品。

该芯片由FTDI (FutureTechnologyDevicesIntl.Ltd.)公司推出,使用简单、性能卓越,只要熟悉单片机编程及简单的VB、VC应用程序编程,就可很容易地进行用户产品开发。

2FT245BM芯片功能简介FT245BM的主要功能是进行USB和并行I/O口之间的协议转换。

芯片一方面可从主机接收USB数据,并将其转换为并行I/O口的数据流格式发送给外设;另一方面外设可通过并行I/O口将数据转换为USB的数据格式传回主机。

中间的转换工作全部由芯片自动完成,开发者无须考虑固件的设计。

FT245BM内部主要由USB收发器、串行接口引擎(SIE)、USB 协议引擎和先进先出(FIFO)控制器等构成,如图1所示。

USB收发器提供USB1.1/2.0的全速物理接口到USB总线,支持UHCI/OHCI主控制器;串行接口引擎主要用于完成USB数据的串/并双向转换,并按照USB1.1规范来完成USB数据流的位填充/位反填充,以及循环冗余校验码(CRC5/CRC16)的产生和检错;USB协议引擎管理来自USB 设备控制端口的数据流;FIFO控制器处理外部接口和收发缓冲区间的数据转换。

FPGA与PC的USB2.0通信实现

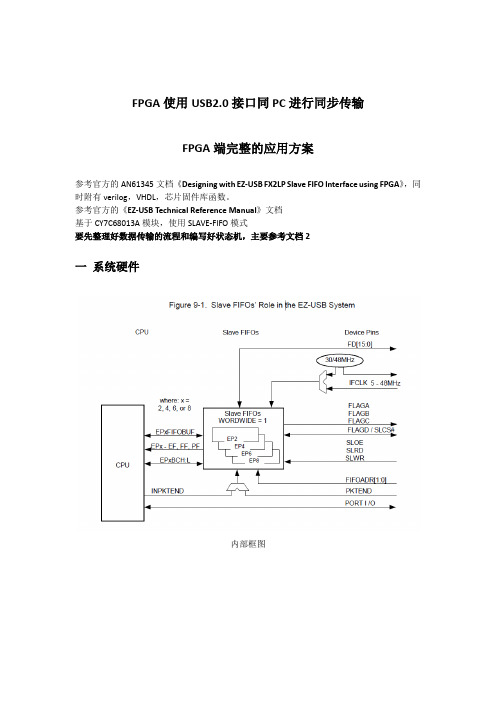

FPGA使用USB2.0接口同PC进行同步传输FPGA端完整的应用方案参考官方的AN61345文档《Designing with EZ-USB FX2LP Slave FIFO Interface using FPGA》,同时附有verilog,VHDL,芯片固件库函数。

参考官方的《EZ-USB Technical Reference Manual》文档基于CY7C68013A模块,使用SLAVE-FIFO模式要先整理好数据传输的流程和编写好状态机,主要参考文档2一系统硬件内部框图硬件连线引脚说明:SLRD FIFO读使能,同步模式可以和SLOE连在一起SLWR FIFO写使能SLOE 允许FIFO数据输出使能FIFOADR[1:0] 端口地址选择FD[15:0] 16-bit data bus.FlagA/FlagB/ FlagC/FlagD 端口2输出空标志=1可读出,输出满表示有数据,可读出。

端口6输入满标志=1可写入,输入空表示缓冲器没有剩余空间可写入了IFCLK 48 MHz and is generated by FX2LP.用于同步PARASET[2:0] 我自己添加的,以便后面增加额外功能或工作方式。

端口配置端口2 地址00,输出,四缓冲*512K Bytes端口6 地址10,输入,四缓冲*512K Bytes(16位的接口应该每来一次数据和每写一次数据需要256次操作(或者严格按照时序要求来))(也即是说数据传输的最小单位是512K Bytes,最后一次数据传输可能小于它,要么填充假数据要么给PKTEND一个负脉冲(低有效)。

同步模式下PKTEND pulse插入时间没有限制(只要缓冲器可用))各种状态FPGA产生的基本控制信号:写入数据过程:The FPGA monitors the Full flag of EP6 (Flag D) and Sync signal. FPGA continuously writes incrementing data into the FIFO when both Flag D and Sync signals are high(同步时钟下降沿时数据有效,因而同步时钟上升沿时写入数据,下降沿时读出数据). While writing data into the EP6 FIFO, the FPGA pauses the writing as soon as the Full flag gets asserted, and resumes thewriting when the flag gets de-asserted.读出数据过程和写入类似,只是针对的信号不一样。

基于FPGA技术实现与PC串行通信

基于FPGA技术实现与PC串行通信时间:2009-05-26 14:47:00 来源:CEDN 作者:摘要:本文主要介绍了基于FPGA技术实现与PC串行通信的过程,给出了各个模块的具体实现方法,分析了实现结果,验证了串行通信的正确性。

引言串行通信即串行数据传输,实现FPGA与PC的串行通信在实际中,特别是在FPGA 的调试中有着很重要的应用。

调试过程一般是先进行软件编程仿真,然后将程序下载到芯片中验证设计的正确性,目前还没有更好的工具可以在下载后实时地对FPGA的工作情况和数据进行分析。

通过串行通信,可以向FPGA发控制命令让其执行相应的操作,同时把需要的数据通过串口发到PC上进行相应的数据处理和分析,以此来判断FPGA是否按设计要求工作。

这样给FPGA的调试带来了很大方便,在不需要DSP等其他额外的硬件条件下,只通过串口就可以完成对FPGA的调试。

本文采用QuartusⅡ3.0开发平台,使用Altera公司的FPGA,设计实现了与PC的串行通信。

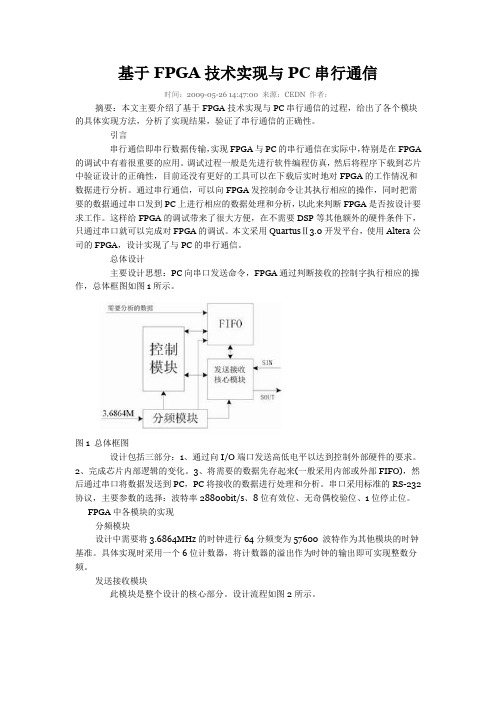

总体设计主要设计思想:PC向串口发送命令,FPGA通过判断接收的控制字执行相应的操作,总体框图如图1所示。

图1 总体框图设计包括三部分:1、通过向I/O端口发送高低电平以达到控制外部硬件的要求。

2、完成芯片内部逻辑的变化。

3、将需要的数据先存起来(一般采用内部或外部FIFO),然后通过串口将数据发送到PC,PC将接收的数据进行处理和分析。

串口采用标准的RS-232协议,主要参数的选择:波特率28800bit/s、8位有效位、无奇偶校验位、1位停止位。

FPGA中各模块的实现分频模块设计中需要将3.6864MHz的时钟进行64分频变为57600 波特作为其他模块的时钟基准。

具体实现时采用一个6位计数器,将计数器的溢出作为时钟的输出即可实现整数分频。

发送接收模块此模块是整个设计的核心部分。

设计流程如图2所示。

图2 发送接收流程图在串行通信中,无论发送或接收,都必须有时钟脉冲信号对所传送的数据进行定位和同步控制,设计中采用的时钟频率是波特率的两倍(57600 bit/s)。

FPGA-USB-PC连接梗概

用其他的芯片也可以的,楼上说的CH375也可以,国产的,飞利浦也有PD开头的,找芯片的时候找技术支持好的,最好能帮你调的,前提是你的量大.

USB数据传输的核心是一个叫端点(endpoint)的东西,(一个端点是一个可唯一识别的USB设备的Portion,它是主机与设备间通信流的一个结

束点。一系列相互独立的端点在一起构成了USB逻辑设备。每个逻辑设备有一个唯一的地

址,这个地址是在设备连上主机时,由主机分配的,而设备中的每个端点在设备内部有

既然一个引脚可以用于输入、输出或其他特殊功能,那么一定有寄存器用来选择这些功能。对于输入,一定可以通过读取某个寄存器来确定引脚电平的高低;对于输出,一定可以通过写入某个寄存器来让这个引脚输出高电平或者低电平;对于其他特殊功能,则有另外的寄存器来控制它们。)

USB1.1速度最快12M bps,2.0最快480Mbps,根据你的数据量来选择

CY68013提供的开发包有驱动,自己改改就OK了,并且68013还带单片机的功能,带GPIO,可以完成其他的功能(General Purpose Input Output (通用输入/输出)简称为GPIO,或总线扩展器,利用工业标准I2C、SMBus或SPI接口简化了I/O口的扩展。当微控制器或芯片组没有足够的I/O端口,或当系统需要采用远端串行通信或控制时,GPIO产品能够提供额外的控制和监视功能。)(GPIO,通用型之输入输出(General Purpose I/O)的简称,功能类似8051的P0—P3,其接脚可以供使用者由程控自由使用,PIN脚依现实考量可作为通用输入(GPI)或通用输出(GPO)或通用输入与输出(GPIO),如当clk generator, chip select等。

想要把FPGA通过USB接口和电脑连起来,实现数据传输,请问是只要设计好FPGA的I/O端口和USB的四条线连接起来就好了吗?还是要做一个外围电路?USB需要控制芯片吗?

基于FPGA的USB通讯

PFGA与USB的通信实现,USB采用赛普拉斯的EZ-USB。

程序包括两部分:发送和接收。

每路都包括一个缓冲区和一个FIFO及校验计算逻辑。

发送逻辑监控发送缓冲区的写入口地址总线,对偏移0xFF的操作,视为命令长度,并触发发送操作。

命令发送时,首先发送到发送FIFO中,然后根据USB总线的忙闲状态,从FIFO中读取数据,并计算校验和,在达到命令长度后将校验和发送到USB上。

接收逻辑监控USB总线,有数据时根据状态机工作。

首先,读到包头后,就接受命令里指定长度的数据,然后进行校验计算,如果通过校验,就产生中断信号。

module usbctrl (nrst,unrst, uclk, udata, uflaga, uflagb, uflagc, uncs, unrd, unwr, uaddr, upktend,txdata, txaddr, txbsy, txlatch, txclk,rxdata, rxaddr, rxlatch, rxclk, rxirq,upktend_en);`include "REGADDRDEF.h"input nrst, uclk, uflaga, uflagb, uflagc;output uncs, unrd, unwr, upktend, unrst;reg unwr;//wire uncs;output [1:0] uaddr;reg [1:0] uaddr;inout [15:0] udata;input [15:0] txdata;input [7:0] txaddr;output txbsy;//reg txbsy;input txlatch, txclk;output [15:0] rxdata;input [7:0] rxaddr;input rxlatch, rxclk;output rxirq;input upktend_en;assign unrst = nrst;//----------------------------------------------------------// ARM Control Signalreg rxcmdbuf_clear;reg [2:0]rxcmdbuf_clear_cnt;always @(posedge rxclk or negedge nrst)if (~nrst)rxcmdbuf_clear_cnt <= #REGOUT 3'hF;else if (rxlatch)rxcmdbuf_clear_cnt <= #REGOUT 3'h0;else if (~&rxcmdbuf_clear_cnt)rxcmdbuf_clear_cnt <= #REGOUT rxcmdbuf_clear_cnt + 1'b1;always @(posedge rxclk or negedge nrst)if (~nrst)rxcmdbuf_clear <= #REGOUT 1'b0;else // Edit the logic to clear therxcmdbuf_clear <= #REGOUT ~&rxcmdbuf_clear_cnt; // flag after read the command//----------------------------------------------------------// USB Bus Control`define BUSST_IDLE 2'b00`define BUSST_RD 2'b10`define BUSST_WR 2'b11wire rx_empty = ~uflagb;wire tx_full = ~uflagc;reg [1:0] bus_stm, bus_stm_next;always @(posedge uclk or negedge nrst)if (~nrst)bus_stm <= #REGOUT 2'b00;elsebus_stm <= #REGOUT bus_stm_next;wire rxbufok, txbufok;wire can_rx = ~rx_empty & rxbufok; // low assertwire can_tx = ~tx_full & txbufok; // low assertalways @(bus_stm or can_rx or can_tx)if (bus_stm == `BUSST_IDLE)beginif (can_rx)bus_stm_next = `BUSST_RD;else if (can_tx)bus_stm_next = `BUSST_WR;elsebus_stm_next = `BUSST_IDLE;endelse if (bus_stm == `BUSST_RD)beginif (can_rx)bus_stm_next = `BUSST_RD;elsebus_stm_next = `BUSST_IDLE;endelse if (bus_stm == `BUSST_WR)beginif (can_tx)bus_stm_next = `BUSST_WR;elsebus_stm_next = `BUSST_IDLE;endelsebus_stm_next = `BUSST_IDLE;assign unrd = ~((bus_stm == `BUSST_RD) && can_rx);//// always @(posedge uclk)// uncs <= #REGOUT ~bus_stm[1]; //unwr & unrd;//assign uncs = ~bus_stm[1]; //unwr & unrd;reg [15:0] udatao;assign udata = (unwr) ? 16'hZZZZ : udatao;// reg unwr_r;// wire txusbbuf_rd;reg txusbbuf_rd;always @(posedge uclk)unwr <= #REGOUT ~txusbbuf_rd;// assign unwr = ~((bus_stm == `BUSST_WR) && can_tx);// always @(posedge uclk)// unwr <= #REGOUT unwr_r;always @(posedge uclk)uaddr <= #REGOUT (bus_stm == `BUSST_WR) ? TXENDPOINT : RXENDPOINT; // assign uaddr = (bus_stm == `BUSST_WR) ? TXENDPOINT : RXENDPOINT;//----------------------------------------------------------// rx logicreg rxcmd_valid, rxcmd_invalid;reg rx_stm, rx_stm_next;wire usb_datain_buf_ren;wire usb_datain_buf_rdempty;wire [7:0] usb_datain_buf_dout;wire usb_datain_buf_full;assign rxbufok = ~usb_datain_buf_full;reg usb_datain_buf_wrreq;always @(posedge uclk)usb_datain_buf_wrreq <= #REGOUT ~unrd;fifo16_8 usb_datain_buf_inst(.aclr(~nrst),.data(udata),.wrclk(uclk),.wrreq(~unrd), //(usb_datain_buf_wrreq),.wrfull(usb_datain_buf_full),.rdclk(uclk),.rdreq(usb_datain_buf_ren),.rdempty(usb_datain_buf_rdempty),.q(usb_datain_buf_dout));reg rxcmdbuf_ok;// indicated that the ARM has get the datareg rxcmdbuf_clear_d;always @(posedge uclk or negedge nrst)if (~nrst)beginrxcmdbuf_clear_d <= #REGOUT 1'b0;rxcmdbuf_ok <= #REGOUT 1'b1;endelsebeginrxcmdbuf_clear_d <= #REGOUT rxcmdbuf_clear;if (rxcmdbuf_ok)rxcmdbuf_ok <= #REGOUT ~rxcmd_valid;elserxcmdbuf_ok <= #REGOUT rxcmdbuf_clear_d;endassign usb_datain_buf_ren = ~usb_datain_buf_rdempty & rxcmdbuf_ok;reg [8:0] rxcmdbuf_wraddr;wire [7:0] rxcmdbuf_din = usb_datain_buf_dout;wire rxcmdbuf_wrclk = uclk;reg rxcmdbuf_wren;wire [7:0] rxcmdbuf_rdaddr = rxaddr;wire rxcmdbuf_rdclk = rxclk;wire [15:0]rxcmdbuf_dout ;assign rxdata = rxcmdbuf_dout;always @(posedge uclk or negedge nrst)if (~nrst)rxcmdbuf_wren <= #REGOUT 1'b0;elserxcmdbuf_wren <= usb_datain_buf_ren && rx_stm_next == 1'b1;rxcmdbuf rxcmdbuf_inst(.data(rxcmdbuf_din),.wraddress(rxcmdbuf_wraddr),.wrclock(rxcmdbuf_wrclk),.wren(rxcmdbuf_wren),.rdaddress(rxcmdbuf_rdaddr),.rdclock(rxcmdbuf_rdclk),.q(rxcmdbuf_dout));always @(posedge uclk or negedge nrst)if (~nrst)rx_stm <= #REGOUT 1'b0;elserx_stm <= #REGOUT rx_stm_next;wire rst_rxstm;always @(rx_stm or rxcmd_invalid or rxcmd_valid or usb_datain_buf_dout or usb_datain_buf_ren or rst_rxstm)if (rst_rxstm)rx_stm_next = 1'b0;else if (rx_stm == 1'b0)beginif (usb_datain_buf_dout == USBRXCMDHEAD && usb_datain_buf_ren)rx_stm_next = 1'b1;elserx_stm_next = 1'b0;endelsebeginif (rxcmd_valid || rxcmd_invalid)rx_stm_next = 1'b0;elserx_stm_next = 1'b1;endreg [15:0] rxcmd_len;reg [7:0] rxcmd_chksum;assign rst_rxstm = rxcmdbuf_wraddr > 2 && rxcmd_len > 64 && ~&rxcmd_len;always @(posedge uclk or negedge nrst)if (~nrst)rxcmd_len <= #REGOUT 16'hFFFF;else if (rxcmdbuf_wraddr == 9'h001)rxcmd_len[7:0] <= #REGOUT rxcmdbuf_din; //{8'h00, rxcmdbuf_din + 1'b1};else if (rxcmdbuf_wraddr == 9'h002)rxcmd_len[15:8] <= #REGOUT rxcmdbuf_din; //{rxcmdbuf_din, 8'h00} + rxcmd_len;else if (rx_stm == 1'b0)rxcmd_len <= #REGOUT 16'hFFFF;always @(posedge uclk or negedge nrst)if (~nrst)rxcmdbuf_wraddr <= #REGOUT {9{1'b0}};else if (rxcmdbuf_wren && rxcmdbuf_ok)rxcmdbuf_wraddr <= #REGOUT rxcmdbuf_wraddr + 1'b1;else if (~rx_stm | ~rxcmdbuf_ok)rxcmdbuf_wraddr <= #REGOUT {9{1'b0}};always @(posedge uclk or negedge nrst)if (~nrst)rxcmd_chksum <= #REGOUT 8'h00;else if (~rx_stm)rxcmd_chksum <= #REGOUT USBRXCMDHEAD;else if (rxcmdbuf_wren) ////****rxcmd_chksum <= #REGOUT rxcmd_chksum + rxcmdbuf_din;wire cmp_r = rxcmd_chksum == usb_datain_buf_dout;always @(posedge uclk or negedge nrst)if (~nrst)rxcmd_invalid <= #REGOUT 1'b0;else if (rxcmd_len + 2 == {7'h00,rxcmdbuf_wraddr})rxcmd_invalid <= #REGOUT ~cmp_r;else if (~rx_stm)rxcmd_invalid <= #REGOUT 1'b0;always @(posedge uclk or negedge nrst)if (~nrst)rxcmd_valid <= #REGOUT 1'b0;else if (rxcmd_len + 2 == {7'h00,rxcmdbuf_wraddr})rxcmd_valid <= #REGOUT cmp_r;else if (~rx_stm)rxcmd_valid <= #REGOUT 1'b0;reg [1:0] rxirq_cnt;always @(posedge rxclk or negedge nrst or posedge rxcmd_valid) if (~nrst)rxirq_cnt <= #REGOUT 2'b11;else if (rxcmd_valid)rxirq_cnt <= #REGOUT 2'b00;else if (~&rxirq_cnt)rxirq_cnt <= #REGOUT rxirq_cnt + 1'b1;assign rxirq = ~&rxirq_cnt;//----------------------------------------------------------// Tx logicreg [8:0] txcmdbuf_rdaddr;wire [7:0] txcmdbuf_dout;wire [15:0] txcmdbuf_dout_16;reg [8:0] txcmdlen, txcmdlen_u, txcmdlen_ur;reg txcmdbuf_ok, txcmdbuf_ok_r, txcmdbuf_ok_rr;txcmdbuf txcmdbuf_inst(.data (txdata),.wraddress (txaddr[7:0]),.wrclock (txclk),.wren (txlatch),.rdaddress (txcmdbuf_rdaddr[8:1]),.rdclock (uclk),.q (txcmdbuf_dout_16));assign txcmdbuf_dout = (~txcmdbuf_rdaddr[0]) ? txcmdbuf_dout_16[15:8] : txcmdbuf_dout_16[7:0];wire txcmd_over_rst = (txcmdbuf_rdaddr >= txcmdlen);reg txcmd_over_rst_r, txcmd_over_rst_rr;always @(posedge txclk)begintxcmd_over_rst_r <= #REGOUT txcmd_over_rst;txcmd_over_rst_rr <= #REGOUT txcmd_over_rst_r;endreg [3:0] txcmd_over_cnt;always @(posedge txclk or posedge txcmd_over_rst_rr)if (txcmd_over_rst_rr)txcmd_over_cnt <= #REGOUT 4'b0000;else if (~&txcmd_over_cnt)txcmd_over_cnt <= #REGOUT txcmd_over_cnt + 1'b1;wire txcmd_over = ~&txcmd_over_cnt;always @(posedge txclk or negedge nrst)if (~nrst)begintxcmdlen <= #REGOUT 9'hFFF;txcmdbuf_ok_r <= #REGOUT 1'b0;endelse if (txlatch == 1'b1 && txaddr == 8'hFF) //**METASTEABILITY begintxcmdlen <= #REGOUT txdata[8:0];txcmdbuf_ok_r <= #REGOUT 1'b1;endelse if (txcmd_over)begintxcmdlen <= #REGOUT 9'hFFF;txcmdbuf_ok_r <= #REGOUT 1'b0;endalways @(posedge uclk or negedge nrst)if (~nrst)begintxcmdlen_u <= #REGOUT 9'h000;txcmdlen_ur <= #REGOUT 9'h000;endelsebegintxcmdlen_u <= #REGOUT txcmdlen;txcmdlen_ur <= #REGOUT txcmdlen_u;endalways @(posedge uclk or negedge nrst)if (~nrst)begintxcmdbuf_ok_rr <= #REGOUT 1'b0;txcmdbuf_ok <= #REGOUT 1'b0;endelsebegintxcmdbuf_ok_rr <= #REGOUT txcmdbuf_ok_r;txcmdbuf_ok <= #REGOUT txcmdbuf_ok_rr;endwire [8:0] txusbbuf_din;wire [17:0] fifo_out;reg txusbbuf_wren;reg txusbbuf_latch;wire txusbbuf_wrfull, txusbbuf_rdempty;always @(posedge uclk or negedge nrst)if (~nrst)txcmdbuf_rdaddr <= #REGOUT 9'h000;else if (txusbbuf_latch && txcmdbuf_rdaddr <= txcmdlen_ur) txcmdbuf_rdaddr <= #REGOUT txcmdbuf_rdaddr + 1'b1;else if (~txcmdbuf_ok)txcmdbuf_rdaddr <= #REGOUT 9'h000;fifo8_16 usb_dataout_buf_inst(.data (txusbbuf_din),.wrclk (uclk),.wrreq (txusbbuf_wren),.wrfull (txusbbuf_wrfull),.rdempty (txusbbuf_rdempty),.rdclk (uclk),.rdreq (txusbbuf_rd),.q (fifo_out));reg [2:0] cnt;always @(posedge uclk or negedge nrst)if (~nrst)begintxusbbuf_latch <= #REGOUT 1'b0;cnt <= #REGOUT 3'b111;endelse if (~txcmdbuf_ok)begintxusbbuf_latch <= #REGOUT 1'b0;cnt <= #REGOUT 3'b111;endelse if (txcmdbuf_rdaddr == txcmdlen_ur)begintxusbbuf_latch <= #REGOUT 1'b0;cnt <= #REGOUT 3'b000;endelse if (txcmdbuf_ok && &cnt && ~txusbbuf_wrfull)txusbbuf_latch <= #REGOUT 1'b1;else if (~&cnt) //if (~txusbbuf_wrfull)cnt <= #REGOUT cnt + 1'b1;reg txusbbuf_latch_d, txusbbuf_latch_dd;always @(posedge uclk)begintxusbbuf_latch_d <= #REGOUT txusbbuf_latch;txusbbuf_latch_dd <= #REGOUT txusbbuf_latch_d;endwire txusbbuf_latch_dp = ~txusbbuf_latch_d & txusbbuf_latch_dd;reg latch_dd;reg[2:0] latch_dd_cnt;always @(posedge uclk or negedge nrst)if (~nrst)latch_dd_cnt <= #REGOUT 3'b111;else if (txusbbuf_latch_dp)latch_dd_cnt <= #REGOUT 3'b000;else if (~&latch_dd_cnt)latch_dd_cnt <= #REGOUT latch_dd_cnt+1'b1;always @(posedge uclk or negedge nrst)if (~nrst)txusbbuf_wren <= #REGOUT 1'b0;elsetxusbbuf_wren <= #REGOUT txusbbuf_latch | (~&latch_dd_cnt);reg [7:0] txcmd_chksum;always @(posedge uclk or negedge nrst)if (~nrst)txcmd_chksum <= #REGOUT 8'h00;else if (txusbbuf_wren)txcmd_chksum <= #REGOUT txcmd_chksum + txcmdbuf_dout;elsetxcmd_chksum <= #REGOUT 8'h00;assign txusbbuf_din = (~&latch_dd_cnt) ? 17'h00000 : (txcmdbuf_rdaddr == txcmdlen_ur) ? {1'b1, txcmd_chksum} : {1'b0, txcmdbuf_dout};assign txbufok = ~txusbbuf_rdempty;// assign txusbbuf_rd = (bus_stm == `BUSST_WR) && txbufok && can_tx;reg [2:0] cnt_d;always @(posedge uclk or negedge nrst)if (~nrst)begincnt_d <= 3'h0;txusbbuf_rd <= 1'b0;endelse if (txusbbuf_rd)begintxusbbuf_rd <= 1'b0;cnt_d <= 3'h0;endelse if (cnt_d==3'h1)begintxusbbuf_rd <= (bus_stm == `BUSST_WR) && txbufok && can_tx;endelse if (cnt_d < 3'h1)cnt_d <= cnt_d + 1'b1;always @(posedge uclk)udatao <= #REGOUT {fifo_out[16:9], fifo_out[7:0]};reg upktend_r;reg [2:0] end_cnt;always @(posedge uclk or negedge nrst)if (~nrst)end_cnt <= 3'hf;else if(txusbbuf_rd && (fifo_out[17] || fifo_out[8]))end_cnt <= 3'h0;else if (~&end_cnt)end_cnt <= end_cnt + 1'b1;//// assign upktend = ~(txusbbuf_rd && (fifo_out[17] || fifo_out[8])); // assign upktend = upktend_r;assign upktend = (end_cnt==3'b101) | upktend_en;assign txbsy = txcmdbuf_ok_r;endmodule。

基于FPGA和FT245R USB的数据采集系统设计

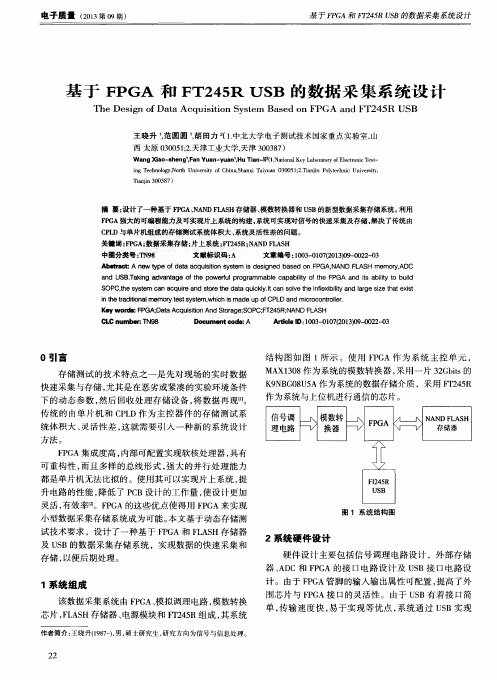

结 构 图如 图 1 所 示 。使 用 F P G A作 为 系统 主控 单 元 , M A X 1 3 0 8作为系统 的模数转 换器 , 采用 一片 3 2 G b i t s 的

K 9 N B G 0 8 U 5 A作为系统的数据存储 介质 ,采用 F T 2 4 5 R

作为系统与上位机进行通信 的芯 片。

_ r j a n j i n 3 0 0 3 8 7)

摘 要: 设计 了 一 种基于 F P G A . N A N D F L A S H ̄

8, 模 数转换 器和 U S B的新型数据采集存储系统 。 利用

F P G A强大的可编程 能力及可实现片上 系统的梅建 , 系统可实现 对信号的快速 采集及存储 , 解决 了传统 由 C P L D与单 片机组成 的存储测试 系统体 积大 、 系统灵 活性差 的问题 。 关键词 : F P ( ; 数 据采集存储 片上系统 ;  ̄2 4 5 R ; N A N D F L A S H

A r t i c l e I D: 1 0 0 3 — 0 1 7( 0 2 0 1 3 ) 0 9 - 0 0 2 2 - 0 3

0引言

存 储测试 的技术特 点之一 是先对 现场 的实时数 据 快速采 集与存储 , 尤 其是 在恶劣或紧凑 的实验 环境 条件 下的动态参 数 , 然后 回收处 理存储设 备 , 将 数据再 现l l l 。 传 统 的 由单 片机 和 C P L D作 为 主控器件 的存储 测试 系

Ke y wo r ds : F PG/  ̄ 4 Da t a Ac qu j s 嘲 O n An d St or a ge ; SOPC; F T 2 45 R; NAND F L AS H

基于FT245BM的多USB接口的实现

收稿日期225作者简介徐锋(2 ),男,无锡职业技术学院电子信息技术学院助教,硕士。

基于FT245BM 的多US B 接口的实现徐 锋(无锡职业技术学院,江苏 无锡 214121)摘 要:在测控应用系统中,US B 已成为目前数据传输的首选接口。

该文介绍了基于FT 245B M 的US B 接口的软硬件设计,然后给出了多个基于FT 245BM 的US B 接口在同一PC 机共存的解决方案。

关键词:U S B,FT 245B M ,数据接口中图分类号:TP334.2 文献标识码:A 文章编号:167127880(2008)022*******D es i g n of M u lti 2USB I n terfa ce Ba sed on FT245B MXu FengAbstra ct:Compared with traditi ona l RS232,Unive rsa l Serial B us ha s been the most favorite choice of data tr ans m issi on inte r face in the m easuring and contr ol applicati on syste m.The paper first intr oduce s the soft 2ware and hard wa r e design of US B interface ba sed on FT245BM,and then gives out the solution to m ulti US B interfaces coexistence on the same compute r .Key W or ds:Universal Se rial B us ;FT245B M;data interf ace0 引言US B 作为一种新型的计算机接口技术,解决了日益增加的PC 外设与有限的主板插槽和端口之间的矛盾,具有传输速度高、支持即插即用、热插拔、易于扩展,能同时连接多达127个外部设备,可以在很大范围内取代R S 2232、并行端口进行短距离的高速数据传输。

基于FPGA技术实现USB通信-软件(毕业设计)

基于F P G A技术实现U S B通信——软件【摘要】本设计能实现的功能:PC主机应用程序通过USB接口模块,对FPGA系统进行控制,以实现语音信号的采集、存储、回放,并且FPGA系统亦可通过USB接口模块将相关的状态信息回传给PC主机应用程序。

本设计软件结构由四部分组成:PC主机应用程序,USB接口模块驱动程序,USB接口模块固件程序,FPGA系统控制程序。

【关键词】应用程序,USB,FPGA,语音USB Communication Based on FPGA ——Software Abstract: This Design can implement the following functions: PC Application Program can control the FPGA-System through the USB-Interface module, in order to sample, store and replay the sound signal , and also FPGA-System can send back the status signal to the PC Application Program. The software structure of this design consist of 4 parts: PC Application Program, USB-Interface module Driver program, USB-interface module Firm program, FPGA-System control program.Key Words:Application Program, USB,FPGA, Sound目录第一章绪论 01.1 课题背景及意义 01.2 国内外相关研究状况 (1)1.3 USB的特点 (2)1.4 系统软件设计要求 (3)1.5 系统基本方案 (3)1.6 软件设计主要内容 (3)第二章软件实现方案选择论证 (3)2.1 PC主机应用程序设计实现方案 (3)2.2 WINDOWS下USB设备驱动程序的设计实现方案 (4)2.3 USB设备固件设计实现方案 (4)2.4 FPGA程序设计实现方案 (5)第三章 PC主机应用程序设计 (5)3.1 开发环境VC++ 6.0简介 (5)3.2 API函数简介 (5)3.3 应用程序控制界面设计 (6)3.4 应用程序设计 (6)3.4.1 查找设备 (8)3.4.2 打开设备 (10)3.4.3 读写USB设备 (10)3.4.4 关闭通信 (10)第四章 USB接口模块驱动程序设计 (11)4.1 驱动程序开发 (11)4.1.1 WDM驱动程序的分层结构 (11)第五章 USB接口模块固件设计 (13)5.1 PDIUSBD12与AT89S52 特性概述 (13)5.1.1 PDIUSBD12特性概要 (13)5.1.2 AT89S52 特性概要 (14)5.2 USB通信协议重要概念概述 (14)5.2.1 端点 (14)5.2.2 帧 (14)5.2.3 上行与下行 (14)5.2.4 USB的传输线结构 (15)5.2.5 USB的编码方案 (15)5.2.6 USB的数据格式 (15)5.2.6.1 域 (15)5.2.6.2 包 (16)5.2.6.3 事务 (16)5.2.6.4 传输 (18)5.3 USB固件程序设计 (19)第六章 FPGA语音采集与回放程序设计 (20)6.1 FPGA语音采集、存储、回放控制程序设计 (20)6.1.1 ADC0809语音采集控制程序设计 (20)6.1.2 语音数据存储器设计 (20)6.1.3 DAC0832语音回放控制程序设计 (20)6.1.4 地址与控制总线选择器设计 (21)6.1.5 FPGA系统设计总体框图 (22)第七章系统调试 (23)7.1 主机应用程序与USB接口模块程序联调 (23)7.2 FPGA系统调试 (23)7.3 整机系统调试 (23)总结 (23)致谢 (24)参考文献 (24)附录 (24)第一章绪论1.1 课题背景及意义USB总线(Universal Serial Bus)翻译为中文就是通用串行总线,由Compaq,DEC,IBM,Inter,Microsoft,NEC和Northen Telecom等公司为简化PC与外设之间的互连而共同研究开发的一种免费的标准化连接协议,它支持各种PC与外设之间的连接,还可实现数字多媒体集成。

FT245BM中文资料

FT245BM USB FIFO ( USB - Parallel ) I.C.

1.1 General Description

The FT245BM provides an easy cost-effective method of transferring data to / from a peripheral and a host P.C. at up to 8 Million bits (1 Megabyte) per second. Its simple, FIFO-like design makes it easy to interface to any microcontroller or microprocessor via IO ports. To send data from the peripheral to the host computer, simply write the byte-wide data into the module when TXE# is low. If the (384-byte) transmit buffer fills up or is busy storing the previously written byte, the device keeps TXE# high in order to stop further data from being written until some of the FIFO data has been transferred over USB to the host. TXE# goes high after every byte written. When the host sends data to the peripheral over USB, the device will take RXF# low to let the peripheral know that at least one byte of data is available. The peripheral can read a data byte every time RXF# goes low. RXF# goes high after every byte read. By using FTDI’s virtual COM port drivers, the peripheral looks like a standard COM port to the application software. Commands to set the baud rate are ignored - the device always transfers data at its fastest rate regardless of the application’s baud-rate setting. Alternatively, FTDI’s D2XX drivers allow application software to access the device “directly” through a published DLL based API. Details of the current VCP and D2XX driver can be found on FTDI’s web site ( )

USB接口芯片FT245AM的原理

USB接口芯片FT245AM的原理摘要:介绍了一种USB总线接口芯片FT245AM及其在航空ARINC429总线测试仪中的应用方法,同时介绍了FT245AM的内部结构、管脚说明以及与微处理器的接口电路,给出了航空ARINC429总线测试仪的总体框图、部分原理和接口逻辑的Verilog HDL源代码及仿真时序。

关键词:USB总线 ARINC429总线 FT245AM CPLD MCU随着计算机的广泛就算,与计算机通信的方式也越来越多,对通信速度和易用性要求也越来越高,这使得USB通信方式显得越来越突出,应用领域也越来越广泛。

因此,在鼠标、键盘、游戏杆、数据采集卡、数码相机、掌上电脑中都有USB的应用。

FT245AM是美国FTDI公司生产的一种USB专用芯片。

它具有功能强、体积小、传输速度快、符合USB1.1技术规范、易于一微处理器接口等特点,因而倍受用户的青睐。

笔者采用FT245AM成功地开发了航空ARINC429总线测试仪。

FT245AM集成了USB1.1通信协议和外设接口,可以方便地实现USB主机与外设MCU、CPLD的接口,其数据传输速率可达1MB/s。

FT245AM内部128字节的接收FIFO和384字节的发送FIFO大大提高了USB主机与外设的通信质量。

另外,FT245AM还具备3.3V的LDO 调整器、8位频器、USB数据时钟恢复PLL、USB数据收发器,且EEPROM接口逻辑单元可外接串行存储器93C46,以实现USB VID、PID、序列号和设备说明字符串的存储。

使用FT245AM 可大大简化其外围电路,使用户设备更趋于小型化。

1 FT245AM简介1.1 FT245AM内部结构和引脚功能FT245AM芯片的内部结构如图1所示。

该芯片采用QFP32封装,其各管脚说明如下:USBDP(7脚):USB差分数据正端;EEDATA(2脚):串行存储器数据;USBDM(8脚):USB 差分数据负端;TEST(5脚):厂商测试管脚;3V3OUT(6脚):3.3V电源输出;D[7:0](25~18脚):外设接口数据总线;XTIN(27脚):晶体振荡器输入;RD(16脚):外设读数据信号输入;XTOUT(28脚):晶体振荡器输出;WR(15脚):外设写数据信号输入;RCCLK(31脚):RC定时器;TXE(14脚):发送FIFO空标志输出;RESET(4脚):芯片复位输入;RXF(12脚):接收FIFO非空标志输出;EECS(32脚):串行存储器片选;[!--empirenews.page--]EEREQ (11脚):串行存储器读取请求;EESK(1脚):串行存储器时钟;EEGNT(10脚):串行存储器读取允许;VCC,AVCC(3、13、26、30脚):分别为芯片电源和电路模拟电源;GND,AGND (9、19、29脚):芯片地和模拟地。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第28卷 第1期2005年3月电 子 器 件Chinese Journal of Elect ron Devices Vol.28 No.1Mar.2005A Method of the Communication bet w een FPGAand the USB H ost B ased on FT245BMCA I J i ang 2hong ,S H I X i ao 2j un ,Z H U W ei ,D U Guo 2li an g(Elect ronics Depart ment S out heast Universit y ,N anj ing 210096,China )Abstract :This article int roduces a met hod of t he communication between FP GA and t he U SB host.The aut hor succeeded in communicating wit h PC using a U SB chip ———F T245BM ,produced by F TDI (Fut ure Technology Devices Intl.Lt d ).A circuit diagram of t he interface between t he F T245BM chip and t he FP GA chip is p repared.The program of FP GA ,written in Verilog HDL ,and t he software running in PC are given ;K ey w ords :F T245BM ;U SB ;FP GA EEACC :4220利用FT245BM 实现FPGA 与PC 机的USB 通讯蔡江洪,史小军,朱 为,堵国梁(东南大学电子工程系,南京210096)收稿日期:2004209224作者简介:蔡江洪(19792),男,硕士研究生,主要研究方向为电路与系统设计,cjh -xf @ 。

摘 要:为了实现FP GA 与USB 主机之间的通讯。

使用了一款F TDI 公司(Future Technology Devices Intl.Ltd )生产的USB 芯片FT245BM ,成功地实现了FP GA 与PC 机之间的USB 通讯;文中提供了该芯片与可编程逻辑器件FP GA 的硬件接口电路,并给出了FP GA 的Verilog HDL 程序及PC 上的软件编程范例。

关键词:F T245BM ;USB ;FP GA 中图分类号:TN919 文献标识码:A 文章编号:100529490(2005)0120132203 随着计算机应用的普及,外围设备与计算机之间的通讯问题成了各种应用中关键的一个环节。

在各种通讯方式中,U SB 因其诸多优点而备受青睐。

FP GA 的可编程特性和速度快的特点使得其在数字电路设计中发挥着越来越重要的作用;在很多计算机的外围设备中,因为高速的要求而使用了FP GA ,但FP GA 与PC 机的通讯通常是系统中的瓶颈所在。

U SB 接口虽然有使用方便和传输速率快的特点,但因为U SB 的协议非常复杂,同时PC 机的驱动编写也很费精力,一般很难在短期内熟练掌握这些知识,这就使得很多设计人员对之望而却步。

而F T245BM 成功的实现了U SB 协议与并行I/O 协议之间的转换,避开了固件设计和驱动的编写,大大缩短了开发周期,成为开发U SB外围设备的上佳选择。

1、FT245BM 简介F T245BM 是F TDI 公司新推出的一款U SB芯片,该芯片功能强大,传输速率快,能够实现U SB 协议与并行I/O 协议之间的转换,并支持U SB1.1及U SB2.0规范,数据传输速率可达1MB/S 。

F T245BM 内部主要由U SB 收发器、串行接口引擎(SIE )、U SB 协议引擎和FIFO 控制器等构成。

片内128byte 的接收FIFO 和384byt 的发送FIFO 使得芯片可以实现高速数据吞吐。

而内嵌的EEPROM接口单元可外接串行存储器93C46,用来存储U SB取电模式及各种产品信息。

F T245BM还包括1个内置的3.3V的稳压器,1个6M Hz的振荡器、8倍频的时钟倍频器和U SB内部锁相环。

F T245BM采用32脚的PQ FP封装,体积小巧,易于嵌入到其它系统中去。

2、硬件设计F T245BM支持U SB总线取电和系统自取电两种模式。

采用U SB总线取电时的最大电流可以到500mA,这个电流基本满足一般系统的要求,使得设备真正做到即插即用,在设计移动设备时可以考虑用此模式;若系统功耗比较大,建议采用自取电模式以保证安全。

F T245BM实现与FP GA的接口,主要通过8根数据线及读写控制线来完成和FP GA的数据交互。

当前的FP GA管脚的电压标准有5V,3.3V,2.5V,1.8V,1.5V几种,根据不同的配置F T245BM可以支持5V和3.3V两种标准,如果使用其它几种I/O电压标准则需另接电压转换器。

系统中使用了Altera公司的ACEX1K50芯片,该芯片内部采用2.5V供电,I/O支持2.5V和3.3V三种标准,系统中使用了3.3V的I/O标准。

图1给出了F T245BM与ACEX1K50的接口电路:该电路采用自取电的模式,3.3V I/O标准。

D0~D7为数据线,RDP、WR、TXD、RXF为读写图1 F T245BM25ACEX1K50的接口电路控制线。

通过PWREN的状态可以获知当前U SB是否处于挂起状态,在挂起状态下不可以进行读写操作。

如果要系统具有唤醒PC的功能,还需将F T245BM的引脚SI/WU连到FP GA的I/O端口上。

电路图中的ACEX1K50外接了两片RAM,用于对数据进行缓存;ACEX1K50的内部已经集成了24kbit的静态RAM,在数据量较小时可以省去外面的两片RAM而直接用其内部集成的RAM。

F T245BM与FP GA之间的数据交互是通过查询的方式进行的,RXF和TXE分别为读写的查询标志,时序图如下:331第1期蔡江洪,史小军等:利用FT245BM实现FP GA与PC机的USB通讯图2 RXF时序图图3 TXE 时序图ACEX1K50中对应的Verilog HDL 程序://从F T245BM 读取数据always @(posedge clk )beginif (!RXF ) //判断读取标志是否有效begin case (Rnd_State ) 0: begin USB_RD <=0; Rnd_State <=Rnd_State +1; end 1: begin //将USB 传来的数据读取到Read_Data 中 Read_Data <=USB_DA TA ; Rnd_State <=Rnd_State +1; end 2: begin Rnd_State <=0; USB_RD <=1; end endcaseend end//将数据写入F T245BM always @(posedge clk )beginif (!TXE ) //判断写入标志是否有效begin case (Wrt_State ) 0:begin Wrt_State <=Wrt_State +1; USB_WD <=1; end 1:begin //将要写入的数据赋给USB_DA TA U SB_DA TA <=Write_Data ; Wrt_State <=Wrt_State +1; end 2:begin Wrt_State <=0; U SB_WD <=0; end endcaseend end需注意的一点是,因为程序中既有读过程又有写过程,须将FP GA 中与数据相连的I/O 口定义为三态,读出时为“高阻”,写入时为“输出”;读写过程需分时操作,否则会引起错误。

4、软件编写当F T245BM 的U SB 接口连到主机时,需在PC 机上装上驱动才可以使用。

F TDI 公司提供了两种驱动,分别为Virt ual COM Port Drivers 和D2XX DLL U SB Drivers 。

前者是将U SB 设备映射为计算机的一个串口,其PC 编程完全与串口编程一样,此处不加赘述;后者提供了一个动态连接库,内部包含了一套函数,使用该驱动传输速率可以达到1MB/S ;如下为使用该驱动的程序范例。

F T_HANDL E ft Handle ;F T_STA TUS ft Status ;DWORD EventDWord ,RxBytes ,RxBytes ,BytesReceived ,BytesSend ;char RxBuffer[256],TxBuffer[256];//打开器件ft Status =F T_Open (0,&ft Handle );if (ft Status ==F T_O K ){::AfxMessagebox (“打开成功,可以对USB 进行其它操作。

”);}else {::AfxMessagebox (“打开失败,给出错误提示。

”);}//从USB 读取数据F T _Get Status(ft Handle ,&RxBytes ,&TxBytes ,&EventDWord );if (RxBytes >0){ftStatus =FT_Read (ft Handle ,RxBuffer ,RxBytes ,&BytesReceived );if (ft Status ==F T_O K ){::AfxMessagebox (“读取成功,可以进行后续操作。

”);}else {::AfxMessagebox (“读取失败,给出错误提示。

”);}}//向USB 写入数据ft Status =F T _Write (ft Handle ,TxBuffer ,TxBytes ,&BytesSend );(下转第137页)431电 子 器 件28卷淀积的3#样品的钝化效果相对较好。

3 结 论由实验结果可以看出,硫处理后的GaAs M ESFETs再经PECVD SiNx钝化,硫钝化的稳定性得到了改善,尤其是在低温/高温SiN x淀积条件下,不但硫钝化的稳定性较好,而且击穿电压较高,与只进行常规PECVD SiN x钝化的GaAs M ESFETs相比,击穿电压高出了4V。