网络接口芯片DP83640技术说明书

用于水听器线列阵的精密时钟同步方法

用于水听器线列阵的精密时钟同步方法陈劲;段发阶;蒋佳佳;常宗杰;华香凝;李彦超【摘要】针对海洋水声探测时水听器间的数据采集同步问题,提出了一种全阵列精确同步的采集时钟产生与传递方法.采用独立的高精度主时钟、异步差分传输线和从时钟端的锁相环(PLL),实现了多节点长时间不间断工作方式下的同步采集,具有抗干扰能力强、同步性能好的特点.建立了时钟同步模型,详细分析了同步延迟的产生环节.通过电路实验验证了整个方案的可行性,在经过长度为18 m的非屏蔽双绞线传递后,恢复的从时钟延迟不大于165 ns,且与距离成线性正比关系.所提方法已经用于实际的水听器阵列数据采集系统,取得较好的效果.%The paper proposed a precise full-array-synchronization data acquisition clock generation and transmission method to handle the hydrophone's data acquisition synchronization problem in the ocean underwater acoustic detection. By using the independent high-precision clock source and asynchronous differential transmission lines, the long distance synchronous acquisition of the hydro-phone's array was realized, which was characterized with high anti-jamming capability and so on. The detailed model of the full-array-synchronization principle was analyzed and the prototype system was established. Circuits experiment was carried out to verify the feasibility of the entire system. Recovered clock's time delay in the acquisition node was less than 165 ns when the low-speed synchronous clock signal was transmitted by the unshielded twisted pair of 18 meters length. The experimental results show that the proposed method has good effectwhen being applied to transfer the standard clock of data acquisition inthe linear array.【期刊名称】《计算机应用》【年(卷),期】2013(033)002【总页数】3页(P600-602)【关键词】水听器阵列;数据采集;精确同步;温补压控晶振【作者】陈劲;段发阶;蒋佳佳;常宗杰;华香凝;李彦超【作者单位】精密测试技术及仪器国家重点实验室(天津大学),天津300072;天津师范大学物理与电子信息学院,天津300387;精密测试技术及仪器国家重点实验室(天津大学),天津300072;精密测试技术及仪器国家重点实验室(天津大学),天津300072;精密测试技术及仪器国家重点实验室(天津大学),天津300072;精密测试技术及仪器国家重点实验室(天津大学),天津300072;精密测试技术及仪器国家重点实验室(天津大学),天津300072【正文语种】中文【中图分类】TP840 引言水听器线列阵数据采集的同步性能直接关系到波束形成及反演的效果[1],因此,对其同步技术进行研究具有实际的意义。

基于DP83640的秒脉冲移相器设计与实现

路,最后给出了平均相移准确度的测试结果。

两级 DP83640 级联可 弥 补 单 个 DP83640 芯 片 输 出

而两级以上 的 DP83640 芯 片 进 行 级 联 虽 也 能 实 现

1PPS 信号的相位 微 调,但 对 最 小 相 移 分 辨 力 没 有

提升,反 而 会 增 加 电 路 噪 声,故 采 用 两 级 DP83640

1 秒脉冲精密移相器的设计和移相原理

芯片级联作为精密移相器的核心部分。

1

.1 系统设计

芯片将 Δϕ 拆 分 为 小 于 8ns 的 相 位 偏 移 量 Δϕ1 和

秒脉冲移相器设 计 如 图 1 所 示,其 主 体 部 分 由

8110

.2024

.01

.014

j

基于 DP83640 的秒脉冲移相器设计与实现

崔海波1,2,3,王

康1,3,武建锋1,2,3

(

1

. 中国科学院国家授时中心,西安 710600;

2

. 中国科学院大学,北京 101408;

3

. 时间基准及应用重点实验室(中国科学院),西安 710600)

摘

要:使用 DP83640IEEE1588 精密时间协议(

PTP)收发芯片设计实现了一款秒脉冲精密移相

器,它能与外部的标准秒脉 冲 (

1PPS)进 行 同 步 并 进 行 精 密 相 位 微 调,可 应 用 于 高 精 度 相 位 微 跃

器。秒脉冲移相器采用 DP83640 芯片进行级联实现秒脉冲精密移相:利用 ARM 微处理器控制第

二级 DP83640 实现与外部标准 秒 脉 冲 的 相 位 粗 调,控 制 第 一 级 DP83640 实 现 相 位 微 调。 相 位 调

基于DP83640的IEEE1588协议实现方案

基于DP83640的IEEE1588协议实现方案作者:周飞马强栾军英杨通强来源:《价值工程》2012年第23期摘要: IEEE1588精确时钟同步协议能够为网络中的各节点提供高精度的时钟同步,在测量和控制系统中具有广泛的应用前景。

本文设计了一种嵌入式环境下两个节点进行同步的IEEE-1588协议实现方案,达到了不低于20ns的同步精度。

关键词:时钟同步;IEEE1588;DP83640中图分类号:TP39 文献标识码:A 文章编号:1006-4311(2012)23-0307-030 引言IEEE1588协议以以太网为通信介质,通过主、从设备在网络上交互同步报文使得从设备能够不断计算出网络线路延迟和主从时钟时间偏差,并利用该时间偏差调整本地时钟,使本地时钟始终与主时钟保持一致以实现时间同步。

IEEE1588协议同步的精度取决于时间戳的精度。

采用软件的方式在网络协议上层标记的时间戳会由于操作系统和网络协议栈的延迟带来较大误差。

要实现高精度的时间同步就必须采用硬件辅助的方式在网络协议栈的最底层即物理层(PHY)为同步报文标记时间戳。

DP83640芯片是美国国家半导体公司推出的具备IEEE1588协议硬件支持功能的以太网物理层芯片,它内置一个精度为8ns的IEEE1588数字时钟,能够在报文发送和接收时精确标记时间戳。

本文使用DP83640芯片在S3C2440A型ARM处理器和WinCE5.0操作系统构成的嵌入式系统环境下实现了IEEE1588协议,对两个节点进行同步测试,达到不低于50ns的同步精度。

1 硬件设计DP83640是PHY芯片,不能直接与S3C2440A处理器通信,需要在二者之间加入MAC芯片。

在本文中使用的MAC芯片是DM9000芯片,DM9000向上通过16位数据\地址复用总线与S3C2440A处理器连接,如图1所示;向下通过介质无关接口(MII)与DP83640芯片连接,如图2所示。

第3版-DP83640的《LXI_DP83640逻辑设计方案说明》

LXI_DP83640逻辑设计方案说明作者:金建平日期:2010-5-16一、逻辑设计框图注:SMI(serial manage interface)串行管理接口2、MDIO接口转换模块说明(1)当对DP83640的MII管理接口做写操作时,工作流程如下:将待发送的16bit数据送到SendData总线上,保持稳定不变。

将控制命令+PHY地址+寄存器地址组成的16bit地址信息送到ADDR 总线上,保持稳定。

[15:14] =01 表示start。

[13:12] =01 表示 write 命令。

[11:7] = PHY地址,根据DP83640的外部配置管脚决定,默认00001。

[6:2] = Register地址,DP83640内部的寄存器地址。

[1:0] = 10 表示TA,结束启动发送,由控制模块将Start信号置高,表示启动一次发送;控制模块应该及时将start清零。

发送开后Busy信号置高,表示忙,直到发送结束才自动清零。

结束一次发送(2)当要对DP83640作读寄存器操作时,步骤如下。

将控制命令+PHY地址+寄存器地址组成的16bit地址信息送到ADDR 总线上,保持稳定。

[15:14] =01 表示start。

[13:12] =10 表示 read 命令。

[11:7] = PHY地址,根据DP83640的外部配置管脚决定,默认00001。

[6:2] = Register地址,DP83640内部的寄存器地址。

[1:0] = ZZ 表示高阻启动发送,由控制模块将Start信号置高,表示启动一次读数;控制模块应该及时将start清零。

发送开后Busy信号置高,表示忙,直到读数发送结束才自动清零。

读回的数倍送到reciveData总线上,保持稳定。

三、DP83640控制模块说明地址空间分配,接收cpu过来的数据及命令,完成指令分析,形成对“MDIO 接口转换模”的控制信号。

完成一个数据的读写,SMI接口需要32us以上时间。

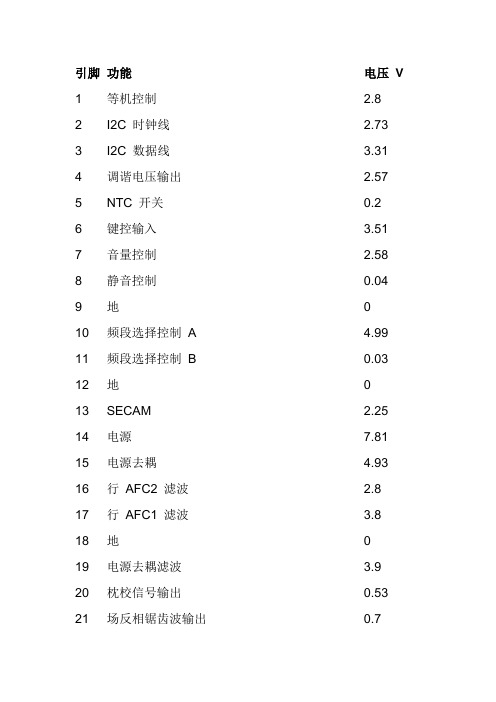

TDA8360A引脚功能Microsoft Word 文档

引脚功能电压V1 等机控制 2.82 I2C 时钟线 2.733 I2C 数据线 3.314 调谐电压输出 2.575 NTC 开关0.26 键控输入 3.517 音量控制 2.588 静音控制0.049 地010 频段选择控制A 4.9911 频段选择控制B 0.0312 地013 SECAM 2.2514 电源7.8115 电源去耦 4.9316 行AFC2 滤波 2.817 行AFC1 滤波 3.818 地019 电源去耦滤波 3.920 枕校信号输出0.5321 场反相锯齿波输出0.722 场正相锯齿波输出0.723 中放输入 1.824 中放输入 1.825 基准电流输入 3.826 场锯齿波形成电容 3.727 高放AGC 输出 1.928 去加重电容 3.329 音频解调滤波 2.230 地031 伴音窄带锁相环滤波/ 伴音中频输入 2.232 自动音量调整滤波0.233 行驱动输出0.534 沙堡脉冲输出0.4535 外部音频信号输入 3.636 高压反馈/ 过压保护输入 1.737 中放锁相环滤波 2.3438 视频信号输出 3.039 电源7.840 视频信号输入 3.841 地042 AV 视频/S 端子亮度信号输入 3.243 S 端子色度信号输入 1.4544 中放音频信号输出 3.345 第二RGB/YUV 插入控制 2.246 DVD/CB 信号输入 2.4747 DVD/Y 信号输入 2.4748 DVD/CR 信号输入 2.3149 ABL 束电流限制输入/ 场保护输入 6.0850 暗电流检测输入 3.2551 R 基色输出 3.8852 G 基色输出 2.7853 B 基色输出 3.4954 电源055 地056 电源 3.357 地 1.7358 晶振信号输入 1.7359 晶振信号输出 1.7960 复位061 电源 3.5162 AV 选择控制输出1 0.0763 AV 选择控制输出2 0.0664 遥控信号入 4.97 TDA9370与TDA9373它集TV信号处理、微处理控制于一体的超级大规模64脚芯片电路,它的详细内容介绍很多的技术资料都有介绍。

DP83640_边界时钟和透明时钟说明

AN-1838© 2008 National Semiconductor Corporation 300615使用DP83640实现IEEE1588边界时钟以及透明时钟30061510图1. 参考时钟和管理接口的连接图由于MDC 信号也被用作一个时钟,所以MDC 上也需要一个时钟分配网络来确保在每个PHY 上有一干净的时钟信号。

图1所示是一个参考时钟和管理接口信号可行的连接例子。

2.1 PHY 编址由于广播写功能使用PHY 的地址0x1F ,边界和透明时钟设备就不应有任何PHY 绑定到地址0x1F 。

另外,PHY 地址0用来强迫PHY 在一个隔离状态下上电,如果某个设备使用物理地址0,使之退出隔离状态需要管理访问。

所有其它PHY 地址的使用都是有效的,没有限制。

由于在一个串行管理接口上只能有31个PHY 设备(保留一个地址用作广播),如果需要更多的设备,必须提供额外的串行管理接口。

同步以太网除正常以太网操作之外,DP83640也可用于一个100 Mb 同步以太网节点。

在这种工作模式下,所有端口可能用某一端口上的恢复时钟作为所有其它端口的参考时钟。

在一PTP 系统中,允许将超级主时钟频率传送给整个网络,对于同步以太网操作的详细资料可参见应用注释:AN-1730AN-1730 DP83640同步以太网模式:在PTP 应用中实现次纳秒精度。

/NSC 2A N -18383.0 IEEE1588的时钟控制.基本的PTP 时钟控制独立于运行方式,如边界时钟对于透明时钟。

在一个节点设备中,一个从设备会基于由PTP 消息时标确定的信息来更新PTP 时钟,设定比率的量则取决于测到的相对于主设备的比率差,这也包含时间调整和对按照协议测定的主设备时间偏移作修正。

在边界时钟或透明时钟里,PTP 时钟控制会以类似的方式伴随一个明显差异而产生。

对时钟控制的改变是对所有的PTP 时钟,而不是对单个时钟。

正像之前提到的,这可用串行管理接口支持的广播机制来完成,从而使送到每个PHY 的PTP 时钟可同时变化。

具备IEEE 1588和光纤模式的以太网收发器DP83640原理图

IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Automotive and Transportation /automotiveAmplifiers Communications and Telecom /communicationsData Converters Computers and Peripherals /computersDLP®Products Consumer Electronics /consumer-appsDSP Energy and Lighting /energyClocks and Timers /clocks Industrial /industrialInterface Medical /medicalLogic Security /securityPower Mgmt Space,Avionics and Defense /space-avionics-defense Microcontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omapWireless Connectivity /wirelessconnectivityTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2012,Texas Instruments Incorporated。

DP83640同步以太网模式_在PTP应用中实现次纳秒精度

DP83640

࣬ްڦথ ้ዓ

PTP้ዓ

PTP୲ۙ বஇड

Ԩ֖ں ้ዓ

PTPຕጴ ऺຕഗ

PTP CLK_OUT႑

30039703

图 2. 同步以太网模式被使能的DP83640内部时钟

2

AN-1730

DP83640୲ۙ বஇड

经验数据还说明了产生的高达125 MHz的从时钟并将其 与PTP主时钟连接的网络锁定和校准的性能。采用一个外部 精确时钟器件,例如NSC LMK3000系列的器件,可实现更高 的锁频时钟。

还需注意,若使能同步以太网模式,可以消除任何本 地从参考时钟的不稳定性,因为从PTP时钟被锁定到主时钟 上。

4.0 背景介绍

4.4 DP83640 时钟结构 DP83640具有几个内部时钟,包括本地参考时钟,一个

以太网接收时钟和一个PTP时钟信号源。同时还包括一个内 部的PTP数字计数器,以及可以控制数字计数器和PTP时钟 速率(频率)的逻辑(参见图1 )。

ᅜྪڦথຕ

25MHzྔ ևৗናई ኁናږഗ

DP83640

本应用注释首先提供了采用同步以太网模式测量主从结 点同步所得到的经验结果的总结。然后,提供了与同步以太 网模式相关的工作原理和拓扑限制有关的背景信息。接着讨 论了典型应用,通过经验数据清楚地解释了采用同步以太网 模式的潜在精度。本应用注释适用于下列产品:

DP83640

2.0 测量同步

同步精确性可定义为主时钟计数器和相应的同步从时钟 计数器之间的瞬间时差。通过测量在特定时间触发的主信号 和由本地同步时钟计数器在相同时间触发的相应从信号之间 的时间差,可以确定同步精度。通常,在PTP讨论的上下文 中,这些触发信号每1秒发生一次,故定义为平均每秒脉冲, 或称之为PPS(秒脉冲)信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DP83640Application Note 1729 DP83640 IEEE 1588 PTP Synchronized Clock OutputLiterature Number: ZHCA333DP83640 IEEE 1588 PTP Array同步时钟输出AN-1729© 2008 National Semiconductor Corporation 3003962A N -1729举例:在10 ms 内设定临时速率纠正持续时间为+3 ns :1.若要在默认参考时钟周期下实现1 ms 的临时速率持续时间,我们需要10 ms / 8 ns = 1250000个时钟周期(0x1312D0)。

若要在1250000个时钟周期实现+3 ns 的纠正,需要3 ns / 1250000 = 0.0000024 ns = 10308亚毫微秒/时钟周期(0x2844)。

2.将0x0013写入PTP_TRDH 。

3. 将0x12D0写入PTP_TRDL 。

4. 将0xC000写入PTP_RA TEH 。

5. 将0x2844写入PTP_RA TEL 。

3.1.1 最大速率纠正由于通常不需要较大的速率纠正(如大于100 ppm ),为1588时钟输出而对源信号的选择决定了最大速率纠正。

当使用FCO 时,最大有效速率纠正为0x1555555,即+/- 651 ppm 。

当使用PGM 时,最大有效速率纠正为0x3FFFFFF ,也即 +/- 1953 ppm 。

3.2 相位对准时钟输出相位的对准要求执行下列步骤:1. 确保已使能时钟输出引脚。

2. 在使能PTP 同步协议之前,使能时钟输出和PTP 时钟。

3. 使能单个事件的事件监控器以捕捉时钟输出引脚的上升沿。

4.通过对准的期望时间确定时钟输出失调:时钟输出周期,即事件时间标记模时钟输出周期。

5. 执行一个步长调整以对准时钟输出。

6. 在同步期间,所有的步长调节都应以时钟输出周期为单位。

举例:一个10 MHz 时钟输出的相位对准:1.确保时钟输出引脚是使能的。

在上电之前将GPIO1引脚拉到高电平,或清除PHYCR2寄存器(页面0,寄存器0x1C )的CLK_OUT_DISABLE 位(第2位)来实现该操作。

2.在10 M H z 处使能时钟输出:将0x 8019写入PTP_COC 寄存器中。

注意到0x19的十进制为25,用25去除250MHz 时钟。

使能PTP 时钟:将0x0004写入PTP_CTL 寄存器。

3.取CLK_OUT 相位错误的100个样值— 使能事件监控并得到事件的时间标记:— 将0x1CE1写入PTP_EVNT 寄存器。

— 将0x5CE1写入PTP_EVNT 寄存器中。

第一个写操作为CLK_OUT/GPIO12(时钟输出引脚)与事件7(尽管可使用任何事件)设置一个单独的事件捕捉。

第二个写操作执行相同的操作,并使能了捕捉。

— 读取PTP_ESTS 寄存器检查0位是否被设置。

如果没有,请等待并重复这一步。

— 一旦TP_ESTS 的0位被设定,通过对PTP_ESTS 值的7:6位加1,从而确定事件时间标记长度(1到4个16位字)。

— 确保事件数目为7,既PTP_ESTS 的4:2位的值等于7。

— 确保事件为上升沿。

通过PTP_ESTS 第5位的数值等于1来指示。

— 读取PTP_EDA T A 寄存器。

事件时间标记返回如下: i.事件纳秒位15:0 ii.事件纳秒位29:16 iii.事件秒位15:0 iv.事件秒位31:16— 从时间标记中减去三倍的参考时钟周期和11 ns ;对于通常为8 ns 的参考时钟周期,这个值为35 ns 。

由此对引脚输入延时和边沿检测进行了纠正。

— 计算相位误差为(100–(事件时间标记模100))。

若结果与时钟周期相等(在此为100 ns ),则相位误差为0。

若相位误差在时钟周期的10 ns 之内(在此为91-99 ns ),则设置”高值”标志。

这等同与负相位误差在-9到-1 ns 内的情况。

4.平均相位误差。

如果有小的正和负相位误差的样值,比如已设了高值(HighValue ),并且相位误差的样值小于10 ns ,则必须将时钟周期加到样值上,以便正确地做样值平均:— I f (HighValue & error[sample]<10)error[sample] += clkout_period5.若平均相位误差大于时钟周期,则减去时钟周期以得到最终的平均相位误差。

6. 计算纠正数值,其为平均相位误差加上两倍的参考时钟周期:— C orrection = 2 * ref_period + avg_phase_error 7.做单步1588时钟时间调整:— 将纠正值写入PTP_TDR 。

— 将PTP_STEP_CLK (0x8)写入PTP_CTL 。

3.2.1 链接丢失时维持相位对准在使用FCO 来产生CLK_OUT 信号时,链接的丢失会使CLK_OUT 信号在短时间内停止,造成相位对准丢失。

DP83640提供三种选择来维护CLK_OUT 与1588时钟对准,并在链接丢失时触发。

1.在已知100 Mb/s 的网络上使用自动协商建立链接。

在此情况下,将0x803F 对页面0寄存器0x1E 写两次。

这将使链接丢失后能保持CLK_OUT 的相位对准。

此外,通过用一个2.2千欧姆电阻下拉LED_SPEED 引脚电平,或将0x0181写入自动协商广播寄存器(ANAR ,寄存器0x04),DP83640可被束缚在仅告知100 Mb/s 的方式。

若链接速度允许是10 Mb/s ,则不用仅告知100 Mb/s 的方式。

2.网络速度为10 Mb/s 或者不能保证是100 Mb/s ,并且应用能容忍从PGM 到CLK_OUT 的稍高的抖动。

设置AN-17293PTP 时钟输出控制寄存器(PTP_COC ,页面6,寄存器0x14)中的14位(PTP_CLKOUT_SEL )。

3.要求CLK_OUT 上的时钟是低抖动,同时不采用选项1。

如果网络设置允许,强制物理层(PHY )进入已知的100 Mb/s 或10 Mb/s 方式。

在BMCR 寄存器(寄存器0x00)内,清除12位,禁止自动协商,设置13位为100 Mb/s 和8位为全双工。

4.0 抖动测试结果4.1 测试设置将器件与一个采用(版本1的)IEEE 1588精密时间协议的主时钟同步,以1秒的同步间隔和10毫秒的临时速率持续时间,执行了一系列的测试来测量时钟输出上的抖动。

使用T ektronix TDS784C 示波器,以单个周期(100 ns )和10 µs 延迟时信号(10 MHz )来测量抖动的直方图。

将探针连接到器件的时钟输出信号,使用了Tektronix TDS784C 内部的直方图功能在特定的延迟时间点捕捉时钟信号的上升沿。

在每个测试条件下大约能捕捉1000个数据点,并记录了直方图的峰峰值和标准偏差值。

4.2 测试条件下表总结了抖动测试设置的条件。

表1. 抖动测试的测试条件工作电压3.3 V 温度25 °C参考频率源板载25 MHz晶振时钟输出频率10 MHz IEEE 1588 PTP 同步间隔 1 s 临时速率持续时间10 ms4.3 测试结果下表显示了对于FCO 和PGM源的抖动测量。

表2. 抖动测试的结果来源周期到周期10 µs 延迟峰峰值(ps )标准偏差(ps )峰峰值(ps )标准偏差(ps )FCO 32053.134058.5PGM34053.21160267.5由此数据可显而易见,尽管FCO 源和PGM 源的(逐周期)短期抖动可相比拟,但使用PGM 源的长时间抖动性能较差。

以下图例,即图1,图2,图3和图4表征了在DP83640与主时钟同步的条件下,时钟输出信号的典型直方图。

30039610图1. 采用FCO 时钟源的逐周期的抖动直方图30039611图2. 采用FCO 时钟源的10 µs 延时抖动直方图30039612图3. 采用PGM 时钟源的逐周期的抖动直方图 4A N -172930039613图4. 采用PGM 时钟源的10 µs 延时抖动直方图5.0 时钟相位误差测试结果5.1 测试设置通过确定主时钟输出到从时钟输出引脚的时延可测得对主时钟的同步误差。

直接用1米的CAT5电缆连接器件。

用了IEEE 1588版本1,1秒的同步周期,100毫秒临时速率持续时间,激活时间标记插入,以及激活单步操作。

5.2 测试条件下表总结了时钟相位误差测试的设置。

表 3.相位误差测试的测量条件工作电压 3.3 V 温度25 °C参考频率源板载25 MHz 晶振时钟输出频率10 MHz IEEE 1588 PTP 同步间隔1s 临时速率持续时间100 ms5.3 示波器设置T ektronix TDS784C 示波器的配置如表4所示。

表4. 用于相位误差测试的示波器设置水平刻度25 ns/div 垂直刻度(CH1) 1 V/div 垂直刻度(CH2)500 mV/div 触发电平 1.58 V 触发模式上升沿扫描主扫5.4 测试结果下表说明了时钟相位误差测试结果的平均值和标准偏差。

表5. 时钟相位误差源周期到周期平均值(ns )标准偏差(ns )FCO 4.647 5.905PGM5.1346.381结果表明,时钟的相位误差与PCO 或PGM 的选择无关。

图5和图6表征了DP83640与主时钟同步的条件下,时钟输出相位误差的典型直方图。

30039614图 5. 采用FCO 时钟源的时钟输出相位误差30039615图 6 采用PGM 时钟源的时钟输出相位误差6.0 结论DP83640提供了一个高精度的低抖动时钟输出,对于IEEE 1588主时钟而言是频率对准的,同时也是相位对准的。

经验测试显示非常低的抖动(使用FCO 源时低于1 ns 的峰峰值和标准偏差)和精确的相位校准。

尽管测试结果表明使用FCO 源能有极好的长时间抖动性能,但使用PGM 时钟源具有多模(10 Mb/s 或100 Mb/s )运行的优点。

AN-1729注释 5A N -1729D P 83640 IE E E 1588 P T P 同步时钟输出重要声明德州仪器(TI)及其下属子公司有权在不事先通知的情况下,随时对所提供的产品和服务进行更正、修改、增强、改进或其它更改,并有权随时中止提供任何产品和服务。

客户在下订单前应获取最新的相关信息,并验证这些信息是否完整且是最新的。

所有产品的销售都遵循在订单确认时所提供的TI销售条款与条件。

TI保证其所销售的硬件产品的性能符合TI标准保修的适用规范。