udp芯片

可运行在单片机上的UDP通讯协议的实现

简单解释一下上面三个过程。初始化不用解释了。A R P 通讯是整个网络传输的开始,而且只 需要运行一次。在《单片机驱动 D M 9 0 0 0 网卡芯片(详细调试过程)【下】》最后的部分已经讲 清楚了。主要是解释第三条,u d p 通讯收发数据。 O S I 参考模型中 a r p 协议属于链路层(最底层),i p 协议比 a r p 协议高一层属于网络层(这 一层还包括 i c m p 和i g m p 协议),在往上一层是运输层,包括 t c p 协议和 u d p 协议。但是按我的 理解,从数据包格式的角度看,我把 a r p 协议与 i p 协议放在同一级别,我们接收到的数据包中 的前几十个字节用来判断是 a r p 协议还是 i p 协议,也就是说这两个协议是互补相容的(下面程 序中会做个过滤,数据包只接收 a r p 或i p 协议,最后处理的数据包中只能是 a r p 协议或者是 i p 协议)。这种互补相容的协议同样也适用于 t c p 协议和 u d p 协议上。既然有互不相容的协议,那 么也就有相容的协议了,这种相容的协议就是指一个协议必须依赖于另一种协议才能实就像一件外套,u d p 协议好比一件衬衫,而真正的数 据可以看做是穿衣服的人。穿衣服的人先穿上衬衫再穿外套,这两个协议之间的关系就是这样: u d p 协议将数据包起来,i p 协议又将 u d p 协议连同其中的数据一起包起来。也就是说,实际的数 据经过 u d p 协议的包装,在经过 i p 协议的包装之后才能发送出去。虽然看起来有些繁琐,但实 际计算机端就是这样识别数据的。 所谓的包装就是在被包装数据前加上一小段首部数据, 一般几 十个字节左右。 2 、A R P 协议的实现 这部分内容在《单片机驱动 D M 9 0 0 0 网卡芯片(详细调试过程)【下】》的后半部分已经讲 过,这里为了完整性再重复一次。 在写所有协议之前,有些全局变量需要事先设定一下,如 i p 地址、m a c 地址等信息。另外, 统一规定一下我们的单片机系统为“基板”,计算机端为“上位机”,以下叫起来方便。再规定 一下:c h a r 型是 8 位,s h o r t 型是 1 6 位,l o n g 型是 3 2 位。O K ! / * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * / u n s i g n e dc h a rm y _ m a c a d d r [ 6 ]={0 x 0 0 ,0 x 0 a ,0 x 0 0 ,0 x 0 1 ,0 x 0 2 ,0 x 0 3} ; / / 基板上 m a c 地 址,这里随便写 6 个字节。 u n s i g n e dc h a rm y _ i p a d d r [ 4 ]={1 9 2 ,1 6 8 ,1 ,2 0 7} ; / / 基板上 i p 地址,根据网关写入合适 值。 u n s i g n e dc h a rs e r v e r _ m a c a d d r [ 6 ]={0 x f f ,0 x f f ,0 x f f ,0 x f f ,0 x f f ,0 x f f} ; / / 上位机 m a c 地址,通过 a r p 协议获取后改变。 u n s i g n e dc h a rs e r v e r _ i p a d d r [ 4 ]={ 1 9 2 ,1 6 8 ,1 ,1 2 2 } ; / / 上位机 i p 地址,看自己的电脑, 这个应该会,不会就问问旁边的人吧。 u n s i g n e dc h a rt r a n s m i t _ b u f f e r [ 2 0 4 8 ]={0} ; / / 发送数据包缓存区 u n s i g n e dc h a rr e c e i v e _ b u f f e r [ 2 0 4 8 ]={0} ; / / 接收数据包缓存区 / * 如果为了节省 r a m ,这两个区可以共用一个(因为发送和接收数据可以分开进行,而且一般网 卡芯片内部都会有自己独立的接收和发送缓存的),容量也可以改小,写成“u n s i g n e dc h a r d a t a _ b u f f e r [ 1 0 0 0 ]={0} ; ”我的 r a m 比较多,所以用了两个区,而且占用很大空间。* /

ZYNQZC702之UDP组播实现

ZYNQZC702之UDP组播实现ZYNQ ZC702是一种嵌入式系统开发板,其中包含了Xilinx公司的可编程SoC (系统级芯片) Zynq-7000系列的一个型号。

该系列芯片集成了一个双核ARM Cortex-A9处理器和Xilinx的可编程逻辑部分,使得它成为一种功能强大且可灵活定制的嵌入式平台。

在ZYNQ ZC702上实现UDP组播,首先需要理解UDP (用户数据报协议)和组播 (Multicast) 的基本概念。

UDP是一种无连接的传输协议,它可以在IP网络上直接发送数据包,但不提供可靠性和可靠的传输保证。

组播是一种通信方式,允许一个主机向多个主机同时发送数据。

UDP组播在局域网或广域网中应用广泛,例如视频流传输、实时通信等。

接下来,我们可以按照以下步骤在ZYNQZC702上实现UDP组播:1. 配置网络接口:在ZYNQ ZC702上,可以使用Linux操作系统,通过配置网络参数来启用网络接口。

可以使用命令行或者配置文件来设置IP地址、子网掩码、网关等信息。

2. 创建UDP Socket:在Linux中,通过在应用层创建一个UDP Socket来实现UDP通信。

可以使用C语言的Socket编程接口,在应用程序中创建一个UDP Socket,并绑定到指定的IP地址和端口号。

3. 加入组播组:为了实现UDP组播,需要将Socket加入到组播组。

可以使用setsockopt(函数设置套接字选项,将Socket加入到指定的组播组。

组播地址通常是一个特定的IP地址范围,例如224.0.0.0到239.255.255.2554. 发送和接收数据:使用Socket的sendto(函数发送数据包到组播地址,或者使用recvfrom(函数从组播地址接收数据包。

数据包可以是任意长度的字节流,根据需要进行解析和处理。

5.处理组播数据:在接收到组播数据后,可以根据需要进行解析和处理。

如果需要对数据进行处理,可以使用C语言或其他编程语言来编写处理逻辑。

xilinx udp实现原理

xilinx udp实现原理Xilinx UDP(User Datagram Protocol)的实现原理涉及到FPGA(Field Programmable Gate Array)的设计和开发。

UDP是一种无连接的、不可靠的网络传输协议,它在IP网络上提供了简单的面向数据包的传输。

Xilinx是一家专门从事FPGA芯片设计的公司,他们的产品包括了各种用于FPGA设计的开发工具和IP核。

Xilinx FPGA上实现UDP协议的原理主要包括以下几个方面:1. IP核集成,Xilinx提供了UDP协议的IP核,用户可以将这些IP核集成到他们的FPGA设计中。

这些IP核包括了UDP的发送和接收功能,用户可以通过配置这些IP核来实现UDP协议的功能。

2. 时序设计,在FPGA设计中,时序是一个非常重要的因素。

UDP协议需要满足严格的时序要求,因为数据包的发送和接收需要在规定的时间内完成。

设计者需要确保时钟信号的稳定性和数据传输的准确性。

3. 数据处理,UDP协议需要进行数据的封装和解包装,同时还需要进行校验和错误处理。

在FPGA设计中,需要实现这些数据处理的功能,确保数据的准确传输。

4. 网络接口,为了能够与外部网络进行通信,FPGA设计中需要包含适当的网络接口电路,以便与外部网络设备进行数据交换。

总的来说,Xilinx FPGA上实现UDP协议的原理涉及到IP核的集成、时序设计、数据处理和网络接口等方面。

设计者需要充分理解UDP协议的工作原理,并结合FPGA的特性进行设计和开发。

同时,还需要考虑到性能、功耗和资源占用等方面的因素,以实现高效、稳定的UDP功能。

88E111调试心得

回想调试88E1111芯片时,遇到不少的心酸,花掉不少的money,从目前实现的UDP数据传输,ICMP ping包,ARP包,与大家一起分享一下,也许是受到调试时遇问题发帖求助,到热心网友的帮助的感慨吧;1、芯片Package:我选择的为《117-Pin TFBGA Package》,建议没有调试过以太网的不要选择BGA封装,最好选择PQFP封装,调试过硬件会懂得;2、硬件配置:通过芯片CONFIG[6:0]这7个引脚与外部信号相连接,得到不同的结果,例如传输速率、光线、以太网接口等,通过与外界不同管脚的连接也影响着寄存器,他们分别可以与VSS、LED_TX、LED_RX、LED_DUPLEX、LED_LINK1000、LED_LINK100、LED_LINK10、VDDO连接,依次代表3位从000到111的值;对于CONFIG[6:0]分别对应3位,每位都具有自己的含义,详见下datasheet P65;我选择的千兆以太网的配置为:CONFIG[0]--VSS,CONFIG[1]-- LED_RX,CONFIG[2]-- LED_LINK100,CONFIG[3]-- VSS,CONFIG[4]-- VDDO,CONFIG[5]-- VDDO,CONFIG[6]-- VSS,对照上面以PHY地址为例,有PHYADR为10000b,也可参照手册实例P64;3、MAC接口:通过上一步硬件配置知HWCFG_MODE[3:0]为1111,实际应该先确定传输速率、模式,再选择HWCFG_MODE[3:0]对应的值,参考手册P48,当选定此值时可知为GMII/MII to copper,接下来可以参照P48 GMII MAC接口图;在此不给我实际的原理图,真是有原因的,我原来做硬件时候就是参照别人的图纸做的,做回来的板子有部分好用,部分不好用,由于采用BGA封装,当时就以为是芯片没有焊接好(没用专用BGA焊接机),做了几种板子之后发现奇怪的现象,数据只能读,不能写,其他的一切都正常,猜想过板子使用发热、焊接内部助焊剂没有清洗干净等等,其实就是自己没有看手册,太相信别人的原理图,受先入为主的思想,认为只要好使过的板子原理就没有问题,如果以后遇到调试硬件问题,一定要回答datasheet中寻求答案,大神们早都知道的东西,可我在调试以太网给我上了深深一课,这也就是不给我画好板子原理图的原因,别给大家误导了!一切都得从根本出发!!!4、上拉电阻:一定要注意一些引脚需要上拉电阻,例如:MIC、MDIO、RESET 等引脚;5、电源地信号:88E1111有两种不同的电源2.5V、1.2V,对于2.5V需要区分不同的地方的供电,参照datasheet P73,我只把数字2.5V与模拟2.5V用磁珠分开,将地采用铺地的方式链接到一起;6、以太网网线接口:有的带有变压器,有的没有,这样就需要外加芯片转换,在两者直接转换时一定要对应好引脚,否则在做好硬件后,最起码的LINK都链接不上的。

以太网协议栈管理芯片CH392用户手册说明书

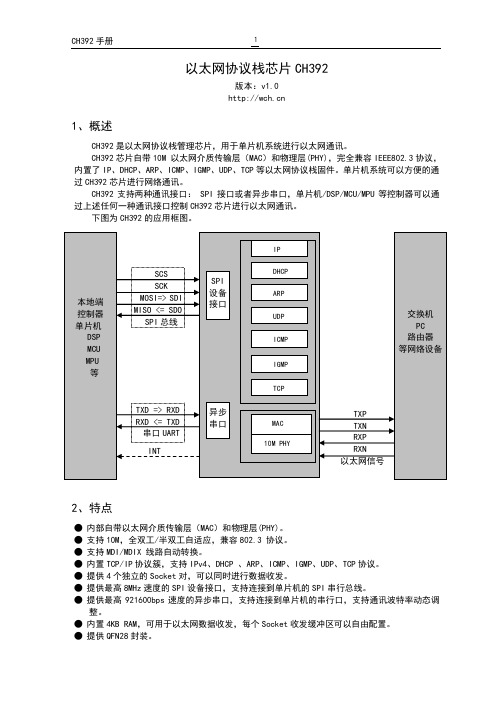

以太网协议栈芯片CH392版本:v1.0 1、概述CH392是以太网协议栈管理芯片,用于单片机系统进行以太网通讯。

CH392芯片自带10M 以太网介质传输层(MAC )和物理层(PHY),完全兼容IEEE802.3协议,内置了IP 、DHCP 、ARP 、ICMP 、IGMP 、UDP 、TCP 等以太网协议栈固件。

单片机系统可以方便的通过CH392芯片进行网络通讯。

CH392支持两种通讯接口: SPI 接口或者异步串口,单片机/DSP/MCU/MPU 等控制器可以通过上述任何一种通讯接口控制CH392芯片进行以太网通讯。

下图为CH392的应用框图。

2、特点● 内部自带以太网介质传输层(MAC )和物理层(PHY)。

● 支持10M ,全双工/半双工自适应,兼容802.3 协议。

● 支持MDI/MDIX 线路自动转换。

● 内置TCP/IP 协议簇,支持IPv4、DHCP 、ARP 、ICMP 、IGMP 、UDP 、TCP 协议。

● 提供4个独立的Socket 对,可以同时进行数据收发。

● 提供最高8MHz 速度的SPI 设备接口,支持连接到单片机的SPI 串行总线。

● 提供最高921600bps 速度的异步串口,支持连接到单片机的串行口,支持通讯波特率动态调整。

● 内置4KB RAM ,可用于以太网数据收发,每个Socket 收发缓冲区可以自由配置。

● 提供QFN28封装。

INT本地端 控制器 单片机 DSP MCU MPU 等 SPI设备 接口 异步 串口 SCS SCK MOSI=> SDI MISO <= SDO SPI 总线 TXD => RXD RXD <= TXD 串口UART 10M PHY交换机 PC路由器 等网络设备 TXP TXN RXPRXN 以太网信号IPARP ICMP IGMP UDP TCP DHCP MAC3、封装芯片型号芯片封装名称描述CH392F QFN28 QFN封装;28脚;本体4x4mm 4、引脚CH392F 引脚号引脚名称类型引脚说明0 GND 电源芯片接地端3,4,22 VCC 电源内部电源,需外接0.1uF退耦电容5 VDD 电源 3.3V工作电压输入,外接2.2uF退耦电容6 RXD 输入异步串口数据输入,内置上拉电阻7 TXD 输出异步串口数据输出,内置上拉电阻8 RXP 以太网信号以太网RXP信号9 RXN 以太网信号以太网RXN信号10 TXP 以太网信号以太网TXP信号11 TXN 以太网信号以太网TXN信号12 INT 输出中断信号输出,低电平有效14 ACT 输出以太网连接通讯指示灯驱动引脚15 LINK 输出PHY连接指示引脚,低有效16 RSTI 输入外部复位输入,低电平有效18 XO 输出晶体振荡的反相输出端,需要外接32MHz晶振19 XI 输入晶体振荡的输入端,需要外接32MHz晶振20 VREF 电源内部模拟电路电源节点,需外接 1uF 退耦电容23 SEL 输入通讯接口选择引脚,内置上拉,高电平选择串口,低电平选择SPI25 SDO 输出SPI数据输出26 SDI 输入SPI数据输入27 SCK 输入SPI时钟输入28 SCS 输入SPI片选输入1,2,13,17,21,24NC NC 保留管脚,悬空5、命令本手册中的数据,后缀B为二进制数,后缀H为十六进制数,否则为十进制数。

ch395_nios_UDP调试

一、Socket0工作在UDP 模式

板极调试:

1、下载sof 文件,在nois_Eclipse 上运行软件工程。

Run As “Nios II Hardware ”。

Nios II Console 窗口,打印运行版本和连接信息。

如下图所示。

1、打开“科来软件分析系统”,建立一个UDP 数据包

.

2

、在PC 端发送UDP 协议的IP 包后,如图所示,Nios II Console 窗口打印除了新接收到的18个字节数据,随后取反并发送出去了。

如下图所示为ch395芯片接收到的18个数据。

发送数据

Ch395芯片与PC

网络连接成功

3、打开“科来软件分析系统”,在协议浏览器的IP栏里找到PC与CH395芯片通信的2个UDP数据包,即192.168.0.23和192.168.0.64互为源IP地址互发的UDP包。

确认PC与CH395成功实现实验通信。

上图为PC发送数据至CH395芯片的UDP数据包

图CH395芯片将数据取反后,发送至PC机的UDP数据包。

(完整版)88E111调试心得

回想调试88E1111芯片时,遇到不少的心酸,花掉不少的money,从目前实现的UDP数据传输,ICMP ping包,ARP包,与大家一起分享一下,也许是受到调试时遇问题发帖求助,到热心网友的帮助的感慨吧;1、芯片Package:我选择的为《117-Pin TFBGA Package》,建议没有调试过以太网的不要选择BGA封装,最好选择PQFP封装,调试过硬件会懂得;2、硬件配置:通过芯片CONFIG[6:0]这7个引脚与外部信号相连接,得到不同的结果,例如传输速率、光线、以太网接口等,通过与外界不同管脚的连接也影响着寄存器,他们分别可以与VSS、LED_TX、LED_RX、LED_DUPLEX、LED_LINK1000、LED_LINK100、LED_LINK10、VDDO连接,依次代表3位从000到111的值;对于CONFIG[6:0]分别对应3位,每位都具有自己的含义,详见下datasheet P65;我选择的千兆以太网的配置为:CONFIG[0]--VSS,CONFIG[1]-- LED_RX,CONFIG[2]-- LED_LINK100,CONFIG[3]-- VSS,CONFIG[4]-- VDDO,CONFIG[5]-- VDDO,CONFIG[6]-- VSS,对照上面以PHY地址为例,有PHYADR为10000b,也可参照手册实例P64;3、MAC接口:通过上一步硬件配置知HWCFG_MODE[3:0]为1111,实际应该先确定传输速率、模式,再选择HWCFG_MODE[3:0]对应的值,参考手册P48,当选定此值时可知为GMII/MII to copper,接下来可以参照P48 GMII MAC接口图;在此不给我实际的原理图,真是有原因的,我原来做硬件时候就是参照别人的图纸做的,做回来的板子有部分好用,部分不好用,由于采用BGA封装,当时就以为是芯片没有焊接好(没用专用BGA焊接机),做了几种板子之后发现奇怪的现象,数据只能读,不能写,其他的一切都正常,猜想过板子使用发热、焊接内部助焊剂没有清洗干净等等,其实就是自己没有看手册,太相信别人的原理图,受先入为主的思想,认为只要好使过的板子原理就没有问题,如果以后遇到调试硬件问题,一定要回答datasheet中寻求答案,大神们早都知道的东西,可我在调试以太网给我上了深深一课,这也就是不给我画好板子原理图的原因,别给大家误导了!一切都得从根本出发!!!4、上拉电阻:一定要注意一些引脚需要上拉电阻,例如:MIC、MDIO、RESET 等引脚;5、电源地信号:88E1111有两种不同的电源2.5V、1.2V,对于2.5V需要区分不同的地方的供电,参照datasheet P73,我只把数字2.5V与模拟2.5V用磁珠分开,将地采用铺地的方式链接到一起;6、以太网网线接口:有的带有变压器,有的没有,这样就需要外加芯片转换,在两者直接转换时一定要对应好引脚,否则在做好硬件后,最起码的LINK都链接不上的。

以太网芯片的工作原理

以太网芯片的工作原理以太网芯片是计算机网络设备中的重要组成部分,负责将数据包传输到以太网上。

它的工作原理涉及到以下几个方面:1.数据编码:以太网将每个数据包划分为多个帧,每个帧由一系列比特组成。

以太网芯片会将数据从计算机的处理器传送到物理介质上,并对数据进行编码处理。

编码和解码过程使用的是物理层规范,如 Manchester 编码或4B/5B编码等。

2.数据传输:以太网芯片会将编码后的数据通过物理介质传输。

物理介质可以是铜缆、光纤或无线电波等。

传输过程中,以太网芯片会按照以太网协议的规范将数据帧发送出去。

发送过程中,会使用载波侦听多路访问(CSMA/CD)技术来协调多个设备之间的访问冲突和碰撞。

3.数据接收:当以太网芯片接收到一个数据帧时,它会进行数据的提取和解码。

首先,芯片会检查数据帧的前导码,并与预设的前导码进行比较,用于同步数据的接收。

之后,芯片会将数据进行解码,还原成原始的比特序列。

4.地址识别:每个以太网芯片都有一个唯一的物理地址,称为MAC 地址。

芯片在接收到数据帧后,会提取出帧头中的目标地址和源地址进行比较,以确定数据是否是发送给本机的。

如果目标地址与本机的 MAC 地址匹配,芯片将接受数据;否则,将忽略数据。

5.数据处理:一旦数据被接受,以太网芯片将数据传输到计算机的内存中,供处理器或操作系统使用。

这些数据可以被上层协议处理,如传输层协议 TCP 或 UDP。

总结起来,以太网芯片的工作原理可以概括为:数据编码、数据传输、数据接收、地址识别和数据处理。

通过这些步骤,以太网芯片实现了快速、可靠的数据传输和通信。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

udp芯片

UDP芯片是一种用于实现用户数据报协议(User Datagram Protocol,简称UDP)功能的集成电路芯片。

UDP是一种无连

接的传输协议,它与传输控制协议(TCP)相比,不提供数据

包的可靠性传输、流量控制和拥塞控制功能,但具有低延迟、高效率和简单的特点,常用于实时音视频传输、游戏和物联网等应用场景。

UDP芯片通常由相应的硬件电路和软件驱动程序组成,能够

直接对接网络接口和传输层协议栈,实现UDP协议的收发功能。

下面将从硬件和软件两个方面来介绍UDP芯片的特点和

功能。

硬件方面:

1. 网络接口:UDP芯片通常具备以太网接口,支持物理层和

链路层的通信,能够直接与以太网交换机或路由器相连接。

2. 存储器:UDP芯片内置一定的存储器,用于缓存发送和接

收的数据包,提高数据的处理速度。

3. 硬件加速器:UDP芯片可能还集成了硬件加速器,用于加

速UDP协议的处理,提高数据的传输速率和性能。

4. 电源管理:UDP芯片通常支持低功耗模式,能够根据需求

进行功耗管理,在不需要进行通信时降低功耗,提高节能效果。

5. 接口和引脚:UDP芯片提供了相应的引脚和接口,以便与

其他设备进行连接和通信,如提供GPIO、SPI、UART等接口。

软件方面:

1. 驱动程序:UDP芯片通常需要安装相应的驱动程序,用于

操作和控制硬件电路,实现UDP协议的发送和接收功能。

2. 库函数:UDP芯片通常提供相应的软件库函数,用于简化

开发者的编程工作,提供API接口,方便上层应用进行使用。

3. 协议栈:UDP芯片需要与操作系统或者嵌入式软件配合使用,通过操作系统提供的协议栈实现UDP协议的功能,完成

数据的传输与处理。

4. 配置和管理工具:UDP芯片通常提供相应的配置和管理工具,用于配置网络参数、调整UDP协议参数以及进行故障排

查和调试。

总结起来,UDP芯片是一种专门用于实现UDP协议功能的集

成电路芯片,通过硬件和软件的设计,能够提供UDP协议的

收发功能,具备低延迟、高效率和简单等特点,被广泛应用于实时音视频传输、游戏和物联网等领域。

随着物联网和实时通信应用的不断发展,UDP芯片的需求将会持续增长。