Debussy是一个VerilogVHDL调试工具

Debussy是一个VerilogVHDL调试工具

介绍一、Debussy是一个Verilog/VHDL调试工具Debussy是一套很好的Verilog/VHDL调试工具,可以帮助设计者快速理解复杂的设计,查找和定位设计中存在的问题,提高效率。

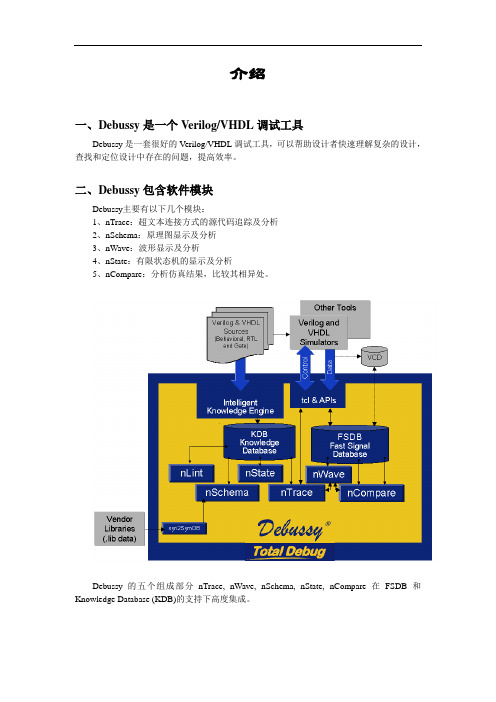

二、Debussy包含软件模块Debussy主要有以下几个模块:1、nTrace:超文本连接方式的源代码追踪及分析2、nSchema:原理图显示及分析3、nWave:波形显示及分析4、nState:有限状态机的显示及分析5、nCompare:分析仿真结果,比较其相异处。

Debussy的五个组成部分nTrace, nWave, nSchema, nState, nCompare在FSDB和Knowledge Database (KDB)的支持下高度集成。

三、Debussy功能Debussy直接编译Verilog/VHDL源代码,并且采用了预综合技术识别电路的单元,可以生成原理图。

在导入仿真结果后,可以用Active Annotation在源代码、原理图、状态图上动态显示变量的仿真值。

Debussy的输入为:Verilog/VHDL或混合语言源代码,仿真波形文件,SDF支持的波形格式:vcd,fsdb,模拟波形文件(PowerMill,TimeMill,Avant! Star-Sim,SmartSpice)支持的仿真器:VCS,Verilog-XL,NC-verilog,NC-VHDL,Modelsim,Leapfrog,Ploaris。

操作一、启动1. 启动%debussy启动debussy时,弹出一个nTrace窗口,包含三个子窗口:a、左边是Hierarchical Browser窗口,用来显示设计的层次(design hierachy)。

b、右边是Source Code window,显示源代码。

跟踪信号的驱动、负载。

c、底下是Message window(消息窗口),用来报告操作的结果。

2.导入设计File->Import DesignDebussy提供了两种导入设计的方法:A、从设计源文件直接导入B、从库导入(先将源文件编译成库)Note: 可以用命令的方式直接启动debussy并导入设计文件,即在命令行上列出所有的选项和源文件,或者把这些选项和源文件写到一个文件中,用-f选项指定这个文件。

verilog和VHDL混合编译仿真

verilog和VHDL混合编译仿真在实际项⽬中,由于项⽬经历了较多的版本更迭或者设计⼈员的技术⽔平限制,有些时候难免有使⽤到verilog的代码和VHDL代码共同存在⼀个项⽬中的情况,那这个时候我们要怎样进⾏混合编译仿真验证呢?这⾥以使⽤vcs⼯具编译verdi查看波形为例:如果我们设计代码是vhdl版本的,但是还想使⽤更⾼级的代码verilog或者systemverilog作为它的顶层tb,并且还想使⽤uvm的组件来搭建更⽅便的验证环境,那么整个环境的编译和执⾏过程如下:1.需要准备的软件vcs-mx和verdi,其中vcs-mx版本会有vlogan和vhdlan两个编译程序2.开始编译编译vhdl的代码,dut_src.f是vhdl的⽂件列表:vhdlan -nc dut_src.f -l cmp_vhdl.log编译uvm库的sv代码:vlogan -full64 -timescale=1ns/1ps +v2k -sverilog -ntb_opts uvm -l cmp_uvm.log编译我们⾃⼰设计的sv代码和⾃⼰设计的uvm各个组件部分的代码,tb.f是⽂件列表:vlogan -full64 -timescale=1ns/1ps +v2k -sverilog tb.f -ntb_opts uvm -l cmp_verilog.log编译vhdl和verilog各⾃的库⽣成可执⾏⽂件simv:vcs -timescale=1ns/1ps -ntb_opts uvm -top tb_top -debug_access+pp -fsdb -j56 -cm line+fsm+tgl+cond -lint=TFIPC-L +nbaopt +rad +notimingchecks +nospecify +error+30run起来,⽣成波形,其中TC_NAME是传⼊的tc参数:./simv -cm line+fsm+tgl+cond +fsdb+force +fsdbfile+../wave/tb_top.fsdb +UVM_TESTNAME=$(TC_NAME)3.查看波形编译出verdi可以查看的库,使⽤vhdlcom是编译vhdl⽂件的库,vericom是编译verilog⽂件的库vhdlcom -lib my_work dut_src.fvericom -lib my_work -sv tb_top.sv使⽤verdi打开波形⽂件:verdi -lib my_work -top tb_top -ssf tb_top.fsdb。

debussy和modelsim协同仿真(VHDL)

debussy和modelsim协同仿真(VHDL)1、编辑modelsim根目录下的modelsim.ini文件,将; Veriuser = veriuser.sl 更换为Veriuser = novas_fli.dll。

2、将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas_fli.dll 拷贝至C:\Modeltech_6.1d\win32中3、将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas.vhd拷贝至工程所在目录4、打开modelsim,在工程所在目录新建一个novas的LIB,然后编译novas.vhd文件。

5、在testbentch中增加library novas;use novas.pkg.all;6、在testbentch中添加debussy_debug:processbeginfsdbDumpfile("**.fsdb");fsdbDumpvars(0,"顶层文件名(有testbench的话即为testbench名)");wait;end process debussy_debug;7、编译整个工程,然后仿真8、打开debussy, import design加载文件,设置好顶层文件,打开nWARE,加入信号即可为了更加方便的使用DEBUSSY,我们可以编写DO文件来达到这一目的:1、先新建dc16_tca目录。

比如在E:/WORK/TEMP里新建该目录,把源程序都放在dc16_tca/soure里头。

2、编写tca.do文件:下面是以TCA为例说明一下这个步骤:tca.do:#start#建立并编译novas库vlib novasvmap novas novasvcom -work novas D:/WORK/temp/dc16_TCA/source/novas.vhd#建立并编译work库vlib workvcom -work work d:/work/temp/dc16_tca/source/dc16_constant_def.vhdvcom -work work d:/work/temp/dc16_tca/source/dc16_tca.vhdvcom -work work d:/work/temp/dc16_tca/source/dc16_tca_tb.vhdvsim dc16_tca_tb#仿真运行时间run 10000usquit#end3、然后在dos界面先进入到dc16_tca目录里,比如E:/WORK/TEMP/dc16_tca然后再输入>c:\modeltech_6.1b\win32/vsim -c -do tca.do这里假设modelsim装在C盘个人感觉modelsim的仿真速度用DO文件的方式比用modelsim的GUI方式要快很多。

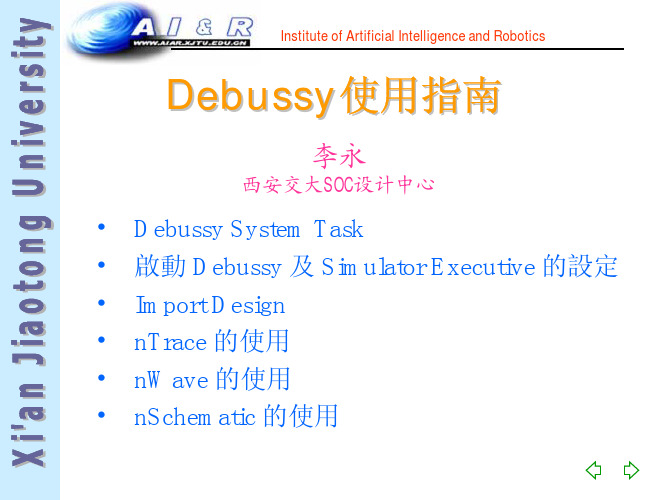

debussy使用指南

Liyong xjtu’soc center

Institute of Artificial Intelligence and Robotics

Debussy功能及包含软件模块

Debussy功能

Debussy直接编译Verilog\VHDL源代码,并且采用了预综合技术 识别电路的单元,可以生成原理图。在导入仿真结果后,可以用 Active Annotation在源代码、原理图、状态图上动态显示变量的 仿真值

nWave 的使用 (Cont.)

4. 選擇欲觀察的signal,以中鍵按住拖曳到右邊的視窗, 如圖所示。

い龄╈Σ:

娩跌怠

Liyong xjtu’soc center

Institute of Artificial Intelligence and Robotics

nWave 的使用 (Cont.)

Liyong xjtu’soc center

Institute of Artificial Intelligence and Robotics

nTrace 的使用 (Cont.)

¤ Â_

ÂI ªº

²Å

¸¹

¼Ð°O

Liyong xjtu’soc center

Institute of Artificial Intelligence and Robotics

Liyong xjtu’soc center

Institute of Artificial Intelligence and Robotics

nSchematic 的使用

1. 在 Import Design 完成之後,進入 Interactive Mode。 2. 按 New Schematic icon ,會出現程式相對應的電路 圖。

FPGA系统设计

知识产权IP——Intellectual Property

经过预先设计、预先验证,符合产业界普遍 认同的设计规范和设计标准,具有相对独立 功能的电路模块或子系统。可以复用(Reuse) 于SOC、SOPC或复杂ASIC设计中。

Quartus II软件及其应用

软件总体框图 典型设计流程 设计输入 编译器选项设置 适配器选项设置

特性

NiosⅡ嵌入式开发软件

DSP Builder系统设计工具

DSP Builder是Altera推出的一个DSP开发工具,它在 Quaruts II FPGA设计环境中集成了MathWorks的 Matlab和Simulink DSP开发软件。Altera的DSP系统 级设计将FPGA的应用领域扩展到的基于主流DSP的 应用,是第一款基于C代码的可编程逻辑设计流程。

嵌入式系统——Embedded System

嵌入式处理器软核以Altera公司的第一代Nios及第二代Nios II 为先进代表。Nios II嵌入式处理器是一种采用流水线技术,单 指令流的RISC (Reduced Instruction Set Computing)处理器,其 大部分指令可以在一个时钟周期内完成。

与嵌入式硬核相比,嵌入式软核具有更大的使用灵活性。

片上系统SOC——System on chip

可编程片上系统SOPC——System On a Programmable Chip

SOC是专用集成系统,设计周期长,设计成 本高。而SOPC是一种通用器件,是基于 FPGA的可重构SOC。设计周期短,设计成 本低。

设计输入

设计综合

布局、布线

Synplify Synopsys ModelSim Debussy 等

FPGA开发-使用modelsim和debussy做rtl仿真

1 引言

做 ASIC 或者 FPGA 设计中,选择合适的软件工具,对工作的开展有很大的帮助,一杆 利器,绝对可以使工作事半功倍。在 Windows 环境下做 rtl 开发(Verilog/VHDL),modelsim 是主流的仿真工具。Modelsim 虽然仿真速度快,功能强大。但是在调试查看波形时,便利 性远比不上 debussy。 或许大家对 debussy 有些陌生, 但是说到 linux 下被广泛使用的 verdi, 应该熟悉。Debussy 就是 verdi 的 Windows 版本,都是思源科技 NOVAS 开发的波形调试工 具,具有相同的源码。Debussy 和 verdi 具有相同的操作界面,熟悉 verdi 的工程师,使用 debussy 很容易上手。

图 6 Debussy 导入设计

4.

选中”From File”选项卡,然后在左下方的窗口中,按路径依次双击文件夹并打开, 找到 nv_lab1.f 的位置, 这时右下侧窗口显示出 nv_lab.f 文件, 双击该文件, 把 nv_lab.f 添加到了 Design Files 列表中,如图 7。然后点击 OK 按钮,则在 Debussy 中打开 了 lab1 的设计。

图 8 Debussy 中打开波形窗口

图 9 打开的波形窗口

6.

在波形窗口菜单栏,点击 File Open,在弹出的对话框中按路径找到 sim_top.fsdb 文件,双击,打开波性文件,如图 10 所示。

图 10 找到并打开波性文件

7.

查看信号波形。如图 11 所示,切换到 debussy 主界面,通过左边的导航栏,找到 想查看的文件并双击打开, 在文件中选中需要观察的信号, 可以按住鼠标左键拖动, 选中多个新号,选中后按 ctrl+w 键,把信号添加到波形窗口中。

Debussy 仿真快速上手教程

Debussy 仿真快速上手教程Debussy 介绍Debussy 是NOVAS Software, Inc(思源科技)发展的HDL Debug & Analysis tool,这套软体主要不是用来跑模拟或看波形,它最强大的功能是:能够在HDL source code、schematic diagram、waveform、state bubble diagram之间,即时做trace,协助工程师debug。

可能您会觉的:只要有simulator如ModelSim就可以做debug了,我何必再学这套软体呢? 其实Debussy v5.0以后的新版本,还提供了nLint -- check coding style & synthesizable,这蛮有用的,可以协助工程师了解如何写好coding style,并养成习惯。

下图所示为整个Debussy 的原理架构,可归纳几个结论:Debussy有四个主要单元(component),nTrace、nWave、nSchema、nStatenTrace -- Hypertext source code analysis and browse tool (为%Debussy &所开启的主画面)nWave -- Waveform analysis tool (可由nTrace内开启,或直接%nWave &开启)nSchema -- Hierarchy schematic generatornState -- Finite State Machine Extraction and analysis toolDebussy本身不含模拟器(simulator),必须呼叫外部模拟器(如Verilog-XL or ModelSim)产生FSDB file,其显示波形的单元"nWave"透过读取FSDB file,才能显示波形或讯号值的变化快速上手五部曲:(Debussy v.5.2)1. Import Files and generate FSDB file2. Trace between hierarchy browser and source code3. Trace between hierarchy browser、source code and schematic4. Trace between hierarchy browser、source code、schematic and waveform5. nLint(nState本文没介绍,有兴趣的读者,请依文后的连结,自行下载CIC所提供的NOVAS原厂编写教材参考)1. Import Files and generate FSDB file1-1 启动Debussy:% Debussy & (此处的D大小写都可以,但其它指令的大小写可能就有差别)开启nTrace window如下,此时工作目录下会新建一个"DebussyLog"目录1-2 Import Files:File \ Import Design...结果如下图所示:nTrace视窗中,含有三个区域,Hierarchical Brower、Source code window、Message window。

模电数电题面试题集锦

模拟电路知识1、基尔霍夫定理的内容是什么?基尔霍夫定律包括电流定律和电压定律电流定律:在集总电路中,任何时刻,对任一节点,所有流出节点的支路电流的代数和恒等于零。

电压定律:在集总电路中,任何时刻,沿任一回路,所有支路电压的代数和恒等于零.2、描述反馈电路的概念,列举他们的应用。

反馈,就是在电子系统中,把输出回路中的电量输入到输入回路中去.反馈的类型有:电压串联负反馈、电流串联负反馈、电压并联负反馈、电流并联负反馈.负反馈的优点:降低放大器的增益灵敏度,改变输入电阻和输出电阻,改善放大器的线性和非线性失真,有效地扩展放大器的通频带,自动调节作用.电压负反馈的特点:电路的输出电压趋向于维持恒定。

电流负反馈的特点:电路的输出电流趋向于维持恒定。

3、有源滤波器和无源滤波器的区别无源滤波器:这种电路主要有无源元件R、L和C组成有源滤波器:集成运放和R、C组成,具有不用电感、体积小、重量轻等优点.集成运放的开环电压增益和输入阻抗均很高,输出电阻小,构成有源滤波电路后还具有一定的电压放大和缓冲作用。

但集成运放带宽有限,所以目前的有源滤波电路的工作频率难以做得很高。

6、FPGA和ASIC的概念,他们的区别.(未知)答案:FPGA是可编程ASIC。

ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。

根据一个用户的特定要求,能以低研制成本,短、交货周期供货的全定制,半定制集成电路。

与门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点。

7、什么叫做OTP片、掩膜片,两者的区别何在?OTP means one time program,一次性编程MTP means multi time program,多次性编程OTP(One Time Program)是MCU的一种存储器类型MCU按其存储器类型可分为MASK(掩模)ROM、OTP(一次性可编程)ROM、FLASHROM 等类型。

Debussy仿真快速上手教程

目录Debussy 仿真快速上手教程错误!未定义书签。

Debussy 介绍......................................................................................... 错误!未定义书签。

1. Import Files and generate FSDB file ............................................. 错误!未定义书签。

1-1 启动Debussy ........................................................................... 错误!未定义书签。

1-2 Import Files ............................................................................... 错误!未定义书签。

1-3 设定外部模拟器 ..................................................................... 错误!未定义书签。

1-4 切换到Interactive Mode ......................................................... 错误!未定义书签。

1-5 结束程式 ................................................................................. 错误!未定义书签。

1-6 快速启动执行序 ..................................................................... 错误!未定义书签。

1-7 其他启动Debussy的方法...................................................... 错误!未定义书签。

MODELSIM经典教程

Liyong xjtu’soc center

4 Ö 添加波形

• GUI) view -> structure • GUI) view -> signals • GUI) view -> wave

选择需要显示的module 选择所要显示的信号 将所选择的信号调入波形窗口

17

Institute of Artificial Intelligence and Robotics

Liyong xjtu’soc center

工程文件test.mpf

1)当下次再次打开这个工程时, modelsim从mpf文件中读取关于库 的定位、启动文件的定位、 ModelSim其他缺省设定等信息 2)在建立工程时,modelsim从初始 化文件 modelsim.ini中获取各种信 息,包括[Library] [vcom] [vlog] [vsim] [lmc],因此有必要修改 modelsim.ini文件以改变一些缺省 信息。 3)缺省modelsim.ini文件存在 modelsim的安装目录下,为只读 文件。 4)modelsim.ini文件的搜索顺序为 : a)环境变量所指的文件架 b)当前的工作目录 c)modelsim的安装目录

15

Institute of Artificial Intelligence and Robotics

Liyong xjtu’soc center

3 Ö 启动仿真器(load design)

GUI) design -> load design

16

Institute of Artificial Intelligence and Robotics

Wave窗口操作

通过在wave窗口可以通过菜单、工具栏和在选中信号后 点右键来完成相应的调试工作。 19

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

介绍

一、Debussy是一个Verilog/VHDL调试工具

Debussy是一套很好的Verilog/VHDL调试工具,可以帮助设计者快速理解复杂的设计,查找和定位设计中存在的问题,提高效率。

二、Debussy包含软件模块

Debussy主要有以下几个模块:

1、nTrace:超文本连接方式的源代码追踪及分析

2、nSchema:原理图显示及分析

3、nWave:波形显示及分析

4、nState:有限状态机的显示及分析

5、nCompare:分析仿真结果,比较其相异处。

Debussy的五个组成部分nTrace, nWave, nSchema, nState, nCompare在FSDB和Knowledge Database (KDB)的支持下高度集成。

三、Debussy功能

Debussy直接编译Verilog/VHDL源代码,并且采用了预综合技术识别电路的单元,可以生成原理图。

在导入仿真结果后,可以用Active Annotation在源代码、原理图、状态图上动态显示变量的仿真值。

Debussy的输入为:Verilog/VHDL或混合语言源代码,仿真波形文件,SDF

支持的波形格式:vcd,fsdb,模拟波形文件(PowerMill,TimeMill,Avant! Star-Sim,SmartSpice)

支持的仿真器:VCS,Verilog-XL,NC-verilog,NC-VHDL,Modelsim,Leapfrog,Ploaris。

操作

一、启动

1. 启动

%debussy

启动debussy时,弹出一个nTrace窗口,包含三个子窗口:

a、左边是Hierarchical Browser窗口,用来显示设计的层次(design hierachy)。

b、右边是Source Code window,显示源代码。

跟踪信号的驱动、负载。

c、底下是Message window(消息窗口),用来报告操作的结果。

2.导入设计

File->Import Design

Debussy提供了两种导入设计的方法:

A、从设计源文件直接导入

B、从库导入(先将源文件编译成库)

Note: 可以用命令的方式直接启动debussy并导入设计文件,即在命令行上列出所有的选项和源文件,或者把这些选项和源文件写到一个文件中,用-f选项指定这个文件。

例如:

%debussy design.v -v lib.v

%debussy -f run.f

Note: 启动debussy后,会自动建立一个日志目录DebussyLog,在这个目录下,有一个日志文件:,记录了Debussy的编译信息。

3.查看编译信息:

File->View Import Log

二、根据仿真结果进行调试

1. 生成仿真的波形文件

Debussy提供的新的波形文件格式FSDB(Fast Signal DataBase),相比于VCD格式,压缩量大,比vcd文件小5-50倍,加载速度快。

Debussy提供了PLI(for Verilog)和FLI(for VHDL)接口,我们可以在仿真时直接导出FSDB文件。

例如,在Verilog的测试模块中加入如下语句:

initial

begin

$dumpfile("");

$dumpvars;

end

initial

begin

$fsdbDumpfile("");

$fsdbDumpvars;

$fsdbDumpflush; // 仿真过程中同时可以把信号的值dump成FSDB文件。

end

vcs -P <DEBUSSY_INSTALL_DIR>/share/PLI/vcs/SOLARIS2/ \

<DEBUSSY_INSTALL_DIR>/share/PLI/vcs/SOLARIS2/pli.a \

-PP -Mupdate +neg_tchk +define+FSDB stim_st_vd.v zx2716_top.v lib.v | tee

Debussy也提供了用于转换VCD文件为FSDB文件的程序(vfast)。

当用nWave导入VCD文件时,自动调用vfast转换成FSDB文件。

VCD:50min 2.1G

VPD:25min 40M

FSDB:40min 57M

nWave可以单独启动用来查看波形。

作为一个波形查看工具,nWave相当不错。

2. 假设在某时间步处,某信号的改变是错误的,要找出错误的原因

(1)在nTrace窗口中调试

STEP 1:把仿真结果标注到nTrace的源代码窗口中

从nTrace窗口中选择菜单Source->Active Annotation

STEP 2:找出转换发生的来源

在nWave窗口上,双击该信号在时间步的转换处。

Note: 在nTrace的源代码窗口中将显示信号转换时的驱动,光标定位在信号“out”上(out 只是一个假设的信号)。

STEP 3:找出“out”的所有驱动

在nTrace的源代码窗口中双击“out”。

Note:在Message window中显示有多个个驱动。

如果逐个跟踪,耗时长。

为了提高效率,我们要找到真正起作用的那个驱动(real active drivers)。

STEP 4:找出“out”的实际驱动。

在nTrace的工具栏上点击Backward History图标,返回STEP 3。

在“out”上单击鼠标右键,在弹出菜单中选择Active Trace。

可以一直用Active Trace跟踪下去,

(2)用nSchema窗口进行调试

STEP 1:生成“out”信号的Fan-In Cone逻辑

选择菜单Tools -> New Schematic -> Fan-In Cone

STEP 2:把仿真结果标注到Fan-In Cone窗口中

选择菜单Schematic->Active Annotation

STEP 3:

分析Fan-In Cone,追溯问题根源。

Note: Fan-In Cone will stop at storage elements,functional blocks,FSMs and primary IOs. 3.比较仿真结果

STEP 1: 平铺和同步两个nWave窗口

在nWave窗口上选择菜单Window->Sync Waveform View

STEP 2: 比较信号

在nWave窗口上选择菜单Tools->Waveform Compare->Compare Selected Signal 4.查看cell延时

STEP1: Load SDF File

去掉激励文件,nTrace窗口:File -> Load SDF Files

STEP2: SDF标注

nSchema窗口:Schematic -> SDF Annotation

STEP3: 查看Cell Delay

nSchema窗口:Schematic菜单,设置Delay Scale, Delay Type, Delay Precision

Schematic -> Cell Delay

5.Interactive Mode

快捷键

L:Reload Design

Ctrl+t:Active Trace

Ctrl+w:Add Signal(s) to Wave h:Hierarchical Name

Z:Zoom In

z:Zoom Out

f:Zoom All

l:Last View。