毕业论文之32位高速计数器的设计

高速32位浮点乘法器设计的开题报告

高速32位浮点乘法器设计的开题报告一、选题依据随着科技的快速发展,计算机在越来越多的领域中发挥着关键作用。

而在计算机的运算过程中,浮点运算是非常重要的一环。

为了能够完成更加复杂的计算任务,需要设计高精度、高效率的浮点运算器。

而高速32位浮点乘法器就是其中非常重要的一种。

因此,本课题选择研究高速32位浮点乘法器的设计。

二、研究的内容本课题研究的内容包括:1. 高速32位浮点乘法器的基本功能2. 高速32位浮点乘法器的设计原理3. 高速32位浮点乘法器的关键技术和算法4. 高速32位浮点乘法器的实现方式5. 高速32位浮点乘法器的性能评估与测试三、研究的意义高速32位浮点乘法器作为现代计算机系统的重要组成部分,其性能的高低直接影响到计算机的整体性能。

因此,研究高速32位浮点乘法器的设计,对于提升计算机的性能具有重要的意义和价值。

同时,在本课题的研究过程中,还可以深入了解现代计算机系统的内部原理和结构,具有很高的教育和研究价值。

四、研究的难点和解决方案在研究高速32位浮点乘法器的过程中,可能会面临以下难点:1. 设计原理的复杂性。

高速32位浮点乘法器的设计原理比较复杂,需要涉及到大量的数学知识。

为了解决这个问题,可以深入学习数学知识,并利用各种工具辅助分析设计。

2. 算法的高效性。

在设计高速32位浮点乘法器时,需要考虑到算法的高效性。

因此,研究合适的算法是非常重要的。

对于算法的研究,可以参考各种文献和优秀的实践经验。

3. 实现方式的可靠性。

在实现高速32位浮点乘法器时,需要考虑到实现方式的可靠性和稳定性。

为了解决这个问题,可以采用多种方案进行比较和测试,确保实现方式的可靠性。

五、预期成果本课题的预期成果包括:1. 高速32位浮点乘法器设计的详细说明和实现方式。

2. 高速32位浮点乘法器的性能评估和测试结果。

3. 研究过程中遇到的问题和解决方案的总结。

六、研究方法本课题的研究方法主要包括:1. 文献调研。

等精度数字频率计的设计设计说明

等精度数字频率计的设计设计说明内蒙古科技大学本科生毕业设计说明书(毕业论文)题目:等精度数字频率计的设计毕业设计(论文)原创性声明和使用授权说明原创性声明本人郑重承诺:所呈交的毕业设计(论文),是我个人在指导教师的指导下进行的研究工作及取得的成果。

尽我所知,除文中特别加以标注和致谢的地方外,不包含其他人或组织已经发表或公布过的研究成果,也不包含我为获得及其它教育机构的学位或学历而使用过的材料。

对本研究提供过帮助和做出过贡献的个人或集体,均已在文中作了明确的说明并表示了谢意。

作者签名:日期:指导教师签名:日期:使用授权说明本人完全了解大学关于收集、保存、使用毕业设计(论文)的规定,即:按照学校要求提交毕业设计(论文)的印刷本和电子版本;学校有权保存毕业设计(论文)的印刷本和电子版,并提供目录检索与阅览服务;学校可以采用影印、缩印、数字化或其它复制手段保存论文;在不以赢利为目的前提下,学校可以公布论文的部分或全部内容。

作者签名:日期:学位论文原创性声明本人郑重声明:所呈交的论文是本人在导师的指导下独立进行研究所取得的研究成果。

除了文中特别加以标注引用的内容外,本论文不包含任何其他个人或集体已经发表或撰写的成果作品。

对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式标明。

本人完全意识到本声明的法律后果由本人承担。

作者签名:日期:年月日学位论文版权使用授权书本学位论文作者完全了解学校有关保留、使用学位论文的规定,同意学校保留并向国家有关部门或机构送交论文的复印件和电子版,允许论文被查阅和借阅。

本人授权大学可以将本学位论文的全部或部分内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存和汇编本学位论文。

涉密论文按学校规定处理。

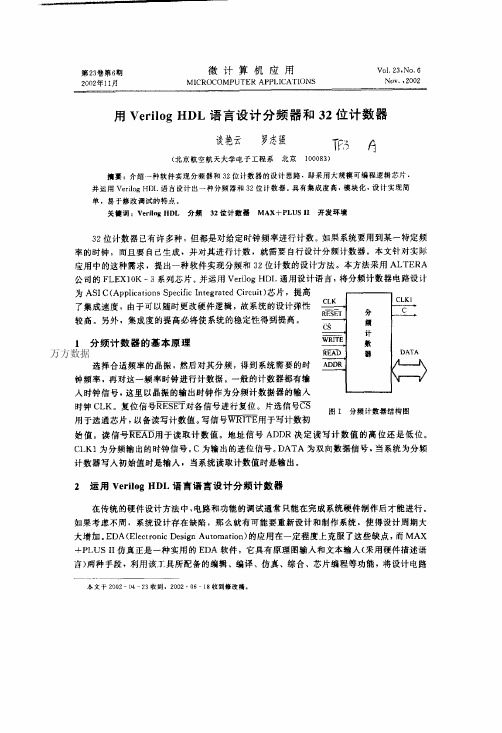

作者签名:日期:年月日导师签名:日期:年月日等精度数字频率计的设计摘要本设计课题为基于FPGA和单片机的等精度数字频率计的设计。

在本设计中,采用先进的自上而下的设计方法,以AT89C52单片机作为系统的主控部件,实现整个电路的信号控制、数据运算处理等功能;一片现场可编程逻辑器件FPGA(Filed Programmable Gate Array)芯片FLEX EPF10K20RC208-4完成各种时序逻辑控制、计数功能。

用Verilog+HDL语言设计分频器和32位计数器

i<i+1l

end

cs)∥有片选信号

end endrnodule

begin if(addr)

aceuh<2data}

该模块已通过软件仿真,符合设计要求。并已将程序下载到FPGA芯片,在电路板上与 系统进行联调,已证明设计达到预期功能,正式投入使用。

参 考 文 献

1夏宇闻.复杂数字电路与系统的VerilogHDL设计技术.北京t北京航空航天大学出版杜,1999.1—86 2阎石鼓字电子技术基础.北京:高等教育出版社.1 997.224--295 3束万焘·罗 车,吴顺军.CPI,D技术及其盥用西安:西安电子科技大学出版社,1999.30】oo

end end

output

elkl.c}//输出时钟和计数进位信号

j

wirte[15

reg

பைடு நூலகம்

O]data—reg·dataI

c,clkl{

if(i>=119) 计数值的高16位数和低

begin

∥对输人时钟进行J20分频

reg[1 5:O]aceub.aecul;

1

6位数

j<=0; clkl<=~clkl;

第23卷第6期 2002年1 1月

微计算机应用

MICROCOMPUTER APPLICATIONS

Vol

23.N。.6

Nov-,2002

用Ver|log

HDL语言设计分频器和32位计数器

谈艳云 罗志强

100083)

仍局

(北京航空航天大学电子工程东北京

擅要t介绍一种软件实现分频器和32位计数器的设计思路.即采用大规模可编程逻辑芯片.

+PLUS

II仿真正是一种实用的EDA软件,它具有原理图输入和文本输入(采用硬件描述语

32位微型计算机原理与接口技术实验指导

32位微型计算机原理与接口技术实验指导下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!32位微型计算机原理与接口技术实验指导引言在现代计算机科学领域中,微型计算机的原理和接口技术至关重要。

毕业设计--32位不恢复替代算法除法器设计[管理资料]

![毕业设计--32位不恢复替代算法除法器设计[管理资料]](https://img.taocdn.com/s3/m/48439dd3482fb4daa48d4b0c.png)

32位不恢复替代算法除法器设计摘要CPU的核心功能之一是实现基本算术运算。

在四则基本运算中,除法在技术实现上具有较高的复杂性,所以硬件除法器的设计一般会成为CPU设计中的重点与难点。

对于嵌入式CPU来说,其设计目标更加关心成本的降低,使得其算术运算单元在性能设计指标上需要有较大的灵活性,从而使硬件占用较小的面积。

本文根据不恢复替代算法,实现了32位不恢复替代算法除法器。

本文首先介绍了除法器在CPU设计中的地位、设计所面临的挑战。

然后简单说明了Digit Recurrence算法基本理论和除法器的基本算法,即:恢复迭代算法及其电路、不恢复迭代算法及其电路、基数-4SRT算法、Newton-Raphson除法算法。

然后用半定制方法对32不恢复替代算法除法器器进行了设计和分析。

最后进行了硬件电路的综合。

综合结果表明,无论从资源占用方面还是从最高工作频率方面。

基于ALTERA Stratix II 的综合结果显示,基于掩码的数据反转的桶形移位器的最高工作频率可以达到30MHz。

关键词:除法器;不恢复替代算法;半定制设计;Verilog HDLDesign of 32-bits Not Resume AlternativeAlgorithm DividerAbstractArithmetic computation is a key function of Central Processor Unit (CPU).Among basic arithmetic operation, division is the most difficult one to implement. Therefore the design of dedicate hardware divider is usually the vital part in CPU development. Since the design of an embedded CPU is more concerned about cost reduction, its ALU design usually emphasizes on flexibility rather than performance. This orientation demands solutions that consume minimum die area.This article does not resume under an alternative method to achieve a 32-bit replacement algorithm does not restore divider. This paper introduces the divider position in the CPU design, design challenges and research significance.Then a brief description of the basic theory and algorithm Digit Recurrence divider the basic algorithm, that is: restore iterative algorithm and its circuit, not to resume iterative algorithm and its circuit, the base -4 SRT algorithm, Newton-Raphson division algorithm. Then the paper designs and analyses The Divider in the semi- custom approach.Finally, I completed to integrate the circuit hardware .The result of systhesis based on the ALTERA Stratix II indicates that the mask-based data- reversal barrel shifter can work in the 30MHz.Keywords: Divider;Not Resume Alternative Algorithm;Semi-custom Approach;Verilog HDL目录 (1) (1) (3) (6) (7) (8)2. 除法器的基本算法 (9)Recurrence算法基本理论 (9) (9)数学表述 (11)基数 (13) (13) (14) (16)SRT算法 (19)Newton-Raphson 除法算法 (23) (24) (24)硬件时序结构的优化方法 (26) (29)3. 32位不恢复替代算法除法器设计 (33)Verilog HDL (33) (34) (38)HDL的设计与验让流程 (38)综合仿真图形 (41) (43) (44) (44)致谢 (45)参考文献 (46)附录 (48)外文资料翻译及原文 (54)微电子技术是随着集成电路,尤其是超大规模集成电路而发展起来的一门新的技术。

基于32位adc的高精度数据采集系统设计

摘要高精度数据采集技术在工厂自动化,石油勘探和航空航天等领域发挥着巨大的作用。

与国外相比,我国数据采集技术还不够成熟,数据采集产品还处于落后地位,自主研究高精度数据采集系统对于我国该领域的发展具有重要意义。

目前市场上有种类繁多的数据采集产品,这些产品的ADC位数在8位到24位之间,采样率在几赫兹到上百兆赫兹之间。

在这些产品中,高速采集系统ADC 的位数往往达不到24位,高于24位的数据采集系统还没有成熟的产品。

本文依托实验室科研项目的需求,针对采样率在几百千赫兹,同时要求高采样精度这一细分领域,设计了一款基于32位ADC的数据采集系统。

本文主要工作如下:1、设计低噪声模拟调理电路。

采用高性能的运放芯片设计模拟电路,并尽量减少器件数量以降低噪声。

采用32位Δ-Σ型AD芯片设计了AD转换电路。

使用DC-DC隔离电源和磁耦隔离芯片,将采集板卡前端模拟地和后端数字地完全分开,降低两个地相互之间的串扰。

为了提高采集系统的同步性能,使用FPGA 设计控制电路。

2、设计基于USB协议的数据传输电路。

为了满足数据传输速率的需求,同时考虑到系统的实用性,设计基于USB 2.0总线协议的数据传输控制电路。

控制电路基于EZ-USB FX2芯片进行设计,数据传输模式选择异步Slave FIFO模式。

3、编写基于虚拟仪器开发环境LabVIEW的上位机软件。

上位机程序采用缓冲设计,解决数据产生和数据消费部分速率不对等的问题,方便程序的维护和升级。

上位机具有设置采集模式,设置采集参数,通道校准,采集数据显示和存储的功能。

4、在实验室环境下对系统进行测试。

系统测试内容包括:短路噪声测试,典型信号测试和系统通道一致性测试。

测试结果表明,系统实测指标满足设计要求,能够应用于高速高精度数据采集。

关键词:32位ADC,高精度数据采集,USB2.0,LabVIEWABSTRACTDesign of High-precision Data Acquisition System Based on 32-bit ADCHigh-precision data acquisition technology played a huge role in the fields of factory automation, oil exploration and aerospace. Compared with foreign countries, the data acquisition technology in our country is not mature enough, and the data acquisition products are still in a backward position. It is of great significance to research the high-precision data acquisition system independently for the development of this field in our country.There are many kinds of data acquisition products on the market at present, the bits of the ADC of these products are between 8 bits and 24 bits, the sampling rates are between several hertz and up to one hundred megahertz. In these products, the bits of the ADC of high speed acquisition system are usually less than 24 bits. There is no mature product in the data acquisition system which is higher than 24 bits. Based on the needs of the laboratory research project, this paper designed a kind of data acquisition system based on 32-bit ADC, and this system is aimed at the segment field which has a sampling rate of several hundreds kilohertz and requires high sampling accuracy. The main work of this paper is as follows:1. A low noise simulation circuit was designed. The analog circuit is designed by the high performance amplifier and the number of the devices is minimized to reduce the noise. The AD converter circuit is designed by the 32-bit AD chip of Δ-Σ t ype. The DC-DC isolated power supply and the digital isolators are used to separate the front analog ground and the back-end digital ground to reduce the crosstalk between the two grounds. In order to improve the synchronization performance of the acquisition board, a FPGA control circuit is designed.2. The data transmission circuit based on USB protocol is designed. In order to meet the requirement of data transmission rate and in consideration of the practicability of the system, a data transmission control circuit based on USB 2.0 bus protocol was designed. The control circuit was designed based on the EZ-USB FX2 chip, and the data transmission mode was the asynchronous Slave FIFO mode.3. Write the PC software based on the virtual instrument development environment labVIEW. The program of the PC software adopted the buffer design, which solves the unequal rate problem of data generation and data consumption, it is also convenient for the maintenance and upgrade of the program. The PC software has the function of setting acquisition mode, setting acquisition parameters, channel calibration, data display and data storage.4. The system test was carried out in the laboratory environment. The system tests include: short circuit noise test, typical signal test and system channel consistency test. The test results showed that the system meets the design requirements, and it can be applied to high-speed and high-precision data acquisition.Key words:32-bit ADC, high-precision data acquisition, USB2.0, LabVIEW目录第1章绪论 (1)1.1 研究背景及意义 (1)1.2 国内外研究现状 (2)1.2.1 国外研究现状 (2)1.2.2 国内研究现状 (3)1.3 本文主要研究内容 (3)第2章系统整体方案设计 (5)2.1 系统性能指标 (5)2.2 系统整体框架设计 (5)2.3 系统硬件设计 (6)2.4 系统数据传输方案设计 (7)2.5 系统上位机软件设计 (7)第3章系统硬件关键技术 (9)3.1 系统硬件总体设计 (9)3.2 低噪声模拟调理电路设计 (9)3.2.1 输入保护电路 (10)3.2.2 低噪声运放芯片选型 (11)3.2.3 输入跟随电路 (12)3.2.4 单端转差分电路 (13)3.2.5 基于抗混叠滤波器的AD驱动电路设计 (13)3.2.6 模拟电路噪声分析 (17)3.3 基于32位ADC的AD转换电路设计 (19)3.4 FPGA控制电路 (22)3.4.1 基于自顶向下理念的FPGA控制电路设计 (23)3.4.2 基于有源晶振的时钟电路设计 (23)3.4.3 基于VHDL语言的模块设计 (24)3.5 基于独立供电结构的低噪声电源设计 (31)3.6 本章小结 (33)第4章系统USB接口设计 (34)4.1 USB通信协议 (34)4.2 EZ-USB FX2单片机 (35)4.3 EZ-USB控制电路设计 (36)4.4 USB固件程序设计 (37)4.4.1 固件程序框架 (38)4.4.2 USB设备配置描述符 (40)4.4.3 USB设备请求 (41)4.4.4 USB设备重列举 (43)4.4.5 Slave FIFO固件设计 (43)4.5 基于动态链接库的USB驱动程序设计 (44)4.5.1 通用USB驱动 (44)4.5.2 LabVIEW下的USB驱动 (44)4.6 本章小结 (45)第5章系统上位机软件设计 (46)5.1 系统上位机软件结构设计 (46)5.2 系统上位机软件程序设计 (47)5.2.1 基于生产消费模式的数据缓存设计 (48)5.2.2 数据预处理 (49)5.2.3 数据的显示与存储 (49)5.3 系统上位机软件界面设计 (50)5.4 本章小结 (51)第6章系统测试 (52)6.1 系统噪声测试 (52)6.2 典型信号测试 (53)6.2.1 正弦波信号测试 (53)6.2.2 三角波信号测试 (54)6.2.3 方波信号测试 (55)6.2.4 测试结果误差分析 (56)6.3 通道一致性测试 (57)6.4 系统性能指标 (59)6.5 本章小结 (60)第7章全文总结 (61)7.1 主要研究工作 (61)7.2 进一步研究建议 (62)参考文献 (63)作者简介及科研成果 (66)致谢 (67)第1章绪论1.1 研究背景及意义数据采集技术在信息采集、自动控制等领域有着广泛的应用。

32位微型计算机接口技术及应用课程设计

32位微型计算机接口技术及应用课程设计课程设计目的本课程设计旨在让学生了解32位微型计算机的接口技术以及应用,并通过实践操作掌握相关技能。

学生将运用所学知识,设计并实现一个基于32位微型计算机的应用程序。

课程设计内容1.基础知识概述–32位微型计算机介绍–接口技术原理–硬件配置和准备工作2.接口技术实践–GPIO口输入输出实现–串口通信数据传输实现–中断响应和处理实现3.应用程序实现–设计一个基于32位微型计算机的应用程序–程序代码编写–功能测试和调试设计要求1.学生应大致了解32位微型计算机的基本知识。

2.学生应理解接口技术的基本原理及应用。

3.学生应能熟练操作32位微型计算机的GPIO口和串口。

4.学生应学会中断响应和处理的实现。

5.学生应通过实践编写并测试一个完整的应用程序。

课程设计流程第一阶段:基础知识概述第一阶段主要讲解下列内容:1.32位微型计算机介绍;2.接口技术原理;3.硬件配置和准备工作。

理论上,在了解完这些知识之后,学生应能搭建32位微型计算机的开发环境。

第二阶段:接口技术实践第二阶段主要讲解下列内容:1.GPIO口输入输出实现;2.串口通信数据传输实现;3.中断响应和处理实现。

学生将使用学到的知识,设计并实现一个基于32位微型计算机的应用程序,从而深入理解接口技术的实际应用。

第三阶段:应用程序实现第三阶段是课程设计的高潮,要求学生提交一个完整的应用程序。

1.设计一个基于32位微型计算机的应用程序;2.编写程序代码;3.功能测试和调试。

学生可以自由发挥,并选择自己感兴趣的应用并进行实现。

课程设计实验环境1.开发板:32位微型计算机;2.软件开发环境:Keil MDK;3.硬件设备:LED灯、按键、电位器等。

课程设计评估1.端口技术原理课堂练习:20%;2.实践操作测试:40%;3.个人应用程序演示:40%。

总结该课程设计旨在让学生从理论和实践两个角度了解32位微型计算机的接口技术和应用,并将其融合到实际应用程序中。

32_32高速乘法器的设计与实现

对传统的基于全加器组成的压缩单元进行分

析 ,得出其布尔表达式如下 :

S = a1 a2 a3 a4 cin

(3)

Carry = ( a1 a2 a3) ·a4 + ( a1 a2 a3) ·

cin + a4 ·cin

(4)

Cout = a1 ·a2 + a1 ·a3 + a2 ·a3

(5)

对式 (4) 、式 (5) 两个表达式进行等价的逻辑转

首先设 A 为被乘数 , B 为乘数 ,且均为 32 位无 符号数 , P 表示乘积. 则有 A ×B 为

31

16

∑ ∑ P = A ×( bi2 i) = A ×[ ( b2 n - 1 + b2 n -

i =0

n =0

16

∑ 2 b2 n +1) 4 n ] =

A ( b2 n - 1 + b2 n - 2 b2 n +1) 22 n (1)

32 ×32 High2speed Multiplier Design and Implementation

L I J un2qiang1 , L I Dong2sheng1 ,2 , L I Yi2lei1 , ZHOU Zhi2zeng3

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

毕业设计报告(论文)报告(论文)题目:32位高速计数器的设计作者所在系部:电子工程系作者所在专业:电子工艺与管理作者所在班级: 08253作者姓名:高崇作者学号: 20083025309指导教师姓名:王晓完成时间: 2011年6月10日北华航天工业学院教务处制北华航天工业学院电子工程系毕业设计(论文)任务书姓名:高崇专业:电子工艺与管理班级: 253 学号:20083025309指导教师:王晓职称:副教授完成时间:2010年6月10日毕业设计(论文)题目:32位高速计数器的设计设计目标:了解一些计数器的应用及其性能特点;掌握32位高速计数器的芯片的设计过程技术要求:1.当一个脉冲到来时32位计数器显示1;相邻特性曲线的间隔相同。

2.脉冲不断地到来32位计数器不断地加13.当32位计数器加到F时,向高位进1;4. 32位计数器的范围为0—FFFFFFFF;所需仪器设备:计算机、MAXPLUS2软件、EDA实验开发系统成果验收形式:论文参考文献:《可编程器件EDA技术与实践》相关文献时间安排1 5周---6周立题论证 3 9周---13周仿真调试2 7周---8周方案设计 4 14周---16周成果验收指导教师:教研室主任:系主任:摘要论文的研究工作是以32位高速计数器程序设计为题展开的,通过熟练运用EDA技术设计32位高速计数器程序,并通过仿真检验程序的正确性。

而且详细介绍现阶段的一些技术器及其参数、性能特点,了解现阶段计数器的发展水平,通过这些计数器在现实生活的各个领域扮演的角色,体会计数器在生活中的重要性。

关键词计数器DEA 仿真检验目录第1章计数器简介 (1)1.1计数器 (1)第2章计数器的应用及其性能特点 (3)2.1零点袋装水泥计数器 (3)2.2ZG30菌落计数器 (3)2.3闪烁计数器 (4)2.4JSYF系列放电计数器 (4)2.5实时碳计数器 (5)2.6ZT-JS01A型智能产品计数器 (5)2.7零件计数器 (6)2.8颗粒计数器 (6)2.9频率计数器 (6)2.10红外人流计数器 (7)2.11盖革计数器 (7)2.12Γ免疫计数器 (7)2.13显示条形码计数器 (8)2.14尘埃计数器 (8)2.15细胞计数器 (8)2.16智能计数器 (9)2.17空气离子浓度计算器 (9)2.18L OAD R UNNER监视的性能计数器 (9)2.19小结 (12)第3章 32位高速计数器 (13)3.132位计数器程序 (13)3.1.1 顶层文件设计 (13)3.1.2 cnt_ffffffff(32位计数器) (14)3.1.3 sel(选择器) (15)3.1.4 deled(译码器) (16)3.2仿真图 (18)3.2.1 顶层仿真图 (18)3.2.2 32位计数器(cnt_ffffffff)仿真图 (19)3.2.3 sel(选择器)仿真图 (21)3.2.4 译码器(deled)仿真图 (22)第4章结论 (23)致谢 (24)参考文献 (25)附录 (26)第1章计数器简介1.1计数器计数器是一种具有多种测量功能、多种用途的电子计数器。

它可以测量频率、周期、时间间隔、频率比、累加计数、计时等;配上相应的插件,还可以测量相位、电压等。

一般我们把凡具有测频和测周两种以上功能的计数器都归类为通用计数器。

计数器的主要性能:1.测试功能电子计数器所具备的测试功能一般包括测量频率、周期、频率比、时间间隔、累加计数和自校等。

2. 测量范围电子计数器的有效测量范围是相对于测量功能而言的,不同的测量功能其测量范围的含义也不同。

如测量频率时是指频率的上、下限;测量周期时是指周期时间单位)的最大、最小值。

3. 输入特性一般情况下,当仪器有2~3个输入通道时,需分别给出各个通道的特性,主要有:3.1输入灵敏度:指仪器正常工作所需输入的最小电压。

3.2 输入耦合方式:主要有AC交流)耦合和DC直流)耦合两种。

AC耦合时,被测信号经隔直电容输入;DC耦合时,被测信号直接输入,在低频及脉冲信号输入时宜采用这种耦合3.3 输入阻抗:包括输入电阻和输入电容,并有高阻抗例如1 MΩ//25 pF)和低阻抗例如50 Ω)之分。

前者多用于频率不太高的场合,以减小对信号源的负载影响;后者多用于频率较高的场合,以满足匹配要求。

3.4 最大输入电压:允许的最大输入电压。

超过最大输入电压后,仪器不能保证正常工作,甚至会被损坏。

4. 测量准确度测量准确度常用测量误差来表示,主要由时基误差和计数误差决定。

时基误差由晶体振荡器的稳定度确定,电子计数器通常给出晶体振荡器的标准频率及其频率稳定度;计数误差主要指量化误差。

5. 闸门时间和时标由仪器内部标准时间信号源提供的标准时间信号包括闸门时间信号和时标信号,可以有多种选择。

6. 输出7. 这里指的是仪器可输出的标准时间频率)信号的种类、输出数据的编码方式及输出电平的高低等。

计数器的构成:1. A、B输入通道输入通道的作用是将被测信号进行放大、整形,使其变换为标准脉冲。

输入通道部分包括A、B两个通道,它们均由衰减器、放大器和整形电路等组成。

凡是需要计数的外加信号(例如测频信号),均由A输入通道输入,经过A通道适当的衰减、放大整形之后,变成符合主门要求的脉冲信号。

而B输入通道的输出与一个门控双稳相连,如果需要测量周期,则被测信号就要经过B输入通道输入,作为门控双稳的触发信号。

门又称闸门,它是用于实现量化的比较电路,它可以控制计数脉冲信号能否进入计数器。

主门电路是一个双输入端逻辑与门。

它的一个输入端接受来自控制单元中门控双稳态触发器的门控信号,另一个输入端则接受计数(脉冲)信号。

在门控信号作用有效期间,允许计数(脉冲)通过主门进入计数器计数。

2. 计数、显示单元计数与显示电路是用于对来自主门的脉冲信号进行计数,并将计数的结果以数字的形式显示出来。

为了便于读数,计数器通常采用十进制计数电路。

带有微处理器的仪器也可用二进制计数器计数,然后转换成十进制并译码后再进入显示器。

3. 时基单元时基电路主要由晶体振荡器、分频及倍频器组成。

时基电路主要用于产生各种标准时间信号。

标准时间信号有两类,一类时间较长的称为闸门(时间)信号,通常根据分频级数的不同有多种选择;另一类时间较短的称为时标信号。

时标信号可以是单一的,也可以有多种选择。

4. 控制单元控制电路的作用是产生门控信号(Q)、寄存信号(M)和复零信号(R)三种控制信号,使仪器的各部分电路按照准备→测量→显示的流程有条不紊地自动进行测量工作。

控制单元中包括前述的门控双稳态电路,它输出的门控信号用于控制主门的开闭,在触发脉冲作用下双稳态电路发生翻转。

通常以一个输入脉冲开启主门,另一路输入脉冲信号使门控双稳复原,关闭主门。

计数器的误差来源:1.量化误差;2. 触发误差;3. 准频率误差[1]。

第2章计数器的应用及其性能特点2.1 零点袋装水泥计数器零点袋装水泥计数器是根据水泥厂恶劣环境研发及生产袋装水泥计数器。

水泥包装车间是企业与客户对接的窗口,精确的发货数据有利于销售管理和企业品牌、形象的提升,传统的计数方式已经不再适合水泥高速生产的需求。

由于水泥在皮带传输过程中偶尔会出现连包,小叠包的现象,传统的计数器已无法满足水泥厂的需求,针对此问题,研制了零点袋装水泥计数器。

零点袋装水泥计数器性能:1.集中管理,易于使用、便于监控,更人性化2.水泥厂专用,计数精确、快速,经久耐用3.可单包计数、连包计数、批量计数4.采用“双通道带速补偿法”可智能分辨连包5.采用“不规则水泥连包补偿法”可智能分辨小叠包6.同装车机连锁,单车到包后,装车机/包装机自动停机7.光电信号隔离,抗干扰性强8.断电存储功能,防止数据丢失9.美观大方,可外接多个大屏幕显示屏10.单包计数:可自动吸收水泥袋上和皮带上的干扰脉冲达到准确计数。

11.连包计数:设定单包的正常参数,连包时可根据单包的正常参数智能识别出连包数。

12.批量计数:可设定并显示单包数(0-60000),达到设定值时,计数器输出闪烁报警信号“AL”并输出一组开关控制信号(5A)。

13.设定值到达时计数器自动清零或手动清零:可按需要输入密码设定。

14.批量设定值到达提前报警:提前包数可按需要输入密码设定。

15.总数累计:可查看计数总数(0-9999999)(输入密码可清零)。

16.故障报警:当计数器检测到感应头状态异常,或连包超过10包以上输出一组继电器开关信号报警(5A),该开关可接报警铃或停皮带。

17.自动控制:继电器开关信号可直接与包装线的二次线路实现自动控制。

(如:控制包装机停止,皮带停止,推包机开合,装车机停止,连接报警铃等)[2]。

2.2 ZG30菌落计数器ZG30菌落计数器使用方便,对用户来说最大的好处就是:再也不会认为计算微生物的数目是一件非常费力,危险的工作。

原因在于:该计数器用来放置培养皿的表面是个压敏元件,当用特制的笔在表面作标记时将自动启动计数功能,用户可调节表面对压力的灵敏度以满足不同用户的操作要求。

智能计数技术BZG30具有回声检测信号,可以自动补偿不同培养皿重量的影响,压力传感器遍布整个表面,且每点的灵敏度保持一致;仪器另有零点电位保护功能,可防止交流电短路的影响。

2.3 闪烁计数器利用射线引起闪烁体的发光而进行记录的辐射探测器。

1947年由J.W.科尔特曼和H.P.卡尔曼所发明。

它由闪烁体、光电倍增管(见光电管)和电子仪器等单元组成。

射线同闪烁体相互作用,使其中的原子、分子电离或激发,被激发的原子、分子退激时发出微弱荧光(见固体发光),荧光被收集到光电倍增管,倍增的电子流形成电压脉冲,由电子仪器放大分析和记录。

可用的闪烁体种类很多,用得较多的有NaI(加微量Tl)、CI(加微S量Tl)、ZnS(加微量Ag)等无机盐晶体和蒽、茋、对联三苯等有机晶体,也有用液体、塑料或气体的闪烁体。

闪烁计数器的优点是效率高,有很好的时间分辨率和空间分辨率,时间分辨率达10-9秒,空间分辨率达毫米量级。

它不仅能探测各种带电粒子,还能探测各种不带电的核辐射;不仅能探测核辐射是否存在,还能鉴别它们的性质和种类;不但能计数,还能根据脉冲幅度确定辐射粒子的能量。

在核物理和粒子物理实验中应用十分广泛。

2.4 JSYF系列放电计数器1. 用途、特点放电计数器是串联工作在避雷器下面用来记录避雷器动作次数的一种装置。

JSYF9系列氧化锌放电计数器适用于220KV及以下电压等级的各型氧化锌避雷器配套,使用的环境条件与相连接的避雷器相同。

氧化锌放电计数器具有以下特点和用途:1. JSYF9型、JSYF9-S型放电计数器系按氧化锌避雷器的动作特性设计生产的,采用大直径氧化锌阀片,具有通流容量大、残压低、适应电压等级范围宽、动作计数准确可靠,下限动作电流灵敏度高。