数字逻辑期中试卷答案

《数字逻辑》期中试卷

《数字逻辑》期中试卷姓名_______ 学号__________ 成绩_______一、是非题(下列各题你认为正确的,请在题干的括号内打“√”,错的打“×”。

每题2分)1、直接对模拟量进行处理的电子线路称为数字电路。

()2、进位计数制中允许使用的基本数字符号的个数为它的基数。

()3、正数的原码就等于真值。

()4、定点机能完成浮点运算。

()5、所谓多项式替代法,是将R进制数按多项式表示法展开,然后按十进制的运算规则求和,即得到与R进制数等值的十进制数。

()6、不因条件变化,表示事物状态的逻辑状态变化的“0”和“l”称为逻辑变量。

( )7、设A=1,B=1,则AB=0。

( )8、实现一个确定逻辑功能的逻辑电路是唯一的。

()9、最简与或式的标准是:或项的数目最少;每个或项的变量数量最少。

( )10、若函数的一个蕴涵项不是该函数中其它蕴涵项的子集,则此蕴涵项称为质蕴涵项(Prime Implicant),简称为质项。

()11、逻辑代数中,若x十y=x十z且x·y=x·z,则y=z。

()12、对一个给定的逻辑函数来说,无关最小项是否出现在函数表达式中,并不影响该函数原来的逻辑功能。

()13、由门电路组成的电路就是组合电路。

()14、寻找最大等效类的关键是要找出原始状态表中所有等效状态对。

()15、用逻辑门构成的各种触发器均属于电平异步时序逻辑电路。

()二、选择题:(每题2分)1、( )是数字系统功能实现的物质基础。

A、模拟集成电路B、数字集成电路C、连续信号D、离散信号2、在数字电路中要采用( )A、十进制B、八进制C、二进制D、十六进制3、5位二进制数的最大值对应的十进制数是( )A、32B、64C、31D、164、下列四个不同进制的数中,其值最小的是()A. 十六进制数 CAB. 八进制数 310C. 十进制数 201D. 二进制数 110010115、(27.25)10转换成十六进制数为()A.(B1.4)16 B.(1B.19)16 C. (1B.4)16 D.(33.4)166、定点8位字长的字,采用2的补码形式表示时,一个字所能表示的整数范围()A -128 ~ +127B -127 ~ +127C -129 ~ +128D -128 ~ +1287、浮点表示范围由浮点数的()部分决定。

数字逻辑复习题有答案

数字逻辑复习题有答案1. 什么是数字逻辑中的“与”操作?答案:在数字逻辑中,“与”操作是一种基本的逻辑运算,它只有当所有输入信号都为高电平(1)时,输出信号才为高电平(1)。

如果任何一个输入信号为低电平(0),则输出信号为低电平(0)。

2. 描述数字逻辑中的“或”操作。

答案:在数字逻辑中,“或”操作是另一种基本的逻辑运算,它只要至少有一个输入信号为高电平(1),输出信号就为高电平(1)。

只有当所有输入信号都为低电平(0)时,输出信号才为低电平(0)。

3. 如何理解数字逻辑中的“非”操作?答案:“非”操作是数字逻辑中最基本的逻辑运算之一,它将输入信号的电平状态取反。

如果输入信号为高电平(1),输出信号则为低电平(0);反之,如果输入信号为低电平(0),输出信号则为高电平(1)。

4. 解释数字逻辑中的“异或”操作。

答案:数字逻辑中的“异或”操作是一种逻辑运算,它只有在输入信号中有一个为高电平(1)而另一个为低电平(0)时,输出信号才为高电平(1)。

如果输入信号相同,即都是高电平或都是低电平,输出信号则为低电平(0)。

5. 什么是数字逻辑中的“同或”操作?答案:“同或”操作是数字逻辑中的一种逻辑运算,它只有在输入信号都为高电平(1)或都为低电平(0)时,输出信号才为高电平(1)。

如果输入信号不同,即一个为高电平一个为低电平,输出信号则为低电平(0)。

6. 什么是触发器,它在数字逻辑中的作用是什么?答案:触发器是一种具有记忆功能的数字逻辑电路,它可以存储一位二进制信息。

在数字逻辑中,触发器用于存储数据、实现计数、寄存器和移位寄存器等功能。

7. 简述D触发器的工作原理。

答案:D触发器是一种常见的触发器类型,它的输出状态由输入端D的电平决定。

当触发器的时钟信号上升沿到来时,D触发器会将输入端D的电平状态锁存到输出端Q,从而实现数据的存储和传递。

8. 什么是二进制计数器,它的功能是什么?答案:二进制计数器是一种数字逻辑电路,它能够按照二进制数的顺序进行计数。

数字逻辑考题及答案

资料范本本资料为word版本,可以直接编辑和打印,感谢您的下载数字逻辑考题及答案地点:__________________时间:__________________说明:本资料适用于约定双方经过谈判,协商而共同承认,共同遵守的责任与义务,仅供参考,文档可直接下载或修改,不需要的部分可直接删除,使用时请详细阅读内容数字逻辑试题1答案一、填空:(每空1分,共20分)1、(20.57)8 =( 10.BC )162、(63.25) 10= ( 111111.01 )23、(FF)16= ( 255 )104、[X]原=1.1101,真值X= -0.1101,[X]补 = 1.0011。

5、[X]反=0.1111,[X]补= 0.1111。

6、-9/16的补码为1.0111,反码为1.0110 。

7、已知葛莱码1000,其二进制码为1111,已知十进制数为92,余三码为1100 01018、时序逻辑电路的输出不仅取决于当时的输入,还取决于电路的状态。

9、逻辑代数的基本运算有三种,它们是_与_ 、_或__、_非_ 。

10、,其最小项之和形式为_ 。

11、RS触发器的状态方程为__,约束条件为。

12、已知、,则两式之间的逻辑关系相等。

13、将触发器的CP时钟端不连接在一起的时序逻辑电路称之为_异_步时序逻辑电路。

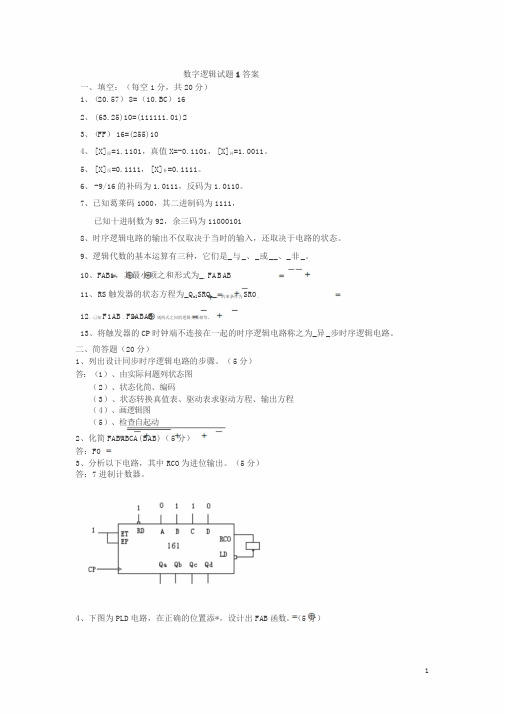

二、简答题(20分)1、列出设计同步时序逻辑电路的步骤。

(5分)答:(1)、由实际问题列状态图(2)、状态化简、编码(3)、状态转换真值表、驱动表求驱动方程、输出方程(4)、画逻辑图(5)、检查自起动2、化简(5分)答:3、分析以下电路,其中RCO为进位输出。

(5分)答:7进制计数器。

4、下图为PLD电路,在正确的位置添 * ,设计出函数。

(5分)5分注:答案之一。

三、分析题(30分)1、分析以下电路,说明电路功能。

(10分)解: 2分该组合逻辑电路是全加器。

以上8分2、分析以下电路,其中X为控制端,说明电路功能。

数字逻辑考题及答案

数字逻辑试题1答案一、填空:(每空1分,共20分)1、(20.57)8=(10.BC)162、(63.25)10=(111111.01)23、(FF)16=(255)104、[X]原=1.1101,真值X=-0.1101,[X]补=1.0011。

5、[X]反=0.1111,[X]补=0.1111。

6、-9/16的补码为1.0111,反码为1.0110。

7、已知葛莱码1000,其二进制码为1111,已知十进制数为92,余三码为110001018、时序逻辑电路的输出不仅取决于当时的输入,还取决于电路的状态。

9、逻辑代数的基本运算有三种,它们是_与_、_或__、_非_。

10、FAB1,其最小项之和形式为_。

FA B AB11、RS触发器的状态方程为_Q n1SRQ n_,约束条件为SR0。

12、已知F1AB、F2ABAB,则两式之间的逻辑关系相等。

13、将触发器的CP时钟端不连接在一起的时序逻辑电路称之为_异_步时序逻辑电路。

二、简答题(20分)1、列出设计同步时序逻辑电路的步骤。

(5分)答:(1)、由实际问题列状态图(2)、状态化简、编码(3)、状态转换真值表、驱动表求驱动方程、输出方程(4)、画逻辑图(5)、检查自起动2、化简FABABCA(BAB)(5分)答:F03、分析以下电路,其中RCO为进位输出。

(5分)答:7进制计数器。

4、下图为PLD电路,在正确的位置添*,设计出FAB函数。

(5分)15分注:答案之一。

三、分析题(30分)1、分析以下电路,说明电路功能。

(10分)解:XY m(3,5,6,7)m(1,2,4,7)2分ABCiXY0000000101010010111010001101101101011111该组合逻辑电路是全加器。

以上8分2、分析以下电路,其中X为控制端,说明电路功能。

(10分)解:FXA B C XABCXABCXABCXABCXABC4分FX(ABC)X(A B C ABC)4分所以:X=0完成判奇功能。

电子线路数字逻辑与数字系统期终试题及参考答案

电子线路数字逻辑与数字系统期终试题姓名:_____________ 学号:______________ 成绩:_____________一、填充题(每空2分,共计22分)1.进行下列数制的转换:(325.39)]。

=( 以(4A.7)]6 =( )102.在使用一个六输入的与或非门时,如果其中有一个输入端是多余的,对其处理的方法有: ,是 __________________ ,二是______________________ O 3.一个数的原码为11011101(第一位为符号位),它的补码为_______________ ,它对应的十进制数是___________ o4.已知逻辑函数的最小项之和的表达式为:F(A, B, C, D) = ^m(l,2,3,5,8,l 2)则其对偶式的最小项之和为:尸£>) = »().5.由33个1和7个。

进行异或运算,其结果的值是_______ o6.时序逻辑电路在任一时刻的电路输出状态与 _________________________ 和_______________________________ 有关。

7.无须将其从系统的电路板上拔下而直接对它进行编程的是 _________ 器件。

二、选择题(每小题3分,共计21分)路的最简乘积项之和的表达式为:F(A,B ,C)= ______________________A. ABCB. A© CC. ~AB^ACD. AOC将肯定使F为D.异或2.________________________________________ 已知逻辑函数F = ABC + CD ,下面的_____________________________________A. A=0, BC=1B. BC=1,D=1C. B=1,C=1D. C=l,B=03.己知二变量输入逻辑门的输入A、B的波形和输出F的波形如右图所示,它是逻辑门。

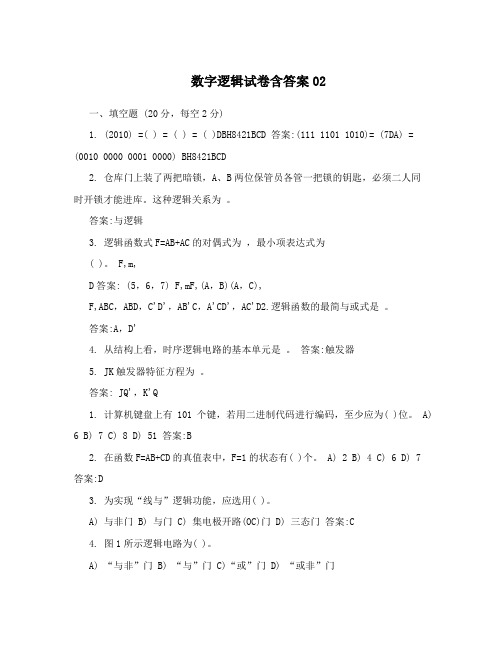

数字逻辑试卷含答案02

数字逻辑试卷含答案02一、填空题 (20分,每空2分)1. (2010) =( ) = ( ) = ( )DBH8421BCD 答案:(111 1101 1010)= (7DA) = (0010 0000 0001 0000) BH8421BCD2. 仓库门上装了两把暗锁,A、B两位保管员各管一把锁的钥匙,必须二人同时开锁才能进库。

这种逻辑关系为。

答案:与逻辑3. 逻辑函数式F=AB+AC的对偶式为,最小项表达式为( )。

F,m,D答案: (5,6,7) F,mF,(A,B)(A,C),F,ABC,ABD,C'D',AB'C,A'CD',AC'D2.逻辑函数的最简与或式是。

答案:A,D'4. 从结构上看,时序逻辑电路的基本单元是。

答案:触发器5. JK触发器特征方程为。

答案: JQ',K'Q1. 计算机键盘上有101个键,若用二进制代码进行编码,至少应为( )位。

A) 6 B) 7 C) 8 D) 51 答案:B2. 在函数F=AB+CD的真值表中,F=1的状态有( )个。

A) 2 B) 4 C) 6 D) 7答案:D3. 为实现“线与”逻辑功能,应选用( )。

A) 与非门 B) 与门 C) 集电极开路(OC)门 D) 三态门答案:C4. 图1所示逻辑电路为( )。

A) “与非”门B) “与”门C)“或”门D) “或非”门第1页,共6页,UCC,UCCRCFRRAKBRBC,UBB图1答案:A5. 在下列逻辑部件中,属于组合逻辑电路的是( )。

A) 计数器 B) 数据选择器 C) 寄存器 D) 触发器答案:B6. 已知某触发器的时钟CP,异步置0端为R,异步置1端为S,控制输入端DDV和输出Q的波形如图2所示,根据波形可判断这个触发器是( )。

i图2A) 上升沿D触发器 B) 下降沿D触发器 C) 下降沿T触发器 D) 上升沿T触发器答案:D7. 寄存器要存放n位二进制数码时,需要( )个触发器。

数字逻辑题目及其答案和解析(1)一共60道题

第一部分:1.在二进制系统中,下列哪种运算符表示逻辑与操作?A) amp;B) |C) ^D) ~解析:正确答案是 A。

在二进制系统中,amp; 表示逻辑与操作,它仅在两个位都为1时返回1。

2.在数字逻辑中,Karnaugh 地图通常用于简化哪种类型的逻辑表达式?A) 与门B) 或门C) 异或门D) 与非门解析:正确答案是B。

Karnaugh 地图通常用于简化或门的逻辑表达式,以减少门电路的复杂性。

3.一个全加器有多少个输入?A) 1B) 2C) 3D) 4解析:正确答案是 C。

一个全加器有三个输入:两个加数位和一个进位位。

4.下列哪种逻辑门可以实现 NOT 操作?A) 与门B) 或门C) 异或门D) 与非门解析:正确答案是 D。

与非门可以实现 NOT 操作,当且仅当输入为0时输出为1,输入为1时输出为0。

5.在数字逻辑中,Mux 是指什么?A) 多路复用器B) 解码器C) 编码器D) 多路分配器解析:正确答案是 A。

Mux 是指多路复用器,它可以选择输入中的一个,并将其发送到输出。

6.在二进制加法中,下列哪个条件表示进位?A) 0 + 0B) 0 + 1C) 1 + 0D) 1 + 1解析:正确答案是 D。

在二进制加法中,当两个位都为1时,会产生进位。

7.在数字逻辑中,一个 JK 触发器有多少个输入?A) 1B) 2C) 3D) 4解析:正确答案是 B。

一个 JK 触发器有两个输入:J 和 K。

8.下列哪种逻辑门具有两个输入,且输出为两个输入的逻辑与?A) 与门B) 或门C) 异或门D) 与非门解析:正确答案是 A。

与门具有两个输入,只有当两个输入都为1时,输出才为1。

9.在数字逻辑中,下列哪种元件可用于存储单个位?A) 寄存器B) 计数器C) 锁存器D) 可编程逻辑门阵列解析:正确答案是 C。

锁存器可用于存储单个位,它可以保持输入信号的状态。

10.一个带有三个输入的逻辑门,每个输入可以是0或1,一共有多少种可能的输入组合?A) 3B) 6C) 8D) 12解析:正确答案是 C。

北邮数字逻辑期中试题评分及答案

北京邮电大学《数字电路与逻辑设计》期中考试试卷2012.3.24班级 姓名班内序号注意:所有答案(包括选择题和计算题)一律写在试卷纸上,如果卷面位置不够,请写在试卷的背后,否则不计成绩。

一、(每题1分,共20分)判断(填√或×)、选择(单项选择)题 (请先在本试卷上答题之后,将全部答案汇总到本题末尾的表格中。

) 1.组合逻辑电路中不存在记忆单元。

( √ )2.晶体管的饱和越深,其对灌电流负载的驱动能力越强,但工作速度越慢。

( √ )3.TTL 门的某输入端通过100K Ω电阻接电源端时,可认为该输入是逻辑“1”。

( √ )4.为了增加驱动能力,相同输入时的相同逻辑门输出可以互连在一起使用。

( √ )5.当两个或两个以上输入信号同时变化,变化前后输出相同,而在输入信号变化时可能出现输出瞬间逻辑错误,称为静态逻辑冒险。

( × ) 6.正逻辑的或非门,对应负逻辑的与非门。

( √)7.TTL 与非门的关门电平V OFF 越接近阈值电压V T ,其噪声容限越大。

( √ ) 8.当i j ≠时,必有两个最大项之积0i j M M ⋅=。

( × )9. 用最简与或式表示一个函数时,其表达式可能不是唯一的。

( √ ) 10.反相器的拉电流负载电阻过小时,主要对输出的高电平产生影响。

( √ ) 11.逻辑项ABCD 的相邻项有:C 。

A.ABCD B.BCD A C.ABC D ⋅ D.C A B D ⋅12.判断下列两个函数式中,是否存在逻辑冒险。

B 。

1(,,)Y A B C A BC =+2(,,)Y A B C ABC ABC =+A.不存在,存在B. 不存在,不存在C.存在,不存在D. 存在,存在 13.通过适当连接和控制,可以实现数据双向传输的门电路是 D 。

A. 集电极开路输出的TTL 门电路; B. 互补式输出的TTL 门电路; C. ECL 门电路;D. 三态输出的门电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第8页

得到 B3, B2 关于 A4 A3 A2 A1 函数的卡诺图:

1

1

1

×

×

×

×

1

1

化简得: B3 B2 A4 A3( A2 A0 )

A4 A3 A2 A1

×

×

B3=B2

第9页

10、己知逻辑函数Y A' B'C AC ’,约束条件为 A'C' 0 ,则卡诺图中有( 2 )个无 关项。

11、一个基本 RS 锁存器在正常工作时,它的约束条件是 R + S = 1 ,则它不允许输入 S =

( 0 )且 R = ( 0 )的信号。触发器异步输入端为低电平有效时,如果异步输入端 RD =

A. 译码器; B. 编码器; C. 全加器; D.寄存器

18、要使 JK 触发器的输出 Q 从 1 变成 0,它的输入信号 JK 应为( B )。

A. 00;

B. 01;

C. 10;

D. 无法确定

19、为实现将 D 触发器转换为 T 触发器,

右图的虚框内应是( C )门电路。

A. 与非门; B.或非门;

15、为实现图示的触发器逻辑功能转换,虚线框中应为( B )。 A. 与门; B.非门; C. 或门; D.异或门

16、逻辑函数F = AB + BC 的最小项表达式为( C )。

A. F = m2 + m3 + m6; B.F = m2 + m3 + m7; C. F = m3 + m6 + m7; D. F = m3 + m4 + m7 17、在下列逻辑电路中,不是组合逻辑电路的是( D )。

解:(1)当输入 8421 码: A4 A3 A2 A1 0101 时,输出的 2421 码不变,输出结果即为 A4 A3 A2 A1 0000 ,则令 B4B3B2B1 0000 。

(2)当 0101 A4 A3 A2 A1 1001 时,输出的 2421 码为: A4 A3 A2 A1 0110 ,则可以令

B4B3B2B1 0110 。

B4B3B2B1 中 B4 B1 0 不变,而 A4 A3 A2 A1 0101 时,B3 B2 0 ;0101 A4 A3 A2 A1 1001 时, B3 B2 1 。当 A4 A3 A2 A1 1001 时,都作无关项处理(也可以看作输出都为 0).

C. 同或门; D.异或门

20、已知某二变量输入逻辑门的输入 A、B及输出Y的波形如下,试判断为何 种逻辑门的功能。( C )。

A.与非门; B.或非门; C.与门; D.异或门

21、Y= ABCDC的反函数为 A 。

A. Y = (AB)CDC;

B. Y = (AB)CDC;

C. Y = (AB)CDC;

第4页

┉┉┉┉┉┉┉┉┉┉┉密┉┉┉┉┉┉┉┉┉┉封┉┉┉┉┉┉┉┉┉┉线┉┉┉┉┉┉┉┉┉┉

四、计算分析题(本大题共 10 分)

25、分析左下图所示电路图,(1)写出输出 Y 的逻辑函数式,并化为最简与或式。 (2)用集成译码器 74LS154 和必要的门电路实现 Y。说明:CC4512 为 8 选 1 数据选择

题号

答

案

1

0

B

2

Y AB AC

3

0001000000100011

4

编码(地址)

3

5

Y ABC D

m(6)

6

组合逻辑电路

时序逻辑电路

7

1

8

4

9

5

3

10

2

11

0

12

Qn1 D

0

Qn1

n

JQ

KQn

1 Qn1 T Qn

专业

系

第1页

1、如右图所示,A = 1 时,Y =( 0 );A = 0,

Y =( B );

5、已知函数 Y=

,则它的对偶式为( Y ABC D ),最小项之和的形式为

( m(6) )。

6、数字系统按组成方式可分为( 组合逻辑电路 )和(时序逻辑电路 )两种;

7、函数Y。 8、已知函数 Y = (A,B,C) = m(1,3,4,5),则使 Y = 0 的输入变量最小项有( 4 )个;

9、函数 Y(A,B,C)= A B + C 使其取值为 1 的输入变量最小项有( 5 )个。使其取值 为 0 的输入变量最小项有( 3 )个。

2、Y AB AC ,Y 的最简与或式为( Y AB AC )。 3、(3FF)16 =( 0001000000100011 )8421BCD 4、译码器的逻辑功能是把输入的二进制代码译成对应的( 编码(地址)

)信号;当

数据选择器的数据输入端的个数为 8 时,则其地址码选择端应有( 3 )位。

m(1,3,4,5,6,9,11)

BD ABC ABD

(2)

根据译码器的输出特性:Y mi Y m(1,3,4,5,6,9,11) m1 m3 m4 m5 m6 m9 m11

输出端:

Y1 Y3 Y4 Y5 Y6 Y9 Y11

第5页

五、作图题(本大题共 10 分)

26、试画出四个 CP 脉冲作用下 Q1、Q2、Q3 的波形。(设各触发器初态为零)

1,SD =0,则触发器直接置成( 1 )状态。

12、D 触发器的特征方程为( Qn1 D ),JK 触发器的特征方程为(

Qn1

n

JQ

KQn

),

T 触发器的特征方程为( Qn1 T Qn )。

二、选择题(每题 3 分,本大题共 30 分。请将答案填在下面的方格内)

题号 13

14

15

16

17

18

(2)利用译码器 74HC138 的输出低有效特性,74HC153 的两输出端 Y1 和Y2 用或非门

连接;

A0 A1 A3

B0 B1 B2

74HC138D_4V U1

1 0

0

1 2 3Hale Waihona Puke 6 4 5A B C

G1 ~G2A ~G2B

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

15 14 13 12 11 10 9 7

┉┉┉┉┉┉┉┉┉┉┉密┉┉┉┉┉┉┉┉┉┉封┉┉┉┉┉┉┉┉┉┉线┉┉┉┉┉┉┉┉┉┉

姓名

班 学号

试卷类型: 期中

苏州科技学院 数字逻辑 试卷

使用专业年级软件外包 11 级考试方式 开卷( )闭卷(√)共 8 页

题号 一 二 三 四 五 六

合计

得分

一、填空题(每空 1 分,本大题共 20 分。请将答案填在方格内)

第6页

六、设计题(每题 10 分,本大题共 20 分)

27、试用三线—八线译码器 74HC138 与数据选择器 74HC153 设计一个四位等值比较电 路,当输入 A2A1A0 和 B2B1B0 相等的时候,Y 输出“1”,否则 Y 输出“0”。

解:(1)将双四一选择器 74HC153 扩展成八一选择器;

D. Y = (AB)CDC

22、右图为数据选择器构成的函数发生器, 其输出逻辑式为( D )。

A.Y = AB ; B.Y = AB; C. Y = A; D.Y = B

第3页

三、化简题:将下列式子化简成最简与或式(每题 5 分,本大题共 10 分)

23、用代数法化简:F= AB ABC A(B A)

19

20

21

22

答案

B

C

B

C

D

B

C

C

A

D

13、若输入变量 A、B 全为 1 时,输出 F = 1,则其输入与输出的关系是( B )。 A. 异或; B. 同或; C. 或非; D. 与或

14、下图中,在单个时钟脉冲作用以后,满足 Qn+1 =1 的触发器是____C_______。

第2页

┉┉┉┉┉┉┉┉┉┉┉密┉┉┉┉┉┉┉┉┉┉封┉┉┉┉┉┉┉┉┉┉线┉┉┉┉┉┉┉┉┉┉

1 2 3 4 5 67 8

U3 NOT

74HC153D_4V U2

6 5 4 3

1C0 1C1 1C2 1C3

10 11 12 13

2C0 2C1 2C2 2C3

14 2

A B

1 15

~1G ~2G

1Y 7 2Y 9

第7页

28、试用四位全加器 74LS283 和必要的门电路设计一电路,其功能是将 8421BCD 码转化成 2421BCD 码。

器,逻辑功能表见下表。右下图为 74LS154 的原理管脚图, SA 、 SB 为片选信号端,

输出低电平有效。

CC4512 逻辑功能表

解: (1)

Y mi Di

(m0 m1 m4 m5 )D m2 1 m6 D (C B A C BA C B A C BA)D CB A CB AD ABCD ABCD ABCD ABCD ABC(D D) ABCD

8421 码 2421 码 A4 A3 A2 A1 B3 B2

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001

0000 0001 0010 0011 0100 1011 1100 1101 1110 1111

0 0 0 00 0 0 0 0 10 0 0 0 1 00 0 0 0 1 10 0 0 1 0 00 0 0 1 0 11 1 0 1 1 01 1 0 1 1 11 1 1 0 0 01 1 1 0 0 11 1 1 0 1 0 ×× 1 0 1 1 ×× 1 1 0 0 ×× 1 1 0 1 ×× 1 1 1 0 ×× 1 1 1 1 ××