jedec hbm带宽计算

HBM测试方法

HBM测试方法本文旨在介绍《HBM测试方法》的目的和背景,并概述本文的结构。

HBM测试方法》是指针对电子产品进行人体静电放电(Human Body Model。

HBM)测试的方法。

HBM测试是一种常见的测试手段,用于评估电子设备在人体静电放电环境下的可靠性和安全性。

测试过程中,会模拟人体静电放电对电子产品可能造成的损害,并评估产品是否能够在此类环境下正常工作。

本文将首先介绍HBM测试的目的,即确定电子产品能否在人体静电放电环境下正常使用。

随后,将概述HBM测试的背景,包括该测试方法的起源和发展。

最后,将简要概述本文的结构,介绍后续各部分的内容和组织安排。

通过阅读本文,读者能够对《HBM测试方法》有一个基本的了解,并对其在电子产品可靠性和安全性评估中的重要性有所认识。

HBM(Human Body Model)测试是一种用于评估电子产品静电放电(ESD)抗性能的方法。

该方法模拟人体静电放电对电子产品可能造成的损害,以确保产品在正常使用时的可靠性。

HBM测试涉及以下几个方面:测试设备:HBM测试需要使用专门的测试设备,包括高阻抗电源、高电压放电控制器和模拟人体模型。

测试条件:HBM测试需要在恒温恒湿的环境下进行,以确保测试结果的准确性和可重复性。

测试环境应符合国际标准,如JESD22-A114.测试步骤:HBM测试包括以下步骤:准备测试样品:将待测产品放置在测试台上,并确保与测试设备连接良好。

设置测试参数:根据测试要求,设置合适的测试电流和放电时间。

进行放电测试:通过电压放电控制器模拟人体静电放电,并记录测试结果。

分析测试结果:根据测试结果评估测试样品的静电放电抗性能,包括放电幅度、放电时间和放电曲线等。

HBM测试方法能够帮助电子产品制造商评估产品的静电放电抗性能,以确保产品在正常使用时不会受到静电放电的损害,提高产品的可靠性和稳定性。

本文将介绍HBM测试的相关标准,包括国际标准和行业标准,并说明其重要性和适用范围。

OPA188运算放大器说明书

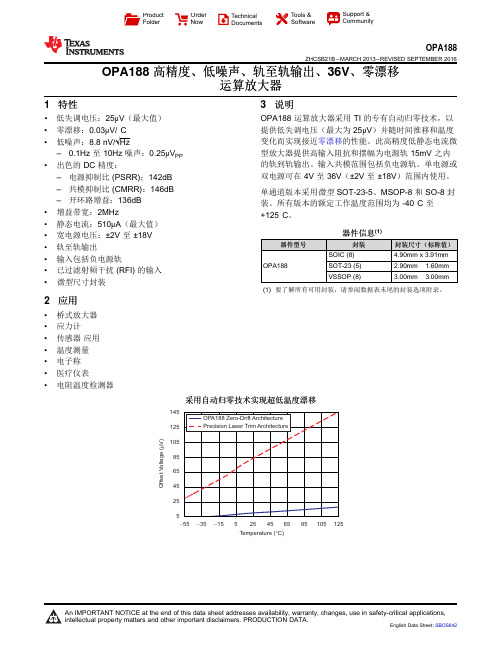

145125105856545255O f f s e t V o l t a g e (V )m -55-15525125Temperature (C)°-35456585105ProductFolder Order NowTechnical Documents Tools &SoftwareSupport &CommunityOPA188ZHCSB21B –MARCH 2013–REVISED SEPTEMBER 2016OPA188高精度、低噪声、轨至轨输出、36V 、零漂移运算放大器1特性•低失调电压:25μV (最大值)•零漂移:0.03μV/°C •低噪声:8.8nV/√Hz–0.1Hz 至10Hz 噪声:0.25μV PP •出色的DC 精度:–电源抑制比(PSRR);142dB –共模抑制比(CMRR):146dB –开环路增益:136dB •增益带宽:2MHz•静态电流:510μA (最大值)•宽电源电压:±2V 至±18V •轨至轨输出•输入包括负电源轨•已过滤射频干扰(RFI)的输入•微型尺寸封装2应用•桥式放大器•应力计•传感器应用•温度测量•电子称•医疗仪表•电阻温度检测器3说明OPA188运算放大器采用TI 的专有自动归零技术,以提供低失调电压(最大为25μV )并随时间推移和温度变化而实现接近零漂移的性能。

此高精度低静态电流微型放大器提供高输入阻抗和摆幅为电源轨15mV 之内的轨到轨输出。

输入共模范围包括负电源轨。

单电源或双电源可在4V 至36V (±2V 至±18V )范围内使用。

单通道版本采用微型SOT-23-5、MSOP-8和SO-8封装。

所有版本的额定工作温度范围均为-40°C 至+125°C 。

器件信息(1)器件型号封装封装尺寸(标称值)OPA188SOIC (8) 4.90mm x 3.91mm SOT-23(5) 2.90mm ×1.60mm VSSOP (8)3.00mm ×3.00mm(1)要了解所有可用封装,请参阅数据表末尾的封装选项附录。

小度写范文[静电放电人体模型测试标准EIA/JEDEC中的问题研究] 静电放电人体模型hbm模板

![小度写范文[静电放电人体模型测试标准EIA/JEDEC中的问题研究] 静电放电人体模型hbm模板](https://img.taocdn.com/s3/m/4de2cdf4c77da26925c5b074.png)

[静电放电人体模型测试标准EIA/JEDEC中的问题研究] 静电放电人体模型hbm摘要:通过具体的实例说明目前的静电放电(Electrostatic Discharge,ESD)人体模型测试标准EIA/JEDEC尚存在一些需要完善的问题。

目前的标准EIA/JEDEC中缺少对起始测试电压的规定,导致有些测试直接从千伏(kV)量级的高压开始进行,造成一些设计不良的ESD防护器件在低压发生失效的状况可能被漏检的后果。

本文研究对象为一个漏端带N阱镇流电阻(Nwell-ballast)的GGNMOS(Gate-Grounded NMOS)型ESD防护结构。

用Zapmaster对它做人体模型(Human Body Model,HBM)测试,发现从1Kv起测时,能够通过8Kv的高压测试;而从50V起测时,却无法通过350V。

TLP测试分析的结果显示此现象确实存在。

本文详细剖析了该现象产生的机理,并采用OBIRCH失效分析技术对其进行了佐证。

因该问题具有潜在的普遍性,因此提出了对目前业界广泛采用的EIA/JEDEC测试标准进行补充完善的建议。

关键词:静电放电;人体模型;EIA/JEDEC 测试标准 A Case Study of Problems in EIA/JEDEC HBM ESD Test Standard HAN Yan, HUO Ming-xu, SONG Bo (ZJU-UCF Joint ESD Lab, Department of Information Science and Electronics Engineering, Zhejiang University, Hangzhou 310027,China)Abstract: There is a current need for modification of EIA/JEDEC Human-Body Model (HBM) Electrostatic Discharge (ESD) test standard, which does not define start and step test voltages. Some measurements start at several kilo-volts, which ignore that ESD protection devices might fail under low voltage stresses. A Gate-Grounded NMOS (GGNMOS) structure with an Nwell-ballast resistor connecting its drain and PAD is investigated for HBM ESD sustaining levels in this paper. When tested with a Zapmaster starting from 1 kilo-volts, the withstand voltage exceeds 8 kilo-volts, whereas the structure failed at 350 volts when the test initiates from 50 volts. The test results from a Transmission-Line Pulsing (TLP)system validate the phenomenon. The reason for the failure is also studied and confirmed with OBIRCH Failure Analysis (FA) results. To address this general issue, a suggestion for improving the present EIA/JEDEC HBM ESD test standard for industry applications is made. Key Words: Electrostatic Discharge, Human Body Model, EIA/JEDEC Test Standard 1引言随着微电子技术的发展和集成电路(Integrated Circuit, IC)工艺的进步,ESD引起的集成电路器件失效的几率越来越大,其防护设计引发业界的高度重视[1-3]。

设计师需要了解的 HBM3 相关知识

2022 年 1 月,JEDEC 发布了新标准JESD238“高带宽内存 (HBM3) DRAM”。

与现有的 HBM2E 标准 (JESD235D) 相比,HBM3 标准提出了多项增强功能,包括支持更大的密度、更高速运算、更高的 Bank 数、更高的可靠性、可用性、可维护性 (RAS) 功能、低功耗接口和新的时钟架构。

HBM3 存储器很快就会被用于 HPC 应用,例如 AI、图形、网络,甚至可能用于汽车。

本文重点介绍了 HBM3 标准的一些关键功能,例如高容量、低功耗、改进的信道和时钟架构以及更先进的 RAS 选项。

图 1 中突出显示了一些关键功能。

图 1:HBM3 与 HBM2E 相比具有多项改进,包括更高的容量、更先进的 RAS 功能和更低的功耗更大、更快、更低功耗HBM2E标准的每个裸片的最大容量为2GB,每个堆栈可以放置12层裸片,从而可实现24GB的最大容量。

虽然标准是允许的,但我们尚未看到市场上出现任何 12 层的 HBM2E 堆栈。

HBM3 标准支持裸片的最大容量是4GB,以及高达 16 层的堆栈,总存储空间可以做到 64 GB,相比HBM2E有近 3 倍的增长。

Synopsys 预计 8 层和 12 层堆栈选项中的 16 GB 和 24 GB HBM3 器件很快就会上市。

为了支持更高密度的器件,HBM3 增加了从 12 层堆栈到 16 层堆栈的可用Bank 数,最多提供 64 个 Bank,增加了 16 个 Bank。

HBM3 标准的最高速度为 6.4 Gbps,几乎是 HBM2E 的最高速度 3.6 Gbps 的两倍。

在不久的将来,我们有理由期待第二代 HBM3 设备的出现。

只需看看HBM2/2E、DDR5(6400 Mbps 升级到 8400 Mbps)和 LPDDR5(最大速度为6400 Mbps,并快速让位于以 8533 Mbps 运行的 LPDDR5X)的速度历史记录,就可见一斑。

hbm jedec标准

hbm jedec标准

HBM是高带宽内存的简称,它是用于高带宽存储器接口的内存规格,主要

应用于高性能计算、服务器、图形处理等领域。

HBM通过并行接口设计,

可以提供更高的内存带宽和容量,以支持大规模数据处理和高性能计算。

JEDEC是电子元件工业联合会(Joint Electron Device Engineering Council)的简称,它是一个国际性的电子设备标准制定组织,制定了许多

关于电子设备的设计、制造、测试和可靠性的标准。

其中,HBM标准就是

由JEDEC制定的一个标准。

HBM标准的制定是为了满足高性能计算和服务器领域对内存带宽和容量的

需求。

HBM通过将多个DRAM芯片堆叠起来,并通过先进的接口技术连接,实现了更高的带宽和容量。

HBM标准经过多次迭代,目前最新的是HBM3标准,它提供了更高的带宽和容量,以及更低的功耗和更高的可靠性。

总之,HBM和JEDEC标准都是为了满足高性能计算和服务器领域对内存带宽和容量的需求而制定的。

通过不断的技术创新和市场需求的推动,HBM

标准将不断演进和升级,以适应未来更高性能、更低功耗、更高可靠性的存储器市场需求。

技术交流-HBM目标等级总结-V1

ESD-HBM目标等级---liukanghui---背景20多年来,HBM (2 kV)和MM (200 V)的IC组件级ESD目标电平基本保持不变,没有更多数据来改变这些电平。

正如本文档中所显示的数据,OEMs所要求的今天增强的静态控制方法并不能证明这些更高的HBM/MM水平是合理的。

在当今最新的硅技术中,ESD过度设计到这种程度,越来越多地限制了硅的面积和性能,并导致产品创新周期更频繁地延迟。

HBM&MM 的ESD 要求回顾一直以来,HBM-2kV 仍然是一个安全“通过”电压目标。

当HBM 测试达到方法3015.7(1989)时,测试仪波形得到了很大的改进,但在这一点上,美国军方停止修改规范,并将HBM 规范的进一步开发转交给ESD 协会和JEDEC 的标准委员会HBM 目标水平动机人们首次对HBM 进行了系统测量(如惠普研究),包括坐在移动椅子上的人。

在第一届EOS/ESD 研讨会上发表了一些关于人体模型的早期工作的总结。

这些早期HBM 研究的工作人员发现,即使戴着腕带,也很容易产生1-2千伏的HBM20世20世纪70年代初汽车行业开始制定ESD 合格等级,福特采用了MM 和200 V ,通用汽车和克莱斯勒更关注HBM ,克莱斯勒在长时间考虑更高的电压后规定了2 kV HBM 的最低标准。

与此同时,RCA TV 部门决定采用2kv HBM 和专门设计的“显像管”测试模型,但没有人接受后者70年代和80年代初根据客户的这些要求,到20世纪80年代中期,半导体公司开始为组件制定内部HBM 标准,2KV HBM 规范成为其中最常见的规范20世纪80年代中期至于原因C, HBM 测试基本与现场的Overstress 破坏无关引入MM 动机a) MM 模拟了未接地的烙铁接触半导体引脚引线引起的故障。

b)此时MM 比HBM 更能模拟CDM 现场的损伤失效。

c)MM 模型中的零欧姆放电电阻导致热损伤的峰值电流高于HBM ,可以进行电压更低的MM 测试由于先进的自动化制造中ESD 控制的显著改善,原因A 不再存在原因B 也不再存在,因为较新的CDM 测试方法比MM 测试更好地再现了这些失败引入MM 动机ESD控制环境的变化和改进ESD历史处理程序早期•ESD控制程序已经实施了很多年。

GDDR和HBM新一代显存技术对比

GDDR和HBM新一代显存技术对比近年来,随着科技的快速发展,电子产品的性能要求也越来越高。

在图形处理和数据存储方面,高性能显卡和内存是不可或缺的组成部分。

GDDR(Graphics Double Data Rate)和HBM(High Bandwidth Memory)作为两种新一代显存技术,已经成为市场上主流的选择。

本文将对这两种显存技术进行对比,探讨它们的优势和不同之处。

1. 技术原理GDDR是一种专为图形处理器(GPU)设计的高带宽显存技术。

它采用了复杂的信号处理技术,在保持较低的功耗和低延迟的情况下实现了较高的数据传输速率。

GDDR通过并行传输技术,在相同频率下比传统的SDRAM(Synchronous Dynamic Random Access Memory)能够传输更多的数据。

HBM则是一种创新的高带宽内存架构。

它采用了通过硅基互联层将内存堆叠在一起的方式,实现了内存容量的大幅度增加和功耗的显著降低。

HBM利用高频率和并行传输方式,能够提供非常高的带宽和低延迟,适用于高性能计算和图形处理。

2. 带宽性能带宽是显存技术的一个重要指标,决定了显卡的数据传输速度和处理能力。

GDDR和HBM在带宽性能上有一些显著的差异。

GDDR技术在数据传输时能够实现较高的频率,从而获得较高的带宽。

GDDR5X甚至可以提供超过400GB/s的带宽,适用于大规模的图形计算和游戏。

HBM技术通过堆叠多个内存芯片来实现高带宽。

由于内存芯片的堆叠,HBM能够在较小的物理尺寸上提供更大的带宽。

例如,HBM2可以提供高达256GB/s的带宽,同时具有较低的延迟。

3. 性能功耗比性能功耗比是衡量显存技术优劣的另一个重要指标。

在同时满足高性能和低功耗的需求下,GDDR和HBM在性能功耗比上有所区别。

GDDR技术通过提高频率和并行传输的方式来提高数据传输速度,但功耗相对较高。

尽管GDDR能够提供高带宽,但其功耗也相应会增加,可能不适用于对功耗有严格要求的应用场景。

ESD模型和测试标准

1、ESD模型分类

2、HBM和MM测试方法标准

3、 CDM模型和测试方法标准

4、 EIC模型和测试方法标准

5、 TLP及其测试方法

6、拴锁测试

7、 I-V测试

8、标准介绍

1、ESD模型分类

因ESD产生的原因及其对集成电路放电的方式不同

,经过统计,ESD放电模型分下列四类:

(1) 人体放电模式 (Human-ቤተ መጻሕፍቲ ባይዱody Model, HBM)

(2) 机器放电模式 (Machine Model, MM)

(3) 组件充电模式 (Charged-Device Model, CDM)

(4) 电场感应模式 (Field-Induced Model, FIM)

另外还有两个测试模型:

(5)对于系统级产品测试的IEC电子枪空气放电模式

(6)对于研究设计用的TLP模型

引脚,将其作为参考节点连接到B端。其他

所有引脚依次连接到A端,并且在AB间接

入短接线。使用正负1000V的脉冲电压在

AB端,观察波形,经过所有引脚对的电流

波形必须符合如图波形

2、HBM和MM测试方法标准

HBM测试方法及标准

1.ANSI-STM5.1-2001

JESD22-A114D -2005

(2)ESD敏感度(sensitivity):引起器件失效的ESD等

级(level)

(3)ESD耐受电压(withstand voltage):在不引起器

件失效前提下的最大ESD等级

(4)步进耐压增强(Step stress test hardening):在步

进增加的测试电压下,器件的耐受电压的现象

4、 EIC模型和测试方法标准

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

jedec hbm带宽计算

JEDEC HBM(High Bandwidth Memory)是一种高带宽内存技术,用于提供高性能的图形处理器和加速器。

要计算JEDEC HBM的带宽,需要考虑以下几个因素:

1. 数据总线宽度,JEDEC HBM标准定义了每个通道的数据总线

宽度,通常为128位或256位。

数据总线宽度越大,带宽越高。

2. 时钟频率,JEDEC HBM规范中定义了内存的工作频率,通常

以MHz为单位。

时钟频率越高,数据传输速度越快,带宽也会相应

增加。

3. 通道数量,HBM内存通常有多个通道,每个通道都有自己的

数据总线。

通道数量的增加会直接提高带宽。

带宽的计算公式为,带宽 = 数据总线宽度× 时钟频率× 通

道数量 / 8。

需要注意的是,这里的数据总线宽度和时钟频率需要

以相应的单位进行转换,以便在公式中得到正确的带宽单位(通常

为GB/s)。

举例来说,假设JEDEC HBM内存的数据总线宽度为256位,时钟频率为1.6 GHz,通道数量为4,则带宽计算公式为,带宽 = 256 × 1.6 × 4 / 8 = 256 GB/s。

通过以上公式和例子,可以计算出JEDEC HBM的带宽。

当然,在实际应用中,还需要考虑其他因素,如延迟、数据传输模式等,以全面评估内存的性能特征。

希望这个回答能够帮助你理解JEDEC HBM带宽的计算方法。