1-38译码器

138译码器的使用

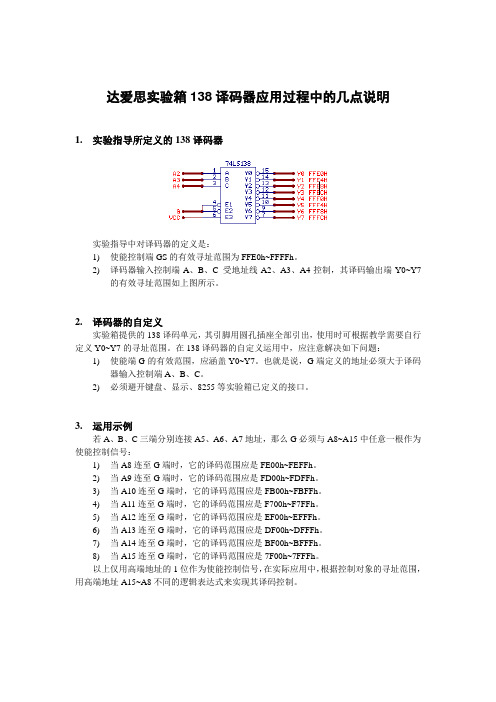

达爱思实验箱138译码器应用过程中的几点说明1.实验指导所定义的138译码器实验指导中对译码器的定义是:1)使能控制端GS的有效寻址范围为FFE0h~FFFFh。

2)译码器输入控制端A、B、C 受地址线A2、A3、A4控制,其译码输出端Y0~Y7的有效寻址范围如上图所示。

2.译码器的自定义实验箱提供的138译码单元,其引脚用圆孔插座全部引出,使用时可根据教学需要自行定义Y0~Y7的寻址范围。

在138译码器的自定义运用中,应注意解决如下问题:1)使能端G的有效范围,应涵盖Y0~Y7。

也就是说,G端定义的地址必须大于译码器输入控制端A、B、C。

2)必须避开键盘、显示、8255等实验箱已定义的接口。

3.运用示例若A、B、C三端分别连接A5、A6、A7地址,那么G必须与A8~A15中任意一根作为使能控制信号:1)当A8连至G端时,它的译码范围应是FE00h~FEFFh。

2)当A9连至G端时,它的译码范围应是FD00h~FDFFh。

3)当A10连至G端时,它的译码范围应是FB00h~FBFFh。

4)当A11连至G端时,它的译码范围应是F700h~F7FFh。

5)当A12连至G端时,它的译码范围应是EF00h~EFFFh。

6)当A13连至G端时,它的译码范围应是DF00h~DFFFh。

7)当A14连至G端时,它的译码范围应是BF00h~BFFFh。

8)当A15连至G端时,它的译码范围应是7F00h~7FFFh。

以上仅用高端地址的1位作为使能控制信号,在实际应用中,根据控制对象的寻址范围,用高端地址A15~A8不同的逻辑表达式来实现其译码控制。

74HC138

`LS138 最大 单位 V V

-1.5

0.4 0.5 V 0.1 20 0.1 20 -0.4 mA mA μA mA μA -40 -42 10 mA mA

IOS 输出短路电流 Icc 电源电流

【1】 :测试条件中的“最大”和“最小”用推荐工作条件中的相应值。

动态特性(TA=25℃) ‘S138 最大 7 10.5 Vcc=5V CL=15pF RL=280Ω (‘LS138 为 2KΩ) 12 12 8 11 ‘LS138 最大 20 41 27 39 18 32 26 38 ns

当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为 低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低 电平译出。 利用 G1、/(G2A)和/(G2B)可级联扩展成 24 线译码器;若外接一个反 相器还可级联扩展成 32 线译码器。 若将选通端中的一个作为数据输入端时,138 还可作数据分配器。 管脚图:

54138/74138

3 线-8 线译码器 简要说明: 138 为 3 线-8 线译码器,共有 54/74S138 和 54/74LS138 两种线路结构型式,其主 要电特性的典型值如下: 型号 CT54S138/CT74S138 CT54LS138/CT74LS138 Tpd (ABC->Y)(3 级) 8ns 22ns PD 245mW 32mW

kings

`S138 测试条件【1】 最小 最大 最小 Vcc 最小 IIK=-12mA 54 -1.2 Vcc=最小, VIH=2V,VIL=最大, IOH=最大 VCC=最 小,VIH=2V,VIL=最 大,IOL=最大 Vcc=5V 2.5 2.5 74 2.7 2.7 54 0.5 74 0.5 1 VI=5.5V VI=7V 50 1 VI=5.5V VI=7V VIH=2.7V VIL=0.4 V VIL=0.5 V 54 74 -40 -40 -2 -100 -100 74 -6 -5 50 Vcc=5V,VIH=2.7V Vcc=最大 Vcc=最大 Vcc=最大 Vcc=最大 Vcc=最大

138二进制译码器

5 输出端

表3-6 74LS138的功能表

高电平 有效

低电平 有效

禁止 译码 译 码 工 作

2015年11月11日10时 25分

译中为0

6

低电平有 效输出

三位二进 制代码

使能端

图3-8 74LS138的逻辑符号

2015年11月11日10时 25分

7

74LS138的逻辑功能

2015年11月11日10器实现逻辑函数:

F ( A, B, C ) m(1,3,5,6,7)

解:因为 则

Yi mi (i 0,1,2,7)

m1 m3 m5 m6 m7 m1 m3 m5 m 6 m 7 Y1 Y3 Y5 Y6 Y7

F ( A, B, C ) m (1,3,5,6,7)

2015年11月11日10时 25分

12

因此,正确连接控制输入端使译码器处于工作 状态,将 Y1 、Y3 、Y5 、 Y7 经一个与非门输 Y6 、 出,A2、A1、A0分别作为输入变量A、B、C,就可实

现组合逻辑函数。

F ( A, B, C ) m(1,3,5,6,7) Y1 Y3 Y5 Y6 Y7

3.3

译码器

结束 放映

3.3.1 二进制译码器 3.3.2 二-十进制译码器

2015年11月11日10时 25分

1

复习

全班有42名同学,需几位二进制代码才能表示? 为什么要用优先编码器?

2015年11月11日10时 25分

2

3.3

译码器

译码: 编码的逆过程,将编码时赋予代码的特 定含义“翻译”出来。 译码器: 实现译码功能的电路。

74ls138译码器

74ls138译码器(1)启动Quartus II,作电路图如下:(2)建⽴波形⽂件:进⼊如下页⾯:点击右键,选择Insert 中的Insert Node or Bus点击其中的Node Finder,点击将引脚导⼊。

点击>>,将引脚导⼊Selected Nodes回主页⾯:选择a、b、c三个引脚放⼊⼀个模块中,点击右键Grouping和Group在Group name中输⼊IN,点击OK,第⼀栏位主线显⽰。

将a、b、c三个管脚全选,单击右键,选择V alue—Random V alue设置仿真时间间隔。

再点击At random intervals点击OK(3)点击Procesing,选中Simulator Tool进⾏仿真进⼊后选中Simulator Tool,选中Functional,进⾏功能仿真。

点击Generate Functional Simulation Netlist,进⾏仿真,波形输出;点击是。

仿真完毕,可以检验波形,看波形。

将此电路转化为⽐较简单的电路转化过程如下:点击File—>Create/Update—>Create Symbol Files for Current File点击保存。

(4)新建图层BDF格式,在Project中找到以ls138命名的简单元件。

再点击右键,选中Generate Pins for System Ports 页⾯如下:保存,再运⾏仿真。

(4)分配引脚:观察引脚颜⾊变化:再将所绘制的电路,输⼊硬件设备中。

点击Start开始。

ls138译码器内部电路逻辑图功能表简单应用

74ls138译码器内部电路逻辑图功能表简单应用74HC138:74LS138 为3 线-8 线译码器,共有 54/74S138和 54/74LS138 两种线路结构型式,其74LS138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

74LS138的作用:利用 G1、/(G2A)和/(G2B)可级联扩展成 24 线译码器;若外接一个反相器还可级联扩展成 32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS138<74ls138译码器内部电路>3线-8线译码器74LS138的功能表<74ls138功能表>无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出<74ls138逻辑图>由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图电路中如果把作为“数据”输入端(在同一个时间),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

138译码器工作原理

138译码器工作原理

138译码器是一种数字电路,可以将三个输入信号转换为八个

输出信号。

它的工作原理如下:

1. 输入信号:138译码器有三个输入信号,分别是A0、A1和

A2。

这些输入信号可以是高电平(1)或低电平(0),代表

不同的逻辑状态。

2. 级联:138译码器的三个输入信号可以级联在一起,形成八

种可能的输入组合。

每个输入组合对应着输出信号的一种状态。

3. 输出信号:138译码器有八个输出信号,分别是Y0、Y1、

Y2、Y3、Y4、Y5、Y6和Y7。

这些输出信号可以是高电平(1)或低电平(0),根据输入信号的不同组合来确定。

4. 译码功能:138译码器根据输入信号的不同组合,将对应的

输出信号设置为高电平,其他输出信号设置为低电平。

这样就可以将三个输入信号译码成八个输出信号。

总之,138译码器根据输入信号的不同状态,将对应的输出信

号设置为高电平,实现输入和输出之间的转换。

这样可以方便地将一个三位输入信号转换为八个输出信号。

三八译码器的结构、原理与设计_毕业论文

题目:三八译码器的结构、原理与设计学院:物理学院专业:电子科学与技术姓名:董少雨指导教师:赵宏亮完成日期:2014年5月20日毕业论文任务书毕业论文题目:三八译码器的结构、原理与设计选题意义、创新性、科学性和可行性论证:如今全球信息化的步伐正在不断加快,数字信号的产生、变换等方面应用的更加广泛。

三八译码器在信号处理方面起着十分重要的作用。

本文主要阐述三八译码器的基本结构和工作原理,并通过对时序逻辑电路设计方法的研究,完成三八译码器的设计。

主要内容:译码器的种类与特点,三八译码器的结构和工作原理,最后完成了三八译码器的设计。

目的要求:1、熟悉三八译码器的发展背景和趋势。

2、掌握各类译码器的工作性能。

3、了解三八译码器的基本结构和工作原理。

4、学会时序逻辑电路的设计方法。

计划进度:2013年12月21日~2014年2月25日,确定毕业论文选题,并搜集资料,查阅相关文献;2014年2月26日~4月10日,写出论文总体大纲,运用软件得到仿真数据;2014年4月11日~4月25日,论文撰写;提交初稿;2014年4月26日~5月19日,修改论文,论文定稿,准备答辩。

指导教师签字:主管院长(系主任)签字:2013年12 月25 日辽宁大学本科毕业论文(设计)指导记录表论文题目三八译码器的结构、原理与设计学生姓名董少雨学号101002103 年级、专业10级电子科学与技术指导教师姓名赵宏亮指导教师职称讲师所在院系物理学院第一次指导(对确定题目、毕业论文(设计)任务书的指导意见):由于以前对三八译码器有所了解,《三八译码器的结构、原理与设计》题目符合毕业论文设计的要求。

研究三八译码器可以加强对数字集成电路的了解,毕业论文进度安排合理,接下来按照进度写出论文总体大纲。

指导方式:(请选择)面谈√电话电子邮件指导教师签字:2013年12月24日第二次指导(对论文提纲的指导意见):查阅相关资料,进一步地掌握三八译码器的基本结构和工作原理,三八译码器的设计方法十分合理,要熟悉掌握相关软件的使用并从中得到相关数据。

138译码器 文档

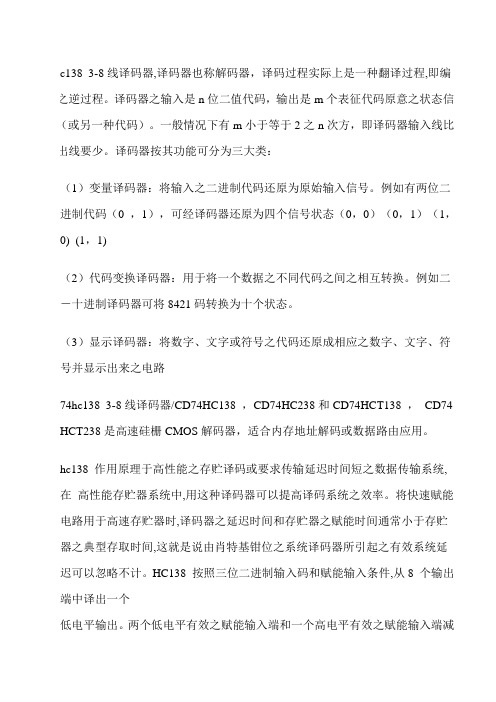

74h c138 3-8线译码器,译码器也称解码器,译码过程实际上是一种翻译过程,即编码之逆过程。

译码器之输入是n位二值代码,输出是m个表征代码原意之状态信号(或另一种代码)。

一般情况下有m小于等于2之n次方,即译码器输入线比输出线要少。

译码器按其功能可分为三大类:(1)变量译码器:将输入之二进制代码还原为原始输入信号。

例如有两位二进制代码(0 ,1),可经译码器还原为四个信号状态(0,0)(0,1)(1,0) (1,1)(2)代码变换译码器:用于将一个数据之不同代码之间之相互转换。

例如二-十进制译码器可将8421码转换为十个状态。

(3)显示译码器:将数字、文字或符号之代码还原成相应之数字、文字、符号并显示出来之电路74hc138 3-8线译码器/CD74HC138 ,CD74HC238和CD74HCT138 ,CD74 HCT238是高速硅栅CMOS解码器,适合内存地址解码或数据路由应用。

hc138 作用原理于高性能之存贮译码或要求传输延迟时间短之数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统之效率。

将快速赋能电路用于高速存贮器时,译码器之延迟时间和存贮器之赋能时间通常小于存贮器之典型存取时间,这就是说由肖特基钳位之系统译码器所引起之有效系统延迟可以忽略不计。

HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效之赋能输入端和一个高电平有效之赋能输入端减少了扩展所需要之外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。

在解调器应用中,赋能输入端可用作数据输入端。

图1 引脚图图2 功能图图3 测试电路和波形应用电路:图4 舞台发光二极管灯光图5 可编程时钟定时器电路由上表可见74HC138译码器输出低电平有效。

为增加译码器功能,除三个输入端C、 B、 A 外,还设置了G1、/G2A,/G2B,使译码器具有较强之抗干扰能力且便于扩展。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

在中规模集成电路中译码器有几种型号,使用最广的通常是74ls138译码器,其是一个3到8的三八译码器,下图是该38译码器原理逻辑符号及管脚排布,下表中列出了74ls138译码器器件的逻辑功能,从表中可以看出其输出为低电平有效,使能端G为高电平有效,/G,/G为低电平有效,当其中一个为低电平,输出端全部为1。

例试用三八译码器_74ls138译码器实现函数F(X,Y,Z)=∑m(0,2,4,7)

用74138实现函数与前面讲到的译码器实现逻辑函数的方法相同,但须注意两点:

1.74ls138译码器的输出是低电平有效,故实现逻辑功能时,输出端不可接或门及或非门(因为每次仅一个为低电平,其余皆为高电平);

2.74ls138译码器有使能端,故使能端必须加以处理,否则无法实现需要的逻辑功能。

下图给出了其最终的38译码器原理图电路。

芯片74LS138有什么用?

5

如题,,请帮忙说明一下各个引脚的作用

满意答案

简单就好 15级 2010-04-11

74HC138:74LS138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其74LS138工作原理如下:

当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为

低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低

电平译出。

74LS138的作用:

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反

相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器

追问:

“可将地址端(A、B、C)的二进制编码在一个对应的输出端以低

电平译出”是什么意思,能举例吗?

回答:。