基于FPGA的全数字锁相环的设计与应用

应用于数字锁相环的NCO设计

应用于数字锁相环的NCO设计保玲;佘世刚;周毅;金玉琳【摘要】本文鉴于数字锁相环在实际应用中对信号频率的准确度和稳定度有较为严格的要求,设计一种应用于数字锁相环的数控振荡器(NCO,Number Controlled Oscillator)。

基于直接数字频率合成(DDS)技术,介绍NCO工作原理,基于FPGA实现NCO,关键是相位累加器与波形存储器两个模块的设计,并利用QUARTUS对设计结果进行编译仿真。

对NCO杂散信号进行频谱分析,并提出解决方法。

该设计有效抑制杂散,修改灵活,便于调试,在数字锁相环设计中可有广泛应用。

%Based on the high standard for veracity and stability of signal frequency applied in digital PLL,a kind of NCO(Number Controlled Oscillator) is designed applied in digital PLL.Based on DDS(Direct Digital Frequency Synthesizers),the basic principle of NCO is introduced,NCO is realized based on FPGA.The key point is how to design phase accumulator and ROM,the design result is complied and simulated with applied software tool QUARTUS.The frequency spectrum of NCO is analyzed,and the resolve measure is given.This design can control spurious,modify conveniently,it has widely application in design of digital PLL.【期刊名称】《电子设计工程》【年(卷),期】2011(019)014【总页数】3页(P160-162)【关键词】NCO;DDS;杂散;FPGA【作者】保玲;佘世刚;周毅;金玉琳【作者单位】兰州空间技术物理研究所,甘肃兰州730000;兰州空间技术物理研究所,甘肃兰州730000;兰州空间技术物理研究所,甘肃兰州730000;兰州空间技术物理研究所,甘肃兰州730000【正文语种】中文【中图分类】TN802数字锁相环已在数字通信、无线电电子学及电力系统自动化等领域得到广泛应用。

全数字锁相环设计研究

一、引言数字锁相环(DPLL)是一种相位反馈控制系统。

DPLL通常有三个组成模块:数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)。

本文采用超前-滞后型数字锁相环(LL-DPLL)的设计方案,在LL-DPLL中,DLF用双向计数逻辑和比较逻辑实现,DCO采用加扣脉冲式数控振荡器。

这样设计出来的DPLL 具有结构简洁明快,参数调节方便,工作稳定可靠的优点。

二、数字锁相环的分类1.过零型数字锁相环路这种数字锁相环路采用过零采样数字鉴相器,即本地估算信号在输入信号的过零点上采样后进行A/D变换,得到数字相位误差信号输出。

2.触发器型数字锁相环路这类全数字锁相环路使用的数字鉴相器是触发器型数字鉴相器。

其特点是利用输入信号和本地估算信号的正向过零点对触发器进行触发,在触发器的置“ 0”和置“ 1” 的时间间隔内,得到相位误差信号。

置“ 0”和置“ 1”的时间间隔宽度就表征了输入信号和本地估算信号之间的相位误差大小。

3.超前-滞后型数字锁相环路这种数字锁相环路采用的鉴相器是超前-滞后型数字鉴相器。

超前-滞后型数字鉴相器在每一个周期内得到输入信号的相位比本地估算信号相位超前或滞后的信息。

因此,这种鉴相器的相位误差输出只有超前或滞后两种状态。

然后将误差相位的超前或滞后信息送到序列滤波器,产生对DCO的“ 加” 或“ 扣” 脉冲控制指令去改变DCO的时钟周期,使本地估算信号的相位输入信号相位靠拢。

4.奈奎斯特速率采样型数字锁相环路在这种数字锁相环路中,对输入信号的采样按照奈奎斯特速率进行。

也就是说,对输入信号进行A/D变换的采样频率必须按照奈奎斯特速率进行,以使输入信号能够依据奈奎斯特取样定理再现。

A/D变换后的输入信号与本地估算信号进行数字相乘,得到需要的相位误差数字信号,以完成鉴相功能。

三、系统设计本设计是基于直接数字频率合成器(Direct Digital Synthesizer)原理的信号发生器,用硬件描述语言Verilog来编程,用Altera公司的开发平台QUARTUSⅡ6.0来仿真,最后下载到StratixⅡ系列的EP2S60器件中进行验证。

基于FPGA的全数字锁相环设计与实现

基于FPGA的全数字锁相环设计与实现一、前言全数字锁相环(Digital Phase-Locked Loop,简称DPLL)是一种数字电路设计技术,可实现同步数字信号的调制和解调。

基于FPGA的全数字锁相环设计与实现,是一个极为重要的课题。

它可以有效地提高数字电路的性能,使得数字系统具有更优越的特性,并可广泛应用于数字电路的设计、数字信号的处理等领域。

二、DPLL 的体系结构DPLL是由相频检测器、滤波器、数字控制振荡器和时钟输出等多个部分组成的。

其中,相频检测器、滤波器和数字控制振荡器通常被集成到FPGA的内部,而时钟输出则需要通过FPGA的普通I/O口与市场上常见的外部输出设备相结合。

三、数字锁相环的工作原理数字锁相环的工作原理基于一个反馈循环系统,其中参考振荡器的频率与输入信号会被比较,然后通过差错检测网络来确定缺陷。

如果这些信号频率不匹配,则通过调整数字控制振荡器的频率来达到匹配。

然后,系统会根据输出信号和参考信号的相位差异来调整数字控制振荡器的频率,并通过PLL的反馈路径传输至输入端,进而得到和参考信号相同频率的输出信号。

四、数字锁相环的应用数字锁相环在通信领域有着广泛的应用,如数据码隆、数字调制、同步检测等;在数字领域,数字锁相环主要应用于数字信号处理、频谱分析、信噪比提高等方面;在电子仪器领域,数字锁相环可以被应用于测量领域、噪声分析、频率合成等方面。

五、基于FPGA的数字锁相环的设计数字锁相环的设计是一项非常复杂的工作,其中需要解决的问题主要有相频检测、低通滤波、数字控制振荡器的设计和时钟输出等方面。

在基于FPGA的数字锁相环设计过程中,可以采用很多不同的方法和技术来解决这些问题。

在数字锁相环的设计中,相频检测器是极其关键的部分,其主要功能是检测输入信号与数字控制振荡器的频率是否匹配。

其中,相频检测器常用的方式有两种:一是通过比较输入信号和数字控制振荡器的频率来实现;二是通过测量输入信号和数字控制振荡器的相位差来实现。

基于Verilog的全数字锁相环的设计

使 用 相 同 的 系 统 时 钟 信 号 . 数 字 锁 相 环 根 据 输 入 信 号 和 时 钟 输 出 信 号 之 间 的相 位 误 差 信 号 送 人 鉴 相 器 , 全 并 对 相 对 误 差 进 行 平 滑 滤 波 , K变 模 计 数 器 产 生 控 制 信 号 , 控 振 荡 器 根 据 控 制 信 号 不 断 反 馈 调 节 , 由 数 使

第2 5卷

图2 全 数 字 锁 相 环 实 现 的 框 图

3 全 数 字锁 相环 的实 现

( )数 字鉴 相 器 的 设 计 1

本 设 计 选 用 异 或 门数 字 鉴 相 器 . 或 门 数 字 鉴 相 器 的 主 要 任 务 是 用 来 比较 输 入 信 号 和 输 出 信 号 之 间 异 的 相 位 差 qs b e:  ̄fi I n—qf u 并 输 出一 个 误 差 信 号 s ) S o t, e作 为 K 变 模 可 逆 计 数 器 的计 数 方 向 控 制 信 号 . 环

另 外 两 个 DAC模 块 把 输 入 信 号 f i n和 输 出 信 号 lu 转 换 成 模 拟 波 形 来 观 察 验 证 . 次 全 数 字 锁 相 环 ot 本

的框 图 如 下 :

・

5 0・

刘 永 勤 : 于 V ro 全 数 字锁 相 环 的 设 计 基 eig的 l

刘 永 勤

( 南 师 范 学 院 物 理 与 电子 工 程 系 , 西 渭 南 7 40 ) 渭 陕 10 0 摘 要 : 章 介 绍 了 全 数 字 锁 相 环 的 基 本 结 构 和 工 作 原 理 , 出 了 一 种 基 于 vro 文 提 eig的全 数 字 锁 相 环 的设 计 方 法 , 利 l 并

FPGA_ASIC-一种基于FPGA实现的全数字锁相环

+ ’P $取 积 分 增 减 计 数 的上限阈值 "&AGC 为略大于 ? &(1"* *&(A+.

$50"" 8 ) 9 是 一 个 二 阶 系 统 的 传 递 函 数 % 而 且 ! 该 二 阶 系 * $ ),=&&’

基于FPGA的数字锁相环的设计

目录第一章绪论...................................... 错误!未定义书签。

1.1锁相环技术的发展及研究现状................................................... 错误!未定义书签。

1.2课题研究意义 .............................................................................. 错误!未定义书签。

1.3本课题的设计内容....................................................................... 错误!未定义书签。

第二章 FPGA的设计基础............................. 错误!未定义书签。

2.1硬件设计语言-Verilog HDL..................................................... 错误!未定义书签。

2.2 FPGA的设计流程 ......................................................................... 错误!未定义书签。

第三章锁相环的原理. (2)3.1全数字锁相环基本结构 (3)3.2全数字锁相环的工作原理 (4)第四章数字锁相环的设计 (5)4.1基于FPGA的数字锁相环总体设计方案 (5)4.2数字鉴相器的设计 (6)4.3 K变模可逆计数器的设计 (7)4.4脉冲加减器的设计 (10)4.5 N分频器的设计 (12)第五章实验仿真与调试 (14)5.1数字锁相环的仿真 (14)5.2数字锁相环的系统实验 (15)结束语 (19)参考文献 (20)附录 (21)第一章锁相环的原理许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

基于FPGA的积分型数字锁相环的设计与实现

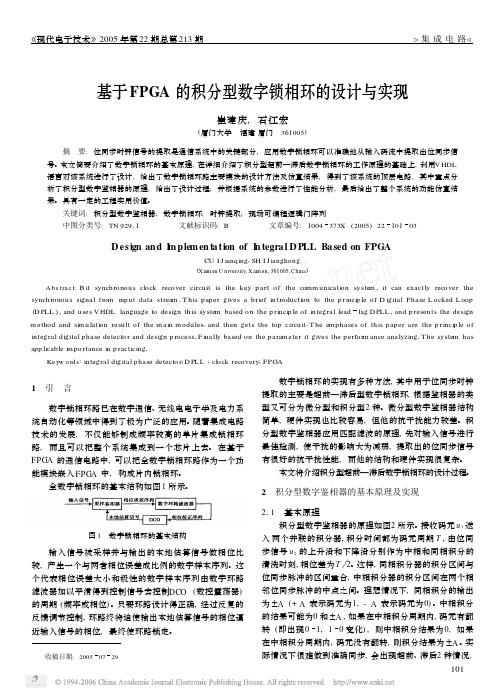

211 基本原理 积分型数字鉴相器的原理如图2 所示。接收码元 u1 送

入 两个并联的积分器, 积分时间都为码元周期 T , 由位同 步信号 u2 的上升沿和下降沿分别作为中相和同相积分的 清洗时刻, 相位差为 T 2。这样, 同相积分器的积分区间与 位同步脉冲的区间重合, 中相积分器的积分区间在两个相 邻位同步脉冲的中点之间。理想情况下, 同相积分的输出 为±A (+ A 表示码元为1, - A 表示码元为0)。中相积分 的结果可能为0 和±A , 如果在中相积分周期内, 码元有翻 转 (即出现0 1, 1 0 变化) , 则中相积分结果为0, 如果 在中相积分周期内, 码元没有翻转, 则积分结果为±A。实 际情况下很难做到准确同步, 会出现超前、滞后2 种情况,

- - 向上计数

dou t1< = dou t1- ′1′;

- - 输入码元为低电平

end if;

- - 向下计数

end if;

end if;

end p rocess; p rocess (sclr)

- - 在清洗时刻完成电平判决

beg in if (sclr′even t and sclr= ′1′) then if (dou t1> = " 01111011") sp hase< = ′1′; elsif (dou t1< " 01111001") sp hase< = ′0′; end if; end if;

101

制造与设计

崔建庆等: 基于 FPGA 的积分型数字锁相环的设计与实现

这时, 同相积分器在清除时刻的输入值为±A , 其极性仍 取决于输入码元的极性。在超前情况下, 中相积分器的积 分区间内码元如果有从- A 到A 的转换, 则中相积分器在 清洗时刻的采样输出为负; 反之, 输出为正。滞后时情况 与超前时的相反。在超前和滞后两种情况下各点波形如图 3 所示。

基于FPGA的宽频带数字锁相环的设计与实现

数控振荡器根据误差信号调整本 地信号的频率和相位,实现信号 的同步。

02 基于FPGA的数字锁相环 设计

FPGA简介

01

02

03

可编程逻辑门阵列

高度集成

灵活性

FPGA是一种可编程逻辑门阵列, 通过编程实现各种数字逻辑功能。

FPGA内部包含大量逻辑门和触 发器,可以实现复杂的数字电路 设计。

FPGA可以通过重新编程实现不 同的数字电路设计,具有很高的 灵活性。

数字锁相环的FPGA实现方案

数字鉴相器

采用FPGA实现数字鉴相器,用于比较输入信号 和参考信号的相位差。

环路滤波器

采用FPGA实现环路滤波器,用于滤除鉴相器输 出信号中的高频分量。

数控振荡器

采用FPGA实现数控振荡器,用于产生参考信号。

FPGA设计流程

仿真验证

使用仿真工具对设计进行仿真 验证,确保逻辑电路的正确性。

03 MATLAB/Simulink:用于系统建模、仿真和分 析。

数字锁相环的FPGA实现过程

1. 系统建模

使用MATLAB/Simulink建立数字锁相 环的数学模型,并进行仿真验证。

3. 代码生成

将算法转换为硬件描述语言 (VHDL/Verilog),并使用FPGA开

发工具进行综合和实现。

2. 算法设计

布局布线

将配置文件映射到FPGA的逻 辑门资源上,进行布局布线。

设计输入

使用硬件描述语言(如VHDL 或Verilog)编写数字锁相环的 逻辑电路。

综合优化

将逻辑电路转换为FPGA上的 配置文件,并进行优化处理。

下载配置

将配置文件下载到FPGA中, 进行实际测试和验证。

03 宽频带数字锁相环的关键 技术