新型全数字锁相环的逻辑电路设计动态参数调节

全数字锁相环设计研究

一、引言数字锁相环(DPLL)是一种相位反馈控制系统。

DPLL通常有三个组成模块:数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)。

本文采用超前-滞后型数字锁相环(LL-DPLL)的设计方案,在LL-DPLL中,DLF用双向计数逻辑和比较逻辑实现,DCO采用加扣脉冲式数控振荡器。

这样设计出来的DPLL 具有结构简洁明快,参数调节方便,工作稳定可靠的优点。

二、数字锁相环的分类1.过零型数字锁相环路这种数字锁相环路采用过零采样数字鉴相器,即本地估算信号在输入信号的过零点上采样后进行A/D变换,得到数字相位误差信号输出。

2.触发器型数字锁相环路这类全数字锁相环路使用的数字鉴相器是触发器型数字鉴相器。

其特点是利用输入信号和本地估算信号的正向过零点对触发器进行触发,在触发器的置“ 0”和置“ 1” 的时间间隔内,得到相位误差信号。

置“ 0”和置“ 1”的时间间隔宽度就表征了输入信号和本地估算信号之间的相位误差大小。

3.超前-滞后型数字锁相环路这种数字锁相环路采用的鉴相器是超前-滞后型数字鉴相器。

超前-滞后型数字鉴相器在每一个周期内得到输入信号的相位比本地估算信号相位超前或滞后的信息。

因此,这种鉴相器的相位误差输出只有超前或滞后两种状态。

然后将误差相位的超前或滞后信息送到序列滤波器,产生对DCO的“ 加” 或“ 扣” 脉冲控制指令去改变DCO的时钟周期,使本地估算信号的相位输入信号相位靠拢。

4.奈奎斯特速率采样型数字锁相环路在这种数字锁相环路中,对输入信号的采样按照奈奎斯特速率进行。

也就是说,对输入信号进行A/D变换的采样频率必须按照奈奎斯特速率进行,以使输入信号能够依据奈奎斯特取样定理再现。

A/D变换后的输入信号与本地估算信号进行数字相乘,得到需要的相位误差数字信号,以完成鉴相功能。

三、系统设计本设计是基于直接数字频率合成器(Direct Digital Synthesizer)原理的信号发生器,用硬件描述语言Verilog来编程,用Altera公司的开发平台QUARTUSⅡ6.0来仿真,最后下载到StratixⅡ系列的EP2S60器件中进行验证。

一种新型带宽自适应全数字锁相环的设计方案

一种新型带宽自适应全数字锁相环的设计方案

本方案采用理论分析与硬件电路设计相结合的方法进行了系统设计,并用FPGA予以实现。

系统仿真与硬件电路测试结果证实了设计方案的正确性。

该锁相环的自由振荡频率可随输入信号频率的变化而改变,具有电路结构简单、锁相范围广、锁定速度快和稳态误差小等特点。

0 引言

锁相环是一个输出信号能够跟踪输入信号相位的闭环自动控制系统,由于其独特的优良性能,在通信、雷达、测量和自动化控制等领域得到极为广泛的应用。

全数字锁相环(ADPLL)相对于模拟锁相环具有可靠性高、参数稳定、易于集成等特点,因而得到了越来越广泛的研究,成为各种电子设备中必不可少的组成部件。

锁相环具有三个重要的性能指标:锁相范围、锁相速度和稳定性。

为提高锁相环的各项性能指标,一些学者进行了深入的分析和研究。

智能全数字锁相环的设计

智能全数字锁相环的设计智能全数字锁相环的设计摘要:在FPGA片内实现全数字锁相环用途极广。

本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智能配置,从而使锁相环快速进入锁定状态,在最短时间内正常工作并且提高输出频率的质量。

关键词:全数字锁相环数字环路滤波器数字单稳态振荡器1引言数字锁相环路已在数字通信、无线电电子学及电力系统自动化等领域中得到了极为广泛的应用。

随着集成电路技术的发展,不仅能够制成频率较高的单片集成锁相环路,而且可以把整个系统集成到一个芯片上去。

在基于FPGA的通信电路中,可以把全数字锁相环路作为一个功能模块嵌入FPGA中,构成片内锁相环。

锁相环是一个相位误差控制系统。

它比较输入信号和振荡器输出信号之间的相位差,从而产生误差控制信号来调整振荡器的频率,以达到与输入信号同频同相。

所谓全数字锁相环路(DPLL)就是环路部件全部数字化,采用数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)构成的锁相环路,其组成框图见图1示。

当锁相环中的鉴相器与数控振荡器选定后,锁相环的性能很大程度依赖于数字环路滤波器的参数设置。

2K计数器的参数设置74297中的`环路滤波器采用了K计数器。

其功能就是对相位误差序列计数即滤波,并输出相应的进位脉冲或是借位脉冲,来调整I/D数控振荡器输出信号的相位(或频率),从而实现相位控制和锁定。

K计数器中K值的选取需要由四根控制线来进行控制,模值是2的N次幂。

在锁相环路同步的状态下,鉴相器既没有超前脉冲也没有滞后脉冲输出,所以K计数器通常是没有输出的;这就大大减少了由噪声引起的对锁相环路的误控作用。

也就是说,K计数器作为滤波器,有效地滤除了噪声对环路的干扰作用。

显然,设计中适当选取K值是很重要的。

K值取得大,对抑止噪声有利(因为K值大,计数器对少量的噪声干扰不可能计满,所以不会有进位或借位脉冲输出),但这样捕捉带变小,而且加大了环路进入锁定状态的时间。

一种新型PID控制的全数字锁相环的设计与实现.

一种新型PID控制的全数字锁相环的设计与实现锁相环是一种能够跟踪输入信号相位的闭环自动控制系统,广泛应用于信号处理、时钟同步、倍频、频率综合等领域。

它根据输入信号和反馈信号的相位差来调整压控振荡器的输出频率,最终达到输入信号频率和输出信号频率相等,输入信号和输出信号保持恒定的相位差。

传统的PI控制器可以消除稳态误差,保证锁定精度,但是对阻尼有不利影响。

在PI控制器中引入微分项可以改善响应速度和阻尼,保证了锁定时间,但不能减少稳态误差,因此本文提出积分分离PID控制,能够大大改善响应时间和阻尼并减少稳态误差,从而保证了锁相精度和锁相时间。

1 电路结构与工作原理1.1 全数字锁相环电路结构快速全数字锁相环的系统框图如图1所示。

鉴相器采用JK触发器,该鉴相器结构简单,鉴相范围为±π,能够满足一般工程的需要。

由于鉴相器输出的是二值高低脉冲,后需接数字滤波器来平滑其中的起伏,消除噪声和干扰脉冲的影响。

一般数字序列滤波器有两种:N 先于M序列滤波器和随机徘徊滤波器,数字滤波器不是环路滤波器,它是无惰性的,加在环路中不影响环路的阶数,仅起到滤噪抗干扰的作用。

本文采用随机徘徊滤波器。

环路滤波器采用PID控制器,能够很好地控制环路相位校正的速度和精度,相对于文献[1]的PI控制器具有更好的特性。

数字压控振荡器采用可变模的分频器。

M分频器对输出信号进行分频,以使环路得到相应的倍频信号。

1.2 电路工作原理鉴相器比较输入信号和输出信号的相位差,产生一误差高低电平脉冲序列pha。

该脉冲的宽度和输入、输出信号的相位误差是成比例的。

K序列滤波器对相位误差信号进行量化,又可以消除输入信号噪声和干扰脉冲的影响。

当pha为高电平时,K序列滤波器对fO进行加计数,当计数器溢出时,一方面向环路滤波器产生一加脉冲i,同时对计数器进行复位,重新计数。

相反,当pha 为低电平时,K序列滤波器对fO进行减计数,当计数器减为零时,一方面向环路滤波器产生一减脉冲d,同时对计数器进行复位,重新计数。

全数字锁相环的VHDL设计【开题报告】

开题报告专业:电子信息工程全数字锁相环的VHDL设计一、综述本课题国内外研究动态,说明选题的依据和意义锁相技术是一种实现相位自动控制的方法,是专门研究相位的技术。

利用锁相技术得到的锁相环PLL是一个闭环的相位自动控制系统,它的输出信号能够自动跟踪输入信号的相位变化,也可以将之称为一个相位自动跟踪系统,它能够自动跟踪两个信号的相位差,并且靠反馈控制达到自动调节输出信号相位的目的。

锁相环的研究一直是学术界的一个研究重点,由于条件所限,国内对于锁相环的研究主要停留在理论方面,高性能锁相环的产品基本基本依赖进口。

而在国外,锁相环技术则在不断发展,从最初采用分离器件到采用集成电路,从采用双极工艺到使用CMOS 工艺,从需要挂电阻和电容到锁相环完全集成在一块芯片上,并且作为嵌入式IP核应用在大的数字系统中。

随着ASIC芯片电源电压下降,使得电源电压与核心薄氧化器件的阈值电压相比裕量有限从而使模拟电路设计,尤其是低噪声低电压锁相环的设计变得非常困难。

因而,当前锁相环的设计关键集中在高速、低电压、低噪声方面。

目前国外的锁相环产品大多采用3.3V电源电压的CMOS工艺,工作频率可从100MHz一直达到2.4GHz,输出噪声(周期到周期)在几十皮秒左右。

VHDL语言的英文全写是:VHSIC(Very High Speed Integrated Circuit)Hardware Description Language.翻译成中文就是超高速集成电路硬件描述语言。

因此它的应用主要是应用在数字电路的设计中。

其是一种行为描述语言, 其编程结构类似于计算机中的C 语言, 在描述复杂逻辑设计时, 非常简洁,具有很强的逻辑描述和仿真能力,是未来硬件设计语言的主流。

基于VHDL 语言的数字锁相环设计,不仅简化了硬件的开发和制作过程,而且使硬件体积大大减小,并提高了系统的可靠性。

该方法可以在不修改硬件电路的基础上,通过修改设计软件、更改移相范围就可满足不同用户的需要。

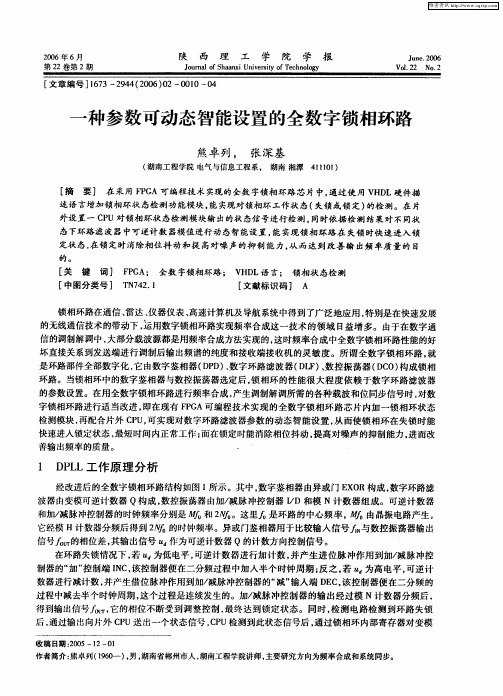

一种参数可动态智能设置的全数字锁相环路

锁 相环路 在通 信 、 雷达 、 器仪 表 、 仪 高速计 算机及 导航 系统 中得 到 了广泛 地应 用 , 特别是 在 快速发 展 的无线通 信技 术 的带动 下 , 运用 数字 锁相 环路 实现 频率 合成 这一 技 术 的领 域 日益 增 多 。 由于在 数 字通

信的调制解调中 , 大部分载波源都是用频率合成方法实现的, 这时频率合成中全数字锁相环路性能的好 坏直 接关 系到发 送端 进行 调 制后输 出频谱 的纯度 和 接 收端接 收 机 的灵 敏 度 。所 谓 全 数 字锁 相环 路 , 就 是环路部件全部数字化 , 它由数字鉴相器( P )数字环路滤波器( L ) 数控振荡器 ( C ) DD 、 DF、 D O 构成锁相 环路。当锁相环中的数字鉴相器与数控振荡器选定后 , 锁相环的性能很 大程度依赖于数字环路滤波器 的参数设 置 。在用 全数 字锁 相环 路 进行 频率合 成 , 生调 制解 调所需 的各种 载波 和位 同步 信号 时 , 产 对数

定状 态 , 在锁 定 时 消除相 位抖 动和 提 高对 噪 声 的抑 制 能 力 , 而 达 到 改善 输 出频 率质 量 的 目 从

的。

[ 关

键

词] F C P A; 全数 字锁相 环路 ; Vt L语 言 ; 锁 相状 态检 测 ID [ 献标识 码 ] A 文

[ 中图分类 号 ] T 72 1 N 4 .

善输 出频率 的质量 。 .

1 DL P L工 作 原 理 分 析

经改进后的全数字锁相环路结构如图 1 所示。其中, 数字鉴相器由异或门 E O X R构成 , 数字环路滤

波器 由变模 可逆计 数 器 Q构成 , 控振 荡器 由J/ 数 J 减脉 冲控 制器 LD和 模 N 计数 器 组 成 。可 逆计 数 器 n / 和J/ J 减脉 冲控制器 的时钟 频率 分别 是 M o 2f。这里 是 环路 的 中心频 率 , f n f 和 No M o由晶振 电路 产生 , 它经模 H计 数器 分频后 得 到 2 f No的时 钟频 率 。异 或 门鉴相器 用 于 比较 输 入信 号 与数控 振 荡器 输 出

一种新型的全数字锁相环

一种新型的全数字锁相环[ 来源:机电论文 | 类别:技术 | 时间:2006-3-11 16:33:27 ][字体:大 中 小]原作者:庞 浩,俎云霄,王赞基 原作者出处:(清华大学电机工程与应用电子技术系,北京,100084) 出处【论文摘要】该文提出了一种实现全数字锁相环的新方法。

在基于该方法实现的全数字锁相环中,一种 论文摘要 论文摘 数字比例积分控制的设计结构取代了传统的一些数字环路滤波控制方法。

通过线性近似,该文推导出该 锁相环系统的数学模型,并进一步对该系统的局部动态特性进行了讨论。

理论分析表明这种新型的全数 字锁相环具有很宽的锁相范围,并且在不同被锁频点的局部范围内都具有相同的稳定形式,锁相跟踪达 到稳定的时间与被锁信号的周期成正比。

由于充分利用了鉴相脉冲宽度所包含的相位误差信息,同时又 引入了积分控制,使锁相环的跟踪响应速度得到提高。

仿真实验进一步验证了理论分析的结论。

该文锁 相环采用数字电路方式实现,其性能可以通过比例和积分控制参数进行调节,因而简化了设计过程,便 于应用在电机调速系统、有源滤波器和静止无功补偿器等领域。

1 引言 信号锁相技术广泛应用于自动化控制等领域。

利用该技术可以产生同步于被锁输入信号的整数倍频或 者分数倍频的输出控制信号。

锁相环的基本结构是由鉴相、环路滤波、可控振荡器和 M 倍分频等模块组 成的一个反馈环路,如图 1 所示。

输入的被锁信号首先与同步倍频信号经过 M 倍分频后产生的锁相信号 进行鉴相处理,输出相位误差信号。

环路滤波模块通常具有低通特性,它将相位误差信号转化为稳定的 控制信号,从而控制可控振荡器模块,产生稳定的频率信号输出。

这个频率信号就是所需的同步倍频信 号。

如果整个反馈环路锁相稳定, 锁相环输出的同步倍频信号的频率就是其输入的被锁信号频率的 M 倍。

假如被锁信号在输入鉴相模块之前又先被分频了 L 倍,则锁相获得的同步倍频信号的频率就是被锁信号频率的 M/L 倍。

全数字锁相环的设计及分析

全数字锁相环的设计及分析1 引言锁相环是一种能使输出信号在频率和相位上与输入信号同步的电路,即系统进入锁定状态(或同步状态)后,震荡器的输出信号与系统输入信号之间相差为零,或者保持为常数。

传统的锁相环各个部件都是由模拟电路实现的,一般包括鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)三个环路基本部件。

随着数字技术的发展,全数字锁相环ADPLL(AllDigital Phase-Locked Loop)逐步发展起来。

所谓全数字锁相环,就是环路部件全部数字化,采用数字鉴相器、数字环路滤波器、数控振荡器构成锁相环路,并且系统中的信号全是数字信号。

与传统的模拟电路实现的锁相环相比,由于避免了模拟锁相环存在的温度漂移和易受电压变化影响等缺点,从而具备可靠性高、工作稳定、调节方便等优点。

全数字锁相环的环路带宽和中心频率编程可调,易于构建高阶锁相环,并且应用在数字系统中时,不需A/D及D/A转换。

在调制解调、频率合成、FM立体声解码、图像处理等各个方面得到广泛的应用。

随着电子设计自动化(EDA)技术的发展,可以采用大规模可编程逻辑器件(如CPLD或FPGA)和VHDL语言来设计专用芯片ASIC和数字系统。

本文完成了全数字锁相环的设计,而且可以把整个系统嵌入SoC,构成片内锁相环。

2全数字锁相环的体系结构和工作原理74XX297 是出现最早,应用最为广泛的一款全数字锁相环,在本文中以该芯片为参考进行设计、分析。

ADPLL基本结构如图1所示,主要由鉴相器、K变模可逆计数器、脉冲加减电路和除N计数器4部分构成。

K变模计数器和脉冲加减电路的时钟分别为Mfc和2Nfc。

这里fc是环路中心频率,一般情况下M和N都是2的整数幂。

2.1 鉴相器常用的鉴相器有两种类型:异或门(XOR)鉴相器和边沿控制鉴相器(ECPD)。

异或门鉴相器比较输入信号Fin相位和输出信号Fout相位之间的相位差θe,并输出误差信号Se作为K变模可逆计数器的计数方向信号。

一种锁定相位编程可调全数字锁相环设计

一种锁定相位编程可调全数字锁相环设计李建伟1,徐红兵1,王 毅2(1.电子科技大学自动化工程学院 四川成都 610054;2.北京伽略电子系统技术有限公司 北京 100081)摘 要:在介绍经典全数字锁相环(DPLL )结构与工作原理的基础上,提出了一种可实现输出信号与输入信号多相位锁定的全数字锁相环路设计,详细介绍了设计思路、结构及工作原理。

设计采用Verilog 硬件描述语言描述,进行了计算机仿真、现场可编程逻辑器件(FP GA )实现和系统板级实验,证明了设计的可行性。

关键词:全数字锁相环;多相位;现场可编程逻辑器件;Verilog中图分类号:TP273 文献标识码:B 文章编号:1004373X (2007)0308403A Design of Locked Phase Programmable DPLLL I Jianwei 1,XU Hongbing 1,WAN G Y i 2(1.School of Automation Engineering ,University of Electronic Science &Technology of China ,,Chengdu ,610054,China ;2.Beijing G alleric Electronics L td.,Beijing ,100081,China )Abstract :At first ,the paper introduces the structure and theory of typical All Digital Phase Locked Loop (ADPLL ).Then it proposes a new design of ADPLL which can lock the input signals and output signals at multiple phase.It describes the de 2sign clue ,structure and principle of the system.Verilog hardware description language is used to describe the puter simulation ,FP GA implementation and system board test all prove that the design is feasible.K eywords :ADPLL ;multiple phase ;FP GA ;Verilog收稿日期:200607251 引 言锁相技术在信号处理、调制解调、时钟同步、倍频、频率综合等领域都得到了广泛的应用。

数字锁相环的参数设计及其应用

$/"

/D

$/4

/ !#

$/K $/I $

/J

$ / !$ $ / !" $

/ !K

[ ]

{

$/4

$ / !J

可以化成 式( 4) !# & ! $

( #

可见, 二者是基本一致的。

( # " # " # ( #

! [ $ ! % ! & (’! % ’ ] $) ’*+ ! % ’!’*+ ! ( !# )

等效噪声带宽、 最小相位均方误差以及最短锁定时间三种意义上的参数优化设计方案, 并给出了简 明的、 具有一定工程指导意义的结果。该结果在应用了 >,035 公司解调芯片 ?2@= A "!#B 的系统中获 得了具体应用。 【 关键词】 数字锁相环 等效噪声带宽

!"# $%&%’#(#& )#*+,- ./ ("# )+,+(%0 $"%*# 1.23 1..4 %-5 6(* 7440+2%(+.!" #$ %&’() *$(+"( %&’() ,$’+"( !"- .’(/0( 1-() 20(3’8 ?4/,64/- C-/&0&,6 D,-E3F1-07( ?4/,64/- "###9# :

"##! 年第 $ 期 总第!"#期

通

信

技

术

%&’ $(

"##!

)&**+,-./0-&,1 23.4,&5&67

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PDF 文件使用 "pdfFactory Pro" 试用版本创建

第 30 卷 第 13 期

电网技术

83

实验和仿真研究表明,KA 主要影响 EPLL 对幅 值的跟踪特性,当 KA 增大时,输出幅值信号的波 动变大,稳定性变差。但幅值响应和跟踪速度加快。 Kp,Ki 主要影响 EPLL 对频率的跟踪特性,Kp 主要 影响对频率比例分量的跟踪,Ki 主要影响对频率积 分分量的跟踪,当 Kp,Ki 增大时,频率跟踪的稳定 性变差,但频率跟踪的速度加快。 2.2 动态参数调节方法

关键词:全数字锁相环;动态参数调节;同步;数字逻辑电路

0 引言

数字锁相环在电力系统自动化、无线电电子学 及数字通信等领域应用广泛。传统的依据过零检测 实现的全数字锁相环[1-4]锁相速度慢,且过零点的扰 动会直接影响锁相精度。另外,其多采用微处理器 和数字信号处理器(digital signal processing,DSP)实 现[5-8],较大程度地依赖于处理器性能,相位精度受 中断响应和指令执行时间影响,因此传统的全数字 锁相环无法应用于触发脉冲等实时控制场合。基于 模数转换电路(analog to digital convert,ADC)和现场 可编程门阵列(field programmable gate array,FPGA)

ABSTRACT: An all-digital enhanced phase-lock loop (EPLL) technology based on ADC and FPGA is designed, On the basis of principle of trajectory tracking EPLL realizes the synchronization with AC fundamental harmonic component, the phase-lock speed of EPLL is rapid and its accuracy is satisfactory. To meet the design requirement of phase-lock speed and stability simultaneously, a new method to adjust dynamic parameters of EPLL is put forward, thus an all-digital phase-lock logical circuit with optimized structure is obtained. The results of phase-lock tracking test verify the performance of EPLL, and the effectiveness of EPLL in harmonics extraction and analysis is confirmed.

实现的高性能数字锁相环成为当前锁相同步技术研 究的重点。该新型锁相技术充分利用信号波形本身 所包含的相位信息,提高了相速度和性能,同时基 于FPGA逻辑电路,实时性强,便于应用。近年来 Karimi和Ziarani提出了改进的数字锁相环(enhanced phase-lock loop,EPLL)方法[9-10]。仿真和实验表明, 该方法能跟踪被锁信号变化,有效滤除谐波和噪声 等干扰,并提供基波幅值、频率和瞬时相位的测量 结果,在测量精度上比传统的模拟锁相环法[11]更精 确。本文实现了该方法的逻辑电路模块化设计,并 通过研究控制参数对锁相性能的影响,提出一种动 态参数调节的新型控制方法。

设系统输出信号为 y(t) = Aˆ sinφˆ 。用e(t)表示输

入信号和输出信号的差,即 e(t) = x(t) − y(t) 。定义

状态向量θ = (Aˆ,ωˆ,φˆ) ,状态向量中各个状态参数分

别代表输入信号的基波幅值、频率和相位测量值,

则EPLL锁相算法由如下微分方程[12]来描述:

&Aˆ = u1e(t)sinφˆ

相对独立的逻辑电路,可以同时并行计算。

2 EPLL 的动态参数调节

2.1 EPLL 的参数特性 KA、KP、K i 是影响 EPLL 性能的 3 个参数。设

输入信号为频率 f0=50Hz,幅值 A=5V 的方波,并 计从施加信号到相位误差小于 1°的时间为测得的 锁相收敛时间。当 KA=32、KP=64、Ki=204 8 时, 系统收敛时间为 44 个周波。稳态时,幅值测量最 大相对误差为 1.7%,角频率测量最大相对误差为 6.1%。当 KA=128、KP=256、Ki=819 2 时,系统收 敛时间为 8 个周波。稳态时,幅值测量最大相对误 差为 6.3%,角频率测量最大相对误差为 57.6%。

将 e(t)·cosφ(t)作为鉴相器的输出,经环路滤波器得 到角频率信号ω (t)。这里 KA = u1 , Kp = u2u3 Aˆ , Ki = u2 Aˆ ,其中 KA 是鉴相器的积分控制参数,KP 和 Ki 分别是环路滤波器的比例控制参数和积分控制参 数。可控振荡器通过对ω (t)积分实现,其输出相位φ (t) 反馈回鉴相器,从而构成整个系统。

首先依据输入输出信号的差 e(t)判断输入信号 的基波突变和锁相基本稳定的状态。以 e(t)的周期 平均值 e 与设定阈值 e0 的比较结果为判定条件。当 e <e0 时,则判定锁相基本达到稳定,反之,则判 定输入信号的基波发生突变,锁相尚未达到稳定。 e0 的选取受系统敏感程度的影响很大,因此应根据 不同的应用要求进行选取。锁相基本稳定时的控制 参数为 KA0,KP0,Ki0。当锁相尚未稳定时,令 KA = µAKA0e / e0 , Kf = µf KP0e / e0 , Ki = µiKi0e / e0 。其 中 µA , µP , µi 为常数。所以,当系统处于锁相稳定状 态时,控制参数相对较小,系统抗干扰性能强,跟 踪过程较稳定;当系统处于锁相尚未稳定的状态 时,控制参数的取值相对较大,锁相跟踪速度快, 可快速收敛到新的稳定状态。

X-寄存器

Y-寄存器

Z-寄存器 i

移位

移位

表θ i

i 加减法

加减法

加减法 ±

±

图 2 CORDIC 算法状态机图

Fig. 2 State machine of the CORDIC arithmetic

为实现 EPLL 整体算法,本文采用状态机控制方 式分步计算,使逻辑资源充分优化。每次采样数据完

成,依照状态变量,按照相应的迭代运算步骤进行运

为实现数字化 EPLL 锁相方法,将式(1)~式(3)

改写为如下差分方程,式中 Fs 为采样频率。

eˆ(k) = x(k) − y(k)

(4)

Aˆ(k + 1)= KAeˆ(k )sinφˆ(k ) + Aˆ(k )

(5)

Fs

ω&ˆ p (k + 1) = K peˆ(k) cosφˆ(k)

(6)

ωˆi

描述的基波信号。这表明 EPLL 算法会自动跟踪输

入信号的基波分量。此外,x(t)的参数幅值、角频率、

相角变化是系统允许的,滤波器输出 y(t)能跟随这

些参数变化,并较快地收敛到新的稳定状态。EPLL

具有以下的优点:

(1)输出信号 y(t)与输入信号 x(t)保持一致,

且与输入信号的基波分量同步,y(t)与 x(t)之间没有

算,最终输出结果。EPLL 程序流程图如图 3 所示。

开始

结构参数及锁相 控制参数设置

由式(5)计算 e(t),并送至行锁相 状态判断模块及动态参数调节模块

计算和输出 A(t)和 y(t)

AD 采样完成? Y N

由式(7)和式(8)计算输出ω (t), 并送至并行的确良可控震荡器模块

图 3 EPLL 程序的流程图

第 30 卷 第 13 期 2006 年 7 月

文章编号:1000-3673(2006)13-0081-04

电网技术 Power System Technology

中图分类号:TM715

文献标识码:A

Vol. 30 No. 13 Jul. 2006

学科代码:470·4054

新型全数字锁相环的逻辑电路设计

(k

+ 1)

=

Kieˆ(k) cosφˆ(k Fs

+ 1)

+

ωˆi

(k)

(7)

φˆ(k +1) = ω&ˆ p (k +1) + ωˆi (k +1) + φˆ(k ) (8) Fs

1.3 EPLL 的实现 本文根据图 1 的数字锁相环结构框图,用硬件

描述语言(hardware description language,VHDL)描 述该系统,并在 FPGA 中实现。本文采用基于坐标 系 旋 转 的 数 字 式 计 算 方 法 [13](coordinate rotation digital computer,CORDIC)实现三角函数运算,其 状态机设计如图 2 所示。

相位误差。

(2)可实时测量输入信号 x(t)基波分量的幅

值、相位、角频率。

(3)对内部参数和外部噪声均具有鲁棒性。

(4)可以通过调整其内部控制参数控制收敛

速度、稳定状态等。

Байду номын сангаас

1.2 EPLL 的结构

根据式(1)~ (3),按锁相环的一般结构整理出实 现 EPLL 的结构框图[12],见图 1。

鉴相器

环路滤波器 可控振荡器

电力系统同步控制对锁相性能的要求包括 2 个 方面:当输入信号的幅值、相位、频率发生改变时, 锁相系统能快速做出反应,并迅速收敛到新的稳定 状态,即要求锁相系统敏感,且有较快的收敛速度; 当输入信号的基波比较稳定,则锁相系统应能有效 滤除谐波和噪声的干扰,具有很好的稳定性。对 EPLL 参数特性的研究表明,单一的控制参数无法 同时满足锁相速度和锁相稳定性的要求。为此,本 文提出对控制参数进行动态调节的方法,以改善 EPLL 的锁相性能。