串行输入并行输出

74ls164

74LS164简介74LS164是一种8位串行输入/并行输出移位寄存器,广泛应用于数字电子领域。

它由TI(Texas Instruments)公司制造,是74系列(TTL)的一员。

功能74LS164具有以下主要功能:•8位位移寄存器:可以将8位数据进行位移操作,并将结果存储在内部存储器中。

•串行输入:通过一个输入引脚,可以逐位地输入8位数据。

•并行输出:通过8个输出引脚,可以同时输出寄存器中存储的8位数据。

引脚描述74LS164具有如下引脚:1.DS(Data Serial Input):串行数据输入引脚,用于输入通过位移操作需要存储的8位数据。

2.SHCP(Shift Clock Input):移位时钟输入引脚,用于控制位移操作的时钟信号。

3.STCP(Storage Clock Input):存储时钟输入引脚,用于控制存储数据的时钟信号。

4.GND(Ground):接地引脚。

5.Q7’(Serial Output):串行输出引脚,用于输出移位操作的结果。

6.Q0-Q6(Parallel Outputs):并行输出引脚,用于输出存储的8位数据。

7.VCC(Positive Supply):正电源引脚。

工作原理74LS164工作时,可以通过两个时钟信号控制其行为。

下面是其工作原理的描述:•存储器清零:在存储器清零时,将SHCP和STCP引脚设置为高电平,并将DS引脚设置为低电平。

此时,存储器中所有的输出引脚将保持低电平状态。

•位移操作:在进行位移操作时,将SHCP引脚设置为低电平,然后将输入引脚DS设置为要输入的数据位状态(0或1)。

接下来,通过将SHCP 引脚设置为高电平,使得数据在寄存器内进行位移,具体移位方向取决于输入引脚DS的状态。

重复进行8次位移操作,即可完成8位数据的输入。

•存储数据:要将位移操作的结果存储在内部存储器中,需要控制STCP引脚的信号。

当所有位移操作完成后,将STCP引脚设置为高电平,将移位结果存储在寄存器中。

74HC165功能说明

74HC165功能说明

1.并行输入:74HC165具有8个并行输入引脚(A-H),可以同时读取8个输入信号。

这些输入信号可以是数字信号,也可以是模拟信号。

2.串行输出:74HC165具有串行输出引脚(QH),它可以将输入信号转换为串行输出信号。

输出信号的顺序与输入信号的读取顺序相同。

3.移位操作:74HC165可以通过移位操作来读取并且存储输入信号。

移位操作可以由一个时钟信号(SH/LD)和一个时钟使能信号(CLKINH)来控制。

当时钟使能信号为高电平时,移位操作生效;当时钟使能信号为低电平时,移位操作被禁止。

4.并行加载:除了移位操作之外,74HC165还可以通过并行加载操作来读取并存储输入信号。

并行加载操作可以通过时钟使能引脚(CLKINH)和并行加载引脚(PL)来控制。

当时钟使能引脚为高电平时,同时并行加载引脚为高电平,即可进行并行加载操作。

5.级联操作:多个74HC165芯片可以级联在一起,以扩展输入信号的数量。

级联操作可以通过级联引脚(SERA/B)和级联输出引脚(QH)来实现。

级联引脚可以将一个74HC165的输出连接到另一个74HC165的输入,以实现数据的串行传输。

总结起来,74HC165是一种用于将8个并行输入信号转换为串行输出信号的移位寄存器芯片。

它通过移位操作和并行加载操作来读取并存储输入信号,并且可以通过级联操作扩展输入信号的数量。

这种芯片在数字电路控制和数据采集等应用中非常常见,具有广泛的用途。

2.4.1 并行输入串行输出

2.4.1 并行输入串行输出移位寄存器实验1.步骤:(1)新建工程SHIFT8R;(2)新建VHDL文件SHIFT8R.vhd,编写程序如下:--带有同步并行预置功能的8位右移移位寄存器:SHIFT8R.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY SHIFT8R ISPORT( CLK , LOAD : IN STD_LOGIC ; --CLK是移位时钟信号、LOAD是并行数据预置使能信号DIN : IN STD_LOGIC_VECTOR(7 DOWNTO 0); --DIN是8位并行预置数据端口QB : OUT STD_LOGIC ); --QB是串行输出端口END ENTITY SHIFT8R;ARCHITECTURE BEHAV OF SHIFT8R ISBEGINPROCESS(CLK,LOAD)VARIABLE REG8 : STD_LOGIC_VECTOR( 7 DOWNTO 0);BEGINIF CLK'EVENT AND CLK='1' THENIF LOAD='1' THENREG8 := DIN; --装载新数据ELSEREG8(6 DOWNTO 0):= REG8(7 DOWNTO 1);-- 此语句表明:一个时钟周期后将上一时钟周期移位寄存器中的高7位-- 二进制数赋给此寄存器的低7位END IF;END IF;QB <= REG8(0);END PROCESS; -- 输出最低位END ARCHITECTURE BEHAV;(3)保存后编译;(4)新建波形图SHIFT8R.vwf,编辑输入波形;(5)进行功能仿真;(6)进行时序仿真;(7)资源分配;(8)编译后,生成可以配置到CPLD的POF文件。

2.功能仿真结果及分析:输入:DIN[7:0]8为并行输入信号输出:QB为串行输出信号控制:CLK为时钟信号LAOD并行数据预置使能信号(1)功能仿真:波形分析:LOAD=1,CLK=1,输入并行信号“01001101”LOAD=0,每输入一个脉冲,右移一位并从QB 端输出,依次为“01001101” 因此,该设计可以实现并行输入串行输出的右移移位功能。

寄存器实验报告

寄存器实验报告一、实验目的1. 了解寄存器的分类方法,掌握各种寄存器的工作原理;2. 学习使用Verilog HDL 语言设计两种类型的寄存器。

二、实验设备PC 微机一台,TD-EDA 实验箱一台,SOPC 开发板一块。

三、实验内容寄存器中二进制数的位可以用两种方式移入或移出寄存器。

第一种方法是以串行的方式将数据每次移动一位,这种方法称之为串行移位(Serial Shifting),线路较少,但耗费时间较多。

第二种方法是以并行的方式将数据同时移动,这种方法称之为并行移位(Parallel Shifting),线路较为复杂,但是数据传送的速度较快。

因此,按照数据进出移位寄存器的方式,可以将移位寄存器分为四种类型:串行输入串行输出移位寄存器(Serial In- Serial Out)、串行输入并行输出移位寄存器(Serial In- Parallel Out)、并行输入串行输出移位寄存器(Parallel In- Serial Out)、并行输入并行输出移位寄存器(Parallel In-Parallel Out)。

本实验使用Verilog HDL 语言设计一个八位并行输入串行输出右移移位寄存器(Parallel In- Serial Out)和一个八位串行输入并行输出寄存器(Serial In- Parallel Out),分别进行仿真、引脚分配并下载到电路板进行功能验证。

四、实验步骤1.并行输入串行输出移位寄存器实验步骤1). 运行Quartus II 软件,选择File New Project Wizard 菜单,工程名称及顶层文件名称为SHIFT8R,器件设置对话框中选择Cyclone 系列EP1C6Q240C8 芯片,建立新工程。

2.) 选择File New 菜单,创建Verilog HDL 描述语言设计文件,打开文本编辑器界面。

3.) 在文本编辑器界面中编写Verilog HDL 程序,源程序如下:module SHFIT8R(din,r_st,clk,load,dout);input [7:0]din;input clk,r_st,load;output dout;reg dout;reg [7:0]tmp;always @(posedge clk)if(!r_st)begindout<=0;endelsebeginif(load)begintmp=din;endelsebegintmp[6:0]=tmp[7:1];tmp[7]=0;enddout<=tmp[0];endendmodule4). 选择File Save As 菜单,将创建的VHDL 设计文件保存为工程顶层文件名SHIFT8R.V。

模式锁存触发电路设计任务说明习题解答

任务8.2模式锁存触发电路设计任务说明习题解答一、测试(一)判断题1、移位寄存器74LS194 可串行输入并行输出,但不能串行输入串行输出。

答案:F解题:并行送数功能。

当/CR=1,M1M0=11时,在上升沿作用下,D0~D3端输入的数码d0~d3并行送入寄存器。

当/CR=1、M1M0=01时,在上升沿作用下,DSR端输入的数码依次送入寄存器。

2、寄存器并行方式与串行方式比较,并行存取方式的速度比串行存取方式慢得多,而且所用的数据线要比串行方式多。

答案:F解题:寄存器并行方式与串行方式比较,并行存取方式的速度比串行存取方式快得多,但所用的数据线要比串行方式多。

3、寄存器能够把串行数据变成并行数据。

答案:T解题:寄存器能够把串行数据变成并行数据。

4、双向移位寄存器74LS194当/CR端输入低电平时,所有输出均为零。

答案:T解题:双向移位寄存器74LS194当/CR端输入低电平时,所有输出均为零。

5、数据锁存器74HC573的/OE引脚输入无效信号为高时,输出为高阻。

答案:T解题:数据锁存器74HC573的/OE引脚输入无效信号为高时,输出为高阻6.能存放二值代码的部件叫做寄存器。

寄存器按功能分为数码寄存器和移位寄存器。

数码寄存器只供暂时存放数码,可以根据需要将存放的数码随时取出参加运算或者进行数据处理。

移位寄存器不但可存放数码,而且在移位脉冲作用下,寄存器中的数码可根据需要向左或向右移位。

答案:T解题:能存放二值代码的部件叫做寄存器。

寄存器按功能分为数码寄存器和移位寄存器。

数码寄存器只供暂时存放数码,可以根据需要将存放的数码随时取出参加运算或者进行数据处理。

移位寄存器不但可存放数码,而且在移位脉冲作用下,寄存器中的数码可根据需要向左或向右移位。

7.从寄存器取出数码的方式也有并行输出和串行输出两种。

在并行输出方式中,被取出的数码在对应的输出端同时出现;在串行输出方式中,被取出的数码在一个输出端逐位输出。

通信协议简介及区别(串行、并行、双工、RS232等)

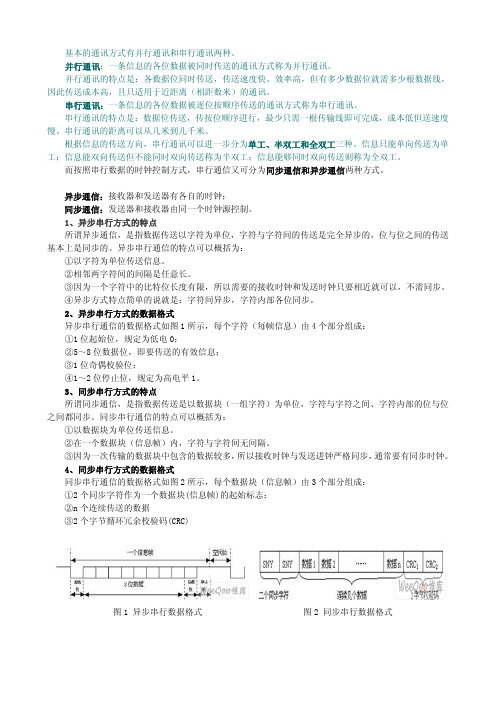

基本的通讯方式有并行通讯和串行通讯两种。

并行通讯:一条信息的各位数据被同时传送的通讯方式称为并行通讯。

并行通讯的特点是:各数据位同时传送,传送速度快、效率高,但有多少数据位就需多少根数据线,因此传送成本高,且只适用于近距离(相距数米)的通讯。

串行通讯:一条信息的各位数据被逐位按顺序传送的通讯方式称为串行通讯。

串行通讯的特点是:数据位传送,传按位顺序进行,最少只需一根传输线即可完成,成本低但送速度慢。

串行通讯的距离可以从几米到几千米。

根据信息的传送方向,串行通讯可以进一步分为单工、半双工和全双工三种。

信息只能单向传送为单工;信息能双向传送但不能同时双向传送称为半双工;信息能够同时双向传送则称为全双工。

而按照串行数据的时钟控制方式,串行通信又可分为同步通信和异步通信两种方式。

异步通信:接收器和发送器有各自的时钟;同步通信:发送器和接收器由同一个时钟源控制。

1、异步串行方式的特点所谓异步通信,是指数据传送以字符为单位,字符与字符间的传送是完全异步的,位与位之间的传送基本上是同步的。

异步串行通信的特点可以概括为:①以字符为单位传送信息。

②相邻两字符间的间隔是任意长。

③因为一个字符中的比特位长度有限,所以需要的接收时钟和发送时钟只要相近就可以,不需同步。

④异步方式特点简单的说就是:字符间异步,字符内部各位同步。

2、异步串行方式的数据格式异步串行通信的数据格式如图1所示,每个字符(每帧信息)由4个部分组成:①1位起始位,规定为低电0;②5~8位数据位,即要传送的有效信息;③1位奇偶校验位;④1~2位停止位,规定为高电平1。

3、同步串行方式的特点所谓同步通信,是指数据传送是以数据块(一组字符)为单位,字符与字符之间、字符内部的位与位之间都同步。

同步串行通信的特点可以概括为:①以数据块为单位传送信息。

②在一个数据块(信息帧)内,字符与字符间无间隔。

③因为一次传输的数据块中包含的数据较多,所以接收时钟与发送进钟严格同步,通常要有同步时钟。

74ls165工作原理

74ls165工作原理74LS165是一款逐位移位寄存器,它可以将8位的输入数据进行并行转换,输出到8位的串行数据线上。

下面我们来了解一下74LS165的工作原理。

让我们了解一下74LS165的引脚和功能。

引脚|功能-|-1|GND2A|串行数据输入2B|并行数据输入3|时钟输入4-11|并行数据输出12|输出使能13-16|电源电压1.并行数据输入与串行数据输入的选择在74LS165中,可以通过引脚2A和2B选择并行输入或串行输入。

当2A引脚被使能时,串行数据输入被禁用,只有并行数据输入被使用。

当2B引脚被使能时,串行数据输入被启用。

2.时钟输入时钟输入引脚(引脚3)接收到一个高电平脉冲时,输入的数据就会进行一次并行转换,然后被输出到串行数据线上。

3.并行数据输出在74LS165中,有8个并行数据输出引脚(引脚4-11),这些引脚输出并行转换后的8位数据。

当时钟输入引脚接收到高电平脉冲时,输入的数据被放入寄存器中,并且寄存器的输出被更新。

在74LS165中,也有一个串行数据输出引脚(引脚2A)。

这个引脚在并行输入模式下不起作用,但在串行输入模式下,输出的数据是串行输入的数据。

5.输出使能输出使能引脚(引脚12)用于控制输出数据。

当输出使能被禁用时,无法从并行数据输出引脚和串行数据输出引脚中读取数据。

除了了解74LS165的工作原理外,还有一些注意事项需要我们关注。

首先是和时钟的相关问题。

在使用74LS165时,时钟输入必须关注到其稳定性和精确度。

如果时钟信号不稳定或者精度不够,将会影响到转换数据的准确性和精度。

其次是和输入电平的相关问题。

对于74LS165,它的输入电平应该在规定范围之内,否则会对其正常工作产生影响。

当输入电平过高时,就会超出芯片的工作范围,导致器件失效。

而当输入电平过低时,芯片不能正常工作。

芯片的使用温度也需要注意。

74LS165的使用温度范围为0℃到70℃,如果超出这个范围,就会对芯片产生影响。

74ls164与单片机的串并转换(串转并-串进并出)

74ls164与单片机的串并转换(串转并\串进并出)

74LS164串转并实验本实验是用74LS164把输入的串行数转换成并行数输出,74LS164为串行输入并行输出移位寄存器,其引脚图及功能如下:

A、B:串行输入端;

QA~QH:并行输出端;

CLR:清零端,低电平有效;

CLK:时钟脉冲输入端,上升沿有效。

实验采用单片机串行工作方式0和P1端口两种方式串行输出数据。

串行口工作方式0时,数据为8位,从RXD端输出,TXD端输出移位信号,其波特率固定为Fosc/12。

在CPU 将数据写入SBUF寄存器后,立即启动发送。

待8位数据输完后,硬件将状态寄存器的TI位置1,TI必须由软件清零。

串行口工作方式0数据/时钟是自动移位输出,用P1端口输出数据时,要编程位移数据,每输出一个数据位,再输出一个移位脉冲。

内容及步骤:

本实验需要用到单片机最小系统(F1区)、十六位逻辑电平显示(I4区)和74LS164(G3区)。

1、选用89C51单片机最小应用系统模块,用八位数据线连接74LS164的并行输出JD5G 与十六位逻辑电平显示模块JD2I,将74LS164的串行输入端A/B(1和2脚)接到RXD 上,CLK接到TXD上,CLR接INT0。

2、用串行数据通信线连接计算机与仿真器,把仿真器插到模块的锁紧插座中,请注意仿真器的方向:缺口朝上。

3、打开KeiluVision2仿真软件,首先建立本实验的项目文件,接着添加TH23_74164.ASM 源程序,进行编译,直到编译无误。

4、全速运行程序,观察发光二极管亮灭情况,先右移动两次,再左移动两次,然后闪烁两次。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

串行出入并行输出寄存器实验1.步骤:

(1)新建工程SHIFT8

(2)新建VHDL文件,编写程序如下:

--串行输入并行输出寄存器:

LIBRARY IEEE;

USE Shift8 IS

PORT( DI ,CLK : IN STD_LOGIC;

DOUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY Shift8;

ARCHITECTURE BEHA OF SHIFT8 IS

SIGNAL TMP : STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

PROCESS(CLK)

BEGIN

IF(CLK'EVENT AND CLK='1') THEN

TMP(7)<=DI;

FOR I IN 1 TO 7 LOOP

TMP(7-I)<=TMP(8-I);

END LOOP;

END IF;

END PROCESS;

DOUT<=TMP;

END ARCHITECTURE BEHA;

(3)保存后编译;

(4)新建波形图,编辑输入波形;

(5)进行功能仿真;

(6)进行时序仿真;

(7)资源分配;

(8)编译后,生成可以配置到CPLD的POF文件。

2.功能仿真结果及分析:

输入:DI为串行输入信号

输出:DOUT[7:0]为并行输出信号

控制:CLK为时钟信号

(1)功能仿真

波形分析:DI串行输入“01010101”

DOUT[0:7]并行输出“01010101”

因此,该设计能够实现串行输出并行输出的功能。

(2)时序仿真

从波形图看出来,并行输出中两条相邻输出时间延迟为.

3.资源分配。