锁相环设计

锁相环电路设计

锁相环电路设计

锁相环电路是一种常见的电路设计,它可以用于信号的同步和频率的稳定。

锁相环电路的基本原理是将输入信号与参考信号进行比较,然后通过反馈控制来调整输出信号的相位和频率,使其与参考信号保持同步。

锁相环电路广泛应用于通信、雷达、测量等领域。

锁相环电路的基本组成部分包括相频检测器、环路滤波器、控制电压源和振荡器。

相频检测器用于将输入信号与参考信号进行比较,产生误差信号。

环路滤波器用于滤除误差信号中的高频成分,以保证系统的稳定性。

控制电压源根据误差信号的大小和方向来产生控制电压,用于调整振荡器的频率和相位。

振荡器则产生输出信号,其频率和相位受到控制电压的影响。

锁相环电路的设计需要考虑多个因素,如相频检测器的灵敏度、环路滤波器的带宽、控制电压源的响应速度等。

此外,还需要根据具体应用场景选择合适的振荡器类型和工作频率。

在实际应用中,锁相环电路的性能也受到环境温度、电源噪声等因素的影响,因此需要进行充分的测试和优化。

锁相环电路是一种重要的电路设计,它可以实现信号同步和频率稳定,广泛应用于通信、雷达、测量等领域。

在设计锁相环电路时,需要考虑多个因素,进行充分的测试和优化,以保证系统的性能和稳定性。

锁相环设计

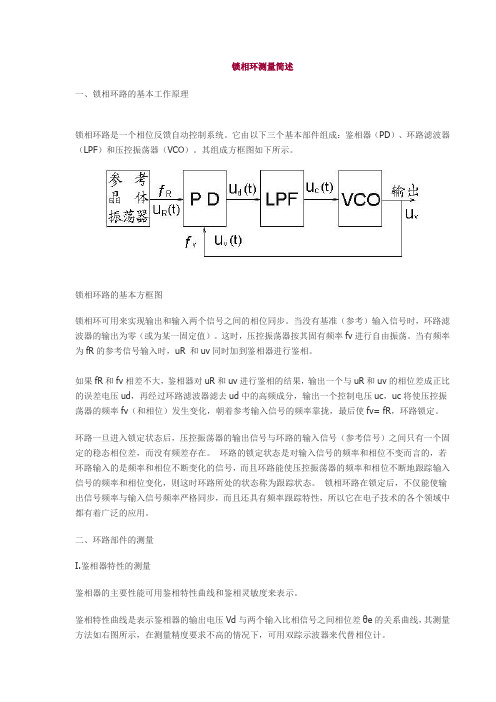

锁相环测量简述一、锁相环路的基本工作原理锁相环路是一个相位反馈自动控制系统。

它由以下三个基本部件组成:鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)。

其组成方框图如下所示。

锁相环路的基本方框图锁相环可用来实现输出和输入两个信号之间的相位同步。

当没有基准(参考)输入信号时,环路滤波器的输出为零(或为某一固定值)。

这时,压控振荡器按其固有频率fv进行自由振荡。

当有频率为fR的参考信号输入时,uR 和uv同时加到鉴相器进行鉴相。

如果fR和fv相差不大,鉴相器对uR和uv进行鉴相的结果,输出一个与uR和uv的相位差成正比的误差电压ud,再经过环路滤波器滤去ud中的高频成分,输出一个控制电压uc,uc将使压控振荡器的频率fv(和相位)发生变化,朝着参考输入信号的频率靠拢,最后使fv= fR,环路锁定。

环路一旦进入锁定状态后,压控振荡器的输出信号与环路的输入信号(参考信号)之间只有一个固定的稳态相位差,而没有频差存在。

环路的锁定状态是对输入信号的频率和相位不变而言的,若环路输入的是频率和相位不断变化的信号,而且环路能使压控振荡器的频率和相位不断地跟踪输入信号的频率和相位变化,则这时环路所处的状态称为跟踪状态。

锁相环路在锁定后,不仅能使输出信号频率与输入信号频率严格同步,而且还具有频率跟踪特性,所以它在电子技术的各个领域中都有着广泛的应用。

二、环路部件的测量I.鉴相器特性的测量鉴相器的主要性能可用鉴相特性曲线和鉴相灵敏度来表示。

鉴相特性曲线是表示鉴相器的输出电压Vd与两个输入比相信号之间相位差θe的关系曲线,其测量方法如右图所示,在测量精度要求不高的情况下,可用双踪示波器来代替相位计。

测得鉴相特性曲线之后,则根据的定义,可从Vd~θe曲线上求得鉴相灵敏度K.II.压控振荡器特性的测量压控振荡器的特性可用压控特性曲线和压控灵敏度来表示。

压控特性曲线是表示压控振荡器的输出频率fv与控制电压Vv之间的关系曲线。

锁相环设计

1.环路滤波电路我们采用有源比例积分器作为该锁相环的的环路滤波电路,并附加两级RC 滤波器以改善抖动转移特性。

过多的引入附加滤波器或者附加滤波器参数选择不当,都会导致环路参数复杂,不利于计算,从而导致环路不稳定。

环路滤波电路如下图:图2 环路滤波网络图中元器件选择:电阻采用0603封装,电容采用0805封装,U1选用RAIL-TO-RAIL 运算放大器LM6142BIM(3.3V 单电源供电)。

LM6142BIM 为双运放,为保证器件可靠工作,另外一个未用的运放要接成电压跟随器,并且注意电源的滤波,如下图:0.01C5L2图3 压随器和电源滤波2.环路参数计算对环路参数的选择,首先是把环路带宽Ωc 和阻尼系数ξ大致确定下来,Ωc 和ξ确定之后,环路滤波器的R 、C 的值就基本确定了。

这时更多考虑的是元件的容差,温度特性等等。

例如,环路中片状电容不宜大于1.8µF ,片状电容大于1.8µF 后,温度特性难以保证。

考虑到单板对155.52MHz 时钟抖动要求很高,而且在输入38.88MHz 基准时钟相位发生跳变(主备倒换时,相位有2ns 跳变)时,要求锁相环不能失锁,而是相位缓慢跟踪,所以初步选定环路带宽f c 为50Hz ;阻尼系数ξ为2。

采用理想积分滤波器的锁相环闭环传递函数可写作:H p p p p n nn n ()=+++22222ξωωξωω 式中,,为环路自然角频率。

ωτn K =1,为环路阻尼系数。

ξττ=212K为环路增益,K d 为鉴相灵敏度,K 0为压控灵敏度,N 为分频比。

K K K N d =a. 鉴相器鉴相灵敏度,V m 为鉴相器输出高低电平的差值,因为我们采K V d m=2π用3.3V 工作的FPGA ,V m 可取2.8V ,∴ k d = 2.82o=0.45V /radb. 压控灵敏度 k 0=2oD f vco D V vco∆f vco 为压控振荡器输出范围。

adisimpll锁相环设计过程

adisimpll锁相环设计过程锁相环(Phase-Locked Loop,PLL)是一种常用于时钟和信号恢复的电子电路。

它可以将输入信号的频率、相位和幅度与参考信号进行比较,然后通过调整其内部振荡器的频率和相位来保持与参考信号的同步。

在现代电子系统中,锁相环已成为许多应用的核心部件,例如通信系统、数据转换和数字信号处理等。

锁相环的设计过程通常包括以下几个主要步骤:1.确定锁相环的规格要求:首先需要确定系统的特定需求,包括输入和输出信号的频率范围、带宽、相位噪声要求以及抖动限制等。

这些规格要求将直接影响锁相环的设计参数和性能。

2.选择合适的锁相环架构:根据系统的特定需求,选择适合的锁相环架构。

常见的锁相环架构包括基于电压控制振荡器(Voltage-Controlled Oscillator,VCO)的基本锁相环、带自由运行振荡器(Free-Running Oscillator)的环-环(Ring-Oscillator)锁相环和数字控制振荡器(Digital-Controlled Oscillator,DCO)的混合锁相环等。

3.设计相位频率检测器:锁相环中的相位频率检测器(Phase-Frequency Detector,PFD)用于比较参考信号和反馈信号的相位和频率差异,并将其转化为控制信号。

常见的PFD电路包括EXOR门和带有多频偏的PFD等。

4.设计环路滤波器:设计环路滤波器用于平稳化锁相环的控制信号。

环路滤波器通常采用低通滤波器结构,能够滤除高频噪声和不稳定性。

5.设计振荡器:根据系统的频率范围和性能要求,设计合适的振荡器。

常见的VCO设计包括压控晶体振荡器(Voltage-Controlled Crystal Oscillator,VCXO)和频率可调振荡器(Voltage-Controlled Oscillator,VCO)。

6.设计控制电路:根据锁相环的设计需求,设计合适的控制电路。

集成电路锁相环及其应用电路设计.pptx

相位锁定。

wi

wo

wo

1

锁相环路基本组成方框图

第2页/共18页

压控振荡器

压控振荡器是一个电压-频率变换装置,在环路

中 作 为 被 控 振 荡 器 , 它 的 振 荡 频 率 应 随 输 入 控 制 电 ωV(t)

压 Uc(t) 线 性 地 变 化 ( 在 一 定 范 围 内 ) , 可 用 线 性

without frequency

offset).

8

固有振荡频率f第v9与页/共R181页,C1的关系

锁相环电路的应用

倍频:

i 鉴相器

i (t )

'

y

yn

环路 滤波器

分频器

÷n

压控 y

振荡器 y (t )

wi

wy n

9

wy nwi

第10页/共18页

锁相环电பைடு நூலகம்的应用

分频:

i 鉴相器

i (t )

方程来表示

即

ωV(t)=ωV + KV Uc(t)

当Uc(t)=0时,VCO的固有振荡频率为ωV 。

ωV

Uc(t)

wi

wo

wo

2

锁相环路基本组成方框图

第3页/共18页

wi

wo

wo

锁相环路基本组成方框图

输入信号和输出信号的相位关系

系统的瞬时相差θe(t)=θ1(t)-θ2(t)

3

第4页/共18页

wi wo

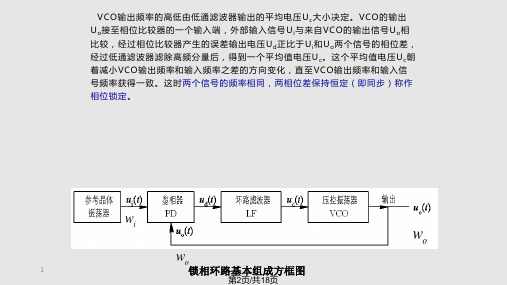

VCO输出频率的高低由低通滤波器输出的平均电压Uc大小决定。VCO的输出 Uo接至相位比较器的一个输入端,外部输入信号Ui与来自VCO的输出信号Uo相 比较,经过相位比较器产生的误差输出电压Ud正比于Ui和Uo两个信号的相位差, 经过低通滤波器滤除高频分量后,得到一个平均值电压Uc。这个平均值电压Uc朝 着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信

锁相环电路设计

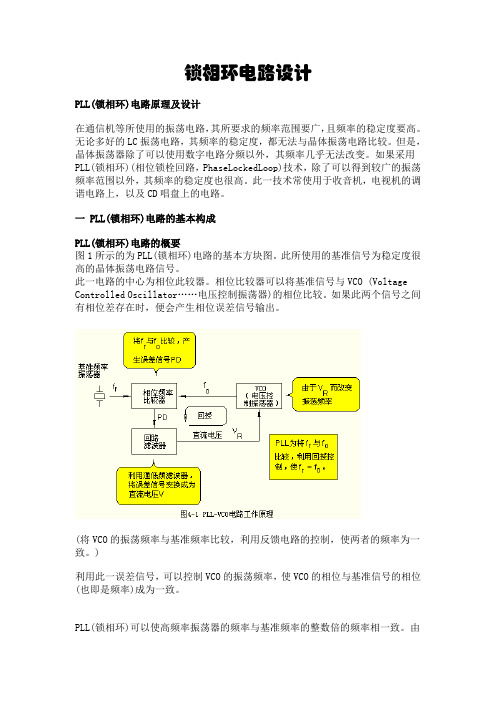

锁相环电路设计PLL(锁相环)电路原理及设计在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。

无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较。

但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。

如果采用PLL(锁相环)(相位锁栓回路,PhaseLockedLoop)技术,除了可以得到较广的振荡频率范围以外,其频率的稳定度也很高。

此一技术常使用于收音机,电视机的调谐电路上,以及CD唱盘上的电路。

一 PLL(锁相环)电路的基本构成PLL(锁相环)电路的概要图1所示的为PLL(锁相环)电路的基本方块图。

此所使用的基准信号为稳定度很高的晶体振荡电路信号。

此一电路的中心为相位此较器。

相位比较器可以将基准信号与VCO (Voltage Controlled Oscillator……电压控制振荡器)的相位比较。

如果此两个信号之间有相位差存在时,便会产生相位误差信号输出。

(将VCO的振荡频率与基准频率比较,利用反馈电路的控制,使两者的频率为一致。

)利用此一误差信号,可以控制VCO的振荡频率,使VCO的相位与基准信号的相位(也即是频率)成为一致。

PLL(锁相环)可以使高频率振荡器的频率与基准频率的整数倍的频率相一致。

由于,基准振荡器大多为使用晶体振荡器,因此,高频率振荡器的频率稳定度可以与晶体振荡器相比美。

只要是基准频率的整数倍,便可以得到各种频率的输出。

从图1的PLL(锁相环)基本构成中,可以知道其是由VCO,相位比较器,基准频率振荡器,回路滤波器所构成。

在此,假设基准振荡器的频率为fr,VCO的频率为fo。

在此一电路中,假设frgt;fo时,也即是VC0的振荡频率fo比fr低时。

此时的相位比较器的输出PD会如图2所示,产生正脉波信号,使VCO的振荡器频率提高。

相反地,如果frlt;fo时,会产生负脉波信号。

(此为利用脉波的边缘做二个信号的比较。

如果有相位差存在时,便会产生正或负的脉波输出。

分立锁相环设计与验证

锁相环一、实验原理许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成框图如图1所示。

)t图1 锁相环基本原理框图图1所示的是锁相环基本原理框图。

锁相环路是一种反馈控制电路,简称锁相环(PLL)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成u d(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压u c(t),对振荡器输出信号的频率实施控制。

锁相环法载波提取:当u i(t)为固定频率正弦信号(θi(t)为常数)时,在环路的作用下,VCO输出信号频率可以由固有振荡频率ωo(即环路无输入信号、环路对VCO无控制作用是VCO的振荡频率),变化到输入信号频率ωi,此时θo(t)也是一个常数,u d(t)、u c(t)都为直流。

称此为环路的锁定状态。

定义△ω=ω-ωo为环路固有的频率差,△ωp表示环路的捕捉带,△ωh表示环路的同步带,模拟锁相环中△ωp<△ωh。

当|△ωo|<△ωp时,环路可以进入锁定状态;当|△ωo|<△ωh时,环路也可以保持锁定状态;当|△ωo|>△ωp时,环路不能进入锁定状态,环路锁定后若△ωo发生变化使|△ωo|>△ωh,环路也不能保持锁定状态。

这两种情况下,环路都将处于失锁状态。

失锁状态下u d(t)是一个上下不对称的差拍电压,当|△ωi|>△ωo时,是u d(t)上宽下窄的差拍电压;反之,u d(t)是一个下宽上窄的差拍电压。

锁相环设计与MATLAB仿真

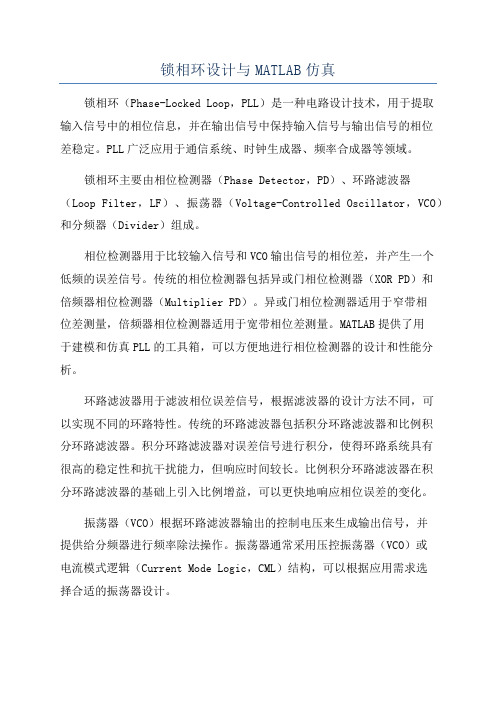

锁相环设计与MATLAB仿真锁相环(Phase-Locked Loop,PLL)是一种电路设计技术,用于提取输入信号中的相位信息,并在输出信号中保持输入信号与输出信号的相位差稳定。

PLL广泛应用于通信系统、时钟生成器、频率合成器等领域。

锁相环主要由相位检测器(Phase Detector,PD)、环路滤波器(Loop Filter,LF)、振荡器(Voltage-Controlled Oscillator,VCO)和分频器(Divider)组成。

相位检测器用于比较输入信号和VCO输出信号的相位差,并产生一个低频的误差信号。

传统的相位检测器包括异或门相位检测器(XOR PD)和倍频器相位检测器(Multiplier PD)。

异或门相位检测器适用于窄带相位差测量,倍频器相位检测器适用于宽带相位差测量。

MATLAB提供了用于建模和仿真PLL的工具箱,可以方便地进行相位检测器的设计和性能分析。

环路滤波器用于滤波相位误差信号,根据滤波器的设计方法不同,可以实现不同的环路特性。

传统的环路滤波器包括积分环路滤波器和比例积分环路滤波器。

积分环路滤波器对误差信号进行积分,使得环路系统具有很高的稳定性和抗干扰能力,但响应时间较长。

比例积分环路滤波器在积分环路滤波器的基础上引入比例增益,可以更快地响应相位误差的变化。

振荡器(VCO)根据环路滤波器输出的控制电压来生成输出信号,并提供给分频器进行频率除法操作。

振荡器通常采用压控振荡器(VCO)或电流模式逻辑(Current Mode Logic,CML)结构,可以根据应用需求选择合适的振荡器设计。

分频器用于将振荡器输出的高频信号按照设定的分频比例进行分频,生成与输入信号相位对齐的输出信号。

分频器采用计数器和锁存器设计,计数器用于记录输入信号的周期数,锁存器将计数器的值锁定在一个周期,输出给相位检测器进行相位比较。

锁相环的设计和仿真可以通过MATLAB工具箱进行。

首先,设计相位检测器的传输函数和特性,选择适当的相位检测器类型和设计参数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

频率范围:

锁相环能够锁定的频率范围,一般由VCO频率范围决定;

科

相位噪声:

锁相环输出信号的相位噪声,分为带内噪声和带外噪声;

学

锁定时间:

锁相环由当前稳定频点跳变并稳定在另一个频点所需要的时间;

频率步长:

锁相环能提供的最小频率分辨步长;

工作电流

电

所 究 分 研 S 山 子 CA E 昆 M 所 究 研 S 子 CA 电 E 微 IM 究 院 KS 研 学 子 CA 电 E 微 IM 院 KS

C

电

所 究 分 研 S 山 子 CA E 昆 M 所 究 研 S 子 CA 电 E 微 IM 究 院 KS 研 学 子 CA 电 E 微 IM 院 KS

电荷泵型整数分频锁相环

H open s I CP 2

I CP

D

Q

K vco CzC p N s s C z C p 1 sRz C C z p

学

充放电电流源的不匹配

器件不匹配; 电荷共享; 沟道长度调制;

Reference spur

V p

I CP , p

I CP

UP

I CP

Vtune

DW

Vn

I CP ,n

电

所 究 分 研 S 山 子 CA E 昆 M 所 究 研 S 子 CA 电 E 微 IM 究 院 KS 研 学 子 CA 电 E 微 IM 院 KS

KVCO s

p1 p 2

p1

p2

o 1 s2 VCO 1 K H s KVCO s s 2 PD LPF 1 1 n s p1 p2

电

所 究 分 研 S 山 子 CA E 昆 M 所 究 研 S 子 CA 电 E 微 IM 究 院 KS 研 学 子 CA 电 E 微 IM 院 KS

所 究 分 研 S 山 子 CA E 昆 M 所 究 研 S 子 CA 电 E 微 IM 究 院 KS 研 学 子 CA 电 E 微 IM 院 KS

锁相环设计

阴亚东

科

学

电

所 究 分 研 S 山 子 CA E 昆 M 所 究 研 S 子 CA 电 E 微 IM 究 院 KS 研 学 子 CA 电 E 微 IM 院 KS

TypeⅠ型锁相环

锁相环开环传递函数在原点只存在一个极点; 理论上对于固定频率输入,输入输出之间存在固定偏差;

i

K PD

科

学

H LPF ( S )

KVCO S

o

KVCO H open s K PD H LPF s S KVCO K H s PD LPF H open s i s o S lim s 2i s 0 s s K PD H LPF s KVCO K PD H LPF 0 KVCO i 1 H open s 1 K PD H LPF s KVCO S s e o i i s K PD H LPF s KVCO i

电

所 究 分 研 S 山 子 CA E 昆 M 所 究 研 S 子 CA 电 E 微 IM 究 院 KS 研 学 子 CA 电 E 微 IM 院 KS

为什么需要锁相环?

科

学

电

所 究 分 研 S 山 子 CA E 昆 M 所 究 研 S 子 CA 电 E 微 IM 究 院 KS 研 学 子 CA 电 E 微 IM 院 KS

H LPF ( S )

KVCO S

o

科

e,FD

学

N

KVCO K KVCO HLPF s VCO 1 s s s o REF FD PFD LPF KVCO KVCO KVCO KVCO VCO 1 KPDH LPF s 1 KPDH LPF s 1 KPDH LPF s 1 KPDH LPF s s s s s KPDH LPF s

以线性化模型分类:

TypleⅠ:理论上ΦREF与反馈相位ΦBAK之间必须存在相位差; Typle Ⅱ:理论上ΦREF与反馈相位ΦBAK之间不存在相位差;

以实现方式分类:

模拟锁相环 数字锁相环

电

所 究 分 研 S 山 子 CA E 昆 M 所 究 研 S 子 CA 电 E 微 IM 究 院 KS 研 学 子 CA 电 E 微 IM 院 KS

REF BAK

out

N / N 1

N

t1 N 1 t 2 N t N 1 t1 t 2 t1 t 2

电

所 究 分 研 S 山 子 CA E 昆 M 所 究 研 S 子 CA 电 E 微 IM 究 院 KS 研 学 子 CA 电 E 微 IM 院 KS

使用Σ-Δ调制器,抑制小数杂散;

锁相环的改进2

整数锁相环中频率步长与锁定时间的折中

频率步长决定参考频率; 为抑制Reference Spur,fREF>>ωp>>ωc; 锁定时间tL∝ ωc;

科

学

小数分频锁相环

使用小数分频器,fVCO=(N+M)fREF ,其中N为整数,M为小数;

改变分频器的分频系数,在t1时间内分频器分频系数为N+1,在t2时间内分频系数为N;

电

所 究 分 研 S 山 子 CA E 昆 M 所 究 研 S 子 CA 电 E 微 IM 究 院 KS 研 学 子 CA 电 E 微 IM 院 KS

TypeⅡ型锁相环

利用电荷泵使锁相环传递函数在原点存在两个极点; 理论上对于固定频率输入,输入输出之间无固定偏差; 为了保证稳定,需要额外产生一个零点;

s KVCO 1 z o s K REF FD 1 K H s VCO s s 1 1 PD LPF s p 1 p 2 K PD H LPF s

科

z

p1 p 2

lg

input

lg

z

p1 p 2

电

所 究 分 研 S 山 子 CA E 昆 M 所 究 研 S 子 CA 电 E 微 IM 究 院 KS 研 学 子 CA 电 E 微 IM 院 KS

锁相环改进1

死区

鉴频器/电荷泵的非理想特性及影响

科

由于电容效应,开启电荷泵需要一定脉冲,而脉冲与ΔΦ成正比;这意味着死区将使ΔΦ随机积 累,最终产生“抖动” (jitter)

i

K PD

科

学

H LPF ( S )

Rz

KVCO S

o

1 sRz C K H open s K PD H LPF s VCO s sC H open s K PD H LPF s KVCO 1 sRz C o 2 i 1 H open s s C s K PD H LPF s KVCO Rz C K PD H LPF s KVCO s2 e o i 2 s C s K PD H LPF s KVCO Rz C K PD H LPF s KVCO i i i s2 lim s 2 2 0 s0 s s C s K PD H LPF s KVCO Rz C K PD H LPF s KVCO

鉴频鉴相器/电荷泵的改进

消除死区——增加延迟单元 消除充放电电流的不匹配——增加电流负反馈校准电路 消除电荷共享——增加自举电路

D

f BAK

科

学

Q

f REF

CK Q

UP

UN

CK Q

Vm

Vtune

Vx

DW

DN

D

Q

Vbn

电

所 究 分 研 S 山 子 CA E 昆 M 所 究 研 S 子 CA 电 E 微 IM 究 院 KS 研 学 子 CA 电 E 微 IM 院 KS

一般可以将参考时钟噪声ΦREF、鉴相器/电荷泵噪声ΦPD、分频器噪声ΦFD归为为 输入噪声,其在锁相环环路中呈现低通特性; VCO噪声在锁相环环路中呈现高通特性; 锁相环输出噪声为各种噪声总和;

VCO

1 f3 1 2 f 1

科

学

VCO

f

p1

p2

lg

lg

PLL

input

VCO型锁相环

控制量为VCO振荡频率; 能够轻易实现频率倍增; 一般为TypeⅡ系统;

REF BAK

out

科

学

延迟线型锁相环

控制量为延迟线的延迟时间; 相位噪声小于VCO;

out

REF

为TypeⅠ系统;

无法实现频率倍增;

电

所 究 分 研 S 山 子 CA E 昆 M 所 究 研 S 子 CA 电 E 微 IM 究 院 KS 研 学 子 CA 电 E 微 IM 院 KS

ωp ; ωc为截止频率,约为锁相环环路带宽。

电

所 究 分 研 S 山 子 CA E 昆 M 所 究 研 S 子 CA 电 E 微 IM 究 院 KS 研 学 子 CA 电 E 微 IM 院 KS

噪声分析

e ,REF

e,PFD / CP

e,LPF

e,VCO

K PD

1 sRz C H s LPF sC c K PD KVCO Rz z 1 R C z c z n c z