云南大学计算机组成原理期末考试

计算机组成原理期末考试及答案

计算机组成原理期末考试及答案A卷基础知识(50分)1、名词解释(10分)机器字长SRAMEPROM指令系统微指令2、选择题(10分)1)设字长32位,使⽤IEEE格式,则阶码采⽤______表⽰。

A.补码B. 原码C. 移码D. 反码2) 四⽚74181ALU和⼀⽚74182CLA器件相配合,具有如下进位传递功能______。

A.形波进位B. 组内先⾏进位,组间先⾏进位C.组内先⾏进位,组间⾏波进位D. 组内形波进位,组间先⾏进位3) 某SARM芯⽚,其存储容量为64K×16位,该芯⽚的地址线数⽬和数据线数⽬分别是___。

A. 16, 16 B .16, 64, C. 64, 8 D. 64, 164)单地址指令中为了完成两个数的算术运算,除地址码指明的⼀个操作数外,另⼀个数常需采⽤______。

A. 堆栈寻址⽅式B. ⽴即寻址⽅式C. 隐含寻址⽅式D. 间接寻址⽅式微5)程序控制器中,机器指令与微指令的关系是______。

A.每⼀条机器指令由⼀条微指令来执⾏B.⼀段机器指令组成的程序可由⼀条微指令执⾏C.⼀条微指令由若⼲条机器指令组成D. 每⼀条机器指令由⼀段⽤微指令编成的微程序来解释执⾏3、填空题(10分)1)存储___①___并按__②____顺序执⾏,这是冯?诺依曼型计算机的⼯作原理。

2)相联存储器是按③访问的存储器。

3) 主存与cache的地址映射有__④___、⑤、⑥三种⽅式。

4)通常指令编码的第⼀个字段是⑦。

5) 异步通信⽅式可分为⑧、⑨、⑩三种类型。

4、问答题(20分)1)在计算机中,为什么要采⽤多级结构的存储器系统2)简述CPU的功能.3)试⽐较⽔平型微指令与垂直型微指令。

4)简述总线集中控制的优先权仲裁⽅式。

⼆、综合应⽤(50分)1、已知X=-0.1101,Y=0.1011,试⽤补码⼀位乘法计算X×Y (15分)2、指令格式如下所⽰。

OP为操作码字段,试分析指令格式特点。

2022年云南大学软件工程专业《计算机组成原理》科目期末试卷A(有答案)

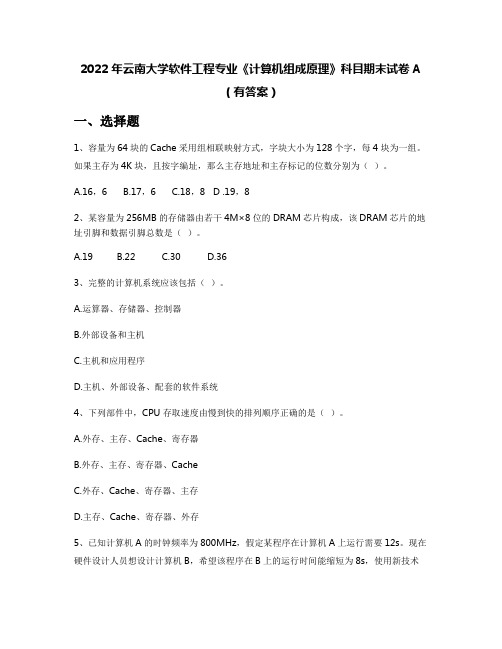

2022年云南大学软件工程专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、容量为64块的Cache采用组相联映射方式,字块大小为128个字,每4块为一组。

如果主存为4K块,且按字编址,那么主存地址和主存标记的位数分别为()。

A.16,6B.17,6C.18,8 D .19,82、某容量为256MB的存储器由若干4M×8位的DRAM芯片构成,该DRAM芯片的地址引脚和数据引脚总数是()。

A.19B.22C.30D.363、完整的计算机系统应该包括()。

A.运算器、存储器、控制器B.外部设备和主机C.主机和应用程序D.主机、外部设备、配套的软件系统4、下列部件中,CPU存取速度由慢到快的排列顺序正确的是()。

A.外存、主存、Cache、寄存器B.外存、主存、寄存器、CacheC.外存、Cache、寄存器、主存D.主存、Cache、寄存器、外存5、已知计算机A的时钟频率为800MHz,假定某程序在计算机A上运行需要12s。

现在硬件设计人员想设计计算机B,希望该程序在B上的运行时间能缩短为8s,使用新技术后可使B的时钟频率大幅度提高,但在B上运行该程序所需要的时钟周期数为在A上的1.5倍。

那么,机器B的时钟频率至少应为()能运到所希望的要求。

A.800MHzB.1.2 GHzC.1.5GHzD.1.8GHz6、一次总线事务中,主设备只需给出一个首地址,从设备就能从首地址开始的若干连续单元读出或写入多个数据。

这种总线事务方式称为()。

A.并行传输B.串行传输C.突发传输D.同步传输7、假设某存储器总线采用同步通信方式,时钟频率为50MHz,每个总线事务以突发方式传输8个字,以支持块长为8个字的Cache行读和Cache行写,每字4B.对于读操作,方式顺序是1个时钟周期接收地址,3个时钟周期等待存储器读数,8个时钟周期用于传输8个字。

请问若全部访问都为读操作,该存储器的数据传输速率为()。

计算机组成原理期末考试试题及答案

计算机组成原理期末考试试题及答案一、选择题(每题2分,共20分)1. 计算机系统由哪两大部分组成?A. 硬件和软件B. CPU和内存C. 输入设备和输出设备D. 运算器和控制器答案:A2. 以下哪个部件不属于计算机五大硬件之一?A. 控制器B. 运算器C. 输入设备D. 显示器答案:D3. 在计算机中,下列哪种寄存器的位数与机器字长相同?A. 程序计数器B. 指令寄存器C. 状态寄存器D. 数据寄存器答案:B4. 下列哪种寻址方式中,操作数地址由形式地址和偏移量相加得到?A. 直接寻址B. 间接寻址C. 基址寻址D. 变址寻址答案:D5. 计算机指令的执行过程分为以下哪几个阶段?A. 取指令、分析指令、执行指令、写回结果B. 取指令、分析指令、执行指令、中断处理C. 取指令、分析指令、执行指令、存储结果D. 取指令、分析指令、执行指令、传输结果答案:A6. 下列哪种总线用于连接CPU和内存?A. 数据总线B. 地址总线C. 控制总线D. 外部总线答案:B7. Cache存储器的作用是?A. 提高内存的读写速度B. 减少CPU访问内存的次数C. 提高程序的运行效率D. 减少CPU与内存之间的数据传输量答案:B8. 下列哪种中断属于可屏蔽中断?A. 外部中断B. 内部中断C. 软件中断D. 硬件故障中断答案:A9. 在计算机系统中,下列哪个设备用于实现数据的输入和输出?A. CPUB. 内存C. 硬盘D. 显示器答案:D10. 下列哪种传输方式不属于并行传输?A. 同步传输B. 异步传输C. 单工传输D. 双工传输答案:C二、填空题(每题2分,共20分)1. 计算机硬件系统包括______、______、______、______和______五大部件。

答案:控制器、运算器、存储器、输入设备、输出设备2. 计算机指令由______和______两部分组成。

答案:操作码、操作数3. 在计算机中,地址总线的作用是______。

云南大学计算机组成原理期末考试

期末考试复习 单项选择题1. 运算器的主要功能是进行_ __ 。

A 、逻辑运算B 、算术运算C 、逻辑运算与算术运算D 、初等函数的运算 2. 若定点整数64位,含1位符号位,补码表示,则所能表示的绝对值最大负数为( )。

A 、-264B 、-(264-1)C 、-263D 、-(263-1) 3. 有关算术右移中,说法正确的是_ __。

A .数据右移1位,数据最高位用0补充B .数据右移1位,数据最高位用原最低位补充C .数据右移1位,数据最高位用符号位补充D .数据右移1位,数据最高位用1补充 4. 堆栈指针SP 寄存器中的内容是_ __。

A .栈顶单元内容B .栈顶单元地址C .栈底单元内容D .栈底单元地址5. 设形式地址为D ,基址寄存器为X ,变址寄存器为Y ,(X )表示基址寄存器X 的内容,基址变址寻址方式的有效地址可表示为_ __。

A .EA=(X )+(Y )+DB .EA=(X+Y )+(D )C .EA=((X )+(Y)+D ) D .EA=((X+Y )+(D )) 6. 寄存器间接寻址方式中,操作数处在______中。

A.通用寄存器B.主存单元C.程序计数器D.堆栈7. 存储周期是指__ _。

A .存储器的读出时间B .存储器的写入时间C .存储器进行连续读或写操作所允许的最短时间间隔D .存储器进行连续写或写操作所需的最长时间间隔 8. 在下列存储器中,_ __可以作为主存储器。

A.半导体SRAM 存储器B.EPROMC.PROMD.半导体DRAM 存储器9. 微程序控制器中,机器指令与微指令的关系是_ __。

A 、每一条机器指令由一段微指令编写的微程序来解释执行 B 、每一条机器指令由一条微指令来执行C 、 每一条机器指令组成的程序可由一条微指令来执行D 、 一条微指令由若干条机器指令组成_____________ ________10.主存储器和CPU之间增加cache的目的是______。

计算机组成原理期末考试试卷及答案

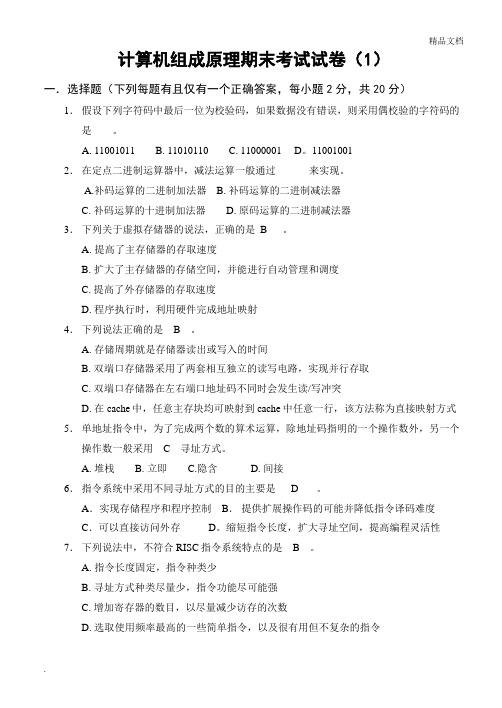

计算机组成原理期末考试试卷(1)一.选择题(下列每题有且仅有一个正确答案,每小题2分,共20分)1.假设下列字符码中最后一位为校验码,如果数据没有错误,则采用偶校验的字符码的是____。

A. 11001011B. 11010110C. 11000001 D。

110010012.在定点二进制运算器中,减法运算一般通过______ 来实现。

A.补码运算的二进制加法器B. 补码运算的二进制减法器C. 补码运算的十进制加法器D. 原码运算的二进制减法器3.下列关于虚拟存储器的说法,正确的是_B___。

A.提高了主存储器的存取速度B.扩大了主存储器的存储空间,并能进行自动管理和调度C. 提高了外存储器的存取速度D. 程序执行时,利用硬件完成地址映射4.下列说法正确的是__B__。

A. 存储周期就是存储器读出或写入的时间B. 双端口存储器采用了两套相互独立的读写电路,实现并行存取C. 双端口存储器在左右端口地址码不同时会发生读/写冲突D. 在cache中,任意主存块均可映射到cache中任意一行,该方法称为直接映射方式5.单地址指令中,为了完成两个数的算术运算,除地址码指明的一个操作数外,另一个操作数一般采用__C__寻址方式。

A. 堆栈B. 立即C.隐含D. 间接6.指令系统中采用不同寻址方式的目的主要是___D___ 。

A.实现存储程序和程序控制 B.提供扩展操作码的可能并降低指令译码难度C.可以直接访问外存 D。

缩短指令长度,扩大寻址空间,提高编程灵活性7.下列说法中,不符合RISC指令系统特点的是__B__。

A.指令长度固定,指令种类少B.寻址方式种类尽量少,指令功能尽可能强C. 增加寄存器的数目,以尽量减少访存的次数D. 选取使用频率最高的一些简单指令,以及很有用但不复杂的指令8. 指令周期是指___C___。

A .CPU 从主存取出一条指令的时间B .CPU 执行一条指令的时间C .CPU 从主存取出一条指令加上执行这条指令的时间D .时钟周期时间 9. 假设微操作控制信号用n C 表示,指令操作码译码输出用m I 表示,节拍电位信号用k M 表示,节拍脉冲信号用i T 表示,状态反馈信息用i B 表示,则硬布线控制器的控制信号n C 可描述为__D__。

2022年云南大学数据科学与大数据技术专业《计算机组成原理》科目期末试卷A(有答案)

2022年云南大学数据科学与大数据技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、某计算机使用4体交叉编址存储器,假定在存储器总线上出现的主存地址(十进制)序列为8005,8006,8007,8008,8001,8002,8003,8004,8000,则可能发生访存冲突的地址对是()。

A.8004和8008B.8002和8007C.8001和8008D.8000和80042、访问相联存储器时,()A.根据内容,不需要地址B.不根据内容,只需要地址C.既要内容,又要地址D.不要内容也不要地址3、在补码加减交替除法中,参加操作的数和商符分别是()。

A.绝对值的补码在形成商值的过程中自动形成B.补码在形成商值的过程中自动形成C.补码由两数符号位“异或”形成D.绝对值的补码由两数符号位“异或”形成4、下列关于进制的说法中正确的是()。

I.任何二进制整数都可用十进制表示Ⅱ.任何二进制小数都可用十进制表示Ⅲ.任何十进制整数都可用二进制表示IⅣ.任何十进制小数都可用二进制表示A.I、ⅢB. I、Ⅱ、ⅢC.I、Ⅱ、Ⅲ、ⅣD.Ⅱ、IV5、有如下C语言程序段:()short si=-32767;unsigned short usi=si;执行上述两条语句后,usi的值为A.-32767B.32767C.32768D.327696、在下列各种情况中,最应采用异步传输方式的是().A.I/O接口与打印机交换信息B.CPU与主存交换信息C.CPU和PCI总线交换信息D.由统一时序信号控制方式下的设备7、在下面描述的PCI总线的基本概念中,不正确的表述是()。

A.PCI总线支持即插即用B.PCI总线可对传输信息进行奇偶校验C.系统中允许有多条PCI总线D.PCI设备一定是主设备8、只有当程序要执行时,它才会去将源程序翻译成机器语言,而且一次只能读取、翻译并执行源程序中的一行语句,此程序称为()。

A.目标程序B.编译程序C.解释程序D.汇编程序9、程序P在机器M上的执行时间是20s,编译优化后,P执行的指令数减少到原来的70%,而CPl增加到原来的1.2倍,则P在M上的执行时间是()。

计算机组成原理期末考试试题及答案

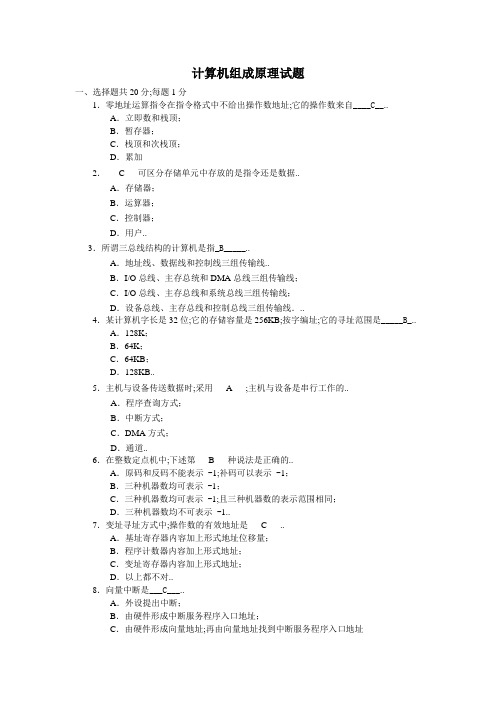

计算机组成原理试题一、选择题共20分;每题1分1.零地址运算指令在指令格式中不给出操作数地址;它的操作数来自____C__..A.立即数和栈顶;B.暂存器;C.栈顶和次栈顶;D.累加2.___C___可区分存储单元中存放的是指令还是数据..A.存储器;B.运算器;C.控制器;D.用户..3.所谓三总线结构的计算机是指_B_____..A.地址线、数据线和控制线三组传输线..B.I/O总线、主存总统和DMA总线三组传输线;C.I/O总线、主存总线和系统总线三组传输线;D.设备总线、主存总线和控制总线三组传输线...4.某计算机字长是32位;它的存储容量是256KB;按字编址;它的寻址范围是_____B_..A.128K;B.64K;C.64KB;D.128KB..5.主机与设备传送数据时;采用___A___;主机与设备是串行工作的..A.程序查询方式;B.中断方式;C.DMA方式;D.通道..6.在整数定点机中;下述第___B___种说法是正确的..A.原码和反码不能表示-1;补码可以表示-1;B.三种机器数均可表示-1;C.三种机器数均可表示-1;且三种机器数的表示范围相同;D.三种机器数均不可表示-1..7.变址寻址方式中;操作数的有效地址是___C___..A.基址寄存器内容加上形式地址位移量;B.程序计数器内容加上形式地址;C.变址寄存器内容加上形式地址;D.以上都不对..8.向量中断是___C___..A.外设提出中断;B.由硬件形成中断服务程序入口地址;C.由硬件形成向量地址;再由向量地址找到中断服务程序入口地址D.以上都不对..9.一个节拍信号的宽度是指_____C_..A.指令周期;B.机器周期;C.时钟周期;D.存储周期..10.将微程序存储在EPROM中的控制器是____A__控制器..A.静态微程序;B.毫微程序;C.动态微程序;D.微程序..11.隐指令是指___D___..A.操作数隐含在操作码中的指令;B.在一个机器周期里完成全部操作的指令;C.指令系统中已有的指令;D.指令系统中没有的指令..12.当用一个16位的二进制数表示浮点数时;下列方案中第____B_种最好..A.阶码取4位含阶符1位;尾数取12位含数符1位;B.阶码取5位含阶符1位;尾数取11位含数符1 位;C.阶码取8位含阶符1位;尾数取8位含数符1位;D.阶码取6位含阶符1位;尾数取12位含数符1位..13.DMA方式__B____..A.既然能用于高速外围设备的信息传送;也就能代替中断方式;B.不能取代中断方式;C.也能向CPU请求中断处理数据传送;D.内无中断机制..14.在中断周期中;由____D__将允许中断触发器置“0”..A.关中断指令;B.机器指令;C.开中断指令;D.中断隐指令..15.在单总线结构的CPU中;连接在总线上的多个部件__B____..A.某一时刻只有一个可以向总线发送数据;并且只有一个可以从总线接收数据;B.某一时刻只有一个可以向总线发送数据;但可以有多个同时从总线接收数据;C.可以有多个同时向总线发送数据;并且可以有多个同时从总线接收数据;D.可以有多个同时向总线发送数据;但可以有一个同时从总线接收数据.. 16.三种集中式总线控制中;___A___方式对电路故障最敏感..A.链式查询;B.计数器定时查询;C.独立请求;D.以上都不对..17.一个16K×8位的存储器;其地址线和数据线的总和是__D____..A.48;B.46;C.17;D.22.18.在间址周期中;__C____..A.所有指令的间址操作都是相同的;B.凡是存储器间接寻址的指令;它们的操作都是相同的;C.对于存储器间接寻址或寄存器间接寻址的指令;它们的操作是不同的;D.以上都不对..19.下述说法中____B__是正确的..A.EPROM是可改写的;因而也是随机存储器的一种;B.EPROM是可改写的;但它不能用作为随机存储器用;C.EPROM只能改写一次;故不能作为随机存储器用;D.EPROM是可改写的;但它能用作为随机存储器用..20.打印机的分类方法很多;若按能否打印汉字来区分;可分为_C_____..A.并行式打印机和串行式打印机;B.击打式打印机和非击打式打印机;C.点阵式打印机和活字式打印机;D.激光打印机和喷墨打印机..二、填空共20分;每空1分1.设浮点数阶码为8位含1位阶符;尾数为24位含1位数符;则32位二进制补码浮点规格化数对应的十进制真值范围是:最大正数为21271-2-23;最小正数为2-129;最大负数为2-128-2-1-2-23;最小负数为-2127..2.指令寻址的基本方式有两种;一种是顺序寻址方式;其指令地址由程序计数器给出;另一种是跳跃寻址方式;其指令地址由指令本身给出..3.在一个有四个过程段的浮点加法器流水线中;假设四个过程段的时间分别是T1 = 60ns ﹑T2 = 50ns﹑T3 = 90ns﹑T4 = 80ns..则加法器流水线的时钟周期至少为90ns ..如果采用同样的逻辑电路;但不是流水线方式;则浮点加法所需的时间为280ns ..4.一个浮点数;当其尾数右移时;欲使其值不变;阶码必须增加..尾数右移1位;阶码加1 ..5.存储器由mm=1;2;4;8…个模块组成;每个模块有自己的地址和数据寄存器;若存储器采用模m编址;存储器带宽可增加到原来的m 倍..6.按序写出多重中断的中断服务程序包括保护现场、开中断、设备服务|.... 恢复现场和中断返回几部分..1.A.A.21271-2-23B.2-129 C.2-128-2-1-2-23D.-2127三、名词解释共10分;每题2分1.微操作命令和微操作答:微操作命令是控制完成微操作的命令;微操作是由微操作命令控制实现的最基本操作.. 2.快速缓冲存储器答:快速缓冲存储器是为了提高访存速度;在CPU和主存之间增设的高速存储器;它对用户是透明的..只要将CPU最近期需用的信息从主存调入缓存;这样CPU每次只须访问快速缓存就可达到访问主存的目的;从而提高了访存速度..3.基址寻址答:基址寻址有效地址等于形式地址加上基址寄存器的内容..4.流水线中的多发技术答:为了提高流水线的性能;设法在一个时钟周期机器主频的倒数内产生更多条指令的结果;这就是流水线中的多发技术..5.指令字长答:指令字长是指机器指令中二进制代码的总位数..四、计算题5分设机器数字长为8位含1位符号位;设A =649;B =3213-;计算A ±B 补;并还原成真值.. 计算题 答:A +B 补=1.1011110; A +B =-17/64A -B 补=1.1000110; A -B =35/64五、简答题共20分1.异步通信与同步通信的主要区别是什么;说明通信双方如何联络..4分同步通信和异步通信的主要区别是前者有公共时钟;总线上的所有设备按统一的时序;统一的传输周期进行信息传输;通信双方按约定好的时序联络..后者没有公共时钟;没有固定的传输周期;采用应答方式通信;具体的联络方式有不互锁、半互锁和全互锁三种..不互锁方式通信双方没有相互制约关系;半互锁方式通信双方有简单的制约关系;全互锁方式通信双方有完全的制约关系..其中全互锁通信可靠性最高..2.为什么外围设备要通过接口与CPU 相连 接口有哪些功能 6分答:外围设备要通过接口与CPU 相连的原因主要有:1一台机器通常配有多台外设;它们各自有其设备号地址;通过接口可实现对设备的选择..2I/O 设备种类繁多;速度不一;与 CPU 速度相差可能很大;通过接口可实现数据缓冲;达到速度匹配..3I/O 设备可能串行传送数据;而CPU 一般并行传送;通过接口可实现数据串并格式转换.. 4I/O 设备的入/出电平可能与CPU 的入/出电平不同;通过接口可实现电平转换.. 5CPU 启动I/O 设备工作;要向外设发各种控制信号;通过接口可传送控制命令..6I/O 设备需将其工作状况“忙”、“就绪”、“错误”、“中断请求”等及时报告CPU;通过接口可监视设备的工作状态;并保存状态信息;供CPU 查询..可见归纳起来;接口应具有选址的功能、传送命令的功能、反映设备状态的功能以及传送数据的功能包括缓冲、数据格式及电平的转换..六、问答题共15分1.设CPU 中各部件及其相互连接关系如下图所示..图中W 是写控制标志;R 是读控制标志;R 1和R 2是暂存器..8分1假设要求在取指周期由ALU 完成PC+1→PC 的操作即ALU 可以对它的一个源操作数完成加1的运算..要求以最少的节拍写出取指周期全部微操作命令及节拍安排..答:由于PC+1→PC 需由ALU 完成;因此PC 的值可作为ALU 的一个源操作数;靠控制ALU 做+1运算得到PC+1;结果送至与ALU 输出端相连的R 2;然后再送至PC..此题的关键是要考虑总线冲突的问题;故取指周期的微操作命令及节拍安排如下:T 0 PC→MAR ;1→RT 1 MMAR→MDR ;PC+1→R 2T 2 MDR→IR ;OPIR→微操作命令形成部件T 3 R 2→PC2写出指令ADD # α#为立即寻址特征;隐含的操作数在ACC 中在执行阶段所需的微操作命令及节拍安排..答:立即寻址的加法指令执行周期的微操作命令及节拍安排如下:T 0 AdIR→R 1 ;立即数→R 1T 1 R 1+ACC→R 2 ;ACC 通过总线送ALUT 2 R 2→ACC ;结果→ACC2.DMA 接口主要由哪些部件组成 在数据交换过程中它应完成哪些功能 画出DMA 工作过程的流程图不包括预处理和后处理答:DMA 接口主要由数据缓冲寄存器、主存地址计数器、字计数器、设备地址寄存器、中断机构和DMA 控制逻辑等组成..在数据交换过程中;DMA 接口的功能有:1向CPU 提出总线请求信号;2当CPU 发出总线响应信号后;接管对总线的控制;3向存储器发地址信号并能自动修改地址指针;4向存储器发读/写等控制信号;进行数据传送;5修改字计数器;并根据传送字数;判断DMA 传送是否结束;6发DMA 结束信号;向CPU 申请程序中断;报告一组数据传送完毕..DMA 工作过程流程如图所示..七、设计题10分设CPU 共有16根地址线;8根数据线;并用MREQ 作访存控制信号低电平有效;用WR 作读写控制信号高电平为读;低电平为写..现有下列芯片及各种门电路门电路自定;如图所示..画出CPU 与存储器的连接图;要求:1存储芯片地址空间分配为:最大4K 地址空间为系统程序区;相邻的4K 地址空间为系统程序工作区;最小16K 地址空间为用户程序区;2指出选用的存储芯片类型及数量;3详细画出片选逻辑..1主存地址空间分配:6000H ~67FFH 为系统程序区;6800H ~6BFFH 为用户程序区..答:1主存地址空间分配..2分A 15 … A 11 … A 7 … … A 0⎪⎪⎭⎪⎪⎬⎫0000000000001111111111111110111100000000000111111111111111111111最大4K 2K ×8位ROM2片 ⎭⎬⎫00000000000001111111111111110111相邻4K 4K ×4位RAM2片 ⎪⎪⎭⎪⎪⎬⎫1111111111111100000000000000010011111111111110000000000000000000最小16K 8K ×8位RAM2片 2合理选用上述存储芯片;说明各选几片2根据主存地址空间分配最大4K 地址空间为系统程序区;选用2片2K ×8位ROM 芯片;1分相邻的4K 地址空间为系统程序工作区;选用2片4K ×4位RAM 芯片;1分最小16K地址空间为用户程序区;选用2片8K×8位RAM芯片..1分3详细画出存储芯片的片选逻辑图..答案:一、选择题共20分;每题1分1.C 2.C 3.B 4.B 5.A 6.B 7.C8.C 9.C 10.A 11.D 12.B 13.B 14.D15.B 16.A 17.D 18.C 19.B 20.C二、填空共20分;每空1分1.A.A.21271-2-23B.2-129 C.2-128-2-1-2-23D.-21272.A.顺序B.程序计数器C.跳跃D.指令本身3.A.90ns B.280ns4.A.A.增加B.加15.A.地址B.数据C.模m D.m6.A.保护现场B.开中断C.设备服务D.恢复现场三、名词解释共10分;每题2分1.微操作命令和微操作答:微操作命令是控制完成微操作的命令;微操作是由微操作命令控制实现的最基本操作.. 2.快速缓冲存储器答:快速缓冲存储器是为了提高访存速度;在CPU和主存之间增设的高速存储器;它对用户是透明的..只要将CPU最近期需用的信息从主存调入缓存;这样CPU每次只须访问快速缓存就可达到访问主存的目的;从而提高了访存速度..3.基址寻址答:基址寻址有效地址等于形式地址加上基址寄存器的内容..4.流水线中的多发技术答:为了提高流水线的性能;设法在一个时钟周期机器主频的倒数内产生更多条指令的结果;这就是流水线中的多发技术..5.指令字长答:指令字长是指机器指令中二进制代码的总位数..四、共5分计算题答:A+B补=1.1011110; A+B=-17/64A-B补=1.1000110; A-B=35/64五、简答题共20分1.4分答:同步通信和异步通信的主要区别是前者有公共时钟;总线上的所有设备按统一的时序;统一的传输周期进行信息传输;通信双方按约定好的时序联络..后者没有公共时钟;没有固定的传输周期;采用应答方式通信;具体的联络方式有不互锁、半互锁和全互锁三种..不互锁方式通信双方没有相互制约关系;半互锁方式通信双方有简单的制约关系;全互锁方式通信双方有完全的制约关系..其中全互锁通信可靠性最高..2.6分;每写出一种给1分;最多6分答:外围设备要通过接口与CPU相连的原因主要有:1一台机器通常配有多台外设;它们各自有其设备号地址;通过接口可实现对设备的选择..2I/O设备种类繁多;速度不一;与CPU速度相差可能很大;通过接口可实现数据缓冲;达到速度匹配..3I/O设备可能串行传送数据;而CPU一般并行传送;通过接口可实现数据串并格式转换..4I/O设备的入/出电平可能与CPU的入/出电平不同;通过接口可实现电平转换..5CPU启动I/O设备工作;要向外设发各种控制信号;通过接口可传送控制命令..6I/O设备需将其工作状况“忙”、“就绪”、“错误”、“中断请求”等及时报告CPU;通过接口可监视设备的工作状态;并保存状态信息;供CPU查询..可见归纳起来;接口应具有选址的功能、传送命令的功能、反映设备状态的功能以及传送数据的功能包括缓冲、数据格式及电平的转换..4.5分答:(1)根据IR和MDR均为16位;且采用单字长指令;得出指令字长16位..根据105种操作;取操作码7位..因允许直接寻址和间接寻址;且有变址寄存器和基址寄存器;因此取2位寻址特征;能反映四种寻址方式..最后得指令格式为:7 2 7其中OP 操作码;可完成105种操作;M 寻址特征;可反映四种寻址方式;AD形式地址..这种格式指令可直接寻址27 = 128;一次间址的寻址范围是216 = 65536..(2)双字长指令格式如下:7 2 7其中OP、M的含义同上;AD1∥AD2为23位形式地址..这种格式指令可直接寻址的范围为223 = 8M..(3)容量为8MB的存储器;MDR为16位;即对应4M×16位的存储器..可采用双字长指令;直接访问4M存储空间;此时MAR取22位;也可采用单字长指令;但R X和R B取22位;用变址或基址寻址访问4M存储空间..六、共15分问答题1.8分答:1由于PC+1→PC需由ALU完成;因此PC的值可作为ALU的一个源操作数;靠控制ALU 做+1运算得到PC+1;结果送至与ALU输出端相连的R2;然后再送至PC..此题的关键是要考虑总线冲突的问题;故取指周期的微操作命令及节拍安排如下:T0PC→MAR;1→RT1MMAR→MDR;PC+1→R2T2MDR→IR;OPIR→微操作命令形成部件T3R2→PC2立即寻址的加法指令执行周期的微操作命令及节拍安排如下:T0AdIR→R1;立即数→R1T1R1+ACC→R2;ACC通过总线送ALUT 2 R 2→ACC ;结果→ACC2.7分答:DMA 接口主要由数据缓冲寄存器、主存地址计数器、字计数器、设备地址寄存器、中断机构和DMA 控制逻辑等组成..在数据交换过程中;DMA 接口的功能有:1向CPU 提出总线请求信号;2当CPU 发出总线响应信号后;接管对总线的控制;3向存储器发地址信号并能自动修改地址指针;4向存储器发读/写等控制信号;进行数据传送;5修改字计数器;并根据传送字数;判断DMA 传送是否结束;6发DMA 结束信号;向CPU 申请程序中断;报告一组数据传送完毕..DMA 工作过程流程如图所示..七、设计题共10分答:1主存地址空间分配..2分A 15 … A 11 … A 7 … … A 0⎪⎪⎭⎪⎪⎬⎫0000000000001111111111111110111100000000000111111111111111111111最大4K 2K ×8位ROM2片 ⎭⎬⎫00000000000001111111111111110111相邻4K 4K ×4位RAM2片 ⎪⎪⎭⎪⎪⎬⎫1111111111111100000000000000010011111111111110000000000000000000最小16K 8K ×8位RAM2片2根据主存地址空间分配最大4K 地址空间为系统程序区;选用2片2K ×8位ROM 芯片;1分相邻的4K 地址空间为系统程序工作区;选用2片4K ×4位RAM 芯片;1分最小16K 地址空间为用户程序区;选用2片8K ×8位RAM 芯片..1分3存储芯片的片选逻辑图5分。

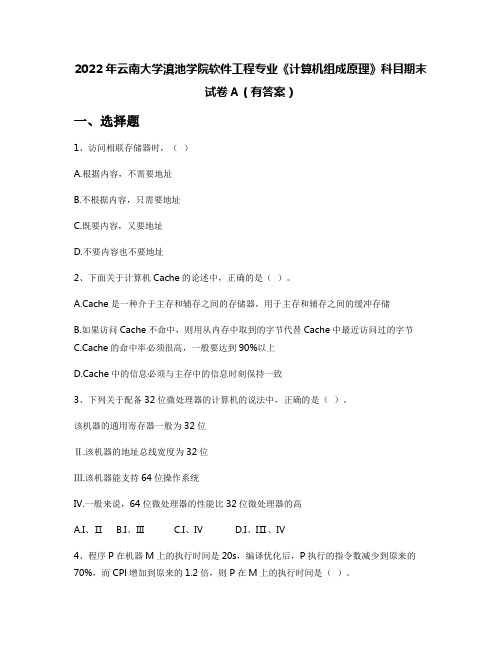

2022年云南大学滇池学院软件工程专业《计算机组成原理》科目期末试卷A(有答案)

2022年云南大学滇池学院软件工程专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、访问相联存储器时,()A.根据内容,不需要地址B.不根据内容,只需要地址C.既要内容,又要地址D.不要内容也不要地址2、下面关于计算机Cache的论述中,正确的是()。

A.Cache是一种介于主存和辅存之间的存储器,用于主存和辅存之间的缓冲存储B.如果访问Cache不命中,则用从内存中取到的字节代替Cache中最近访问过的字节C.Cache的命中率必须很高,一般要达到90%以上D.Cache中的信息必须与主存中的信息时刻保持一致3、下列关于配备32位微处理器的计算机的说法中,正确的是()。

该机器的通用寄存器一般为32位Ⅱ.该机器的地址总线宽度为32位Ⅲ.该机器能支持64位操作系统IV.一般来说,64位微处理器的性能比32位微处理器的高A.I、ⅡB.I、ⅢC.I、ⅣD.I、IⅡ、Ⅳ4、程序P在机器M上的执行时间是20s,编译优化后,P执行的指令数减少到原来的70%,而CPl增加到原来的1.2倍,则P在M上的执行时间是()。

A.8.4sB.11.7sC.14sD.16.8s5、CPU中的译码器要用()。

A.地址译码人B.指令译码C.数据译码1D.控制信号译码6、某同步总线的时钟频率为100MHz,宽度为32位,地址/数据线复用,每传输一个地址或数据占用一个时钟周期。

若该总线支持突发(猝发)传输方式,则一次“主存写”总线事务传输128位数据所需要的时间至少是()。

A.20nsB.40nsC.50nsD.80ns7、为协调计算机系统各部件的工作,需要一种器件来提供统一的时钟标准,这个器件,是()。

A.总线缓冲器B.总线控制器C.时钟发生器D.以上器件都具备这种功能8、单周期处理器中所有指令的指令周期为一个时钟周期。

下列关于单周期处理器的叙述中,错误的是()。

A.可以采用单总线结构数据通路B.处理器时钟频率较低C.在指令执行过程中控制信号不变D.每条指令的CPI为19、下列说法中,正确的是()。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

期末考试复习 单项选择题

1. 运算器的主要功能是进行_ __ 。

A 、逻辑运算

B 、算术运算

C 、逻辑运算与算术运算

D 、初等函数的运算 2. 若定点整数64位,含1位符号位,补码表示,则所能表示的绝对值最大负数为( )。

A 、-264

B 、-(264-1)

C 、-263

D 、-(263-1) 3. 有关算术右移中,说法正确的是_ __。

A .数据右移1位,数据最高位用0补充

B .数据右移1位,数据最高位用原最低位补充

C .数据右移1位,数据最高位用符号位补充

D .数据右移1位,数据最高位用1补充 4. 堆栈指针SP 寄存器中的内容是_ __。

A .栈顶单元内容

B .栈顶单元地址

C .栈底单元内容

D .栈底单元地址

5. 设形式地址为D ,基址寄存器为X ,变址寄存器为Y ,(X )表示基址寄存器X 的内

容,基址变址寻址方式的有效地址可表示为_ __。

A .EA=(X )+(Y )+D

B .EA=(X+Y )+(D )

C .EA=((X )+(Y)+

D ) D .EA=((X+Y )+(D )) 6. 寄存器间接寻址方式中,操作数处在______中。

A.通用寄存器

B.主存单元

C.程序计数器

D.堆栈

7. 存储周期是指__ _。

A .存储器的读出时间

B .存储器的写入时间

C .存储器进行连续读或写操作所允许的最短时间间隔

D .存储器进行连续写或写操作所需的最长时间间隔 8. 在下列存储器中,_ __可以作为主存储器。

A.半导体SRAM 存储器

B.EPROM

C.PROM

D.半导体DRAM 存储器

9. 微程序控制器中,机器指令与微指令的关系是_ __。

A 、每一条机器指令由一段微指令编写的微程序来解释执行 B 、每一条机器指令由一条微指令来执行

C 、 每一条机器指令组成的程序可由一条微指令来执行

D 、 一条微指令由若干条机器指令组成

_____________ ________

10.主存储器和CPU之间增加cache的目的是______。

A、扩大主存贮器的容量

B、解决CPU和主存之间的速度匹配问题

C、扩大CPU中通用寄存器的数量

D、既扩大主存的容量,又扩大CPU通用寄存器的数量

11.在流水机器中,控制相关是指_ __。

A、资源使用冲突

B、由转移指令引起的相关

C、先写后读

D、先读后写

12.系统总线中地址线的功能是______。

A、选择主存单元地址

B、选择进行信息传输的设备

C、选择外存地址

D、指定主存和I/O设备接口电路的地址

13.相联存贮器是按______进行寻址的存贮器。

A.地址指定方式

B.堆栈存取方式

C.内容指定方式

D.地址指定与堆栈

14.下面描述的RISC机器基本概念中不正确的句子是______。

A.RISC机器不一定是流水CPU

B.RISC机器一定是流水CPU

C.RISC机器有复杂的指令系统

D.CPU配置很少的通用寄存器

15.主机、外设不能并行工作的方式是_ __。

A.程序查询方式 B.中断方式 C.DMA方式 D.通道方式

一、填空题(每空1分,共10分)

1.若[X]补=11010011,则X的十进制数真值是______。

用四位反码表示为。

2. (-4)

10

3.在一个32位总线中,时钟频率为20MHZ,总线数据的传输周期为5个时钟传输4

个字的数据块,总线数据的传输速率为_______。

4.微指令分成水平型微指令和垂直型微指令,________ 型微指令可同时执行若干

个微操作。

5.假定对字符码ll00101做偶校验,没有数据错误,偶校验的字符码是。

6.存储器模块采用多体交叉编址方式:同一模块内的地址都是。

7.DMA技术的出现,可以通过DMA控制器使得___ ___ 与__ ____之

间可以进行直接访问。

8.在典型的PCI总线中“北桥”是指___ ___桥,“南桥”是指__ ___桥。

二、计算题

1.假设X= - 0.1011,Y= 0.0111,采用双符号位法,计算X-Y=?同时指出是否发生“溢出”?上溢出还是下溢出?

2.已知x=21×0.1101, y=23×(-0.1010), 两数均以补码表示,阶码、尾数均采用双符号位。

阶码的数值部分用两位表示、尾数的数值部分用五位表示,其中包含一位隐藏数值位,朝+∞舍入。

求x+y=?

3.16K×8位(=128×128×8位) DRAM芯片,设存储器的读/写周期为0.5µs,CPU在1µs内至少要访问一次。

(1)若采用集中刷新,刷新周期最短是多长时间?(2)若采用异步刷新,刷新周期是2 ms,每隔多长时间对芯片刷新一行?(3)若采用分散式刷新,刷新周期是多长时间?

4.磁盘组有10片磁盘,每片有两个记录面,最上最下两个面不用,存储区域内径22cm,外径33cm,道密度为40道/cm,内层位密度400位/cm,转速3600转/分。

问:(1)共有多少个柱面?(2)盘组总存储容量是多少?(3)数据传输率是多少?

三、某计算机部分的指令助记符和指令格式如下图所示,设机器字长为8位,rs代

表源寄存器,rd代表目标寄存器。

(1)分析下面指令格式的特点;(2)写出指令MOV R1,R3和 INC R3 的机器指令代码。

四、有一个cache-主存存储层次。

Cache为4个块。

采用组相联映像,组内块数为

2块,替换算法为近期最少使用法(LRU)。

1)如下表所示,主存块地址流的访问顺序是:4,1,2,4,3,7,0,0,4,7, cache 初始时为空,请列出cache 中各块随时间的使用情况;

2)指出访问主存块地址时cache失效又发生争用(即替换)的访问顺序;

3)求出这段访问期间cache的命中率。

访问顺序 1 2 3 4 5 6 7 8 9 10 组

号主存块地址 4 1 2 4 3 7 0 0 4 7

Cache 块

地

址

0 组

1 组

访问情况

五、某计算机CPU的模型如下图所示,

(1)用方框图语言表示如下三条指令的指令周期:

MOV R2,R1 (R1中的数送入R2)

LAD R3,5 (把数据CACHE 地址5中的数据送入R3)。

ADD R2,R3 (R2与R3中的数相加,结果送入R2)

(2)用文字表述LAD指令的执行周期CPU所执行的动作。

CPU的模型图

六、流水线结构分为4个段,即取指(IF)段、译码(ID)段、执行(EX)段和写回(WE)

段。

IF,ID,WE 段只需1个时钟周期完成。

EX段有多个功能部件,其中LOAD/STORE 部件完成数据cache访问,只需一个时钟周期;逻辑运算和减法运算完成需2个时钟周期,乘法运算需3个时钟周期,它们都已流水化。

IE段有内部数据定向传送,结果生成即可使用。

现有如下4条指令序列,

● I1 LAD R0,A ;M(A)->R0,M(A)是存储器单元

● I2 SUB R1,R0 ; (R1) + (R0)->R0

●I3 SHR R0,R2 ;R0的内容逻辑右移R2次再送入R0

● I4 MUL R2,R3 ;(R2)×(R3)->R2

(1)请写出指令流水线的时空图;

(2)请写出指令的相关性。

七、设有一台计算机的指令系统共有10条指令,他们的使用频率分别为:0.19,

0.12, 0.10, 0.13, 0.17, 0.03, 0.02, 0.15, 0.08, 0.01。

(1)用霍夫曼编码设计这10条指令的操作码,并计算操作码的平均长度;

(2)设计两种编码长度,且平均长度不超过3.2位的等长扩展操作码,并计算操作码平均长;

(3)若操作码为固定长度编码,需要多少位?其后继产品需要增加18条指令,并与原来指令保持兼容,操作码应该扩展到多少位?

基本模型机CPU的数据通路结构图下所示,(1)画出下面三条机器指令的微程序流

程图。

(2) 如果R0和R1寄存器的初始值分别为22H和66H,存储器地址为0AH单元

中存放的数据为35H,写出下面三条指令运行后LED数码管显示的数据。

用方框图语言表示如下三条指令的指令周期:

用文字表述MOV指令的执行周期CPU所执行的动作

MOV R0,R1 ;(R0)→R1

ADD [0AH],R0 ;(R0)+[0AH]→R0

OUT 10,R0 ;(R0)→LED。