High-performance, parallel, stack-based genetic programming

专业英语_单词

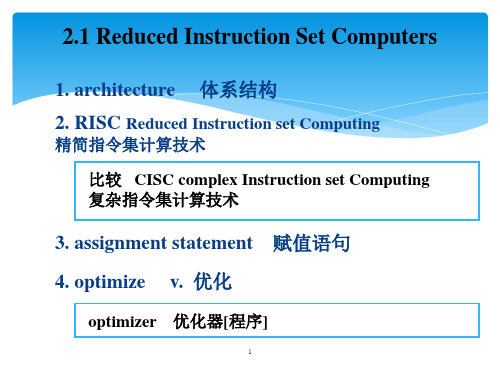

说明:本单词是按照专业英语吕老师课前提问的单词所总结,由于水平有限加之期末时间仓促,错误在所难免,敬请同学们谅解~~~编辑:张婷婷于超2011年12月17日——————1.1原件、组件component性能capability暂时的temporary永久的permanentlyRAM random-access memory 随机存取器ROM read-only memory 只读存取器存取,访问access指令instruction数据data命令command内部的internal外部的external处理机process主存储器primary storageCPU central processing unit 中央处理机辅助存储器secondary storage容量capacity功能functionality外围设备peripheral1.2总线互联bus interconnection通信communication传输transmission设备device并行parallel串行serial元件、组件component分层结构hierarchy性能performance/capability目的地destination容量capacity处理器processor命令command操作operation体系结构architecture 接口interface、外设peripheral扩充总线expansionSCSI small computer system interface改写rewrite外设peripheralPCI peripheral component体系结构architecture微处理器microprocessor性能、能力capability/performance组件、部件component并行parallel串行serial带宽bandwidth接口interface目的地destination实现、设计实现implementation电磁magnetic吞吐量throughput配置configuration应用程序application驱动程序driver兼容的compatible操作系统OS operating system可扩展性scalabilityVOIP voice on IP IP电话,网络电话分层结构hierarchy2.4USB universal serial bus 通用串行总线设备device并行的parallel串行的serial调制解调器modem数码相机digital camera安装软件install the software标准化的standardizedOS operating system 操作系统驱动程序driver电缆cable版本version升级upgrade发行,发布release宽带bandwidth多媒体multimedia应用程序application传输transmission可兼容性compatibility容量capacity分辨率resolution外设peripheral生产率productivity性能performance枚举技术enumeration中断interrupt成批bulk执行perform询问query火线firewire替代品alternative接口interface实现implement数字化的digitized屏蔽干扰shield interference 方便的convenient配置configuration互联interconnect外设peripheral3.1局域网local area network便利的convenient配置configuration重新配置reconfiguration互联interconnect外设peripheral面向对象object-oriented类class结构struct预处理preprocessor表示represent相互作用interaction 数据结构data structure消息message方法method面向过程procedure-oriented函数function调用函数call function扩充extension抽象abstract属性attribute实例instance最终ultimately属于描述describedescriptiondescriptor封装encapsulation3种描述符public private protected派生子类derived subclass分层结构hierarchy多态性polymorphism派生derive响应response公共的public可扩充性extendability虚函数virtual function动态的dynamically静态的statically运行run编译compile完成accomplish早期约束early binding初始化initialize体系结构architecture利用utilize分布式环境distributed environment硬件软件平台hardware and software platform 嵌入式系统embedded system可靠的reliable可移植的portable实时的real time确保secure鲁棒性robust操作operation网络network分布式的distributed升级upgrade补丁patch动态地dynamically可移植的portable自适应的adaptable面向对象object-oriented平台platform多线程的multithreaded可移植性的portable portability动态性能dynamic capability各自的respective灵活的flexible性能capability performance分配allocate存储storage特性property编译compile接口interface执行executeOS operating system 操作系统GUI graphical user interface图形用户接口SCSI small computer system interface小型计算机系统接口IC integrated circuit 集成电路软件software硬件hardware便利的,方便的convenient资源分配器resource allocator汇编程序assembler编译程序compiler批处理程序batch system常驻,驻留resident利用率utilization脱机操作off-line operation缓冲buffering重叠overlap多道程序设计multiprogramming分时time sharing交互interact实时系统real-time system多处理器multiprocessor 专用应用系统dedicated application传感器sensor可靠性reliability网络OS network operating system分布式OS distributed operating system 并行OS parallel operating system 干扰interfere正常的normal修改modify指令instruction执行execute中断interrupt体系结构architecture设备device应用程序application信息information消息message视频video音频audio输入输出input output显示present表示represent脚本script引擎engine位图bit map分配allocation进程process便利的convenient文本编辑器text editor数据库database检索retrieveIC integrated circuit 集成电路集成integrated访问access通信communication视图view完成百分比completion percentage窗口管理程序window managers显示present消息message描述describe采取适当的行动take appropriate action 适当的appropriate复杂的sophisticated构造construct库library可重用的reusable交互interaction对象object互连connection接口,界面interface终端terminal独立性independence工作台workstation应用程序application可移植性transportability各种各样variety5.1网络network因特网Internet硬件hardware软件software通信communication不兼容incompatible网关gateway转换translation互连interconnect主干网backbone参考模型reference model协议protocol协议栈protocol stackFTP 文件传输协议file transfer protocol LAN 局域网local area networkWAN 广域网wide area networkMAN 城域网metropolitan area network TCP/IP 传输控制协议transmission control protocol 互联网协议Internet protocol下载downloadWWW 万维网world wide web图形电子文档graphical electronic document 浏览browse浏览器browser视频会议video conferencing传真fax体系结构框架architectural framework存取,访问access客户机client 服务器serverC/S 客户机服务器client-sever systemB/S 浏览器服务器browser-sever system 网页page链接link超文本hypertext虚拟现实virtual reality服务进程sever process协议protocolHTTP 超文本传输协议hypertext transport protocol URL 统一资源定位器uniform resource locator DNS 域名系统domain name system万维网WWW word wide webISP internet serve provider因特网服务提供商导航navigation大写字母capitalization恰当的,适当的appropriate工具栏toolbar滚动栏scroll bar标题栏title bar菜单栏menu bar地址栏address bar5.2有线的wired无线的wireless区域网regional设置setup主干网backbone拨号dial-up调制解调器modem接口interface临时的temporary当前因特网会话the current session安全性security呼叫等待call-waiting呼叫转接call-forwarding促进facilitate数据传输率data transfer rate装置appliance便携设备portable device访问accessISDN 综合服务数字网integrated services digital network PC 个人电脑personal computer 静态static虚函数virtual function实际上virtuallyIC 集成电路integrated circuitCD 光盘compact discDVD 数字视盘digital video discLCD 液晶显示liquid crystal display HTML 超文本传输语言hypertext markup language CA TV 有线电视community antenna television 专用的dedicatedDSL 数字用户线路digital subscriber line可用的available转换,开关switch安装installation版本version宽带broadband选择alternative电缆cable升级update全双工full-duplex访问access带宽bandwidth显著的dramatically费用fee卫星satellite固定无线fixed wireless移动无线mobile wireless防火墙firewall文件共享file sharing合并incorporate性能capability 7.1数据库database数据库管理系统database management system 关系relation表示represent永久permanently软件software主存primary storage便利的convenient检索retrieve数据抽象data abstraction最终用户ultimate user终端terminal设备device访问access视图view用户程序application外部的external内部的internal应用程序application指定specify专用dedicate实现implement管理员administrator分配allocate分布式distribute语义semantic语法syntax约束constraint描述describe基于对象object-based实体关系模型entity-relationship model各自的respectively主键primary key相关联的associated适当的appropriate层次hierarchy多态性polymorphism封装encapsulationRTOS 实时操作系统real-time operating system XML 可扩展标记语言Extensive Makeup Language URI 统一资源标识符Uniform Resource IdentifierISO/OSI 国际标准化组织International Standardization Organization /开放系统互联模型Open System Interconnection ModelASP 应用服务供应商application service providerPAN 个人网personal area networkCAD 计算机辅助设计Computer - Aided DesignCAM 计算机辅助制造computer-aided manufacturingGIS 地理信息系统Geographic Information SystemCIM 计算机集成制造computer integrated manufacturingAPI 应用程序设计接口Application Program InterfaceDA T 数字式录音带digital audio tapeMPEG 运动图像专家组Moving Picture Experts GroupJPEG 联合图像专家组Joint Photographic Experts GroupMIDI 音乐设备数字界面Musical Instrument Digital InterfaceA VI 多媒体文件格式Audio V ideo Interactive--------只总结到2011年12月15日,12月22日的上课内容请同学们自行总结。

轮机工程三管轮考试单词

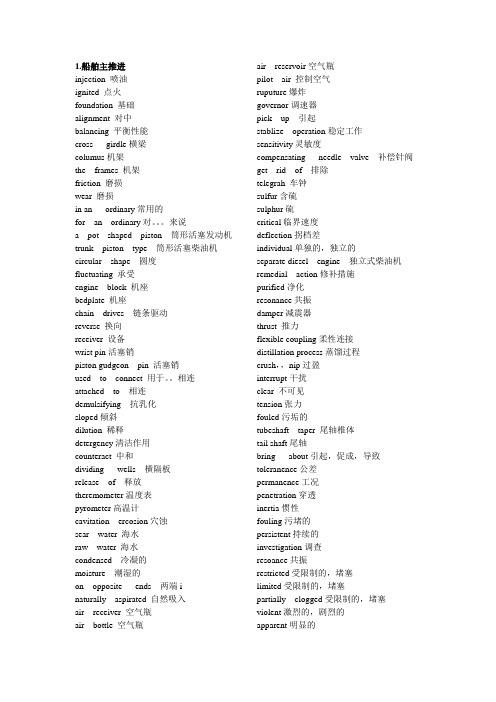

1.船舶主推进injection 喷油ignited 点火foundation 基础alignment 对中balancing 平衡性能cross girdle横梁columus机架the frames 机架friction 磨损wear 磨损in an ordinary常用的for an ordinary对。

来说a pot shaped piston 筒形活塞发动机trunk piston type 筒形活塞柴油机circular shape 圆度fluctuating 承受engine block 机座bedplate 机座chain drives 链条驱动reverse 换向receiver 设备wrist pin活塞销piston gudgeon pin 活塞销used to connect 用于。

相连attached to 相连demulsifying 抗乳化sloped倾斜dilution 稀释detergency清洁作用counteract 中和dividing wells 横隔板release of 释放theremometer温度表pyrometer高温计cavitation ercosion穴蚀sear water 海水raw water 海水condensed 冷凝的moisture 潮湿的on opposite ends 两端inaturally aspirated 自然吸入air receiver 空气瓶air bottle 空气瓶air reservoir空气瓶pilot air 控制空气ruputure爆炸governor调速器pick up 引起stablize operation稳定工作sensitivity灵敏度compensating needle valve 补偿针阀get rid of 排除telegrah 车钟sulfur含硫sulphur硫critical临界速度deflection拐档差individual单独的,独立的separate diesel engine 独立式柴油机remedial action修补措施purified净化resonance共振damper减震器thrust 推力flexible coupling柔性连接distillation process蒸馏过程crush,,nip过盈interrupt干扰clear 不可见tension张力fouled污垢的tubeshaft taper 尾轴椎体tail shaft尾轴bring about引起,促成,导致toleranence公差permanence工况penetration穿透inertia惯性fouling污堵的persistent持续的investigation调查resoance共振restricted受限制的,堵塞limited受限制的,堵塞partially clogged受限制的,堵塞violent激烈的,剧烈的apparent明显的MEP平均有效压力MCR最大持续功率MIP平均指示功率fracture折断,破碎seizure咬岗temporary临时flexible coupling弹性联轴节flection弯曲,indined倾斜pads推力块collar推力环contemporary当代的wisely明智theoretical理论上gray淡褐色accelerate加速initiate发起simultaneously同时的against对着kept pace with跟上,,的步伐projection突起物,凸台predude排除hollow中空的firmly牢固的plasma等离子precise精确的generating tube产气管downcomer下降occupy占据oriteria标准precipitate沉淀re-purge重新扫气chloride氯化物neutralization number中和值adazzling white亮白色purged驱气scarenge驱气warp弯曲band弯曲pit麻点stack烟囱econmizer经机器troublesome棘手的,麻烦的contribute to成为。

英语作文loong和dragon的区别

英语作文loong和dragon的区别全文共3篇示例,供读者参考篇1A Tale of Two Processors: Loong and Dragon Chips ComparedAs a computer science student, I've become fascinated by the world of processors – those tiny yet incredibly powerful computing engines that make our digital devices run. Recently, two homegrown Chinese processor architectures have caught my attention: the Loong and the Dragon chips. While both are designed and manufactured in China, they have distinct characteristics that set them apart. In this essay, I'll delve into the key differences between these processors, exploring their performance, architecture, and potential applications.Performance: The Need for SpeedOne of the most critical factors in evaluating a processor is its performance, measured in terms of clock speed, instructions per cycle (IPC), and overall throughput. The Loong architecture, developed by Loongson Technology Corporation, boasts impressive performance capabilities. The latest Loong64 3A5000processor, for instance, features a clock speed of up to 3.0 GHz and supports up to 256 cores, making it a formidable contender in the high-performance computing (HPC) arena.On the other hand, the Dragon chips, designed by Higon Information Technology Co., Ltd., have been primarily focused on delivering cost-effective performance for general-purpose computing tasks. The Dragon V9 processor, for example, operates at a modest clock speed of 1.8 GHz but offersquad-core processing capabilities, making it suitable for applications that don't require extreme computational power.Architecture: Diverging PathsThe Loong and Dragon processors have taken different architectural approaches, each with its own strengths and weaknesses. The Loong architecture is based on the MIPS64 instruction set architecture (ISA), which has a long history and is known for its simplicity and efficiency. This design philosophy has allowed Loongson to optimize the Loong chips forhigh-performance computing tasks, such as scientific simulations, data analysis, and artificial intelligence (AI) workloads.In contrast, the Dragon processors adopt the GroundMedia ISA, which is derived from the ARM architecture. This decisionwas likely driven by the widespread adoption of ARM-based processors in mobile and embedded devices, as well as the vast ecosystem of software and development tools available for ARM. The GroundMedia ISA aims to strike a balance between performance and power efficiency, making Dragon chipswell-suited for applications in consumer electronics, Internet of Things (IoT) devices, and mobile computing.Ecosystem and Software SupportThe success of any processor architecture heavily depends on the availability of software and development tools. In this regard, the Loong and Dragon chips have taken divergent paths, each with its own challenges and opportunities.The Loong processors benefit from the well-established MIPS ecosystem, which includes a wide range of compilers, libraries, and development tools. Additionally, the open-source nature of the MIPS architecture has fostered a vibrant community of developers and researchers, contributing to the ongoing improvement and optimization of the Loong chips.On the other hand, the Dragon processors face the challenge of building a robust software ecosystem around the GroundMedia ISA. While ARM-based software can be ported to the Dragon architecture, the process can be complex and mayrequire significant effort from developers. However, the growing interest in Chinese-developed processors could spur the creation of dedicated development tools and libraries for the Dragon chips, potentially attracting a new generation of developers and software vendors.Applications and Use CasesGiven their distinct characteristics, the Loong and Dragon processors are better suited for different applications and use cases.The Loong chips, with their high-performance capabilities and support for massive parallelism, are well-positioned for applications in scientific computing, data centers, and artificial intelligence. These processors could power supercomputers, high-performance clusters, and specialized hardware accelerators for tasks like deep learning and large-scale data analysis.In contrast, the Dragon processors are more aligned with general-purpose computing tasks, such as desktop and mobile applications, embedded systems, and Internet of Things (IoT) devices. Their focus on cost-effectiveness and power efficiency makes them attractive choices for consumer electronics, smarthome appliances, and other devices that require moderate processing power while maintaining energy efficiency.Security and TrustworthinessIn an increasingly digital world, security and trustworthiness have become paramount concerns, particularly for critical infrastructure and sensitive applications. Both the Loong and Dragon processors have made efforts to address these concerns, but their approaches differ.The Loong architecture implements hardware-based security features, such as memory protection mechanisms and secure boot capabilities. These measures aim to prevent unauthorized access to sensitive data and ensure the integrity of the system during the boot process. Additionally, the open-source nature of the MIPS architecture allows for thorough security audits and community-driven security improvements.On the other hand, the Dragon processors leverage the security features inherited from the ARM architecture, including TrustZone technology and secure enclaves. These features enable hardware-based isolation and secure execution environments, protecting sensitive data and code from potential threats.ConclusionThe Loong and Dragon processors represent China's growing technological prowess and ambition to develop homegrown computing solutions. While they share a common goal of providing high-performance and energy-efficient processing capabilities, their architectural differences and design philosophies make them suitable for distinct applications and use cases.The Loong chips, with their MIPS-based architecture and focus on high-performance computing, are well-suited for scientific simulations, data analysis, and AI workloads. Their support for massive parallelism and hardware-based security features make them attractive choices for mission-critical applications and sensitive computing tasks.In contrast, the Dragon processors, built upon the GroundMedia ISA, offer a balance between performance and power efficiency, making them suitable for general-purpose computing tasks, consumer electronics, and IoT devices. Their ARM-based heritage provides a familiar development ecosystem, albeit with the challenge of building a robust software stack around the GroundMedia ISA.As these homegrown Chinese processors continue to evolve and gain traction, it will be fascinating to observe their impact on the global technology landscape. The competition between the Loong and Dragon architectures could drive innovation, foster the development of new software and hardware ecosystems, and ultimately benefit end-users by providing more choices and tailored computing solutions.篇2The Differences Between Loong and Dragon ProcessorsAs a student studying computer science, one area that has always fascinated me is the world of processors. These tiny yet incredibly complex components are the beating heart of our computers, responsible for executing instructions and performing calculations at lightning-fast speeds. In recent years, the processor market has witnessed the emergence of two fascinating architectures: the Loong and the Dragon. While both are designed to power our digital devices, they exhibit distinct characteristics that set them apart. In this essay, I will delve into the key differences between these two processor families, exploring their origins, architectures, performance, and potential applications.Origins and Background:The Loong processor finds its roots in China, developed by Loongson Technology Corporation, a company based in Beijing. Loongson's mission has been to create a domestic,high-performance processor architecture that can compete with established players like Intel and AMD. The first Loong processor, the Loongson 1, was introduced in 2001, marking the beginning of China's journey towards self-sufficiency in the processor domain.On the other hand, the Dragon processor emerged from the United States, born out of the collaborative efforts of several technology giants, including Google, Amazon, and Ampere Computing. The Dragon architecture was designed to address the growing demand for energy-efficient and scalable processors, particularly in the realm of cloud computing and data centers.Architectural Differences:One of the most fundamental differences between the Loong and Dragon processors lies in their underlying architectures. The Loong processors are based on the MIPS (Microprocessor without Interlocked Pipeline Stages) instruction set architecture (ISA), which has a long history dating back to the1980s. MIPS is known for its simplicity, efficient pipeline design, and compatibility with a wide range of software and operating systems.In contrast, the Dragon processors are built upon the Arm instruction set architecture (ISA), which has become increasingly popular in the mobile and embedded systems market. Arm's strength lies in its power-efficient design, making it an attractive choice for devices with limited power budgets, such as smartphones, tablets, and Internet of Things (IoT) devices.Performance and Capabilities:When it comes to performance, both the Loong and Dragon processors have their strengths and weaknesses. The Loong processors have traditionally been geared towardhigh-performance computing (HPC) applications, offering impressive computational power and support for advanced features like vector processing and multithreading. However, they have sometimes lagged behind their Intel and AMD counterparts in terms of raw processing power and software ecosystem support.The Dragon processors, on the other hand, have been optimized for cloud computing and data center workloads. They excel in areas such as parallel processing, virtualization, andenergy efficiency. While they may not match the raw performance of high-end server processors from Intel and AMD, the Dragon processors offer a compelling balance of performance and power efficiency, making them well-suited for large-scale deployments in cloud environments.Applications and Use Cases:The differing architectures and capabilities of the Loong and Dragon processors lend themselves to different applications and use cases.Loong processors have found their niche inhigh-performance computing environments, such as scientific simulations, weather forecasting, and computational fluid dynamics. They are also utilized in certain server and workstation applications where performance is the primary consideration. Additionally, the Loong architecture has garnered interest from the Chinese government and military for national security and defense applications, as it provides a domestic alternative to foreign-made processors.On the other hand, Dragon processors are primarily targeted at cloud computing and data center infrastructure. Their energy-efficient design and scalability make them well-suited for powering large-scale cloud services, web servers, and distributedcomputing applications. Companies like Amazon and Google have already begun deploying Dragon-based processors in their data centers, taking advantage of their cost-effectiveness and power savings.Future Outlook and Implications:As technology continues to evolve, both the Loong and Dragon processor architectures are poised to play significant roles in shaping the future of computing.For the Loong processors, the primary challenge lies in gaining wider adoption and software ecosystem support. While China's push for domestic technology has driven the development of the Loong architecture, its adoption outside of specialized domains has been limited. Overcoming this hurdle and fostering a robust software ecosystem will be crucial for the Loong processors to compete on a global scale.The Dragon processors, backed by industry giants like Google and Amazon, have a strong foundation and significant resources invested in their development. As cloud computing and data center demands continue to grow, the need for energy-efficient and scalable processors will likely increase, positioning the Dragon architecture as a compelling solution. However, competition from established players like Intel andAMD, as well as emerging architectures like Arm's Neoverse, will keep the landscape dynamic and competitive.Conclusion:In the ever-evolving world of processors, the Loong and Dragon architectures represent two distinct approaches to addressing the computational demands of our digital age. While the Loong processors excel in high-performance computing and offer a domestic alternative for China, the Dragon processors have carved out a niche in the cloud computing and data center realm, leveraging their energy efficiency and scalability.As a student fascinated by these technologies, I find it exciting to witness the advancements and innovations happening in the processor space. The competition between different architectures and the pursuit of performance, efficiency, and versatility will undoubtedly drive further technological breakthroughs. Regardless of which architecture ultimately prevails, one thing is certain: the relentless pursuit of computing power will continue to shape our digital future in ways we can scarcely imagine.篇3The Loong and Dragon: A Tale of Two Chinese CPUsAs a student of computer science, I've become fascinated by the world of processors and the companies that design them. While most of us are familiar with the big names like Intel and AMD, there are other players in the game, particularly in China. Two such processors are the Loong and the Dragon, both designed and manufactured by Chinese companies. At first glance, they may seem similar, but upon closer inspection, some significant differences emerge.The Loong processor is developed by Loongson Technology Corporation Limited, a company based in Beijing. It is a RISC (Reduced Instruction Set Computer) processor, which means it has a relatively simple instruction set architecture (ISA) compared to more complex designs like x86. The Loong family includes several different models, such as the Loong3A4000 and the Loong3C3000, each with varying levels of performance and power efficiency.One of the key advantages of the Loong processor is its compatibility with the MIPS instruction set, which has been around since the 1980s. This compatibility allows the Loong to run a wide range of existing software that has been compiled for MIPS architectures. Additionally, the Loong processors are designed with a focus on low power consumption, making themsuitable for use in embedded systems and other applications where energy efficiency is crucial.On the other hand, the Dragon processor is developed by Higon Information Technology Co., Ltd., a company based in Tianjin. Unlike the Loong, the Dragon is a CISC (Complex Instruction Set Computer) processor, which means it has a more complex instruction set architecture. The Dragon family includes models such as the Dragon V9, which is designed for use in servers and high-performance computing applications.One of the key advantages of the Dragon processor is its compatibility with the x86 instruction set, which is widely used by many popular operating systems and applications. This compatibility allows the Dragon to run a vast array of software that has been compiled for x86 architectures, without the need for emulation or recompilation. Additionally, the Dragon processors are designed with a focus on high performance, making them suitable for use in demanding applications such as scientific simulations and data processing.Despite their differences, both the Loong and the Dragon processors share a common goal: to reduce China's reliance on foreign-made processors and foster the growth of a domestic semiconductor industry. This goal has become increasinglyimportant in recent years, as tensions between China and the United States have escalated, and concerns over supply chain security have grown.From a technical standpoint, one of the key differences between the Loong and the Dragon processors lies in their instruction set architectures. As mentioned earlier, the Loong is a RISC processor, while the Dragon is a CISC processor. RISC architectures are generally simpler and more energy-efficient, while CISC architectures are more complex and can execute more complex instructions in a single cycle.Another important difference is their respective performance capabilities. While the Loong processors are designed with a focus on low power consumption, they tend to lag behind the Dragon processors in terms of raw computational power. The Dragon processors, on the other hand, are designed to deliver high performance, making them better suited for demanding applications such as scientific simulations and data processing.It's worth noting that both the Loong and the Dragon processors are still relatively new players in the market, and their adoption and development are closely tied to the broader goals of China's semiconductor industry. As such, it's likely that we'llcontinue to see ongoing improvements and innovations in both processor families as time goes on.From a student's perspective, the competition between the Loong and the Dragon processors is fascinating to observe. On one hand, the Loong's compatibility with the MIPS instruction set and its focus on low power consumption make it an interesting option for embedded systems and other applications where energy efficiency is a priority. On the other hand, the Dragon's compatibility with the x86 instruction set and its focus on high performance make it a compelling choice for demanding applications such as scientific simulations and data processing.Ultimately, the choice between the Loong and the Dragon processors will likely depend on the specific needs of the application and the priorities of the user or organization. For students like myself, the opportunity to learn about and work with these processors can be invaluable, as it provides exposure to different architectures and design philosophies.As I continue my studies in computer science, I'll be keeping a close eye on the developments in the Loong and Dragon processor families, as well as the broader landscape of China's semiconductor industry. It's an exciting time to be in this field,and I can't wait to see what the future holds for these homegrown Chinese processors.。

hpc方案工程

hpc方案工程Key Components of an HPC SolutionAn HPC solution is comprised of several key components that work together to provide high-performance computing capabilities. These components include:1. Compute Nodes: The compute nodes are the heart of an HPC system, and they are responsible for executing the computational tasks. These nodes are typically high-performance servers with multiple processors, large amounts of memory, and fast interconnects.2. Interconnect: The interconnect is the network that connects the compute nodes and allows them to communicate with each other. A high-speed, low-latency interconnect is essential for ensuring efficient data transfer and synchronization between the compute nodes.3. Storage: HPC systems require a large amount of storage to store the massive amounts of data generated during computational tasks. High-performance storage solutions, such as parallel file systems and object storage, are used to provide fast and reliable data access.4. Software Stack: The software stack is the collection of software tools and libraries that are used to manage and run HPC applications. This includes the operating system, job schedulers, parallel programming models, and scientific computing libraries.Considerations for Designing an HPC InfrastructureWhen designing an HPC infrastructure, there are several important considerations that need to be taken into account. These considerations include:1. Scalability: An HPC system should be designed to scale to accommodate the increasing computational demands of the organization. This includes the ability to add additional compute nodes, storage capacity, and interconnect bandwidth as needed.2. Performance: The performance of an HPC infrastructure is crucial for meeting the requirements of high-performance computing applications. This includes optimizing the compute nodes, interconnect, and storage for maximum performance and efficiency.3. Reliability: An HPC system needs to be highly reliable to ensure uninterrupted operation and minimal downtime. This includes using redundant components, fault-tolerant designs, and reliable data storage solutions.4. Manageability: Managing an HPC infrastructure can be complex, so it is important to design the system with manageability in mind. This includes centralized management tools, monitoring and alerting systems, and automation for common tasks.Benefits of Implementing a Robust HPC SystemImplementing a robust HPC system can provide several benefits to an organization, including:1. Increased Productivity: HPC systems enable researchers and engineers to perform complex simulations and analyses in a fraction of the time it would take with traditional computing systems. This can significantly increase productivity and accelerate time-to-discovery.2. Cost Savings: Although the initial investment in an HPC system can be substantial, the long-term cost savings can be significant. By consolidating workloads onto a single, high-performance system, organizations can reduce the need for multiple lower-performance systems and decrease overall operational costs.3. Competitive Advantage: Organizations that have access to high-performance computing capabilities have a competitive advantage in their respective fields. They can tackle more complex problems, produce higher-quality results, and stay ahead of the competition.4. Flexibility: HPC systems can be used for a wide range of applications, from scientific research to big data analytics. This flexibility allows organizations to leverage their HPC infrastructure across multiple departments and use cases.ConclusionDesigning and implementing an HPC solution requires careful consideration of the key components, infrastructure design considerations, and the potential benefits of high-performance computing. With the right HPC infrastructure in place, organizations can achieve significant productivity gains, cost savings, and a competitive advantage in their respective fields. As the demand for faster and more powerful computing capabilities continues to grow, it is essential for organizations to invest in robust HPC solutions that can meet their specific needs.。

IT单词-H

hierarchical cell structure (HCS) 分级信元结构,分层信元结构

hierarchical database 层次结构数据库

hierarchical file system (HFS) 层次结构档案系统

hierarchical menu 层次结构式操作指引

hardware/software co-design 硬软件协同设计

hardwire 固定线路

hardwired circuit 固定电路

hardwired control logic 固定线路控制逻辑

hardwired logic 固定线路逻辑

harmonic 谐波

harmonic analyzer 谐波分析仪

header 起始码;标头

header error control (HEC) 信头差错控制,报头差错控制

header suppression 数据报头压缩

heap 堆阵

hearing, threshold 听觉阈

heat 热

heat capacity 热容量

heat conduction 热传导

harmonic balance simulator 谐波平衡模拟器

harmonic distortion 谐波失真

harmonic voltage distortion 谐波电压失真

harmonic, even 偶谐波

harmonic, odd 奇谐波

harmonic, sub- 次谐波

high definition television (HDTV) 高清晰度电视

计算机专业常用英语

10. local a. 局部;本地[机]

localhost 本(主)机

比较 remote a. 远程 remote access 远程访问 remote communications 远程通信 remote terminal 远程终端

11. ring network 环形网络 ring topology 环形拓扑

4

比较 model 模型 module 模块 modulo 模(运算)

11. opcode 操作码( operation code ) 12. decode v. 译码

decoder 译码器,解码器,翻译程序

5

2.2 Microprocessor And Microcomputer

1. integrated circuit 集成电路

8. library (程序)库,库

16

9. single threading 单线程处理方式

Within a program, the running of a single process at a time. 在程序中,一次运行一个进程的方式。

single-precision 单精度 single-user computer 单用户计算机 thread 线程;线索 threaded tree 线索树 threading 线程技术

11

16. idle a. 空闲,等待

Operational but not in use. 用来说明处在可操作状态但不在使用。 idle state 空闲状态

12

18. launch v. 启动,激活 19. prototyping 原型法 20. project n. 投影运算 21. workstation 工作站

建筑学英语【完全版】

建筑学英语【完全版】 01.建筑学序码汉文名英文名注释01.1 总论01.0001 建筑学architecture01.0002 建筑物building01.0003 人体测量学anthropometry01.0004 人体尺寸human dimensions01.0005 人体舒适human comfort01.0006 人类行为human behavior01.0007 [人因]工效学human factorengineering01.0008 人类群居学ekistics01.0009 环境心理学environmentalpsychology01.0010 人类生态学human ecology01.0011 建筑功能building function01.0012 建筑类型学building typology01.0013 空间构图space configuration01.0014 领域性territoriality01.0015 建筑经济学building economics01.0016 价值工程学value engineering01.0017 费用效益cost effectiveness01.0018 建筑美学architectural aesthetics 01.0019 艺术格调artistic touch01.0020 建筑几何学architectural geometry 01.0021 建筑形态学architecturalmorphology01.0022 建筑形式architectural form01.0023 建筑风格architectural style01.0024 建筑环境architectural environment 01.0025 环境艺术environmental art01.0026 建筑文化architectural culture01.0027 建筑文脉architectural context01.0028 建筑符号学architectural semiotics 01.0029 模式语言pattern language01.0030 建筑设计方法学architecturaldesign methodology01.0031 无障碍设计barrier free design01.0032 古建筑保护historical buildingpresvervation01.0033 风水学fengshui01.0034 建筑科学building science01.0035 建筑气候学building climatology01.0036 建筑物理[学]building physics01.0037 建筑光学building optics01.0038 建筑热学building thermodymamics,building thermology01.0039 建筑声学building acoustics01.0040 太阳能建筑solar building01.0041 建筑工程building engineering01.0042 建筑标准化buildingstandardization01.0043 建筑模数building module01.0044 模数协调modular coordination01.0045 建筑工业化buildingindustrialization01.0046 工业化建筑体系industrializedbuilding system01.0047 支撑体系support system01.0048 填充体系infill system01.0049 建筑安全building safety01.0050 建筑防灾building disasterprevention01.0051 建筑节能building energyconservation01.0052 减灾学natural disasterprevention01.0053 建筑防火building fire protection 01.0054 建筑抗震building aseismicity01.0055 建筑病理building pathology01.0056 健康建筑healthy building01.0057 建筑综合症synthetic buildingsyndrome,SBS01.0058 建筑保安building security01.0059 防卫性空间defensible space01.0060 建筑性能building performance01.0061 建筑评价building evaluation01.0062 社会影响评价social impactassessment,SIA01.0063 环境影响评价environmental impactassessment,EIA01.0064 建筑测量building surveying01.0065 建筑勘探building geotechnics01.0066 工程施工engineering construction 01.0067 建筑材料building material01.0068 建筑制品building product01.0069 建筑构造architecturalconstruction01.0070 建筑设备系统building servicesystem01.0071 建筑设备building equipment01.0072 建筑设备安装building equipmentinstallation01.0073 建筑设施building facilities01.0074 建筑设施管理building facilitiesmanagement01.0075 建筑装修builidng finishing01.0076 室内装饰interior decoration01.0077 建筑壁画mural01.0078 浅浮雕bas-relief01.0079 建筑维护building maintenance01.0080 建筑修缮building repair01.0081 建筑管理building management01.0082 建筑业building industry01.0083 建筑立法building legislation01.0084 建筑史architectural history01.0085 古典建筑classical architecture01.0086 古典柱式classical order01.0087 古埃及建筑Egyptian arhcitecture01.0088 美索不达米亚建筑Mesopotamianarchitecture01.0089 古希腊建筑Greek architecture01.0090 古罗马建筑Roman architecture01.0091 拜占庭建筑Byzantine architecture 01.0092 罗曼式建筑Romanesque architecture 01.0093 哥特式建筑Gothic architecture01.0094 文艺复兴建筑Renaissancearchitecture01.0095 巴洛克建筑Baroque architecture01.0096 洛可可建筑Rococo architecture01.0097 伊斯兰建筑Islamic architecture01.0098 新艺术运动Art-nouveau Movement01.0099 现代主义modernism01.0100 国际风格International Style01.0101 后现代主义post-modernism01.0102 功能主义functionalism01.0103 构成主义constructivism01.0104 表现主义expressionism01.0105 手法主义mannerism01.0106 折中主义eclecticism01.0107 结构主义structuralism01.0108 新古典主义neoclassicism01.0109 复古主义revivalism01.0110 民族风格national style01.0111 新理性主义neorationalism01.0112 批判地方主义critical regionalism 01.0113 解构主义deconstruction01.0114 反构成主义deconstructivism01.0115 粗野主义brutalism01.0116 文脉主义contextualism01.0117 新陈代谢主义metabolism01.0118 高技术建筑hightech architecture01.0119 乡土建筑vernacular architecture01.0120 有机建筑organic architecture01.0121 国际建筑师协会Union ofInternational Architects, UIA01.0122 亚洲建筑师协会Architects RegionalCouncil Asia, ARCASIA 01.0123 中国建筑学会Architectural Societyof China, ASC01.2 建筑类型及组成01.0124 单层建筑single-story building01.0125 多层建筑multistory building01.0126 高层建筑highrise building, tallbuilding01.0127 超高层建筑super highrisebuilding, supertall building01.0128 摩天楼skyscraper01.0129 活动房屋mobile house01.0130 建筑队群building group01.0131 裙房podium01.0132 楼层floor01.0133 夹层mezzanine01.0134 底层ground floor01.0135 地下室basement01.0136 半地下室sub-basement01.0137 顶层top floor01.0138 房间room01.0139 走廊corridor01.0140 游廊gallery01.0141 入口entrance01.0142 门斗anteroom01.0143 门厅enrtance hall, vestibule01.0144 接待室reception room01.0145 会议室conference room01.0146 值班室janitor's room01.0147 收发室mail/distribution room01.0148 问询处information desk01.0149 衣帽间coat room, cloak room01.0150 开水间water heater room01.0151 卫生间washroom01.0152 厕所toilet01.0153 浴室bathroom01.0154 电话总机房telephone exchangeroom01.0155 电子计算机房computer room01.0156 广播室broadcasting room01.0157 储藏室storage room01.0158 变电间substation01.0159 锅炉间boiler room01.0160 阳台balcony01.0161 平台terrace01.0162 天井light court01.0163 屋前空地frontage01.0164 居住建筑residential building01.0165 人居human habitat01.0166 住房housing01.0167 独户住宅single family house01.0168 多户住宅multi-family house01.0169 联排式住宅row house, terracehouse01.0170 台阶式住宅stepped house,terraced house01.0171 公寓式住宅apartment house01.0172 板式住宅slab block01.0173 点式住宅point block01.0174 跃层式公寓skip-floor aparment01.0175 外廊式公寓exterior-corridor typeapartmnet01.0176 步行上楼式公寓walk-up apartment01.0177 电梯式公寓elevator apartment01.0178 平房one-story house, bungalow01.0179 农舍cottage01.0180 别墅villa01.0181 庭院式住宅courtyard house01.0182 两层独立公寓maisonette01.0183 宿舍dormitory01.0184 青年公寓youth apartment01.0185 老年公寓house for the elderly01.0186 养老院nursing home01.0187 公共活动室commom room, communityroom01.0188 卧室bedroom01.0189 起居室living room01.0190 书房study01.0191 餐室dining room01.0192 厨房kitchen01.0193 壁柜wall unit, case unit01.0194 吊柜hanging cabinet01.0195 地窖cellar01.0196 教育建筑educational building01.0197 大学建筑university building01.0198 学院建筑institute building,collehe building01.0199 专科学校建筑specail collegebuilding01.0200 中学建筑secondary schoolbuilding01.0201 职业学校建筑professional schoolbuilding01.0202 小学建筑elementary schoolbuilding01.0203 幼儿园kindergarten01.0204 寄宿制托儿所nursery01.0205 全日制托儿所day-care center01.0206 教室classroom01.0207 阶梯教室lecture theater01.0208 电化教室audio-visual classroom01.0209 实验教室laboratory01.0210 美术教室artroom 01.0211 音乐教室music room01.0212 劳作教室handicraft room01.0213 实验工厂practice workshop01.0214 儿童活动室children's playroom01.0215 哺乳室nursing room01.0216 配乳室milk kitchen01.0217 隔离室isolation room01.0218 学生中心students' center01.0219 游戏场地playground01.0220 黑板blackborad01.0221 讲台forum01.0222 文化建筑cultural building01.0223 图书馆library01.0224 博物馆museum01.0225 科技馆science museum01.0226 美术馆art museum01.0227 画廓gallery01.0228 文化中心cultural center01.0229 展览馆exhibition hall01.0230 天文馆planetarium01.0231 水族馆aquarium01.0232 自然博物馆natural history museum 01.0233 青年中心youth center01.0234 妇女中心women's center01.0235 陈列室display room01.0236 展览室exhibition room01.0237 阅览室reading room01.0238 阅览间reading carrel01.0239 微缩图书阅览室microfilm readingroom01.0240 善本图书阅览室rare books readingroom01.0241 文献资料阅览室referenceliterature room01.0242 目录厅catalogue room01.0243 出纳处lending department01.0244 编目室cataloging room01.0245 鉴定室authentication room01.0246 研究室research room01.0247 复印室copying room01.0248 装订室binding room01.0249 书库stack room01.0250 开架管理open stack management01.0251 闭架管理closed stack management 01.0252 书架book shelf01.0253 展览架display shelf01.0254 体育建筑sport building01.0255 体育场stadium01.0256 室内体育场indoor stadium01.0257 体育馆sports hall01.0258 游泳馆swimming hall, natatorium01.0259 健身房gymnasium01.0260 田径场track field01.0261 足球场football court, soccercourt01.0262 篮球场basketball court01.0263 排球场volleyball court01.0264 手球场handball court01.0265 垒球场softball court01.0266 网球场tennis court01.0267 羽毛球场badminton court01.0268 壁球场squash court01.0269 棒球场baseball field01.0270 射击场shooting range01.0271 射箭场archery01.0272 赛马场race course01.0273 斗牛场bullfighting arena01.0274 自行车赛场velodrome01.0275 滑冰场skating rink01.0276 水上运动场aquatic sport waters 01.0277 冰球场ice hockey rink01.0278 曲棍球场hockey field01.0279 高尔夫球场golf course01.0280 跳伞俱乐部parachute club01.0281 保龄球场bowling club01.0282 桑拿浴室sauna bathroom01.0283 按摩室massage room01.0284 练习场warm-up01.0285 看台grandstand01.0286 活动看台movable stand01.0287 裁判席referee's seat01.0288 运动员席sportsman's seat01.0289 固定座位bleacher01.0290 场地field01.0291 跑道track01.0292 跳高场地high jump runway01.0293 跳远场地long jump runway01.0294 三级跳远场地triple jump runway 01.0295 撑竿跳高场地pole vault runway 01.0296 标枪投掷区javelin throwing zone 01.0297 铅球投掷区hammer throwing zone 01.0298 铁饼投掷区discus throwing zone 01.0299 障碍赛跑道hurdle race track01.0300 跳水池diving pool01.0301 武术场地martial arts ground01.0302 举重场地weightlifting platform 01.0303 摔跤场地wrestling ring01.0304 拳击比赛台boxing ring01.0305 击剑场地fencing area01.0306 游泳池swimming pool01.0307 泳道swimming lane01.0308 跳水台diving platform 01.0309 体操台gymnastic floor01.0310 单杠horizontal bar01.0311 双杠parallel bars01.0312 高低杠uneven parallel bars01.0313 吊环rings01.0314 鞍马vaulting horse01.0315 跳马pommel horse01.0316 自由体操free exercise01.0317 平衡木halancing beam01.0318 篮球架backboard01.0319 球门goal01.0320 记分牌scoreboard01.0321 跳伞塔parachuting tower01.0322 观演建筑theatrical building01.0323 剧院theater, playhouse01.0324 表演艺术中心performing artscenter01.0325 歌剧院opera house01.0326 芭蕾舞剧院ballet theater01.0327 京剧院Beijing opera theater01.0328 木偶剧院puppet play theater01.0329 露天剧场open air theater,amphitheater01.0330 话剧院drama theater01.0331 实验剧场experimental theater01.0332 电影院cinema, movie theater01.0333 全景电影院panoramic cinema01.0334 立体电影院stereophonic cinema01.0335 汽车影院drive-in theater01.0336 音乐厅concert hall01.0337 交响乐厅symphony hall01.0338 独唱独奏厅recital hall01.0339 观众厅auditorium01.0340 座席容量seating capacity01.0341 多用途观众厅multiuse auditorium 01.0342 多媒体演出multimedia performance 01.0343 地面升起rakde floor01.0344 视线sight line01.0345 排距row spacing01.0346 错排座席staggered seating01.0347 纵过道longitudinal aisle01.0348 横过道transverse aisle01.0349 天花反射板ceiling reflector01.0350 池座层orchestra level01.0351 池座前排stall01.0352 楼层挑台balcony01.0353 楼面层tier01.0354 包厢box01.0355 迟到席late-comers' seat01.0356 舞台stage01.0357 箱形舞台proscenium frame stage01.0358 旋转舞台revolving stage01.0359 凸出舞台thrust stage01.0360 中心舞台arena stage01.0361 活动舞台flexible stage01.0362 基本台main stage01.0363 侧台side stage01.0364 转台turntable01.0365 升降台elevating stage, stagelift01.0366 车台wagon stage01.0367 表演区acting area01.0368 乐池orchestra pit01.0369 台唇apron, forestage01.0370 台口proscenium01.0371 假台口 false proscenium,adjustable proscenium01.0372 大幕front curtain, house tabs 01.0373 防火幕fire curtain01.0374 天幕cyclorama01.0375 边幕wing sets01.0376 声罩acoustic shell01.0377 布景stage scenery01.0378 道具stage property, prop01.0379 银幕film screen01.0380 宽银幕wide film screen01.0381 立体银幕cinemascope screen01.0382 天桥fly gallery01.0383 灯光渡桥traveling lightinggallery01.0384 舞台塔fly tower01.0385 舞台吊杆flybar, barrten01.0386 手动吊杆hand-driven battern01.0387 电动吊杆motorized winch batten 01.0388 单式吊杆single purchasecounterweight batten01.0389 复式吊杆double purchasecounterweight batten01.0390 排烟窗vent window01.0391 舞台灯光stage lighting01.0392 耳光wall-slot lighting01.0393 面光front lighting01.0394 侧光side lighting01.0395 放映室projection booth,projection room01.0396 放映孔projection port01.0397 观察窗observation port01.0398 后台back stage01.0399 化妆室dressing room, make-uproom01.0400 排练厅rehearsal room01.0401 演员休息室green room 01.0402 舞台监督室stge manager's room 01.0403 灯光控制室light control room01.0404 音响控制室sound control room01.0405 前厅foyer01.0406 售票处box office01.0407 疏散出口emergency exit01.0408 娱乐建筑recreation building01.0409 娱乐中心recreation center01.0410 舞厅ballroom01.0411 俱乐部clubhouse01.0412 夜总会night club01.0413 舞池dancing floor01.0414 医[疗]卫[生]建筑medical building 01.0415 医院hospital01.0416 综合医院general hospital01.0417 精神医院mental health hospital 01.0418 口腔医院dental hospital01.0419 妇科医院gynaecologic hospital01.0420 妇产医院obstetric hospital01.0421 儿科医院pediatric hospital01.0422 传染医院contagious diseasehospital01.0423 肿瘤医院tumour hospital01.0424 眼科医院ophthalmologic hospital 01.0425 疗养院sanatorium01.0426 急球中心emergency care center 01.0427 康复中心rehabilitation center01.0428 中医院traditional Chinesemedical hospital01.0429 医疗站medical station01.0430 卫生所health center01.0431 防疫站health and quarantinestation01.0432 门诊部outpatient department01.0433 急诊部emergency department01.0434 治疗部examination-treatmentcenter01.0435 理疗部therapeutic department01.0436 化疗部chemical treatmentdepartment01.0437 手术部operationdepartment,surgical suite01.0438 针灸部acupuncture department01.0439 放射部radioactive department01.0440 分娩部delivery department01.0441 住院部ward01.0442 同位素室radioisotope unit01.0443 化验室testing laboratory01.0444 挂号处admitting office01.0445 候诊室waiting lounge01.0446 诊室consulting room01.0447 药房pharmacy01.0448 病房patients' room01.0449 隔离病房isolation ward01.0450 阳光室solaria01.0451 营养厨房dietary kitchen01.0452 手术准备室preparation room01.0453 手术消毒室sterilizing room01.0454 麻醉室anesthesia room01.0455 手术洗涤室scrub-up01.0456 停尸房mortuary01.0457 解剖室autopsy room01.0458 中心供应站central supply01.0459 工业建筑industrial building01.0460 火力发电厂steam power station01.0461 选煤厂coal preparation plant01.0462 炼油厂oil refinery01.0463 液化石油气厂liquid petroleum gasplant, LPG plant01.0464 自来水厂water supply andpurification plant01.0465 钢铁厂iron and steel works01.0466 铝厂aluminium factory01.0467 焦化厂coke plant01.0468 机械厂machine making factory01.0469 汽车厂automobile factory01.0470 拖拉机厂tractor factory01.0471 机车车辆厂locomotive and coachwagon factory01.0472 机床厂machine tool factory01.0473 电机厂electric motor factory01.0474 冷冻机厂refrigerating machinewagon01.0475 锅炉厂boiler making factory01.0476 轴承厂bearing factory01.0477 齿轮厂gear factory01.0478 电镀厂electroplating factory01.0479 电解厂electrolysis tactory01.0480 建筑机械厂building equipmentfactory01.0481 建筑材料厂building materialfactory01.0482 建筑五金厂building hardwarefactory01.0483 建筑陶瓷厂building ceramicsfactory01.0484 水泥厂cement works01.0485 砖瓦厂brick and tile factory01.0486 木材厂woodworking factory01.0487 大理石厂marble factory01.0488 精密仪器厂precision instrumentfactory 01.0489 仪器仪表厂instument and meterfactory01.0490 钟表厂clock and watch factory01.0491 眼镜厂spectacles factory01.0492 化工厂chemical plant01.0493 塑料厂plastics plant01.0494 制药厂pharmaceutical factory01.0495 油漆厂paint factory01.0496 制管厂piping factory01.0497 皮毛加工厂leather factory01.0498 纺织厂textile mill01.0499 针织厂knitting mill01.0500 印染厂dyeing plant01.0501 服装厂tailor shop01.0502 鞋厂shoemaking factory01.0503 工艺美术厂handicraft factory01.0504 印刷厂printing press01.0505 玩具厂toy making factory01.0506 面包厂bakery01.0507 面粉厂flour mill01.0508 食品厂food products factory01.0509 清真食品厂muslem food productsfactory01.0510 豆制品厂bean products factory01.0511 饮料厂beverage01.0512 酿酒厂winery01.0513 啤酒厂brewery01.0514 屠宰厂butchery01.0515 肉类加工厂meat products factory 01.0516 卷烟厂cigarette factory01.0517 茶厂tea factory01.0518 糖厂sugar mill01.0519 厂房factory building01.0520 车间workshop01.0521 堆场storage yard01.0522 原料加工车间raw material handingplant01.0523 治炼车间smelting shop01.0524 铸造车间casting shop01.0525 锻造车间forging shop01.0526 冲压车间drop forging shop01.0527 焊接车间welding shop01.0528 金工车间machine-cutting shop01.0529 木工车间carpentry shop01.0530 加工车间 processing plant01.0531 装配车间assembly plant01.0532 冷拉车间cold-drawing shop01.0533 热处理车间heat-treatment shop01.0534 电镀车间electroplating shop01.0535 电解车间electrolysis shop01.0536 油漆车间painting shop01.0537 机修车间machine repair shop01.0538 中试车间pilot plant01.0539 烧制车间furnace room01.0540 精密车间precision workshop01.0541 洁净车间dust-proof workshop,clearoom01.0542 中央试验室central laboratory01.0543 动力站power plant01.0544 锅炉房boiler house01.0545 煤气发生站gas generating station 01.0546 压缩空气站compressed air station 01.0547 氧气站oxygen station01.0548 乙炔站acetylene generatingstation01.0549 充电站battery recharge room01.0550 仓库warehouse, godown01.0551 总仓库central warehouse01.0552 成品库final product storage01.0553 装卸站台loading platform01.0554 厂前区administration quarter01.0555 生活间changing room, lockerroom01.0556 吊车crane01.0557 汽车地磅truck-weighing platform 01.0558 水塔water tower01.0559 电瓶车库battery car room01.0560 商业建筑commercial building01.0561 百货商店department store01.0562 超级市场supermarket01.0563 自选商场self service store01.0564 购物中心shopping center01.0565 市场market hall01.0566 农贸市场farm product market01.0567 鱼市fishmonger, fish stall01.0568 肉市butcher shop01.0569 禽市poultry stall01.0570 蛋市egg stall01.0571 果市fruit stall01.0572 菜市场vegetable market01.0573 批发商店wholesale store01.0574 零售商店retail store01.0575 专卖店speciality shop01.0576 粮店grain store01.0577 副食店foodstuffs store01.0578 食品店provisions shop01.0579 熟食店delicatessen shop01.0580 点心铺pastry store01.0581 杂货铺grocery01.0582 饭馆restaurant01.0583 饮食店cafeteria01.0584 小吃店snack bar 01.0585 快餐店fast food restaurant01.0586 茶馆 tea house01.0587 包子铺stuffed bun house01.0588 食堂canteen01.0589 中药店traditional Chinsesmedicine store01.0590 西药店drugstore01.0591 布店cloth store01.0592 呢绒绸缎店silk and wool fabricstore01.0593 服装店clothing store01.0594 鞋帽店hat and shoes store01.0595 床上用品店bed linens store01.0596 家具店furniture store01.0597 眼镜店spectacles store01.0598 钟表店clocks and watches store01.0599 文具用品店stationary store01.0600 书店bookstore01.0601 花店flower shop01.0602 服饰店haberdashery01.0603 洗染店laundering and dyeingshop01.0604 干洗店dry cleaning shop01.0605 工艺美术品店arts and caftsstore01.0606 金银手饰店jewelry store01.0607 珠宝店jewelry shop01.0608 照相馆photo studio01.0609 理发店barber shop01.0610 美发廊hair salon01.0611 美容院beauty parlour01.0612 浴堂bath house01.0613 旅馆hotel01.0614 旅店inn01.0615 宾馆guesthouse01.0616 汽车旅馆motel01.0617 银行bank01.0618 储蓄所saving bank01.0619 证券交易所stock exchange01.0620 营业厅shopping hall01.0621 售货区Sales area01.0622 顾客活动区customers' area01.0623 橱窗shop window, show window01.0624 收款柜台cashier01.0625 货架shelf01.0626 货柜counter01.0627 卸货间delivery room01.0628 卸货台delivery platform01.0629 主食加工间staple food processingroom01.0630 副食加工间non-staple foodprocessing room01.0631 主食库staple food storage01.0632 副食库non-staple food storage01.0633 调料库condiment storage01.0634 备餐间pantry, food preparationroom01.0635 食具洗涤消毒间ware washing andsterilizing room01.0636 烧火间firing sector01.0637 冷[藏]库cold storage01.0638 冷藏间refrigerated storage room01.0639 冷冻间freezed storage room01.0640 制冻间ice-mking room01.0641 客房guest room01.0642 套间客房suite01.0643 总统客房presidential suite01.0644 单床间single-bed room01.0645 双床间double room01.0646 休息厅looby, loung01.0647 接待厅reception hall,front desk01.0648 总服务台reception desk01.0649 餐厅dining hall01.0650 中餐厅Chinese restaurant01.0651 西餐厅west restaurant01.0652 咖啡厅coffee house, coffee shop01.0653 风味餐厅speciality restaurant01.0654 宴会厅banquet hall01.0655 多功能厅multi-function hall01.0656 酒巴间bar01.0657 洗手间rest room01.0658 洗衣房laundry01.0659 交通建筑transportain building01.0660 航空港airport01.0661 候机楼air-terminal01.0662 售票厅booking hall01.0663 候机厅departure hall01.0664 行李托运站baggage check-in01.0665 旅客通道passenger concourse01.0666 海关检查处customs examination01.0667 登机口boarding gate01.0668 行李提取站bagggage claim01.0669 停机坪apron01.0670 直升机坪helistop01.0671 指挥塔command tower01.0672 飞机跑道runway01.0673 火车站railway terminal, railwaystation01.0674 汽车客运站bus passenger terminal,bus passenger station01.0675 水路客运站waterway passengerterminal, watermqy passengerstation01.0676 候车室waiting lounge01.0677 行李室luggage room01.0678 站台railway platform01.0679 站台雨棚platform shed01.0680 灯塔beacon, lighthouse01.0681 汽车库garage01.0682 多层车库multistory garage01.0683 加油站petrol filling station01.0684 汽车修理站car repair pit01.0685 汽车洗车台car wash01.0686 岗亭sentry box01.0687 农业生产建筑farm building01.0688 粮库granary01.0689 筒仓silo01.0690 种子库seed storage01.0691 选种室seed selection room01.0692 粮食加工厂grain processing plant 01.0693 晒场sunning ground01.0694 温室greenhouse01.0695 塑料大棚plastic-cover greenhouse 01.0696 农机站farm machinery station01.0697 保养间maintenance shop01.0698 农具棚agricultural tools shed01.0699 零件库machine parts storage01.0700 农机修理站agricultural machinerepair station01.0701 种马场stallion barn01.0702 役马场military horse harn01.0703 马厩horse stable01.0704 乳牛场dairy farm01.0705 牛舍stanchion barn01.0706 公牛舍bull barn01.0707 犊牛舍calf barn01.0708 挤乳间milking parlour01.0709 牛乳处理间milkhouse01.0710 养鸡场poultry yard01.0711 鸡舍hencoop01.0712 养猪场pig farm, hog lot01.0713 猪舍pigsty01.0714 饲料储存处feed storage01.0715 饲料加工间feed processing plant 01.0716 食槽manger01.0717 饮水池drinking water pool01.0718 人工采精室sperm collection room 01.0719 授精配种室sperm fertilizationroom01.0720 病兽隔离室isolation barn01.0721 兽医站veterinary stastion01.0722 积肥场fertilizer yard01.0723 沼气池biomass pool01.0724 农业服务中心agricultural servicecenter01.0725 办公建筑office building01.0726 多层办公楼multistory office01.0727 高层办公楼office tower01.0728 行政办公楼administrative building 01.0729 专用办公楼special-use officebuilding01.0730 综合性办公楼multiuse officebuilding01.0731 智能办公楼intelligent building,smart building01.0732 单间式布局private office layout 01.0733 大空间布局open landscape layout 01.0734 单走道布局single-corridor layout 01.0735 双走道布局double-corridor layout 01.0736 单外廊布局singleexterior-corridor layout01.0737 双外廊布局doubleexterior-corridor layout01.0738 办公室office room01.0739 设计室design studio01.0740 绘图室driafting room01.0741 档案室file room01.0742 晒图室reproduction room01.0743 图档室drawings and documentsroom01.0744 打字室typing room01.0745 模型室model shop01.0746 公共建筑public building01.0747 国际会议大厦internationalconvertion hall01.0748 国家会议大厦state conventionhall01.0749 市政厅municipal hall, city hall 01.0750 会议厅assembly hall01.0751 礼堂auditorium01.0752 主席台presidium01.0753 同声传译控制室simultaneousinterpretation booth01.0754 翻译室interpreters' room01.0755 监听室monitor room01.0756 扩音控制室broadcasting controlroom01.0757 电视转播室television transmissionroom01.0758 电视转播车television transmissionvehicle01.0759 总指挥室general director's room 01.0760 法院courthouse 01.0761 法庭courtroom01.0762 法官室judge's suite01.0763 秘书室law clerk's room01.0764 律师室lawyer's room01.0765 证人室witness' room01.0766 拘留室detention room01.0767 警察局police station01.0768 派出所police substation01.0769 监狱prison, jail01.0770 牢房prison cell01.0771 接收牢房incarceration cell01.0772 隔离牢房isolation cell01.0773 检查室examination room01.0774 讯问处interrogation room01.0775 看守室guards' room01.0776 瞭望室watchtower01.0777 消防站fire station01.0778 消防车库fire engine room01.0779 训练塔training tower01.0780 通信建筑communication building 01.0781 邮局post office01.0782 电信楼telecommunication building 01.0783 营业柜台clerk counter01.0784 书写台writing counter01.0785 电话间telephone booth01.0786 广播楼broadcasting station01.0787 电视中心television center, TVcenter01.0788 卫星通信地面站satellite groundstation01.0789 录音室recording room01.0790 演播室studio01.0791 微波塔microwave transmissiontower01.0792 电视塔TV transmission tower01.0793 电影制片厂motion picture studio 01.0794 科学建筑science building01.0795 研究中心research center01.0796 试验楼laboratory building01.0797 试验室laboratory room01.0798 物理试验室physics laboratory01.0799 化学试验室chemistry laboratory 01.0800 光学试验室optics laboratory01.0801 声学试验室acoustic laboratory01.0802 混响室reverberationroom01.0803 隔声室soundproof room01.0804 消声室sound attenuation room,anechoic room01.0805 热工试验室thermal sciencelaboratory01.0806 生物试验室biology laboratory01.0807 机械性能试验室mechanicalproperties laboratory01.0808 无菌室bacteria-free room01.0809 计量室metrology room01.0810 天平室balance room01.0811 电子显微镜室electronic microscopyroom01.0812 试验台testing counter01.0813 通风罩ventilation hood01.0814 天文台observatory01.0815 气象台meteorological station01.0816 宗教建筑religious building01.0817 庙temple01.0818 寺buddhist temple01.0819 庵nunnery01.0820 祠shrine01.0821 观taoist temple01.0822 山门temple gate01.0823 大殿main temple hall01.0824 经堂scripture hall01.0825 钟楼bell tower01.0826 鼓楼drum tower01.0827 纪念建筑memorial building01.0828 纪念碑memorial monument01.0829 台座pedestal01.0830 纪念堂memorial hall01.0831 纪念牌坊monumental gateway01.0832 地下建筑underground building01.0833 人防地下室air-raid shelter01.0834 防核尘地下室fallout shelter01.0835 地铁车站subway station, metrostation01.0836 地下商场underground store01.0837 地下窑居underground dwelling01.0838 地下珍宝馆underground treasurechamber01.0839 地下车库underground garage01.0840 地下仓库underground warehouse01.0841 地下金库underground goldtreasury01.0842 地下冷库underground cold storage 01.0843 地下粮仓underground granary01.0844 地下试验室underground testinglaboratory01.0845 生土建筑earth building01.0846 窑居cave dwelling01.0847 夯土房rammed earth construction 01.0848 土筑房earthwork house01.0849 土坯房adobe house01.0850 覆土建筑earth-coveredconstruction 01.0851 自行车棚bicycle shed01.0852 围墙fence wall, enclosure wall 01.0853 大门entrance gate, main door01.0854 门房gatehouse01.3 建筑设计01.0855 设计管理design administration01.0856 建筑法buliding law,buildingordinance01.0857 建筑师注册法architects'registration ordinance 01.0858 职业工程师法professionalengineers' law01.0859 建筑主管机关building authority01.0860 建筑设计院building design institute 01.0861 建筑设计所building design office01.0862 建筑师architecf01.0863 结构工程师structural engineer01.0864 职业工程师professional engineer01.0865 咨询工程师design consultant01.0866 估价师estimator, quantity surveyor 01.0867 设计委托design commission01.0868 设计协议design agreement01.0869 设计合同design contract01.0870 设计义务design liability01.0871 损害义务tort liability01.0872 设计费design fee01.0873 收费标准fee scale01.0874 百分比收费percentage cost fee01.0875 单位面积收费unit area fee01.0876 总额收费lump sum fee01.0877 成本附加费cost plus fee01.0878 资质审查qualification01.0879 注册registration01.0880 执照license01.0881 合伙制设计事务所design partnership 01.0882 设计规范design code01.0883 设计标准design approval01.0884 职业道德守则code of professionalethics01.0885 设计程序design process01.0886 可行性研究feasibility study01.0887 机会研究opportunity study01.0888 建筑策划architectural programming 01.0889 场址选择site selection01.0890 需求预测demand forecasting01.0891 价格分析price analysis01.0892 建筑条件construction conditions01.0893 设计方案design alternative01.0894 劳动定员manpower quota01.0895 实施计划implementation schedule01.0896 投资额investment cost。

云计算Cloud-Computing-外文翻译

毕业设计说明书英文文献及中文翻译学生姓名:学号:计算机与控制工程学院:专指导教师:2017 年 6 月英文文献Cloud Computing1。

Cloud Computing at a Higher LevelIn many ways,cloud computing is simply a metaphor for the Internet, the increasing movement of compute and data resources onto the Web. But there's a difference: cloud computing represents a new tipping point for the value of network computing. It delivers higher efficiency, massive scalability, and faster,easier software development. It's about new programming models,new IT infrastructure, and the enabling of new business models。

For those developers and enterprises who want to embrace cloud computing, Sun is developing critical technologies to deliver enterprise scale and systemic qualities to this new paradigm:(1) Interoperability —while most current clouds offer closed platforms and vendor lock—in, developers clamor for interoperability。

sigcomm2019-hpcc高精度拥塞控制-alibaba

批注本地保存成功开通会员云端永久保存去开通

HPCC: High Precision Congestion Control

Yuliang Li

Rui Miao, Hongqiang Harry Liu, Yan Zhuang, Fei Feng, Lingbo Tang, Zheng Cao, Ming Zhang, Frank Kelly, Mohammad Alizadeh, Minlan Yu

Congestion

0

T

feedback

HPCC - Rate mismatch is bad measurement - Actual sending rate is non-constant, due

to the inflight bytes limit

feedback

2T

0

T

2T

16

Estimating inflight bytes

o Traffic patterns, failure scenarios, and network arch

• Feedback (ECN/delay) is imprecise

o CC has to use heuristics to guess (1) network condition; (2) rate adjustments

英特尔 AVX-512 技术指南 - 数据流工作负载的超并行多哈希计算说明书