8 VHDL语言状态机汇总

第12讲_VHDL状态机

BEGIN CASE current_state IS WHEN s0 => comb_outputs<= “0101”; IF state_inputs = "00" THEN next_state<=s0; ELSE next_state<=s1; END IF; WHEN s1 => comb_outputs<= “1000”; IF state_inputs = "00" THEN next_state<=s1; ELSE next_state<=s2; END IF; WHEN s2 => comb_outputs<= “1100”; IF state_inputs = "11" THEN next_state <= s0; ELSE next_state <= s3; END IF; WHEN s3 => comb_outputs <= “1110”; IF state_inputs = "11" THEN next_state <= s3; ELSE next_state <= s0; END IF; END case; END PROCESS; END behv;

Company Logo

Moore状态机特点总结 1、多进程Moore状态机程序结构清晰,状态输出 时序与状态转换同步,但由于输出无时序控制, 容易产生毛刺。 在对时序要求较高,而对输出的毛刺不敏感的电 路描述中可用多进程 2、单进程Moore状态机同步完成状态译码,状态 输出和状态转换,避免出现毛刺,但是输出较多 进程状态机晚了一个时钟周期 在对毛刺敏感的电路描述中用单进程,比如将电 路的输出作为下一级电路的参考时钟时

VHDL状态机程序

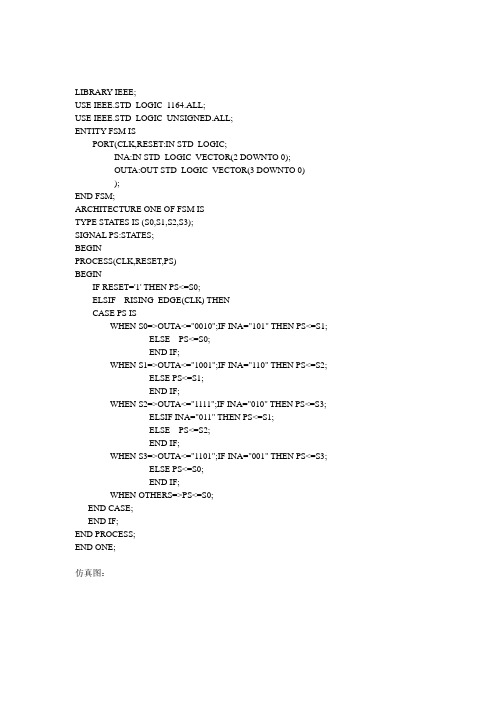

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY FSM ISPORT(CLK,RESET:IN STD_LOGIC;INA:IN STD_LOGIC_VECTOR(2 DOWNTO 0);OUTA:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END FSM;ARCHITECTURE ONE OF FSM ISTYPE STATES IS (S0,S1,S2,S3);SIGNAL PS:STATES;BEGINPROCESS(CLK,RESET,PS)BEGINIF RESET='1' THEN PS<=S0;ELSIF RISING_EDGE(CLK) THENCASE PS ISWHEN S0=>OUTA<="0010";IF INA="101" THEN PS<=S1;ELSE PS<=S0;END IF;WHEN S1=>OUTA<="1001";IF INA="110" THEN PS<=S2;ELSE PS<=S1;END IF;WHEN S2=>OUTA<="1111";IF INA="010" THEN PS<=S3;ELSIF INA="011" THEN PS<=S1;ELSE PS<=S2;END IF;WHEN S3=>OUTA<="1101";IF INA="001" THEN PS<=S3;ELSE PS<=S0;END IF;WHEN OTHERS=>PS<=S0;END CASE;END IF;END PROCESS;END ONE;仿真图:图C:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY C ISPORT(CLK,RESET:IN STD_LOGIC;INA:IN STD_LOGIC_VECTOR(2 DOWNTO 0);OUTA:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END C;ARCHITECTURE ONE OF C ISTYPE STATES IS(S0,S1,S2,S3);SIGNAL PS,NEXT_STATE:STA TES;BEGINREG:PROCESS(CLK,RESET) BEGINIF RESET='1' THEN PS<=S0;ELSIF CLK'EVENT AND CLK='1' THENPS<=NEXT_STA TE;END IF;END PROCESS REG;COM:PROCESS(PS,INA) BEGINCASE PS ISWHEN S0 => OUTA<="0010";IF INA="101" THEN NEXT_STA TE<=S1;ELSE NEXT_STATE<=S0;END IF;WHEN S1 => OUTA<="1001";IF INA="110" THEN NEXT_STATE<=S2;ELSE NEXT_STATE<=S1;END IF;WHEN S2 => OUTA<="1111";IF INA="010" THEN NEXT_STATE<=S3;ELSIF INA="011" THEN NEXT_STATE<=S1;ELSE NEXT_STATE<=S2;END IF;WHEN S3 => OUTA<="1101";IF INA="001" THEN NEXT_STATE<=S3;ELSE NEXT_STATE<=S0;END IF ;END CASE;END PROCESS COM ;END ONE;仿真图:三种编码形式实现方式:一位热码:ARCHITECTURE ONE OF C ISTYPE states IS (S0, S1, S2, S3);attribute enum_encoding :string;attribute enum_encoding of states:type is "one_hot";SIGNAL PS: states;顺序编码:ARCHITECTURE ONE OF C ISTYPE states IS (S0, S1, S2, S3);attribute enum_encoding :string;attribute enum_encoding of states:type is "sequential";SIGNAL PS: states;约翰逊码:ARCHITECTURE ONE OF C ISTYPE states IS (S0, S1, S2, S3);attribute enum_encoding :string;attribute enum_encoding of states:type is "johnson"; SIGNAL PS: states;程序其它部分不变。

VHDL 状态机

集大信息

图5-2 例5-1状态机的工作时序

集大信息

5.2 Moore状态机

5.2.1 多进程状态机

图5-3 ADC0809工作时序

集大信息

Moore状态机的应用实例---A/D采样控制器设计 一般传统方法用CPU或单片机完成,编程简单,控制

灵活,但是控制周期长、速度慢。尤其当A/D本身速度 比较快时,单片机或CPU的速度极大限制了A/D高速性 能的应用。以AD674为例:

comb_outputs : OUT INTEGER RANGE 0 TO 15 );

END s_machine;

ARCHITECTURE behv OF s_machine IS

TYPE FSM_ST IS (s0, s1, s2, s3); --数据类型定义,状态符号化

SIGNAL current_state, next_state: FSM_ST;--将现态和次态定义为新

态,并在此状态中根据外部信号指令,如stata_inpits等 向内或外发出控制信号,如comb_outputs,同时确定 下一个状态的走向,也就是向next_state中附入相应的 状态值。此状态值通过next_state传给REG时序进程, 直到下一个时钟到来再进入另一次的状态转换周期。

4. 辅助进程 用于配合状态机工作的组合进程或时序进程。比如:

WHEN st2=> ALE<='0';START<='0';LOCK<='0';OE<='0'; IF (EOC=‘1’) THEN next_state <= st3; --EOC=1表明转换结束

VHDL语法简单总结

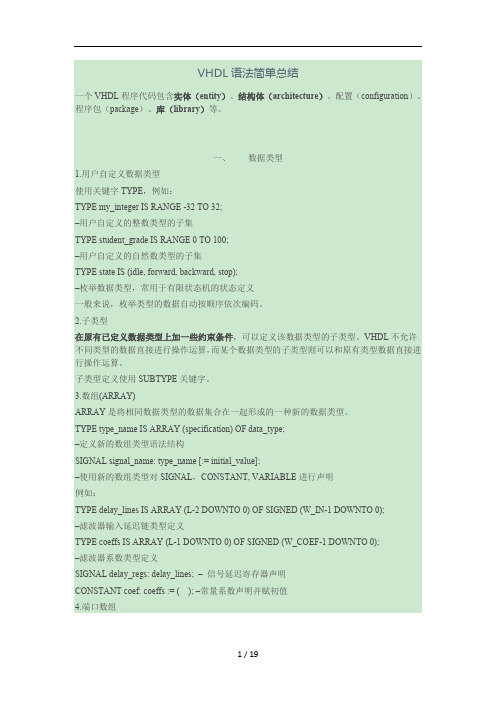

VHDL语法简单总结一个VHDL程序代码包含实体(entity)、结构体(architecture)、配置(configuration)、程序包(package)、库(library)等。

一、数据类型1.用户自定义数据类型使用关键字TYPE,例如:TYPE my_integer IS RANGE -32 TO 32;–用户自定义的整数类型的子集TYPE student_grade IS RANGE 0 TO 100;–用户自定义的自然数类型的子集TYPE state IS (idle, forward, backward, stop);–枚举数据类型,常用于有限状态机的状态定义一般来说,枚举类型的数据自动按顺序依次编码。

2.子类型在原有已定义数据类型上加一些约束条件,可以定义该数据类型的子类型。

VHDL不允许不同类型的数据直接进行操作运算,而某个数据类型的子类型则可以和原有类型数据直接进行操作运算。

子类型定义使用SUBTYPE关键字。

3.数组(ARRAY)ARRAY是将相同数据类型的数据集合在一起形成的一种新的数据类型。

TYPE type_name IS ARRAY (specification) OF data_type;–定义新的数组类型语法结构SIGNAL signal_name: type_name [:= initial_value];–使用新的数组类型对SIGNAL,CONSTANT, VARIABLE进行声明例如:TYPE delay_lines IS ARRAY (L-2 DOWNTO 0) OF SIGNED (W_IN-1 DOWNTO 0);–滤波器输入延迟链类型定义TYPE coeffs IS ARRAY (L-1 DOWNTO 0) OF SIGNED (W_COEF-1 DOWNTO 0);–滤波器系数类型定义SIGNAL delay_regs: delay_lines; –信号延迟寄存器声明CONSTANT coef: coeffs := ( ); –常量系数声明并赋初值4.端口数组在定义电路的输入/输出端口时,有时需把端口定义为矢量阵列,而在ENTITY中不允许使用TYPE进行类型定义,所以必须在包集(PACKAGE)中根据端口的具体信号特征建立用户自定义的数据类型,该数据类型可以供包括ENTITY在内的整个设计使用。

状态机VHDL讲解

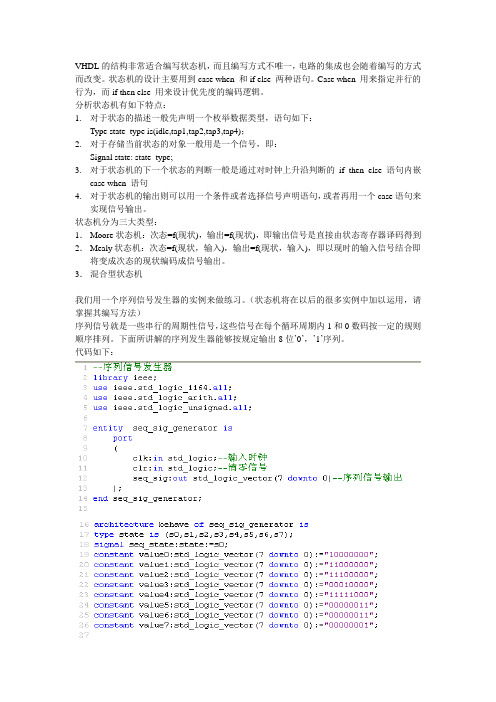

VHDL的结构非常适合编写状态机,而且编写方式不唯一,电路的集成也会随着编写的方式而改变。

状态机的设计主要用到case when 和if else 两种语句。

Case when 用来指定并行的行为,而if then else 用来设计优先度的编码逻辑。

分析状态机有如下特点:1.对于状态的描述一般先声明一个枚举数据类型,语句如下:Type state_type is(idle,tap1,tap2,tap3,tap4);2.对于存储当前状态的对象一般用是一个信号,即:Signal state: state_type;3.对于状态机的下一个状态的判断一般是通过对时钟上升沿判断的if then else 语句内嵌case when 语句4.对于状态机的输出则可以用一个条件或者选择信号声明语句,或者再用一个case语句来实现信号输出。

状态机分为三大类型:1.Moore状态机:次态=f(现状),输出=f(现状),即输出信号是直接由状态寄存器译码得到2.Mealy状态机:次态=f(现状,输入),输出=f(现状,输入),即以现时的输入信号结合即将变成次态的现状编码成信号输出。

3.混合型状态机我们用一个序列信号发生器的实例来做练习。

(状态机将在以后的很多实例中加以运用,请掌握其编写方法)序列信号就是一些串行的周期性信号,这些信号在每个循环周期内1和0数码按一定的规则顺序排列。

下面所讲解的序列发生器能够按规定输出8位’0’,’1’序列。

代码如下:逐行解释:10:清零复位信号,高电平复位清零。

12:序列信号输出。

因为是8位的端口,但序列信号是串行的,所以相当于有8路的序列信号,任取一位端口就是一个序列信号输出。

17:用type声明一种枚举类型。

共8中状态,每个状态都对应唯一的一种输出,至于在什么状态输出什么信号则由程序决定。

18:定义一个state类型信号量,其初始的状态为s0。

19-26:用constant定义一些常量,这些常量将作为在不同状态时的输出信号。

VHDL状态机

ST0 ST1

ST2

ST3 ST4

42

st0 对0809初始化

LOCK:

0-→1 由LOCK 信号锁 存转换 好的数

据

st4 OE=’1'

st1

数据输出 有效

采样周 期等待

st3

st2

启动AD 转换 EOC=

‘0’正 在转换

EOC=‘1'转换结束

图8-6 控制ADC0809采样状态图

43

PROCESS

30

31

32

33

34

35

36

37

38

以下以ADC0809为例 ,说明状态机的设计 方法。用状态机对 0809进行采样控制首 先必须了解工作时序 ,然后据此作出状态 图,最后写出相应的 VHDL代码。

ADC0809 ALE

sin START OE

clk ADDA EOC D[7..0]

VHDL状态机设计

1

2

3

4

5

6

Moore型有限状态机的结构图

7

Mealy型有限状态机的结构图

8

9

10

11

12

13

14

用户自定义数据类型定义语句

这里介绍与有限状态机设计有重要联 系的其它语法现象,即用户自定义数据类 型定义语句及相关的语法现象。如枚举型 、整数类型、数组类型、记录类型、时间 类型、实数类型等。

39

ADC0809工作时序 地址锁存信号

转换启动控制 进入转换状态 转换状态结束

输出有效控制

输出数据 稳定 40

时序图中,START为转换启动控制 信号,高电平有效;ALE为模拟信号输 入选通端口地址锁存信号,上升沿有效; 一旦START信号有效后,状态信号EOC 即变为低电平,表示进入转换状态。转换 结束后,EOC将变为高电平。此后外部 控制可以使OE由低电平变为高电平(输 出有效),此时,0809的输出数据总线 D[7..0]从原来的高阻态变为输出数据有效 。

8 VHDL语言状态机

0000_0000_0000_0001

0000_0000_0000_0010 0000_0000_0000_0100 0000_0000_0000_1000 0000_0000_0001_0000 0000_0000_0010_0000 0000_0000_0100_0000 0000_0000_1000_0000 0000_0001_0000_0000 0000_0010_0000_0000 0000_0100_0000_0000 0000_1000_0000_0000 0001_0000_0000_0000 0010_0000_0000_0000 0100_0000_0000_0000 1000_0000_0000_0000

3.摩尔状态机

Moore状态机的输出只与有限状态自动机的当

前状态有关,与输入信号的当前值无关。 Moore有限状态机在时钟CLOCK脉冲的有效 边沿后的有限个门延后,输出达到稳定值。即 使在一个时钟周期内输入信号发生变化,输出也 会在一个完整的时钟周期内保持稳定值而不变。 输入对输出的影响要到下一个时钟周期才能反 映出来。

Mealy型有限状态机的结构图

1 状态机分类

FSM的设计要点

定义枚举类型表达不同的状态特点;

设置信号表达现有状态和转换的状态;

对每一个现态,利用选择语句,根据控制条

件x决定转换次态;

根据现态和x决定输出y。

1 状态机分类 状态机的基本操作

状态机内部状态转换。状态机的下一个状态

由译码器根据当前状态和输入条件决定。 产生输出信号序列。输出信号由输出译码器 根据当前状态和输入条件决定。

0000

0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111

第八章 状态机在vhdl中的实现

第八章状态机在vhdl中的实现数字电路分为组合逻辑和时序逻辑两大类。

组合逻辑电路的输出只与当前的输入有关;而时序逻辑电路的输出则不仅与当前的输入有关,而且还与过去的一系列输入有关。

组合逻辑电路就像老式的按扭式电扇,按1输入弱风,按2输出中等强度的风,按3则输出强风。

输出风力的大小(输出值)完全取决于按下的按扭值(输入值)。

时序逻辑电路则更像空调遥控器中靠“+”键和“-”键调节温度的控制电路,无法单凭当前按下的键(输入值)来判断将设定的温度(输出值),显然必须知道遥控器当前设定的温度,即遥控器目前的状态。

状态机(State Machine)可以说是一个广义的时序电路,触发器、计数器、移位寄存器等都算是他的特殊功能类型的一种。

实际时序电路的状态数是有限的,因此又叫做有限状态机(FSM,Finite State Machine)。

用VHDL设计状态机不必知道其电路具体实现的细节,而只需要描述在逻辑上加以描述。

因此本书在提到状态机一词时,更多地是指对状态及状态转移的总体描述,而不是一个具体的时序电路。

状态机又分为Moore型与Mealy型,前者的输出仅取决于其所处状态;而后者的输出则不仅与当前所处的状态有关,同时也与当前的输入有关。

(区别这两种状态机的简单方法就是看状态图中,输出信号是在状态图的圈内还是圈外)下面分别介绍这两种状态机在VHDL中的实现。

8.1 Moore状态机的VHDL描述Moore状态机的输出仅由状态决定,一个典型的Moore状态机的状态转移图如图8—1所示,其对应的VHDL程序(带异步复位信号)见例程8—1。

例程8—1的仿真波形如图8—2所示。

图8—1 Moore状态机的状态转移图例程8—1实现Moore状态机的状态转移library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity Moore isport(Reset: IN Std_logic;Clock: IN Std_logic;DIN: IN Std_logic;DOUT: OUT Std_Logic_vector(2 downto 0));end;architecture Mooremachine of Moore ISTYPE State_type IS (S0,S1,S2,S3); --用枚举类型来表示状态,使程序更具可读性SIGNAL State:State_type;BEGINChange_State:PROCESS(Reset,Clock)BEGINIF Reset='1' THENState<=S0;ELSIF rising_edge(Clock) THENcase sTATE ISWHEN S0=>IF DIN='1' THENState<=S1;END IF;WHEN S1=>IF DIN='1' THENState<=S2;END IF;WHEN S2=>IF DIN='1' THENState<=S3;END IF;WHEN S3=>IF DIN='1' THENState<=S0;ELSEState<=S1;END IF;END CASE;END IF;end PROCESS;Output_Process: --此进程决定输出值PROCESS(State)BEGINCASE State ISWHEN S0=>DOUT<="001";WHEN S1=>DOUT<="011";WHEN S2=>DOUT<="101";WHEN S3=>DOUT<="111";END CASE;END PROCESS;END;图8—2 例程8—1仿真波形图例8—1是MAX+plu sII默认的状态机描述格式之一,因此其仿真波形图中将State以状态名的形式表示出来,使仿真波形十分直观、易懂。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

பைடு நூலகம்

有限状态机FSM的设计

哈尔滨工业大学(威海) 信息工程学院电子工程系

第八章 有限状态机FSM的设计

1.状态机概念 2.一般状态机 3.摩尔状态机 4.米利状态机 5.状态机实例

一 .有限状态机的基本概念

有限状态机:指那些输出取决于过去输入部

分和当前输入部分的时序逻辑电路。有限状 态机一般有三部分:输入部分、输出部分和 状态寄存器。 Moore型有限状态机:输出信号仅与当前状 态有关 Mealy型有限状态机:输出信号不仅与当前 状态有关,而且还与所有的输入信号有关。

时序电路的结构与特点

根据输出函数的形式,可以分为moore机和 mealy机两类。

1 状态机分类

一般状态机 MOORE状态机 MEALY状态机

1 状态机分类

FSM的表达形式

通常采用状态转换图表达电路信号的变化:

Moore: y = f(s)

Mealy: y = f(s0,x)

Moore型有限状态机的结构图

begin process(clk,rst) begin if rst='1' then cur_state<=st0; elsif clk'event and clk='1' then cur_state<=next_state; end if; end process; process(cur_state,next_state) begin case cur_state is when st0=>comb_output<="00"; if state_input="00" then next_state<=st0; else next_state<=st1; end if; when st1=>comb_output<="01"; if state_input="00" then

0000

0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111

0000

0001 0011 0010 0110 0111 0101 0100 1100 1101 1111 1110 1011 1010 1001 1000

Mealy型有限状态机的结构图

1 状态机分类

FSM的设计要点

定义枚举类型表达不同的状态特点;

设置信号表达现有状态和转换的状态;

对每一个现态,利用选择语句,根据控制条

件x决定转换次态;

根据现态和x决定输出y。

1 状态机分类 状态机的基本操作

状态机内部状态转换。状态机的下一个状态

由译码器根据当前状态和输入条件决定。 产生输出信号序列。输出信号由输出译码器 根据当前状态和输入条件决定。

状态机的特点

克服了纯硬件数字系统顺序方式控制不灵活的缺

点。 VHDL综合器易于优化 易构成性能良好的时序逻辑模块 结构模式简单、层次分明、易读易懂、易排错 利用同步时序和全局时钟线可实现高速FSM 运行模式类似于CPU,易于进行顺序控制 高可靠性,非法状态易控制

1 状态机分类

一般状态机实例

2.一般状态机

library IEEE; use IEEE.STD_LOGIC_1164.all; entity s_machine is port( clk : in STD_LOGIC; rst : in STD_LOGIC; state_input : in STD_LOGIC_VECTOR(1 downto 0); comb_output : out STD_LOGIC_VECTOR(1 downto 0) ); end s_machine; architecture s_machine of s_machine is type states is (st0,st1,st2,st3); signal cur_state,next_state : states;

状态机的编码方式

Binary、gray-code编码使用最少的触发器, 较多的组合逻辑资源,而one-hot编码反之。 另一方面,对于小型设计使用Binary、 gray-code更有效,而大型状态机使用 one-hot编码更高效。

十位数

二进制码

格林码

独热码

约翰逊

0

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

0000_0000_0000_0001

0000_0000_0000_0010 0000_0000_0000_0100 0000_0000_0000_1000 0000_0000_0001_0000 0000_0000_0010_0000 0000_0000_0100_0000 0000_0000_1000_0000 0000_0001_0000_0000 0000_0010_0000_0000 0000_0100_0000_0000 0000_1000_0000_0000 0001_0000_0000_0000 0010_0000_0000_0000 0100_0000_0000_0000 1000_0000_0000_0000

2.一般状态机

为了能获得可综合的,高效的vhdl状态描述,

建议使用枚举数据类型来定义状态机的状态, 并使用多进程方式来描述状态机的内部逻辑。 • 一般情况下,一个进程描述时序逻辑,包括状 态寄存器的工作和寄存器状态的输出。另一个 进程描述组合逻辑,包括进程间状态值的传递 逻辑以及状态以及状态转换值的输出。必要时 还可以引入第三个进程完成其他的逻辑功能。

使用两段式状态机设计方法

设计状态机的方法多种多样,但总结起来有两大 类:第一种,将状态转移和状态的操作、判断等 写在一起;另一种是将状态转移单独写成一个部 分,将状态的操作和判断写到另一个部分中。 第二种设计方法较好,将同步时序和组合逻辑 分别放到不同的程序块中实现不仅仅便于阅读、 理解、维护,更有利于综合器优化代码,利于用 户添加合适的时序约束条件,利于布局布线器实 现设计。

0000_0000

0000_0001 0000_0011 0000_0111 0000_1111 0001_1111 0011_1111 0111_1111 1111_1111 1111_1110 111_11100 111_11000 111_10000 111_00000 110_00000 100_00000