ADC0809引脚功能及程序

ADC0809引脚功能及程序汇总

• 可以作为状态信号由CPU查询; • 可以作为中断请求信号通知CPU。

• (4) CPU在查询式I/O程序或中断服务程序中:

• 执行输入指令(读ADC0809数据端口); • 该指令经地址译码电路产生OE信号, • 0809内三态缓冲器被打开, • 转换结果通过数据总线进入CPU。

ADC0809应用说明

5、 AD转换电路

编程思路

• (1) 向AD0809写入通道号并启动转换 • (2) 延时1ms后等待EOC出现高电平 • (3) 给OE置高并读入转换数据存入数据

地址或数组中。 • (4) 显示、传输、控制

Proteus 的仿真问题

造成较大的误差,需要采取适当的滤波措施。

2、ADC0809通道地址选择表

ADDC ADDB ADDA 000 001 010 011 100 101 110 111

选通的通道 IN0 IN1 IN2 IN3 IN4 IN5 IN6 IN7

3、ADC0809结构1

启动(高电平脉冲,输入)

start

4、ADC0809转换工作时序

结束 允许输出

1.送地址 2.启动 3.结束 4.允许输出 5.得到数据

ADC0809的工作过程

• (1)ALE信号锁存地址信号ADDA~ADDC。对应 的模拟信号进入0809

• (2) START脉冲(下跳沿)启动A/D转换 • (3) 转换完成后,转换结束信号EOC变为高电

转换的数据就输出给单片机了。

• ADC0809与系统有三种常见的连接方法: • (1) 占用三个I/O端口: • 端口1用来向0809输出模拟通道号并锁存; • 端口2用于启动转换; • 端口3读取转换后的数据结果。 • (2) 占用二个I/O端口: • 端口1输出模拟通道号并锁存,同时启动转换; • 端口2读取转换后的数据结果。 • (3) 通过并行接口芯片(例如8255A)连接。

FPGA与ADC0809接口电路详解

FPGA与ADC0809接口电路详解注:(1)本程序基于FPGA和vhdl编写有详尽的程序解释和原理分析以及原理图,状态图(2)对于adc0809具体资料可上网查在此不累述一.FPGA与ADC0809的接口电路图原理二.关于ADC0809的说明(重点)(1)ale信号(引脚):高电平时把三个地址信号送入地址锁存器,并经译码器得到地址数据,以选择相应的模拟输入通道。

(2)oe信号(引脚)en使能信号:电平由低变高时,打开数据输出锁存器,将转换数据送到数据总线上(3)eoc信号(引脚):eoc为高电平时完成转换,为低电平时正在转换。

(4)start信号(引脚):要给start线送一个100ns宽的启动正脉冲,start下跳沿时,开始进行A/D转换,在转换期间start以保持低电平。

三.转换状态图对于状态图的真值表未列出 注意对应的注释为vhdl 语句ale<='1';start<='0';en<='0';----eoc='1' ale<='0';start<='0';en<='0';--再次检测数据是否转换完 if eoc='0' then next_state<=st4;else next_state<=st5;器,将数据送入数据总线存器四.ADC0809采样接口电路程序--*********ADC0809采样控制*************--******因为FPGA 的时钟频率为50MHz ,则256分频后,即ADC0809输入时钟为195KHz****** --******对ADC0809进行简单的采样控制,得到的数据进FPGA 送到8个并排的数码管显示***** library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity PL_AD isport ( d : in std_logic_vector(7 downto 0); --ADC0809输出的采样数据输入FPGA clk,eoc: in std_logic; --clk 为系统时钟,eoc 为ADC0809转换结束信号输入FPGA lock1,start, ale,en: out std_logic; --ADC0809控制信号FPGA 输出信号 abc_in :in std_logic_vector(2 downto 0); --模拟选通信号abc_out :std_logic_vector(2 downto 0);--ADC0809模拟信号选通信号q : out std_logic_vector(7 downto 0));送至8个并排数码管信号FPGA 输出数字信号 end pl_AD;architecture behav of PL_AD istype states is ( st0,st1, st2, st3, st4,st5,st6);--定义状态类型枚举类型signal current_state, next_state:states:=st0;--定义总体两个状态现态和次态并且初值为st0态signal regl :std_logic_vector(7 downto 0);--定义中间寄存器signal lock : std_logic;signal qq:std_logic_vector(7 downto 0);--定义计数器用于分频begincom:process(current_state,eoc) –此进程主要是驱动ADC0809工作即数据转换过程begincase current_state iswhen st0=>next_state<=st1;ale<='0';start<='0';en<='0';--准备when st1=>next_state<=st2;ale<='1';start<='0';en<='0';--三个地址信号送入地址锁存器when st2=>next_state<=st3;ale<='0';start<='1';en<='0';--开始数据转换when st3=> ale<='0';start<='0';en<='0';--检测数据是否转换完if eoc='1' then next_state<=st3;else next_state<=st4;end if;when st4=> ale<='0';start<='0';en<='0';--再次检测数据是否转换完if eoc='0' then next_state<=st4;else next_state<=st5;end if;when st5=>next_state<=st6;ale<='0';start<='0';en<='1'; --打开输出数据锁存器,将数据送入数据总线when st6=>next_state<=st0;ale<='0';start<='0';en<='1';regl<=d;--打开输出数据锁存器,将数据送入寄存器regl when others=> next_state<=st0;ale<='0';start<='0';en<='0';end case;end process;clock:process(clk) --对系统时钟进行分频,得到驱动ADC0809的时钟信号beginif clk'event and clk='1' then qq<=qq+1;if QQ="01111111" THEN lock<='1';--实现分频current_state <=next_state;--在lock上升沿,转换至下一状态elsif qq<="01111111" then lock<='0';end if;end if;end process;q<=regl;--寄存器数据输出即FPGA输出lock1<=lock;abc_out<=abc_in;--模拟选通信号送往ADC0809end behav;注:有错when st3=> ale<='0';start<='0';en<='0';--检测数据是否转换完if eoc='1' then next_state<=st3;else next_state<=st4;end if;when st4=> ale<='0';start<='0';en<='0';--再次检测数据是否转换完if eoc='0' then next_state<=st4;else next_state<=st5;end if;不过我这里的注释好像错了,这两个when合起来才是检测数据是否转换完的。

adc0809引脚图及功能

adc0809引脚图及功能

ADC0809是8位A / D转换器,它的转换方法为逐次逼近法。

ADC0809为CMOS工艺,其管脚为28脚,管脚排列如图所示。

各个管脚的功能如下:

INo ~ IN7:八个模拟量输入端。

START:启动A / D转换,当START为高电平时,开始A / D转换。

EOC:转换结束信号。

当A / D转换完毕之后,发出一个正脉冲,表示A / D转换结束,此信号可用做

A / D转换是否结束的检测信号或中断申请信号(加一个反相器)。

C、B、A:通道号地址输入端,C、B、A为二进制数输入,C为最高位,A 为最低位,CBA从000~111分别选中通道IN0 ~ IN7。

ALE:地址锁存信号,高电平有效。

当ALE为高电平时,允许C、B、A 所示的通道被选中,并把该

通道的模拟量接入A / D转换器。

CLOCK:外部时钟脉冲输入端,改变外接R、C可改变时钟频率。

D7~D0:数字量输出端。

D7为高位。

VREF(+),VREF(—):参考电压端子,用来提供D / A转换器权电阻的标准电平。

一般 VREF(+)=5V,

VREF(—)= 0V

Vcc:电源电压,+5V。

GND:接地端。

图 ADC0809 管脚排列图

ADC0809可以进行八路A / D转换,并且这种器件使用时无需进行调零和满量程调整,转换速度和精度属中高档,售价又不贵。

所以,一般控制场合采用这些ADC0809(或0800 系列)的A / D转换片是比较理想的。

AD0809详解

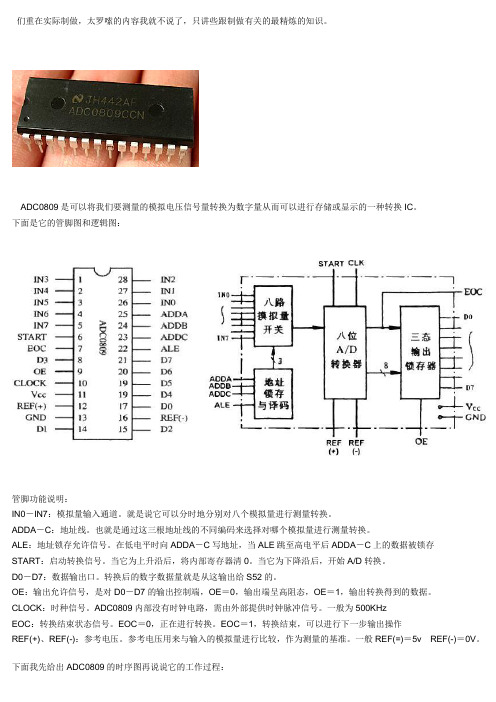

们重在实际制做,太罗嗦的内容我就不说了,只讲些跟制做有关的最精炼的知识。

ADC0809是可以将我们要测量的模拟电压信号量转换为数字量从而可以进行存储或显示的一种转换IC。

下面是它的管脚图和逻辑图:管脚功能说明:IN0-IN7:模拟量输入通道。

就是说它可以分时地分别对八个模拟量进行测量转换。

ADDA-C:地址线。

也就是通过这三根地址线的不同编码来选择对哪个模拟量进行测量转换。

ALE:地址锁存允许信号。

在低电平时向ADDA-C写地址,当ALE跳至高电平后ADDA-C上的数据被锁存START:启动转换信号。

当它为上升沿后,将内部寄存器清0。

当它为下降沿后,开始A/D转换。

D0-D7:数据输出口。

转换后的数字数据量就是从这输出给S52的。

OE:输出允许信号,是对D0-D7的输出控制端,OE=0,输出端呈高阻态,OE=1,输出转换得到的数据。

CLOCK:时种信号。

ADC0809内部没有时钟电路,需由外部提供时钟脉冲信号。

一般为500KHzEOC:转换结束状态信号。

EOC=0,正在进行转换。

EOC=1,转换结束,可以进行下一步输出操作REF(+)、REF(-):参考电压。

参考电压用来与输入的模拟量进行比较,作为测量的基准。

一般REF(=)=5v REF(-)=0V。

下面我先给出ADC0809的时序图再说说它的工作过程:它的工作过程是这样的,①在IN0-IN7上可分别接上要测量转换的8路模拟量信号。

有人问了,可不可以只接一路?我就只想测一个模拟信号。

当然可了②将ADDA-ADDC端给上代表选择测量通道的代码。

如000(B)则代表通道0;001(B)代表通道1;111则代表通道7。

③将ALE由低电平置为高电平,从而将ADDA-ADDC送进的通道代码锁存,经译码后被选中的通道的模拟量送给内部转换单元。

④给START一个正脉冲。

当上升沿时,所有内部寄存器清零。

下降沿时,开始进行A/D转换;在转换期间,START保持低电平。

ADC0809工作原理及C编程

3.C 语言源代码编辑

C51 程序设计是单片机应用的必要组成部分。常见的 C 程序包括注释、头文件、全局变

量定义、自定义函数声明、宏定义、主函数和子函数等内容,对于一个优秀的 C 程序案例,

注释必不可少。本任务作为电压模拟信号采集实验。参考程序如下所示:

/********************************************************************************** * 平台:THMEMU-1 + Keil U4 + STC89C52 * 晶振:12MHZ

**********************************************************************************/

#include<reg51.h>

//调用库文件

unsigned char weima[10]={0xfc,0x60,0xda,0xf2, 0x66,0xb6,0xbe,0xe0,0xfe,0xf6};

ADC0809 是 8 通道 8 位 CMOS 逐次逼近式 A/D 转换芯片,片内有模拟量通道选择开关 及相应的通道锁存、译码电路,A/D 转换后的数据由三态锁存器输出,由于片内没有时钟需 外接时钟信号,利用它可直接输入 8 个单端的模拟信号分时进行 A/D 转换,在多点巡回检测 和过程控制、运动控制中应用十分广泛。。芯片的引脚及内部结构如图 2。

//时钟信号 //延时函数

//T1 初始化 //串口初始化 //T1 定时开始

//先上升沿,后下降沿,延时给转换时间

//T1 定时器,方式 2 //初值,10us,时钟频率 50KHz // // // //

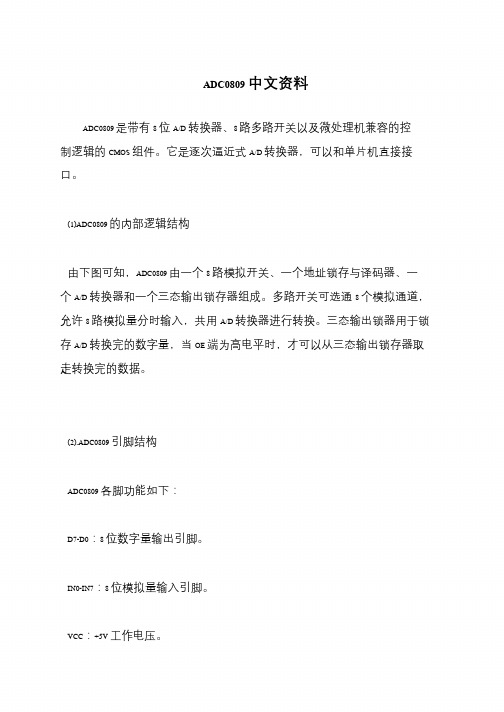

ADC0809中文资料

ADC0809 中文资料

ADC0809 是带有8 位A/D 转换器、8 路多路开关以及微处理机兼容的控制逻辑的CMOS 组件。

它是逐次逼近式A/D 转换器,可以和单片机直接接口。

(1)ADC0809 的内部逻辑结构

由下图可知,ADC0809 由一个8 路模拟开关、一个地址锁存与译码器、一个A/D 转换器和一个三态输出锁存器组成。

多路开关可选通8 个模拟通道,允许8 路模拟量分时输入,共用A/D 转换器进行转换。

三态输出锁器用于锁存A/D 转换完的数字量,当OE 端为高电平时,才可以从三态输出锁存器取走转换完的数据。

(2).ADC0809 引脚结构

ADC0809 各脚功能如下:

D7-D0:8 位数字量输出引脚。

IN0-IN7:8 位模拟量输入引脚。

VCC:+5V 工作电压。

模数转换器ADC0809应用原理

精品文档AD0809应用原理--很全面的资料1.0809 的芯片说明:ADC0809是带有 8 位 A/D 转换器、 8 路多路开关以及微处理机兼容的控制逻辑的 CMOS 组件。

它是逐次逼近式 A/D 转换器,可以和单片机直接接口。

(1) ADC0809的内部逻辑结构由上图可知, ADC0809由一个 8 路模拟开关、一个地址锁存与译码器、一个A/D 转换器和一个三态输出锁存器组成。

多路开关可选通8 个模拟通道,允许8 路模拟量分时输入,共用 A/D 转换器进行转换。

三态输出锁器用于锁存A/D 转换完的数字量,当OE端为高电平时,才可以从三态输出锁存器取走转换完的数据。

( 2).引脚结构IN0- IN7:8 条模拟量输入通道ADC0809对输入模拟量要求:信号单极性,电压范围是0-5V,若信号太小,必须进行放大;输入的模拟量在转换过程中应该保持不变,如若模拟量变化太快,则需在输入前增加采样保持电路。

地址输入和控制线: 4 条ALE为地址锁存允许输入线,高电平有效。

当ALE线为高电平时,地址锁存与译码器将 A,B,C三条地址线的地址信号进行锁存,经译码后被选中的通道的模拟量进转换器进行转换。

A,B 和 C 为地址输入线,用于选通 IN0-IN7 上的一路模拟量输入。

通道选择表如下表所示。

C B A 选择的通道000IN0001IN1010IN2011IN3100IN4101IN5110IN6111IN7数字量输出及控制线: 11 条ST 为转换启动信号。

当 ST 上跳沿时,所有内部寄存器清零;下跳沿时,开始进行 A/ D 转换;在转换期间, ST应保持低电平。

EOC为转换结束信号。

当 EOC为高电平时,表明转换结束;否则,表明正在进行 A/D 转换。

OE为输出允许信号,用于控制三条输出锁存器向单片机输出转换得到的数据。

OE= 1,输出转换得到的数据; OE=0,输出数据线呈高阻状态。

D7- D0为数字量输出线。

ADC0809中文资料

A D C0809中文资料(总5页) -CAL-FENGHAI.-(YICAI)-Company One1-CAL-本页仅作为文档封面,使用请直接删除ADC0809是带有8位A/D转换器、8路多路开关以及微处理机兼容的控制逻辑的CMOS组件。

它是逐次逼近式A/D转换器,可以和单片机直接接口。

(1)ADC0809的内部逻辑结构由下图可知,ADC0809由一个8路模拟开关、一个地址锁存与译码器、一个A/D转换器和一个三态输出锁存器组成。

多路开关可选通8个模拟通道,允许8路模拟量分时输入,共用A/D转换器进行转换。

三态输出锁器用于锁存A/D转换完的数字量,当OE端为高电平时,才可以从三态输出锁存器取走转换完的数据。

(2).ADC0809引脚结构ADC0809各脚功能如下:D7-D0:8位数字量输出引脚。

IN0-IN7:8位模拟量输入引脚。

VCC:+5V工作电压。

GND:地。

REF(+):参考电压正端。

REF(-):参考电压负端。

START:A/D转换启动信号输入端。

ALE:地址锁存允许信号输入端。

(以上两种信号用于启动A/D转换)EOC:转换结束信号输出引脚,开始转换时为低电平,当转换结束时为高电平。

OE:输出允许控制端,用以打开三态数据输出锁存器。

CLK:时钟信号输入端(一般为500KHz)。

A、B、C:地址输入线。

ADC0809对输入模拟量要求:信号单极性,电压范围是0-5V,若信号太小,必须进行放大;输入的模拟量在转换过程中应该保持不变,如若模拟量变化太快,则需在输入前增加采样保持电路。

地址输入和控制线:4条ALE为地址锁存允许输入线,高电平有效。

当ALE线为高电平时,地址锁存与译码器将A,B,C三条地址线的地址信号进行锁存,经译码后被选中的通道的模拟量进入转换器进行转换。

A,B和C为地址输入线,用于选通IN0-IN7上的一路模拟量输入。

通道选择表如下表所示。

C B A选择的通道000IN0001IN1010IN2011IN3100IN4101IN5110IN6数字量输出及控制线:11条ST为转换启动信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

• • • • • • • • •

ADC0809与系统有三种常见的连接方法: (1) 占用三个I/O端口: 端口1用来向0809输出模拟通道号并锁存; 端口2用于启动转换; 端口3读取转换后的数据结果。 (2) 占用二个I/O端口: 端口1输出模拟通道号并锁存,同时启动转换; 端口2读取转换后的数据结果。 (3) 通过并行接口芯片(例如8255A)连接。

ADC0809结构2

START CLK IN7

8路 模拟 开关

控制与时序 SAR 三态 输出 锁存 缓冲 器

EOC D7 数 字 量 输 出

IN0

ADDA ADDB ADDC ALE

树状开关

地址 锁存 与 译码

D0

电阻网络

VCCGND REF(+)

REF(-) OE

基准电压输入VREF(+)和VREF(-)

逐次逼近式的A/D转换器的特点

• 转换速度较快,转换时间在1~100μs以内, 分辨率可达18位,适用于高精度、高频信号 的A/D转换; • 转换时间固定,不随输入信号的大小而变化; • 抗干扰能力较双积分型弱。采样时,干扰信号会 造成较大的误差,需要采取适当的滤波措施。

2、ADC0809通道地址选择表

汽车传感器项目器件 ADC0809

1、ADC0809芯片简介

• • • • • • • • • • • 输 入: 8路(0V~5V) 线性误差:1LSB 数字输出:TTL电平,三态输出 电 源:+5V~15V 时钟频率:10KHZ-1280KHZ (典型640KHz) 转换时间:100μs 分辨率:8位 功 耗:15mW 输入电压范围:0V~VREF CMOS工艺,28Pin 输出: V IN V REF 255 NB

• 1、ADC0809内部带有输出锁存器,可以与 AT89S51单片机直接相连。 • 2、初始化时,使ST和OE信号全为低电平。 • 3、送要转换的通道的地址到A,B,C端口上。 • 4、在ST端给出一个至少有100ns宽正脉冲信号。 • 5、是否转换完毕,我们根据EOC信号来判断。 • 6、当EOC变为高电平时,这时给OE为高电平, 转换的数据就输出给单片机了。

V

REF

V

REF

0809特征

• 逐次逼近型8位A/D转换芯片; • 单极性,量程为0~5V;若信号太小,必 须进行放大;输入的模拟量在转换过程中 应该保持不变,如若模拟量变化太快,则 需在输入前增加采样保持电路。 • 片内有三态输出缓冲器,可直接与CPU总 线连接; • 有较高的性能价格比,适用于对精度和采 样速度要求不高的场合或一般的工业控制 领域。

ADDC 0 ADDB 0 ADDA 0 选通的通道 IN0

0

0 0 1

0

1 1 0

1

0 1 0

IN1

IN2 IN3 IN4

1

1 1

0

1 1

1

0 1

IN5

IN6 IN7

3、ADC0809结构1

启动(高电平脉冲,输入)

500KHz~1MHz

start clock

转换结束(=1,输出)

地址锁存, 输入信号 输出允许 (=1,输入信号)

4、ADC0809转换工作时序

1.送地址 2.启动

结束

3.结束 4.允许输出 5.得到数据

允许输出

ADC0809的工作过程

• (1)ALE信号锁存地址信号ADDA~ADDC。对应 的模拟信号进入0809 • (2) START脉冲(下跳沿)启动A/D转换 • (3) 转换完成后,转换结束信号EOC变为高电 平:

5、 AD转换电路

编程思路

• (1) 向AD0809写入通道号并启动转换 • (2) 延时1ms后等待EOC出现高电平 • (3) 给OE置高并读入转换数据存入数据 地址或数组中。 • (4) 显示、传输、控制

Proteus 的仿真问题

• 它们决定了输入模拟电压的最大值和最小值 • 对转换精度要求不高时,可以把VREF(+)接到 Vcc(+5V)电源上,VREF(-)接GND(地) • 为了避免数字脉冲信号对基准电源的干扰,可以 设置独立的VREF(+)和VREF(-),加在两个引脚 的电压必须满足以下条件: • VREF(+)+VREF(-) =Vcc,偏差值≤±0.1V • Vcc≥VREF(+)≥VREF(-) ≥0

• • • • • • 可以作为状态信号由CPU查询; 可以作为中断请求信号通知CPU。 执行输入指令(读三态缓冲器被打开, 转换结果通过数据总线进入CPU。

• (4) CPU在查询式I/O程序或中断服务程序中:

ADC0809应用说明